## 8 Circuit Description

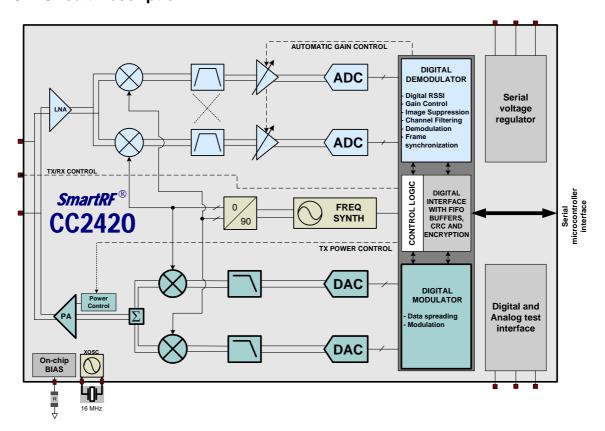

Figure 2. CC2420 simplified block diagram

A simplified block diagram of *CC2420* is shown in Figure 2.

*cc2420* features a low-IF receiver. The received RF signal is amplified by the low-noise amplifier (LNA) and down-converted in quadrature (I and Q) to the intermediate frequency (IF). At IF (2 MHz), the complex I/Q signal is filtered and amplified, and then digitized by the ADCs. Automatic gain control, final channel filtering, despreading, symbol correlation and byte synchronisation are performed digitally.

When the SFD pin goes high, this indicates that a start of frame delimiter has been detected. *CC2420* buffers the received data in a 128 byte receive FIFO. The user may read the FIFO through an SPI interface. CRC is verified in hardware. RSSI and correlation values are appended to the frame. CCA is available on a pin in receive mode. Serial (unbuffered) data modes are also available for test purposes.

The *CC2420* transmitter is based on direct up-conversion. The data is buffered in a 128 byte transmit FIFO (separate from the receive FIFO). The preamble and start of frame delimiter are generated by hardware. Each symbol (4 bits) is spread using the IEEE 802.15.4 spreading sequence to 32 chips and output to the digital-to-analog converters (DACs).

An analog lowpass filter passes the signal to the quadrature (I and Q) upconversion mixers. The RF signal is amplified in the power amplifier (PA) and fed to the antenna.

The internal T/R switch circuitry makes the antenna interface and matching easy. The RF connection is differential. A balun may be used for single-ended antennas. The biasing of the PA and LNA is done by connecting TXRX\_SWITCH to RF\_P and RF\_N through an external DC path.

The frequency synthesizer includes a completely on-chip LC VCO and a 90

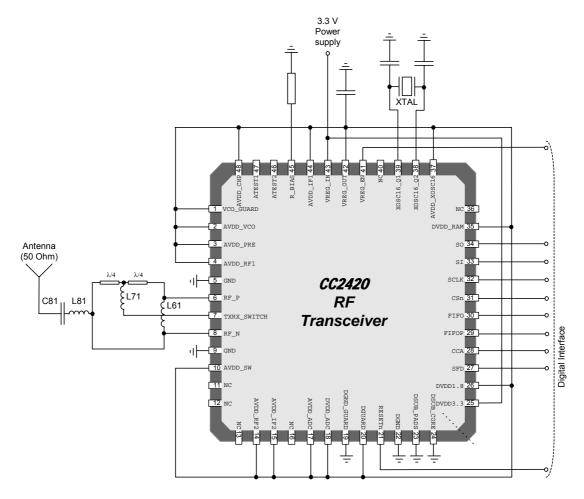

| Ref  | Description                                        |

|------|----------------------------------------------------|

| C42  | Voltage regulator load capacitance                 |

| C61  | Balun and match, see page 55                       |

| C62  | DC block to antenna and match                      |

| C71  | Front-end bias decoupling and match, see page 55   |

| C81  | Balun and match, see page 55                       |

| C381 | 16MHz crystal load capacitor, see page 54          |

| C391 | 16MHz crystal load capacitor, see page 54          |

| L61  | DC bias and match, see page 55                     |

| L62  | DC bias and match, see page 55                     |

| L71  | DC bias and match, see page 55                     |

| L81  | Balun and match, see page 55                       |

| R451 | Precision resistor for current reference generator |

| XTAL | 16MHz crystal, see page 54                         |

Table 1. Overview of external components

Figure 3. Typical application circuit with transmission line balun for single-ended operation