# JukeBlox Networked Media Module CX Series

## **Preliminary Datasheet**

Complete audio networking system on a small module

Integrated Ethernet + USB2.0

WiFi-certified 802.11b/g (optional)

Built-in strip antenna

Optional 2X Diversity Antenna

Glueless audio, video and control ports

FCC certified

Ideal for enabling network and USB audio playback for iPod docks, audio systems, AV Receivers, active speaker systems, internet radios, network playback adaptors

## **Table of Contents**

| 1. Introduction                                                               | 4 |

|-------------------------------------------------------------------------------|---|

| 2. Block Diagram                                                              | 4 |

| 3. Board Pictures                                                             | 5 |

| 3.1 Top View of CX870                                                         | 5 |

| 3.2 Bottom View of CX870                                                      | 5 |

| 4. Ordering Guide                                                             | 6 |

| 5. Electrical Specifications                                                  | 6 |

| 5.1 Absolute Maximum Ratings                                                  | 7 |

| 5.2 Operating Conditions                                                      | 7 |

| 5.3 WiFi Specification (CX870 only)                                           | 7 |

| 6. Regulatory Compliance and Quality                                          | 8 |

| 6.2 Environmental Test                                                        | 9 |

| 6.3 ESD and Transient Test (Applies to LAN and USB external connections only) | 9 |

| 6.4 Magnetic Field Test                                                       | 9 |

| 6.5 MTBF                                                                      | 9 |

| 6.6 Mechanical Specifications                                                 | 9 |

| 6.7 Module Quality                                                            | 9 |

| 7. Board Dimensions and Weight                                                                      | 10                   |

|-----------------------------------------------------------------------------------------------------|----------------------|

| 7.1 Top & Bottom View of CX870 module                                                               | 10                   |

| 7.2 Side View of CX870 module                                                                       | 10                   |

| 7.3 3D View of CX870 module                                                                         | 11                   |

| 7.4 Module weight                                                                                   | 11                   |

| 8. Connectors and Connections                                                                       | 12                   |

| 8.1 WLAN UFL Antenna Connector (optional)<br>8.1.1 Coaxial antenna connector dimensions             | 12<br>12             |

| 8.2 Module Connectors 8.2.1 Pin Descriptions 8.2.2 Connector PIN Assignments 8.2.3 GPIO Assignments | 12<br>13<br>17<br>19 |

| 9. Application Guidelines                                                                           | 19                   |

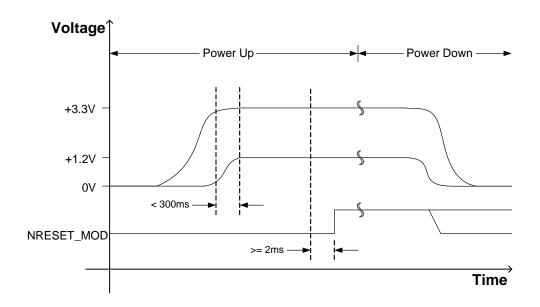

| 9.1 Power Supply sequencing and Reset Timing 9.1.1 Power up, Reset and Power Down Timing            | 19<br>20             |

| 9.2 RF Considerations                                                                               | 20                   |

| 10. Revision Control                                                                                | 21                   |

| Module Revision History                                                                             | 23                   |

| Trademarks                                                                                          | 23                   |

| Warranty Limitations                                                                                | 23                   |

#### 1. Introduction

The CX-series module is a single-board networked media player module, based on BridgeCo's DM860 and DM870 media processors, and enables fast product developments with Ethernet, USB and optional WiFi connectivity. The module connects to standard legacy components in various audio, video/LCD and control formats.

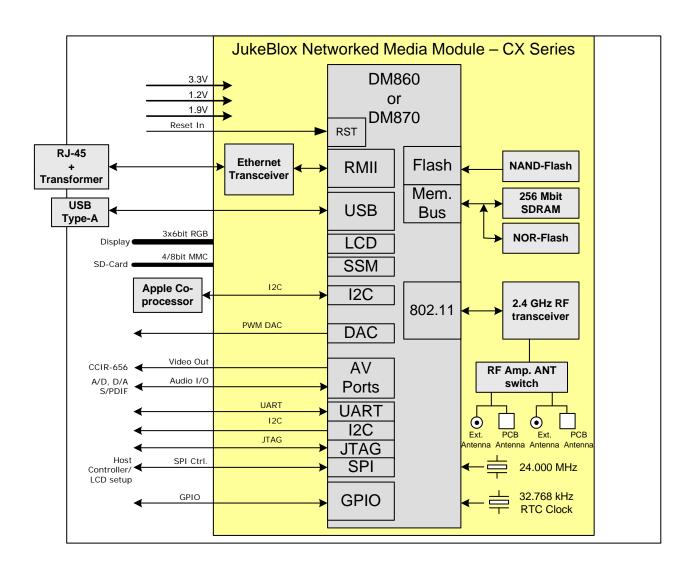

### 2. Block Diagram

Note: Choice of antenna is a build option, see Ordering Guide.

#### 3. Board Pictures

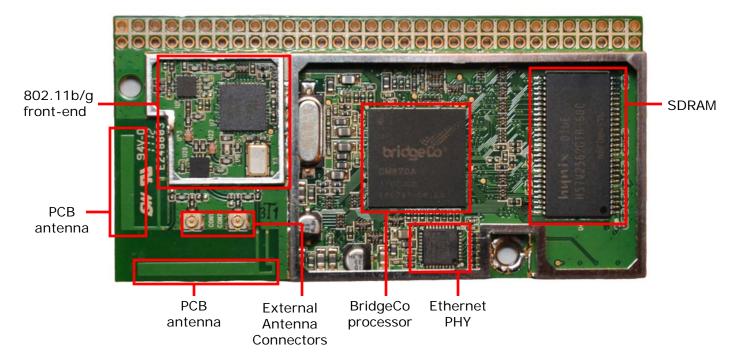

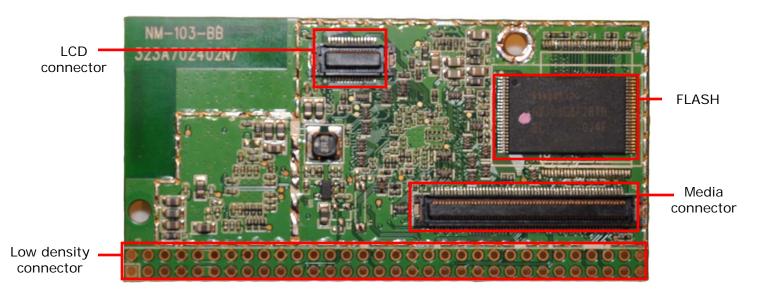

Please note that the below pictures show the prototype version of the layout, and do not include the RF and top shields that will be present on production modules. Pictures of production version modules will be added as soon as possible. Also, please note that the 64-pin connector mounted on the module is the male gender.

#### 3.1 Top View of CX870

#### 3.2 Bottom View of CX870

dat\_CX860\_CX870\_1\_7\_datasheet\_c.doc

PRELIMINARY - CONFIDENTIAL

Version 1.7 – May 13<sup>th</sup> 2011 - Page 5 of 23

## 4. Ordering Guide

| Part<br>Number | BridgeCo IC's | WiFi (on-<br>module<br>PCB<br>diversity) | Ext.<br>Diversity<br>Antennas<br>(UFL Conn.) | Ethernet | USB<br>Host | Low<br>density<br>64-pin<br>Conn. | Media<br>120-pin<br>Conn. | LCD<br>Conn. | 32MByte<br>SDRAM | 16MByte<br>SDRAM | 1Gbit<br>NAND<br>FLASH | 8MByte<br>NOR<br>FLASH | Top<br>Module<br>Shield |

|----------------|---------------|------------------------------------------|----------------------------------------------|----------|-------------|-----------------------------------|---------------------------|--------------|------------------|------------------|------------------------|------------------------|-------------------------|

|                |               |                                          |                                              |          |             |                                   |                           |              |                  |                  |                        |                        |                         |

| CX870-3A       | DM870+T6201   | X                                        | (X)*                                         | X        | Χ           |                                   | X                         | Χ            | X                |                  | X                      |                        | X                       |

| CX870-3B       | DM870+T6201   |                                          | X                                            | X        | Х           | X                                 |                           |              | X                |                  | X                      |                        | X                       |

| CX870-3D       | DM870+T6201   | Х                                        | (X)*                                         | X        | Х           |                                   | X                         |              |                  | X                | Х                      |                        | X                       |

| CX870-3F       | DM870+T6201   | Х                                        |                                              | Х        | Х           | Х                                 |                           |              |                  | X                |                        | X                      | X                       |

| CX870-3G       | DM870+T6201   | Х                                        |                                              |          | Х           | Х                                 |                           |              |                  | X                |                        | X                      | X                       |

| CX870-3H       | DM870+T6201   |                                          | Х                                            | Х        | Х           | Х                                 |                           |              |                  | Х                |                        | Х                      | X                       |

| CX870-3I       | DM870+T6201   |                                          | Х                                            |          | Х           | Х                                 |                           |              |                  | Х                |                        | Х                      | X                       |

| CX870-3J       | DM870+T6201   |                                          | Х                                            |          | Х           |                                   | Х                         |              |                  | X                |                        | X                      | X                       |

|                |               |                                          |                                              |          |             |                                   |                           |              |                  |                  |                        |                        |                         |

**Note:** Please note that the Apple Authentication Coprocessor will not be provided on the CX module. The Apple Authentication Coprocessor should be provided on the product motherboard, connected to the SDA, SCL signals from the CX module.

**Note:** Shaded rows indicate Custom or Obsolete configuration - NOT TO BE USED FOR NEW/STANDARD MP DESIGNS.

## 5. Electrical Specifications

| Parameter                                               | State             | Model | Voltage | Symbol           | min. | typ.  | max.  | Units |

|---------------------------------------------------------|-------------------|-------|---------|------------------|------|-------|-------|-------|

|                                                         |                   |       |         |                  | 3.0  | 3.3   | 3.6   | V     |

| Power Supply Input Voltage                              |                   |       |         | VIN              | 1.08 | 1.2   | 1.32  | V     |

|                                                         |                   |       |         |                  | 1.8  | 1.9   | 2.0   | V     |

| Logic Input high voltage                                |                   |       |         | $V_{IH}$         | 1.7  |       | 5.5   | V     |

| Logic Input low voltage                                 |                   |       |         | $V_{IL}$         | -0.3 |       | 0.7   | V     |

| Logic Input threshold voltage                           |                   |       |         | V <sub>IT</sub>  | 1.29 | 1.39  | 1.5   | V     |

| Schmitt-trigger input low to high threshold voltage     |                   |       |         | V <sub>IT+</sub> | 1.58 | 1.65  | 1.71  | V     |

| Schmitt-trigger input high to low threshold voltage     |                   |       |         | V <sub>IT-</sub> | 0.95 | 1.01  | 1.06  | V     |

| Logic Output high voltage                               |                   |       |         | V <sub>OH</sub>  | 2.4  |       |       | V     |

| Logic Output low voltage                                |                   |       |         | $V_{OL}$         |      |       | 0.4   | V     |

| Logic Low-level output current (V <sub>OL</sub> =0.4V)  |                   |       |         | I <sub>OL</sub>  | -9.6 | -15.6 | -19.3 | mA    |

| Logic High-level output current (V <sub>OH</sub> =2.4V) |                   |       |         | I <sub>OH</sub>  | 11.1 | 22.5  | 35.3  | mA    |

|                                                         | Reset State       |       | 3.3     | 13.3             |      | 60    | 78    | mA    |

|                                                         |                   |       | 1.2     | I1.2             |      | 32    | 42    | mA    |

|                                                         |                   |       | 1.9     | I1.9             |      | 18    | 23    | mA    |

|                                                         | Operating in idle |       | 3.3     | 13.3             |      | 185   | 241   | mA    |

| Current Consumption                                     | state             | CX870 | 1.2     | I1.2             |      | 337   | 438   | mA    |

|                                                         |                   |       | 1.9     | I1.9             |      | 257   | 334   | mA    |

|                                                         | Playback over     |       | 3.3     | 13.3             |      | 240   | 312   | mA    |

|                                                         | WiFi high mips    |       | 1.2     | I1.2             |      | 347   | 451   | mA    |

|                                                         | & rate condition  |       | 1.9     | I1.9             |      | 258   | 335   | mA    |

**Note:** The maximum current values are 30% larger than the typical values. The maximum values are intended to be used for power supply sizing calculations.

dat\_CX860\_CX870\_1\_7\_datasheet\_c.doc

PRELIMINARY - CONFIDENTIAL

Version 1.7 – May 13<sup>th</sup> 2011 - Page 6 of 23

<sup>\*</sup> Connector on board, but requires board modification to enable the connector

## **5.1 Absolute Maximum Ratings**

| Parameter            | Component | Min  | Max | Units |

|----------------------|-----------|------|-----|-------|

| 3.3V Supply Voltage  |           | -0.5 | 4.6 | V     |

| 1.2V Supply Voltage  |           | -0.5 | 1.8 | V     |

| 1.9V Supply Voltage  | Main      | -0.5 | 2.2 | V     |

| Logic Input Voltage  |           | -0.5 | 6   | V     |

| Logic Output Voltage |           | -0.5 | 4.6 | V     |

### 5.2 Operating Conditions

| Parameter                             | Min | Max                 | Units |

|---------------------------------------|-----|---------------------|-------|

| Operating Temperature                 | 0   | +70                 | °C    |

| Operating Humidity                    | 10  | 90 (non condensing) | %RH   |

| Storage Temperature                   | -10 | +75                 | °C    |

| Storage Humidity                      | 10  | 95 (non condensing) | %RH   |

| Storage Temperature Cycle Test 24 hrs | -10 | +75                 | °C    |

## 5.3 WiFi Specification (CX870 only)

| Feature                  | Description                                                  |

|--------------------------|--------------------------------------------------------------|

| WLAN Standards           | IEEE 802.11b                                                 |

|                          | IEEE 802.11g                                                 |

| Frequency Band           | 2.412 - 2.472 GHz (2.4GHz ISM Band, 13 Channels)             |

|                          | Channel 1 - Channel 13                                       |

|                          | North America, Japan Telec, Europe ETSI                      |

| Modulation               | 802.11b mode (DS-SS: IEEE 802.11b)                           |

|                          | 802.11g mode (OFDM: IEEE 802.11g)                            |

| Transmission Speed       | 802.11b mode                                                 |

| ·                        | 11Mbps, 5.5Mbps, 1Mbps                                       |

|                          | 802.11g mode                                                 |

|                          | 54Mbps, 48Mbps, 36Mbps, 24Mbps, 18Mbps, 12Mbps, 9Mbps, 6Mbps |

| Tx Power                 | 802.11b mode (16.5dBm, +/-1dBm)                              |

|                          | 802.11g mode (21dBm, +/-1dBm)                                |

| Power-on Ramp            | < 2us                                                        |

| RF Carrier Suppression   | < 15dBc                                                      |

| TX EVM                   | < -5dB @ 6Mbps                                               |

|                          | < -25dB @ 54Mbps                                             |

| Rx Sensitivity           | 802.11b mode                                                 |

| (incl. CE2 Mother board) | =<-88dBm @ 1Mbps, =<-85dBm @ 5.5Mbps, =<-83dBm @ 11Mbps      |

|                          | 802.11g mode                                                 |

|                          | =<-86dBm @ 6Mbps, =<-75dBm @ 36Mbps, =<-69dBm @ 54Mbps       |

| Throughput Rate          | See factory test specification                               |

| (measured for each       |                                                              |

| module)                  |                                                              |

### 6. Regulatory Compliance and Quality

| Description                   | Country               | Compliance        | Module Versions Passed |

|-------------------------------|-----------------------|-------------------|------------------------|

| Electromagnetic Compatibility | USA                   | FCC CFR47 Part15B |                        |

| (Prescan)                     | Europe                | EN 55022          |                        |

|                               |                       | EN 55024          |                        |

|                               |                       | EN 61000-3-2      |                        |

|                               |                       | EN 61000-3-3      |                        |

|                               |                       | EN 61000-4-2      |                        |

|                               |                       | EN 61000-4-3      |                        |

|                               |                       | EN 61000-4-4      |                        |

|                               |                       | EN 61000-4-5      |                        |

|                               |                       | EN 61000-4-6      |                        |

|                               |                       | EN 61000-4-8      |                        |

|                               |                       | EN 61000-4-11     |                        |

| Radio Regulations (CX870      | USA                   | FCC Part 15C      | tbd                    |

| only)                         | Japan                 | Telec             | tbd                    |

|                               | Canada                | IC RSS-210        | tbd                    |

|                               | Europe                | CE                | tbd                    |

|                               | New Zealand/Australia | CE                | tbd                    |

|                               | China                 | SRRC              | tbd                    |

|                               | Korea                 | KCC               | tbd                    |

**Note:** BridgeCo does not certify all module variants for all countries. Please contact your BridgeCo sales office for the latest information about which modules are certified for which countries, and arranging for additional certification for your chosen module if needed. Product manufacturers are responsible for the end product certification.

BridgeCo can help manufacturers to prepare for the WiFi Alliance tests by providing an example test plan and the required commands to enable special test modes. Please contact your BridgeCo sales office about WiFi Alliance logo certification assistance.

#### **6.1 RoHS**

Uses only RoHS compliant components

#### 6.2 Environmental Test

Withstands 4 hours at 70°C, 90% RH

## 6.3 ESD and Transient Test (Applies to LAN and USB external connections only)

ESD: +/- 2kV operation, +/- 4kV no destruction (part of CE test)

Fast electrical transients: +/- 500V operation, +/- 1000V no destruction (part of CE test)

#### 6.4 Magnetic Field Test

Passes EN55022 and EN55024 (part of CE test)

#### **6.5 MTBF**

>10000 hours

#### 6.6 Mechanical Specifications

Passes drop test according to I.E.C. 68-2-32, height 100 cm, 1 corner, 6 faces. Passes vibration test with sine, vertical, 60 minutes, 600 to 18000 cpm, 1G

### 6.7 Module Quality

Defect Rate: TBD

AQL CR=0, MA=0.4, MI=0.4

## 7. Board Dimensions and Weight

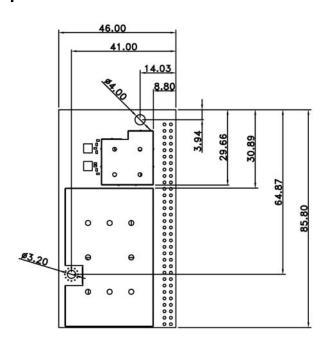

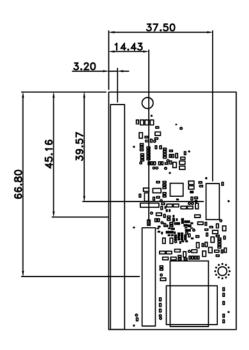

#### 7.1 Top & Bottom View of CX870 module

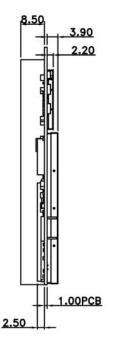

#### 7.2 Side View of CX870 module

#### Note:

- 1. All dimensions are measured in **millimetres** (mm).

- 2. PCB's thickness: 1.00 +/- 0.10mm

- 3. Tolerance: +/-0.10mm

- 4. Outline Tolerance: +/-0.10mm

- 5. NPTH Hole: +/-0.05mm

- 6. PTH Hole: +/-0.075mm

- Connector positions, board dimensions, mounting hole positions and sizes are the same for all module variants.

- 8. Connector position tolerance: +/- 0.38mm

- The 64-pin connector mounted on the module along one edge is the male gender.

- Not all module variants have all connectors. Please see the Ordering Guide table for details of connector options.

dat\_CX860\_CX870\_1\_7\_datasheet\_c.doc

PRELIMINARY - CONFIDENTIAL

Version 1.7 - May 13th 2011 - Page 10 of 23

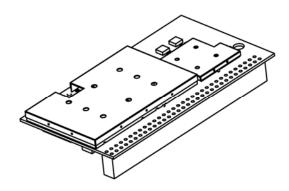

#### 7.3 3D View of CX870 module

### 7.4 Module weight

CX860: 14g CX870: 15g

**Note:** Module weight applies to all versions of the module.

#### 8. Connectors and Connections

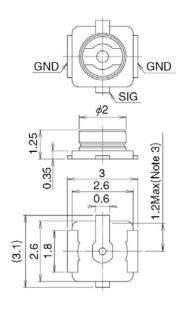

#### 8.1 WLAN UFL Antenna Connector (optional)

The module includes two PCB strip antennas operated in diversity mode. Alternatively, two coaxial antenna connectors are provided for connecting external (to the module) antennas. The choice between using the strip antenna or using the coaxial sockets is a build option, determined by the position of surface mount capacitors on the module PCB. If the PCB antennas are chosen, then diversity mode is always used. If external (to the module) antenna sockets are used, then either one or two external antennae may be connected. Using two antennae is preferred since this provides 2X diversity operation. Please see ordering guide for build option details.

The surface-mount receptacle parts:

Hirose

U.FL-R-SMT (CL No. 331-0471-0)

#### 8.1.1 Coaxial antenna connector dimensions

#### 8.2 Module Connectors

The CX860/870 module uses 3 board-to-board connectors as interfaces to the product main board. The part numbers for the connectors needed on the product main board, which mate with the connectors on the CX module, are shown in the table below.

| Connector | Connector   | Connector | Number  | Pin             | Mating Connector Part          |

|-----------|-------------|-----------|---------|-----------------|--------------------------------|

| Number    | Purpose     | Туре      | of Pins | Configuration   | Numbers                        |

| J1        | LCD         | B2B       | 30      | 2 x 15 x 0.5mm  | 14-5046-030-145-829+ (Kyocera) |

| J2        | Media       | Connector | 120     | 2 x 60 x 0.5mm  | 14-5046-120-145-829+ (Kyocera) |

| J3        | Low Density | Connector | 64      | 2 x 32 x 2.54mm | CSHA201-3202A001A1AB           |

dat\_CX860\_CX870\_1\_7\_datasheet\_c.doc

PRELIMINARY - CONFIDENTIAL

Version 1.7 - May 13th 2011 - Page 12 of 23

The pinout and signal names are shown on the next page. The following table provides an overview for the most important control and interface signals.

#### 8.2.1 Pin Descriptions

| Signal(s)   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER       |      |                                                                                                                                                                                                                                                                                                                                                                               |

| VIN(+3.3V)  | Р    | Power supply input; +3.3V.                                                                                                                                                                                                                                                                                                                                                    |

| VIN (+1.2V) | P    | Power supply input ; +1.2V.                                                                                                                                                                                                                                                                                                                                                   |

| VIN (+1.2V) | P    | Power Supply input; +1.9V for powering RF section. Make sure this is a clean supply.                                                                                                                                                                                                                                                                                          |

| 3V3RTC      | P    | For module versions without Real Time Clock (RTC) option, and for module versions with                                                                                                                                                                                                                                                                                        |

|             |      | RTC option where the RTC function is not used, this pin should be left open. For module versions with RTC option, and the RTC function is used, then this pin should be connected                                                                                                                                                                                             |

|             |      | to the positive terminal of a 1F capacitor connected to GND. This capacitor will power the                                                                                                                                                                                                                                                                                    |

|             |      | RTC circuits in the DM870 IC when the module power supply is switched off.                                                                                                                                                                                                                                                                                                    |

| GND         | P    | Ground (GND) connection for power supply 0V, signal returns and shielding.                                                                                                                                                                                                                                                                                                    |

| GND         | l P  | Ground (GND) connection for power supply ov, signal returns and shielding.                                                                                                                                                                                                                                                                                                    |

| SPI         |      |                                                                                                                                                                                                                                                                                                                                                                               |

| SPI_DOUT    | 0    | SPI data from DM870 to host controller.                                                                                                                                                                                                                                                                                                                                       |

| SPI_DIN     | I    | SPI data from host controller to DM870.                                                                                                                                                                                                                                                                                                                                       |

| SPI_CLK     | I    | SPI clock from host controller to DM870. Maximum recommended frequency is 2MHz,                                                                                                                                                                                                                                                                                               |

|             |      | typical frequency is 1MHz. See Note 2 below.                                                                                                                                                                                                                                                                                                                                  |

| SPI_NCS0    | I    | SPI chip select from host controller to DM870.                                                                                                                                                                                                                                                                                                                                |

| PDOUT1      | 0    | This signal is used as SPI_REQ, SPI request signal, from DM870 to host controller for eDMP applications. Logic 1 indicates that there is an SPI message waiting to be read, the host controller should start the SPI clock and read any changed registers. Logic 0 indicates that all changed register messages have been read and the message buffer is empty. Also GPIO-06. |

| SPI_NCS1    | I    | Not used. Leave open.                                                                                                                                                                                                                                                                                                                                                         |

| UART        |      |                                                                                                                                                                                                                                                                                                                                                                               |

| RXD1        | I    | UART1 input to the DM870, used for shell access. BridgeCo recommends providing a connection to an external RS-232 transceiver and DB9 connector to connect to a PC COM port. Such a connection can be used for product development debugging, and for module programming control on the product manufacturing line and for module control during certification procedures.    |

| TXD1        | 0    | UART1 output from the DM870, used for shell access. BridgeCo recommends providing a connection to an external RS-232 transceiver and DB9 connector to connect to a PC COM port. Such a connection can be used for product development debugging, and for module programming control on the product manufacturing line and for module control during certification procedures. |

| RXD0        | I    | UARTO input. Optionally used for controlling an iPod via UART.                                                                                                                                                                                                                                                                                                                |

| TXD0        | 0    | UARTO output. Optionally used for controlling an iPod via UART.                                                                                                                                                                                                                                                                                                               |

#### AUDIO

| AUDIU                           |   |                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AV2DATA0                        | 0 | I2S or left justified audio data output. Typically connected to external D/A converter input or to external DSP for further audio processing. Used for main left and right channel audio output data. See Note 3.                                                                                                                           |

| AV2CTRL0                        | 0 | LRCK, audio data word clock at the audio sample rate (Fs). Maximum currently supported frequency is 192kHz.                                                                                                                                                                                                                                 |

| AV2CTRL1                        | 0 | MCLK, audio master clock at 256Fs. This can be used to clock an external D/A converter or DSP.                                                                                                                                                                                                                                              |

| AV2CLK                          | 0 | SCLK, audio data bit clock at 64Fs. Allows for up to 32 audio data bits per sample word.                                                                                                                                                                                                                                                    |

| AV4DATA1                        | 0 | SPDIF format output. Can support samples rates up to 192kHz, so the maximum instantaneous frequency on this pin is 24.576MHz.                                                                                                                                                                                                               |

| AV4DATA0                        | I | SPDIF input. Not used at present. Leave open.                                                                                                                                                                                                                                                                                               |

| AV2DATA1                        | 0 | I2S or left justified audio data output. Not used at present. Leave open.                                                                                                                                                                                                                                                                   |

| AOUTLP/AOUTLN,<br>AOUTRP/AOUTRN | 0 | Differential stereo output from PWM-DAC, right and left channels. These signals require analog low pass filtering. BridgeCo is not recommending using the PWM-DAC outputs because of the potential for high out-of-band noise and uncharacterized audio quality. BridgeCo recommends using an external D/A converter connected to AV2DATAO. |

| AV2DATA2                        | I | I2S or left justified audio data input. Can be driven from an optional external A/D converter used to interface to iPod analog output or other analog audio sources. If not used, leave open.                                                                                                                                               |

| AV2DATA3                        | I | 12S or left justified audio data input. Not used at present. Leave open.                                                                                                                                                                                                                                                                    |

#### CONTROL

| CONTROL            |     |                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NCS3               | I   | BIST activate. Low-active input to invoke the Built In Self Test (BIST) function. This only applies to factory fresh modules. After JB2 firmware is loaded, this signal becomes GPIO-17 and is currently not used. DM870-internal pull-up. Leave this pin open.                                                                                                        |

| PDOUTO             | I   | Factory Reset. GPIO-04. Return the CnE to factory settings. High-active input, DM870-internal pull-down. Pull to GND with a 10kohm resistor, unless return to factory settings from a hardware control is needed. Normally, return to factory settings is controlled from the host controller via SPI register. This pin is only monitored during the boot up process. |

| VCO0               | 1   | Infrared sensor input. GPIO-05. This is a Schmitt-Trigger input and can handle inputs with slow slopes. Used for aDMP firmware builds for infrared remote control sensor output connection to DM870. For applications with a host controller, pull this pin to +3.3V via a 10kohm resistor.                                                                            |

| AV3CLK             | 0   | ETH_NRESET Low-active reset for the on-board ethernet PHY. This output is driven by the DM870. GPIO-12. Leave this pin open.                                                                                                                                                                                                                                           |

| AV3CTRL0, AV3CTRL1 | I/O | I2C_SCL, I2C_SDA bus created by GPIO-13 and GPIO-14.  No internal pull-ups; Use 4.7kohm pull up resistor on each pin to +3.3V. Maximum frequency is 400kHz.                                                                                                                                                                                                            |

| NRESET_MOD         | 1   | Low-active input to reset the module. This signal must be driven by an external reset generator, or by a GPIO output from a host controller. See the application section of this data sheet for the timing requirements for NRESET_MOD. Includes internal 10K pull-up resistor to +3.3V.                                                                               |

| NPD_RF             | I   | Active low input to shut down the power for the 802.11 RF section. Internal 10kohm pull-up resistor to +3.3V. Leave open if powering down the RF section is not required.                                                                                                                                                                                              |

#### ETHERNET

| ETH_RXN, ETH_RXP,<br>ETH_TXN, ETH_TXP | М | Ethernet signals between the PHY on the module and the external magnetics (transformer). See Note 4. Maximum bit rate is 100Mbps.                                                 |

|---------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ETH_LED_SPEED,<br>ETH_LED_ACT         | 0 | 3.3V push-pull outputs (max. ±12mA) to drive the ethernet LEDs. 100Mbps speed mode and activity are indicated by the outputs being low. Connect to LEDs through 220ohm resistors. |

| 030            |   |                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|----------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| USB_DN, USB_DP | М | USB data signals, normally connected to type A connector, USB switch or iPod dock connector. Maximum bit rate is USB High Speed at 480Mbps.                                                                                                                                                                                     |  |  |  |  |  |  |  |

| USB_VBUS       | M | Analog input for monitoring USB type A connector power. Connect to the +5V power which is driving the USB type A connector power pins. If this pin drops below 4.6V, then the DM870 will drive the USBVBUSDRV signal low to control an external power MOSFET to disconnect +5V power from the USB type A connector. See Note 5. |  |  |  |  |  |  |  |

| USBVBUSDRV     | 0 | Logic output to control an external MOSFET that is in series with USB type A connector power. See USB_VBUS above and Note 5.                                                                                                                                                                                                    |  |  |  |  |  |  |  |

#### ΙΤΔα

| JIAG             |     |                                  |

|------------------|-----|----------------------------------|

| TMS,TCK,TDI, TDO | 1/0 | JTAG port for DM870. Leave open. |

#### SSM

| JUIN                                                              |     |                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSMD4, SSMD5,<br>SSMD6, SSMD7                                     | 1/0 | Can be used to drive external shift registers to make extended GPIO signals (see Note 6), or as individual GPIO signals, or to make an SD card interface. SD card firmware is not supported at present in JB2. Can be mapped to GPIO #s 08,09,10,11. Leave open if not used. |

| SSMD0, SSMD1,<br>SSMD2, SSMD3,<br>SSMCLK, SSMCP,<br>SSMCMD, SSMWP | 1/0 | Used to make an SD card interface. SD card firmware is not supported at present in JB2. Leave open.                                                                                                                                                                          |

#### **VIDEO**

| 1100                |   |                                                                                          |

|---------------------|---|------------------------------------------------------------------------------------------|

| AVOCLK, AVOCTRLO,   | 0 | ITU-R BT.656 digital video output signals. Optionally used to make a TVout menu display, |

| AVOCTRL1, AVOCTRL2, |   | or to display decoded album art. Can be connected to video D/A converter (see Note 7),   |

| AVODATAO, AVODATA1, |   | or connected to a video DSP.                                                             |

| AVODATA2, AVODATA3, |   |                                                                                          |

| AV1DATAO, AV1DATA1, |   |                                                                                          |

| AV1DATA2, AV1DATA3  |   |                                                                                          |

## GPIO (not already mentioned elsewhere in this table)

| A22      | 0   | GPIO18 Reserved for NOR flash address A22. Leave open.            |

|----------|-----|-------------------------------------------------------------------|

| A23      | 0   | GPIO-16 Reserved for NOR flash address A23. Leave open.           |

| NWAIT    | 1/0 | GPIO-15 Not currently assigned. Leave open.                       |

| NCS2     | 1   | GPIO-19 Assigned to iPod dock connector iPod NDETECT. See Note 8. |

| VCO1     | 1/0 | GPIO-07 Not currently assigned. Leave open.                       |

| MMIICRS  | 1/0 | GPIO-00 Not currently assigned. Leave open.                       |

| MIICOL   | 1/0 | GPIO-01 Not currently assigned. Leave open.                       |

| MIITXER  | 1/0 | GPIO-02 Not currently assigned. Leave open.                       |

| MIITXCLK | 1/0 | GPIO-03 iPod dock connector Accessory Power signal. See Note 8.   |

#### MII

| MIITXD0, MIITXD1, | 1/0 | Can be used, with GPIO signals above, to drive an external ethernet PHY. This is not |

|-------------------|-----|--------------------------------------------------------------------------------------|

| MIIRXD0, MIIRXD1  |     | supported by JB2 firmware. Leave open.                                               |

#### LCD

| LCDD0, LCDD1,       | 0 | Uses optional J1 LCD connector. Connect to local LCD display. See Note 9. Leave open if |

|---------------------|---|-----------------------------------------------------------------------------------------|

| LCDD2, LCDD3,       |   | not used.                                                                               |

| LCDD4, LCDD5,       |   |                                                                                         |

| LCDD6, LCDD7,       |   |                                                                                         |

| LCDD8, LCDD9,       |   |                                                                                         |

| LCDD10, LCDD11,     |   |                                                                                         |

| LCDD12, LCDD13,     |   |                                                                                         |

| LCDD14, LCDD15,     |   |                                                                                         |

| LCD16, LCDD17,      |   |                                                                                         |

| LCDCLK, LCDCTRLO,   |   |                                                                                         |

| LCDCTRL1, LCDCTRL2, |   |                                                                                         |

| LCDCTRL3            |   |                                                                                         |

dat\_CX860\_CX870\_1\_7\_datasheet\_c.doc

PRELIMINARY - CONFIDENTIAL

Version 1.7 – May 13<sup>th</sup> 2011 - Page 15 of 23

#### Notes:

- 1. Signal type codes:

- I 3.3V level Digital Logic Input into the DM870

- O 3.3V level Digital Logic Output from the DM870

- IO 3.3V level Digital Logic Input and Output (bi-directional) signal

- M Miscellaneous, see text for description

- P Power Supply

- 2. For SPI timing diagram for eDMP applications, please see:

BridgeCo\_JB2x - DeviceControlProtocol\_Registers\_v\_2\_1.pdf, or later version.

For detailed setup and hold timing details, see DM870 IC data sheet:

dat\_DM870\_16\_datasheet.pdf, or later version.

- 3. For audio port timing diagrams, and for detailed setup and hold timing, please see DM870 IC data sheet: dat\_DM870\_16\_datasheet.pdf, or later version.

- For example ethernet external schematic, see: CX Module Ethernet (RJ45 + Ext.Magnetics)\_V1.2.pdf, or later version.

- 5. For example USB schematics, see: *CX Module USB\_V1.2.pdf*, or later version.

- 6. For example use of extended GPIO shift registers, see CE2 schematic: A EVMCE2-4\_schematic.pdf, or later version.

- 7. For example connection to a video D/A converter, see CE2 schematic: A EVMCE2-4\_schematic.pdf, or later version.

- 8. iPod dock connector pin and GPIO assignments are under discussion. Please contact BridgeCo for recommendations for iPod dock connections to CX870 module.

- 9. For example connection to an LCD display, see CE2 schematic: A EVMCE2-4\_schematic.pdf, or later version.

- 10. All the above signals are brought out to J2 pins. Not all the above signals are brought out to J3, the 64-pin low density connector. The J3 pin assignments table shows which signals are brought out to the J3 pins.

- 11. BridgeCo has a set of example motherboard schematics that shows example external circuitry that is typically connected to the module. Please check the BridgeCo customer portal for a copy of these example schematics.

- 12. Please check the BridgeCo Customer Portal *Download* area for the latest version of the BridgeCo documents. Go to <u>bridgeco.com</u>, click on Client Login button. If you do not have an account, please contact BridgeCo.

#### 8.2.2 Connector PIN Assignments

#### J2 - Media Connector

| Function                                       | GPIO                          | IC PIN                                 | Signal                                                                        | PIN Number                                    |   | Signal                                        | IC PIN | GPIO                                                                          | Function                               |                                          |                                              |

|------------------------------------------------|-------------------------------|----------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------|---|-----------------------------------------------|--------|-------------------------------------------------------------------------------|----------------------------------------|------------------------------------------|----------------------------------------------|

|                                                |                               |                                        | GND<br>VIN (+3.3V)<br>VIN (+3.3V)<br>GND<br>VIN (+1.2V)<br>VIN (+1.2V)<br>GND | 1<br>3<br>5<br>7<br>9<br>11                   |   | 2<br>4<br>6<br>8<br>10<br>12                  |        | GND<br>VIN (+3.3V)<br>VIN (+3.3V)<br>GND<br>VIN (+1.2V)<br>VIN (+1.2V)<br>GND |                                        |                                          |                                              |

|                                                |                               | F4                                     | VIN (+1.9V)<br>GND<br>3V3RTC<br>GND                                           | 15<br>17<br>19<br>21                          |   | 16<br>18<br>20<br>22                          |        | VIN (+1.9V)<br>GND<br>GND<br>TMS                                              | B20                                    |                                          |                                              |

| SPI                                            |                               | E17<br>F17<br>D17                      | GND<br>SPI_DOUT<br>SPI_DIN<br>SPI_CLK                                         | 23<br>25<br>27<br>29                          | E | 24<br>26<br>28<br>30                          |        | TCK<br>TDI<br>TDO<br>SPI_NCS0                                                 | A20<br>B19<br>A19<br>D16               |                                          | JTAG<br>SPI                                  |

| Debug UAF                                      | RT                            | C17<br>A18<br>B17<br>A17               | TXD0<br>RXD0<br>RXD1<br>TXD1                                                  | 31<br>33<br>35<br>37                          |   | 32<br>34<br>36<br>38                          |        | SPI_NCS1<br>NRESET_MOD<br>SSMD6<br>SSMD4                                      | D15<br>B16<br>C15                      |                                          | Module reset input<br>SPI_E_CLK<br>SPI_E_SDO |

| SPI_E_NCS<br>SPI_E_SDI                         | GPIO-11<br>GPIO-09            | C16<br>A16<br>B15<br>B14<br>C13<br>C12 | GND<br>SSMD7<br>SSMD5<br>SSMD3<br>SSMD0<br>SSMCLK<br>SSMCP<br>GND             | 39<br>41<br>43<br>45<br>47<br>49<br>51<br>53  |   | 40<br>42<br>44<br>46<br>48<br>50<br>52<br>54  |        | SSMD2<br>SSMD1<br>SSMCMD<br>SSMWP<br>NCS3<br>NCS2<br>GND<br>USB_VBUS          | A15<br>C14<br>A14<br>C11<br>M18<br>L18 |                                          | BIST activate iPod NDETECT USB               |

| USB                                            |                               | A1<br>B1                               | USB_DN<br>USB_DP<br>USBVBUSDRV                                                | 55<br>57<br>59                                |   | 56<br>58<br>60                                |        | GND<br>AOUTRN<br>AOUTRP                                                       | K2<br>J2                               |                                          | USB                                          |

|                                                | GPIO-16                       | H3<br>J3<br>K20                        | GND<br>AOUTLP<br>AOUTLN<br>GND<br>A23                                         | 61<br>63<br>65<br>67<br>69                    |   | 62<br>64<br>66<br>68<br>70                    |        | GND<br>PDOUT1<br>VCO1<br>PDOUT0<br>VCO0                                       | L1<br>L2<br>M1<br>M2                   | GPIO-07                                  | SPI_REQ Factory reset                        |

| I2C SDA<br>I2C SCL                             | GPIO-18<br>GPIO-14<br>GPIO-13 | K19<br>V1<br>V2<br>K3                  | A22<br>AV3CTRL1<br>AV3CTRL0<br>AV0CTRL2                                       | 71<br>73<br>75<br>77                          | E | 72<br>74<br>76<br>78                          |        | AV3CLK<br>AV0CTRL0<br>AV1DATA3<br>AV1DATA2                                    | U3<br>M3<br>P3<br>R1                   | GPIO-12                                  | ETH NRESET                                   |

| Video Outp                                     | ut                            | L3<br>N1<br>N2                         | AV0CTRL1<br>AV0CLK<br>AV0DATA3                                                | 79<br>81<br>83                                |   | 80<br>82<br>84                                |        | AV1DATA2<br>AV1DATA1<br>AV1DATA0<br>GND<br>AV2CTRL1                           | R2<br>R3                               |                                          | /ideo Output                                 |

| L DOV                                          |                               | N3<br>P1<br>P2                         | AVODATA2<br>AVODATA1<br>AVODATA0<br>GND                                       | 85<br>87<br>89<br>91                          |   | 86<br>88<br>90<br>92                          |        | GND<br>AV2CLK<br>GND                                                          | R4                                     |                                          | SCLK                                         |

| LRCK<br>A/D data 1<br>A/D data 0<br>D/A data 1 |                               | T2<br>T3<br>T4<br>U1                   | AV2CTRL0<br>AV2DATA3<br>AV2DATA2<br>AV2DATA1                                  | 93<br>95<br>97<br>99                          |   | 94<br>96<br>98<br>100                         |        | AV4DATA1<br>AV4DATA0<br>GND<br>ETH_LED_ACT                                    | W2<br>Y1                               |                                          | SPDIF output SPDIF input  Ethernet           |

| D/A data 0  Ethernet                           |                               | U2                                     | AV2DATA0<br>GND<br>ETH_RXN<br>ETH_RXP<br>ETH_TXN<br>ETH_TXN                   | 101<br>103<br>105<br>107<br>109<br>111<br>113 |   | 102<br>104<br>106<br>108<br>110<br>112<br>114 |        | ETH_LED_SPEED MICRS MIICOL MITXER MITXCLK MITXD0 MIITXD1                      | Y14<br>W14<br>V10<br>V11<br>W10<br>Y10 | GPIO-00<br>GPIO-01<br>GPIO-02<br>GPIO-03 | iPod Access Power                            |

|                                                | GPIO-15                       | N18                                    | GND<br>NWAIT<br>NPD_RF                                                        | 115<br>117<br>119                             |   | 116<br>118<br>120                             |        | MIIRXD0<br>MIIRXD1<br>GND                                                     | W12<br>Y12                             |                                          |                                              |

**Note:** The IC PIN column indicates the pin number on the DM860 or DM870 integrated circuit. This allows for easy cross-reference to the DM860 or DM870 data sheet information.

dat\_CX860\_CX870\_1\_7\_datasheet\_c.doc

PRELIMINARY - CONFIDENTIAL

Version 1.7 – May 13<sup>th</sup> 2011 - Page 17 of 23

#### J1 - LCD Connector

| Function  | GPIO | IC PIN | Signal   | PIN N | Number |    | Signal   | IC PIN | GPIO | Function    |

|-----------|------|--------|----------|-------|--------|----|----------|--------|------|-------------|

|           |      |        |          |       |        |    |          |        |      |             |

|           |      |        | GND      | 1     |        | 2  | GND      |        |      |             |

|           |      | Y7     | LCDD0    | 3     |        | 4  | LCDD1    | W7     |      |             |

|           |      | V7     | LCDD2    | 5     |        | 6  | LCDD3    | Y6     |      |             |

|           |      | W6     | LCDD4    | 7     |        | 8  | LCDD5    | V6     |      |             |

|           |      | U6     | LCDD6    | 9     |        | 10 | LCDD7    | Y5     |      |             |

| LCD Inter | face | W5     | LCDD8    | 11    |        | 12 | LCDD9    | V5     | LCI  | ) Interface |

|           |      | U5     | LCDD10   | 13    |        | 14 | LCDD11   | Y4     |      |             |

|           |      | W4     | LCDD12   | 15    |        | 16 | LCDD13   | V4     |      |             |

|           |      | U4     | LCDD14   | 17    |        | 18 | LCDD15   | Y3     |      |             |

|           |      | W3     | LCDD16   | 19    |        | 20 | LCDD17   | Y2     |      |             |

|           |      |        | GND      | 21    |        | 22 | GND      |        |      |             |

|           |      | Y9     | LCDCLK   | 23    |        | 24 | LCDCTRL0 | W9     | 1.01 | ) Interface |

| LCD Inter | face | Y8     | LCDCTRL1 | 25    |        | 26 | LCDCTRL2 | W8     | LCI  | interrace   |

|           |      | V8     | LCDCTRL3 | 27    |        | 28 | GND      |        |      |             |

|           |      |        | GND      | 29    |        | 30 | GND      |        |      |             |

**Note:** The IC PIN column indicates the pin number on the DM860 or DM870 integrated circuit. This allows for easy cross-reference to the DM860 or DM870 data sheet information.

#### J3 - Low Density Connector

| Function                                     | ction   GPIO   IC PIN   Signal           |                          | PIN N                                                                                | umber                                                           | Signal                                                           | IC | PIN                                                                         | GPIO   | Function               |                                         |                                  |

|----------------------------------------------|------------------------------------------|--------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------|----|-----------------------------------------------------------------------------|--------|------------------------|-----------------------------------------|----------------------------------|

| Free<br>iPod NDETECT                         | GPIO-15<br>GPIO-19                       | N18<br>L18<br>F4         | GND VIN (+3.3) VIN (+3.3) GND VIN (+1.9) VIN (+1.9) GND NWAIT NCS2 NRESET 3V3RTC GND | 1<br>3<br>5<br>7<br>9<br>11<br>13<br>15<br>17<br>19<br>21<br>23 | 2<br>4<br>6<br>8<br>10<br>12<br>14<br>16<br>18<br>20<br>22<br>24 |    | GND RXD0 TXD0 GND VIN (+1.2) VIN (+1.2) GND RXD1 TXD1 GND AV2CTRL1 AV2CTRL0 | A      | 317<br>λ17<br>Γ1<br>Γ2 | ı                                       | Debug UART  MCLK LRCK            |

| SPI                                          |                                          | F17<br>E17<br>D17<br>D16 | SPI_DIN<br>SPI_DOUT<br>SPI_CLK<br>SPI_NCS0                                           | 25<br>27<br>29<br>31                                            | 26<br>28<br>30<br>32                                             |    | AV2CLK<br>AV2DATA2<br>AV2DATA0<br>AV4DATA1                                  | l<br>V | R4<br>T4<br>J2<br>V2   | SCLK A/D data 0 D/A data 0 SPDIF output |                                  |

| Free<br>E-GPIO_NCS/TBA<br>I2C SDA<br>I2C SCL | GPIO-17<br>GPIO-11<br>GPIO-14<br>GPIO-13 | D15<br>C16<br>V1<br>V2   | NCS3<br>GND<br>SSMD7<br>AV3CTRL1<br>AV3CTRL0<br>GND                                  | 33<br>35<br>37<br>39<br>41<br>43                                | 34<br>36<br>38<br>40<br>42<br>44                                 |    | AV4DATA0<br>GND<br>USB_DN<br>USB_DP<br>USBVBUSDRV<br>USB_VBUS               | A      | Y1<br>A1<br>B1         |                                         | SPDIF input  USB                 |

| SPI_REQ<br>Factory Reset<br>IR input         | GPIO-06<br>GPIO-04<br>GPIO-05            | L1<br>M1<br>M2           | PDOUT1<br>PDOUT0<br>VCO0<br>GND                                                      | 45<br>47<br>49<br>51                                            | 46<br>48<br>50<br>52                                             |    | GND<br>SSMD5<br>SSMD4<br>GND                                                |        | (20<br>(15             |                                         | E-GPIO_SDI/TBA<br>E-GPIO_SDO/TBA |

| Ethernet                                     |                                          |                          | ETH_LED_SPEED                                                                        | 53                                                              | 54                                                               |    | ETH_LED_ACT                                                                 |        |                        |                                         | Ethernet                         |

| iPod Access Power<br>Ethernet                | GPIO-03                                  | V11                      | MIITXCLK<br>ETH_RXN<br>ETH_TXN                                                       | 55<br>57<br>59                                                  | 56<br>58<br>60                                                   |    | SSMD6<br>ETH_RXP<br>ETH_TXP                                                 | В      | 316                    | GPIO-10                                 | E-GPIO_CLK/TBA  Ethernet         |

| Free                                         | GPIO-00                                  |                          | MMIICRS<br>GND                                                                       | 61<br>63                                                        | 62<br>64                                                         |    | MIICOL<br>GND                                                               |        |                        | GPIO-01                                 | Free                             |

**Note:** The IC PIN column indicates the pin number on the DM860 or DM870 integrated circuit. This allows for easy cross-reference to the DM860 or DM870 data sheet information.

dat\_CX860\_CX870\_1\_7\_datasheet\_c.doc

PRELIMINARY - CONFIDENTIAL

Version 1.7 – May 13<sup>th</sup> 2011 - Page 18 of 23

#### 8.2.3 GPIO Assignments

#### **GPIO Assignments for J3 64-pin Low Density Connector**

| GPIO | PIN Name | PIN Number | Function                         |  |

|------|----------|------------|----------------------------------|--|

| 00   | MMIICRS  | 61         | Free                             |  |

| 01   | MIICOL   | 62         | Free                             |  |

| 03   | MIITXCLK | 55         | iPOD Access Power                |  |

| 04   | PDOUT0   | 47         | Factory Reset                    |  |

| 05   | VCO0     | 49         | IR Input                         |  |

| 06   | PDOUT1   | 45         | Host NIREQ                       |  |

| 08   | SSMD4    | 50         | E_GPIO_SDO/TBA                   |  |

| 09   | SSMD5    | 48         | E_GPIO_SDI/TBA<br>E_GPIO_CLK/TBA |  |

| 10   | SSMD6    | 56         |                                  |  |

| 11   | SSMD7    | 37         | E_GPIO_NCS/TBA                   |  |

| 13   | AV3CTRL0 | 41         | I2C_SCL                          |  |

| 14   | AV3CTRL1 | 39         | I2C_SDA                          |  |

| 15   | NWAIT    | 15         | Free                             |  |

| 17   | NCS3     | 33         | Free                             |  |

| 19   | NCS2     | 17         | IPOD NDETECT                     |  |

Note: Not all 20 GPIO signals are brought out to J3 64-pin low density connector.

### 9. Application Guidelines

### 9.1 Power Supply sequencing and Reset Timing

There are strict power sequencing and reset timing requirements.

- Power up the I/O voltage (3.3V) first and hold NRESET\_MOD low.

- The core voltage (1.2V) must never be higher than (I/O voltage +0.5 V).

- The core voltage (1.2V) must be within the specified core voltage limits less than 300ms after the I/O voltage (3.3V) reaches the specified I/O voltage limits.

- Throughout the power down process, the 3.3V supply must maintain a higher voltage than the 1.2V supply, until both have reached ground potential.

- To assure a proper IC reset, the power supplies must be present for a minimum time of 2ms before NRESET\_MOD is de-asserted.

Please see the power and reset timing figure in Section 9.1.1 below.

About 1.9V, the arrival of 1.9V supply should lag behind the arrival of the 3.3V. The delay between the 1.9V and the 3.3V is not critical. Typical delay is approximately 10ms, for example using 10kohm resistor and 0.1uF capacitor on the enable pin of a 1.9V dc-to-dc converter.

#### 9.1.1 Power up, Reset and Power Down Timing

#### 9.2 RF Considerations

Note that overall system, RF and WiFi performance is significantly affected by the product design, environment and the application. It is the responsibility of the product designer to ensure proper system level shielding (if required) and to verify performance and fitness for the given product features and applications.

The WiFi performance will be affected by the RF environment surrounding the CX module. Please ensure that the CX module is positioned in a "quiet" RF environment, as far away as possible from high frequency clock signals and any other sources of RF energy. Also, make sure the antenna is not shielded by any metal objects, for example loudspeakers or other metal parts. Please make sure that the power supplies, in particular the +1.9V supply, are quiet and free from noise.

BridgeCo recommends that systems implementing AirPlay should use a module configuration that includes on-module shielding, as well as paying particular attention to system configuration and shielding.

## 10. Revision Control

| Revision | Date / Author           | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|----------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| V1.7 c   | May 13, 2011 / SHs      | <ul> <li>Updated "Module Quality" Defect Rate field entry</li> <li>Updated "Board Dimensions &amp; Weight" drawings</li> <li>Updated the "Electrical Specifications" table</li> <li>Added another Note to the "Pin Descriptions" section</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| V1.7 b   | May 11, 2011 / SHs      | <ul> <li>Updated Note 8 in "Pin Descriptions" table</li> <li>Re-imported "Board Dimensions &amp; Weight" drawings</li> <li>Updated "Board Pictures" images</li> <li>Updated board photo on Cover page</li> <li>Updated the Feature list on Cover page</li> <li>Updated J1, J2 &amp; J3 "Connector PIN Assignments" tables: removed Power column &amp; re-organised columns</li> <li>Changed "Application Notes" title to "Application Guidelines"</li> <li>Updated Copyright date to "2011"</li> <li>Updated Table of Contents font styling</li> </ul>                                                                                                                                                                                                                   |  |  |

| V1.7 a   | May 6, 2011 / SHs       | <ul> <li>Re-imported Block Diagram as a wmf file</li> <li>Updated "Power up, Reset &amp; Power down Timing" figure</li> <li>Updated "Pin Descriptions" table</li> <li>Re-organised text in "Power Supply sequencing &amp; Reset Timing"</li> <li>Re-imported J2 &amp; J3 Connector PIN Assignment tables</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| V1.7     | May 4, 2011 / SHs       | <ul> <li>Added note to Module Weight section</li> <li>Updated the Ordering Guide – Part Numbers &amp; added new J version</li> <li>Added new text to the Board Pictures section</li> <li>Updated all Mechanical Drawings and added &amp; removed Notes</li> <li>Updated the J3 Low Density Connector table</li> <li>Updated the GPIO Assignment table</li> <li>Added new Power Supply &amp; Timing figure</li> <li>Updated the text in the "Power Supply sequencing and Reset Timing" section</li> <li>Updated the Key Connections table</li> <li>Updated "Key Connections" section title to "Pin Descriptions"</li> <li>Updated "Detailed Connector PIN Descriptions" section title to "Connector PIN Assignments"</li> <li>Updated J2 Media Connector table</li> </ul> |  |  |

| V1.6 d   | March 3, 2011 / SHs     | <ul><li>Updated J3 Low Density Connector table</li><li>Update GPIO Assignments section and table</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| V1.6 c   | February 24, 2011 / SHs | Updated all mechanical drawings in "Board Dimensions and Weights" section     Deleted warning note in "Board Dimensions and Weights" section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |