Perfect Wireless Experience 完美无线体验

# FIBOCOM\_NL952-NA\_ Hardware\_User\_Manual

Version: 1.0.1 Date: 2020-02-28

#### Applicability Table

| N | 0. | Product model | Description       |

|---|----|---------------|-------------------|

| 1 |    | NL952-NA-00   | Cat20 WWAN Module |

| 2 | 2  | NL952-NA-20   | Cat12 WWAN Module |

#### Copyright

Copyright © 2020 Fibocom Wireless Inc. All rights reserved.

Without the prior written permission of the copyright holder, any company or individual is prohibited to excerpt, copy any part of or the entire document, or distribute the document in any form.

#### Notice

The document is subject to update from time to time owing to the product version upgrade or other reasons. Unless otherwise specified, the document only serves as the user guide. All the statements, information and suggestions contained in the document do not constitute any explicit or implicit guarantee.

#### Warning

Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation.

If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

-- Reorient or relocate the receiving antenna.

-- Increase the separation between the equipment and receiver.

-- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

-- Consult the dealer or an experienced radio/TV technician for help.

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment. End user must follow the specific operating instructions for satisfying RF exposure compliance. This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter.

The portable device is designed to meet the requirements for

exposure to radio waves established by the Federal Communications

Commission (USA). These requirements set a SAR limit of 1.6 W/kg

averaged over one gram of tissue. The highest SAR value reported under

this standard during product certification for use when properly worn on the body

This device complies with Industry Canada license-exempt RSS standard(s). Operation is subject to the following two conditions:

(1) this device may not cause interference,

(2) this device must accept any interference, including interference that may cause undesired operation of the device.

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes :

(1) l'appareil ne doit pas produire de brouillage,

(2) l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

#### Trademark

**FIDCON** The trademark is registered and owned by Fibocom Wireless Inc.

#### Versions

| Version | Author     | Date       | Remark                           |  |  |  |

|---------|------------|------------|----------------------------------|--|--|--|

| V1.0.0  | Lei Daijun | 2020-01-02 | Draft version                    |  |  |  |

| V1.0.1  | Xu Xialin  | 2020-02-28 | Add NL952-NA-00 and NL952-NA-20  |  |  |  |

| V 1.0.1 |            | 2020-02-28 | Add PCIe_BOOT_DISABLE definition |  |  |  |

## Contents

| 1 | Fore | ewo   | ord    |                              | 8    |

|---|------|-------|--------|------------------------------|------|

|   | 1.1  |       | Intro  | duction                      | 8    |

|   | 1.2  |       | Refe   | erence Standard              | 8    |

|   | 1.3  |       | Rela   | ited Documents               | 8    |

| 2 | Ove  | rvie  | w      |                              | 9    |

|   | 2.1  |       | Intro  | duction                      | 9    |

|   | 2.2  |       | Speo   | cification                   | 9    |

|   | 2.3  |       | CAc    | combinations                 | . 11 |

|   | 2.4  |       | Appl   | lication Block               | .12  |

|   | 2.5  |       | Ante   | enna Configuration           | .12  |

| 3 | Арр  | olica | tion   | Interface                    | .13  |

|   | 3.1  |       | M.2    | Interface                    | .13  |

|   | ,    | 3.1.1 | 1      | Pin Map                      | . 13 |

|   |      | 3.1.2 | 2      | Pin Definition               | . 14 |

|   | 3.2  |       | Pow    | er Supply                    | .18  |

|   | ,    | 3.2.1 | 1      | Power Supply                 | . 18 |

|   |      | 3.2.2 | 2      | Logic level                  | . 19 |

|   |      | 3.2.3 | 3      | Power Consumption            | . 20 |

|   | 3.3  |       | Cont   | trol Signal                  | .21  |

|   |      | 3.3.1 | 1      | Module Start-Up              | . 22 |

|   |      |       | 3.3.1. | 1 Start-up Circuit           | 22   |

|   |      |       | 3.3.1. | .2 Start-up Timing Sequence  | 22   |

|   |      | 3.3.2 | 2      | Module Shutdown              | . 23 |

|   |      | 3.3.3 | 3      | Module Reset                 | . 24 |

|   | ,    | 3.3.4 | 4      | PCIe Link State              | .26  |

|   |      |       | 3.3.4. | 1 D0 L1.2                    | 26   |

|   |      |       | 3.3.4. | .2 D3cold L2                 | 27   |

|   |      | 3.3.5 | 5      | Timing application           | . 27 |

|   | 3.4  |       | IPC    | Interface                    | .28  |

|   |      | 3.4.1 | 1      | PCIe Interface               | . 28 |

|   |      |       | 3.4.1. | 1 PCIe Interface Definition  | 28   |

|   |      |       | 3.4.1. | 2 PCIe Interface Application | 29   |

|   |      | 3.4.2 | 2      | USB Interface                | . 31 |

|   |      |       | 3.4.2 | 2.1 USB Interface Definition      | 31 |

|---|------|-------|-------|-----------------------------------|----|

|   |      |       | 3.4.2 | 2.2 USB2.0 Interface Application  | 31 |

|   |      |       | 3.4.2 | 2.3 USB3.0 Interface Application  | 32 |

|   | 3.5  |       | USI   | IM Interface                      | 33 |

|   |      | 3.5.  | 1     | USIM1 Pins                        | 33 |

|   |      | 3.5.  | 2     | USIM2 Pins                        | 33 |

|   |      | 3.5.  | 3     | USIM Interface Circuit            | 34 |

|   |      |       | 3.5.3 | 3.1 N.C. SIM Card Slot            | 34 |

|   |      |       | 3.5.3 | 3.2 N.O. SIM Card Slot            | 34 |

|   |      | 3.5.  | 4     | USIM Hot-Plugging                 | 35 |

|   |      | 3.5.  | 5     | USIM Design                       | 35 |

|   | 3.6  |       | Stat  | atus Indicator                    | 36 |

|   |      | 3.6.  | 1     | LED#1 Signal                      | 36 |

|   |      | 3.6.  | 2     | WOWWAN#                           | 36 |

|   | 3.7  |       | Inte  | errupt Control                    | 37 |

|   |      | 3.7.  | 1     | W_DISABLE1#                       | 37 |

|   |      | 3.7.  | 2     | BODYSAR                           | 38 |

|   |      | 3.7.  | 3     | PCIe_BOOT_DISABLE                 | 38 |

|   |      | 3.7.  | 4     | ANT_CONFIG                        | 38 |

|   | 3.8  |       | AN    | T Tunable Interface (Reserved)    | 38 |

|   | 3.9  |       | Con   | nfiguration Interface             | 39 |

|   | 3.10 | 0     | Oth   | ner Interfaces                    | 39 |

| 4 | Rad  | dio I | Freq  | quency                            | 40 |

|   | 4.1  |       | RF    | Interface                         | 40 |

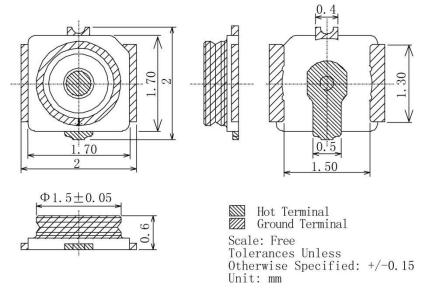

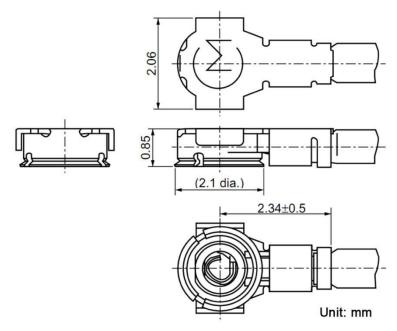

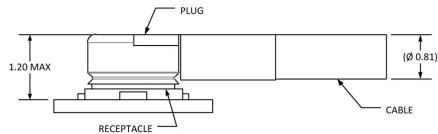

|   |      | 4.1.  | 1     | RF Interface Functionality        | 40 |

|   |      | 4.1.  | 2     | RF Connector Characteristic       | 40 |

|   |      | 4.1.  | 3     | RF Connector Dimension            | 41 |

|   |      | 4.1.  | 4     | RF Connector Assembly             | 42 |

|   | 4.2  |       | Оре   | erating Band                      | 43 |

|   | 4.3  |       | Tra   | ansmitting Power                  | 44 |

|   | 4.4  |       | Rec   | ceiver Sensitivity                | 45 |

|   |      | 4.4.  | 1     | Dual Antenna Receiver Sensitivity | 45 |

|   |      | 4.4.  | 2     | Four Antenna Receiver Sensitivity | 46 |

|   | 4.5  |       | GN    | ISS                               | 46 |

|   |      |       |       |                                   |    |

|   | 4.6     | Ant    | enna Design          | .47  |

|---|---------|--------|----------------------|------|

| 5 | Structu | ure \$ | Specification        | .49  |

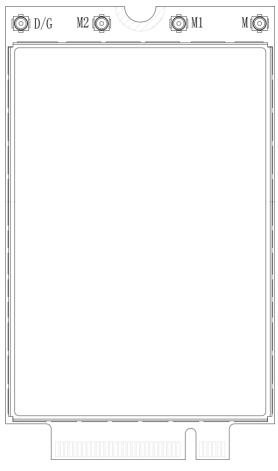

|   | 5.1     | Pro    | duct Appearance      | .49  |

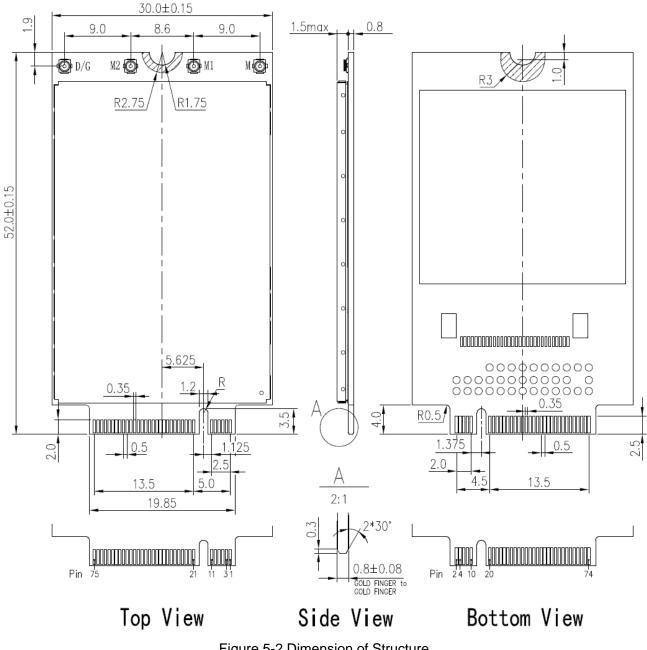

|   | 5.2     | Dim    | nension of Structure | .49  |

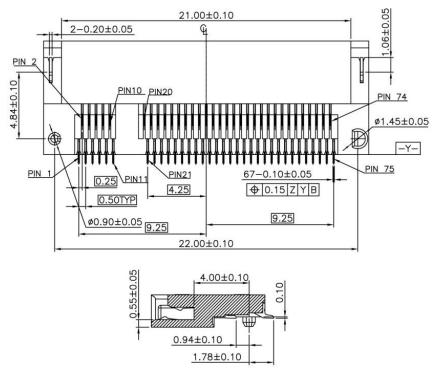

|   | 5.3     | M.2    | Interface Model      | .50  |

|   | 5.4     | M.2    | Connector            | .51  |

|   | 5.5     | Sto    | rage                 | .52  |

|   | 5.5.    | .1     | Storage Life         | . 52 |

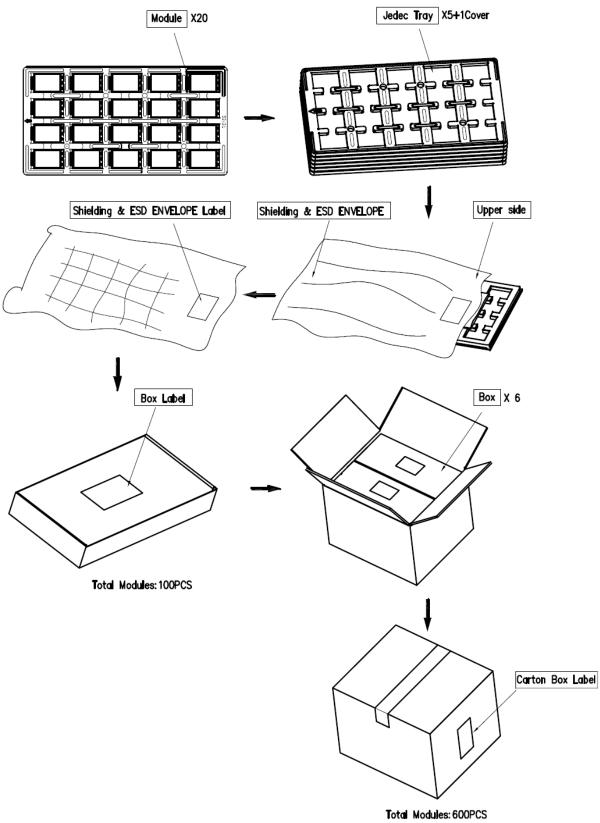

|   | 5.6     | Pac    | king                 | .52  |

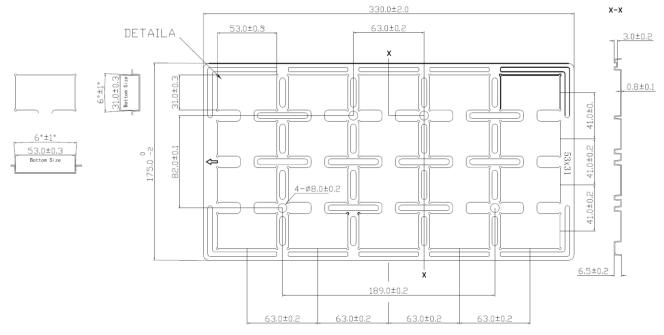

|   | 5.6     | .1     | Tray Package         | . 52 |

|   | 5.6.    | .2     | Tray size            | . 54 |

## Fibccon 1 Foreword

### **1.1 Introduction**

The document describes the electrical characteristics, RF performance, dimensions and application environment, etc. of NL952-NA (hereinafter referred to as NL952). With the assistance of the document and other instructions, the developers can quickly understand the hardware functions of NL952 modules and develop products.

### **1.2 Reference Standard**

The design of the product complies with the following standards:

- 3GPP TS 34.121-1 V8.11.0: User Equipment (UE) conformance specification; Radio transmission and reception (FDD);Part 1: Conformance specification

- 3GPP TS 34.122 V14.0.0: Technical Specification Group Radio Access Network; Radio transmission and reception (TDD)

- 3GPP TS 36.521-1 V14.0.0: User Equipment (UE) conformance specification; Radio transmission and reception; Part 1: Conformance testing

- 3GPP TS 21.111 V10.0.0: USIM and IC card requirements

- 3GPP TS 51.011 V4.15.0: Specification of the Subscriber Identity Module -Mobile Equipment (SIM-ME) interface

- 3GPP TS 31.102 V10.11.0: Characteristics of the Universal Subscriber Identity Module (USIM) application

- 3GPP TS 31.11 V10.16.0: Universal Subscriber Identity Module (USIM) Application Toolkit(USAT)

- 3GPP TS 36.124 V10.3.0: Electro Magnetic Compatibility (EMC) requirements for mobile terminals and ancillary equipment

- 3GPP TS 27.007 V10.0.8: AT command set for User Equipment (UE)

- 3GPP TS 27.005 V10.0.1: Use of Data Terminal Equipment Data Circuit terminating Equipment (DTE DCE) interface for Short Message Service (SMS) and Cell Broadcast Service (CBS)

- PCI Express M.2 Specification Rev1.2

## **1.3 Related Documents**

- RF Antenna Application Design Specification

- NL952 System Driver Integration and Application Guidance

- NL952 AT Commands Manual

## Fibccon 2 Overview

## **2.1 Introduction**

NL952 is a highly integrated 4G WWAN module which uses M.2 form factor interface. It supports LTE FDD/LTE TDD/WCDMA systems and can be applied to most cellular networks of mobile carrier in the world.

## 2.2 Specification

| Specification            | Specification                                                            |                                                                          |                                   |  |  |  |  |

|--------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------|--|--|--|--|

|                          | LTE FDD: Band 2, 4, 5, 7, 12, 13, 14, 17, 25, 26, 29, 30, 66, 71         |                                                                          |                                   |  |  |  |  |

|                          | LTE TDD: Band 41, 46, 48                                                 |                                                                          |                                   |  |  |  |  |

| Operating Band           | DL 4x4 MIMO:                                                             | Band 2, 4, 7, 25, 30, 66, 41, 4                                          | 48                                |  |  |  |  |

|                          | WCDMA/HSP/                                                               | A+: Band 2, 4, 5,                                                        |                                   |  |  |  |  |

|                          | GNSS: suppor                                                             | t GPS, GLONASS, Galileo, Bl                                              | DS                                |  |  |  |  |

|                          |                                                                          | NL952-NA-20(Cat12)                                                       | NL952-NA-00(Cat20)                |  |  |  |  |

|                          | LTE FDD                                                                  | 600Mbps DL(Cat 12)/<br>150Mbps UL                                        | 2Gbps DL(Cat20)/<br>150Mbps UL    |  |  |  |  |

| Data Transmission        | LTE TDD                                                                  | ~460Mbps DL(Cat 12)/<br>90Mbps UL                                        | ~1.44Gbps DL(Cat20)/<br>90Mbps UL |  |  |  |  |

|                          |                                                                          | When LTE TDD achieves maximum DL rate, its UL rate can reach 30Mbps only |                                   |  |  |  |  |

|                          | UMTS/                                                                    | UMTS:384 kbps DL/384 kbps UL                                             |                                   |  |  |  |  |

|                          | HSPA+                                                                    | DC-HSPA+:42 Mbps DL(Cat 24)/5.76 Mbps UL(Cat6)                           |                                   |  |  |  |  |

| Carrier aggregation      |                                                                          | 3CA Downlink Max                                                         | 6CA Downlink Max                  |  |  |  |  |

| Power Supply             | DC 3.3V~4.4                                                              | $3.3V{\sim}4.4V$ , Typical $3.8V$                                        |                                   |  |  |  |  |

|                          | Normal operating temperature: -10 $^\circ$ C $\sim$ +55 $^\circ$ C       |                                                                          |                                   |  |  |  |  |

| Temperature              | Extended operating temperature: -30 $^{\circ}$ C $\sim$ +75 $^{\circ}$ C |                                                                          |                                   |  |  |  |  |

|                          | Storage temperature: -40° C $\sim$ +85° C                                |                                                                          |                                   |  |  |  |  |

|                          | Interface: M.2 Key-B                                                     |                                                                          |                                   |  |  |  |  |

| Physical characteristics | Dimension: 30 x 52 x 2.3mm                                               |                                                                          |                                   |  |  |  |  |

|                          | Weight: About 8.0 g                                                      |                                                                          |                                   |  |  |  |  |

| Interface                | Interface                                                                |                                                                          |                                   |  |  |  |  |

| Antenna Connector        | WWAN Antenr                                                              | na x 4                                                                   |                                   |  |  |  |  |

|                          | Support 4x4 M                                                            | IMO                                                                      |                                   |  |  |  |  |

Reproduction forbidden without Fibocom Wireless Inc. written authorization - All Rights Reserved.

| Specification      | Specification             |  |  |  |  |

|--------------------|---------------------------|--|--|--|--|

|                    | Dual SIM, 1.8V/3V         |  |  |  |  |

|                    | PCle 2.0 X1               |  |  |  |  |

|                    | USB 2.0                   |  |  |  |  |

|                    | USB 3.0                   |  |  |  |  |

| Function Interface | W_Disable#                |  |  |  |  |

|                    | BodySar                   |  |  |  |  |

|                    | LED                       |  |  |  |  |

|                    | Tunable antenna(Reserved) |  |  |  |  |

|                    | I2S(Reserved)             |  |  |  |  |

| Software           |                           |  |  |  |  |

| Protocol Stack     | IPV4/IPV6                 |  |  |  |  |

| AT commands        | 3GPP TS 27.007 and 27.005 |  |  |  |  |

| Firmware update    | USB/PCIe                  |  |  |  |  |

| Other feature      | Multiple carrier          |  |  |  |  |

|                    | Windows update            |  |  |  |  |

#### Note:

When temperature goes beyond normal operating temperature range of -10°C~+55°C, RF performance of module may be slightly off 3GPP specifications.

## 2.3 CA combinations

| DL CA C | DL CA Combinations                                            |     |  |  |  |  |  |

|---------|---------------------------------------------------------------|-----|--|--|--|--|--|

|         | Inter-band                                                    | TBD |  |  |  |  |  |

| 2CA     | Intra-band(non-contiguous)                                    | TBD |  |  |  |  |  |

| 20/1    | Intra-band(contiguous)                                        | TBD |  |  |  |  |  |

|         |                                                               |     |  |  |  |  |  |

|         | Inter-band                                                    | TBD |  |  |  |  |  |

|         | 2 intra-band(non-contiguous)                                  | TDD |  |  |  |  |  |

|         | plus inter-band                                               | TBD |  |  |  |  |  |

| 3CA     | 2 intra-band(contiguous) plus                                 | TDD |  |  |  |  |  |

|         | inter-band                                                    | TBD |  |  |  |  |  |

|         | Intra-band(non-contiguous)                                    | TBD |  |  |  |  |  |

|         | Intra-band(contiguous)                                        | TBD |  |  |  |  |  |

|         | Inter-band                                                    | TBD |  |  |  |  |  |

|         | 2 intra-band(non-contiguous)                                  | TBD |  |  |  |  |  |

|         | plus inter-band                                               |     |  |  |  |  |  |

|         | 2 intra-band(contiguous) plus                                 | TBD |  |  |  |  |  |

|         | inter-band                                                    |     |  |  |  |  |  |

| 4CA     | 2 intra-band(contiguous) plus                                 | TBD |  |  |  |  |  |

| 40A     | 2 intra-band(contiguous)<br>2 intra-band(contiguous) plus     |     |  |  |  |  |  |

|         | 2 intra-band(configuous) plus<br>2 intra-band(non-contiguous) | TBD |  |  |  |  |  |

|         | 3 intra-band(contiguous) plus                                 | TBD |  |  |  |  |  |

|         | inter-band                                                    |     |  |  |  |  |  |

|         | Intra-band(non-contiguous)                                    | TBD |  |  |  |  |  |

|         | Intra-band(contiguous)                                        | TBD |  |  |  |  |  |

|         | 2 intra-band(contiguous) plus 2                               |     |  |  |  |  |  |

|         | intra-band(contiguous) plus                                   | TBD |  |  |  |  |  |

|         | inter-band<br>2 intra-band(contiguous) plus 3                 |     |  |  |  |  |  |

|         | inter-band                                                    | TBD |  |  |  |  |  |

|         | 2 intra-band(contiguous) plus 2                               |     |  |  |  |  |  |

|         | intra-band(non-contiguous) plus                               | TBD |  |  |  |  |  |

| 5CA     | inter-band<br>3 intra-band(contiguous) plus 2                 |     |  |  |  |  |  |

| JUA     | intra-band(configuous) plus z                                 | TBD |  |  |  |  |  |

|         | 3 intra-band(contiguous) plus 2                               | TBD |  |  |  |  |  |

|         | inter-band                                                    |     |  |  |  |  |  |

|         | 3 intra-band(contiguous) plus 2                               | TBD |  |  |  |  |  |

|         | intra-band(non-contiguous)<br>4 intra-band(contiguous) plus   |     |  |  |  |  |  |

|         | inter-band                                                    | TBD |  |  |  |  |  |

|         | Intra-band(non-contiguous)                                    | TBD |  |  |  |  |  |

| 6CA     | 4 intra-band(contiguous) plus 2                               | TBD |  |  |  |  |  |

|         | inter-band                                                    |     |  |  |  |  |  |

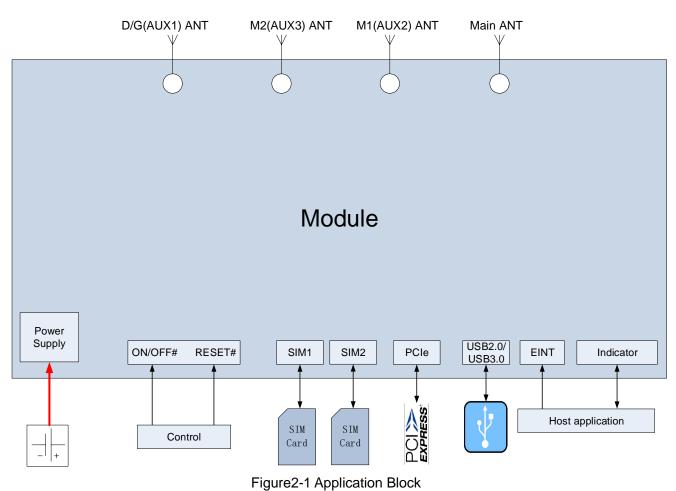

## 2.4 Application Block

The peripheral applications for NL952 module are shown in Figure 2-1:

## 2.5 Antenna Configuration

NL952 module support four antennas and the configuration is as below table:

| Antenna Connector | Function Description | Band configuration                                                                  |

|-------------------|----------------------|-------------------------------------------------------------------------------------|

| М                 | Main ANT             | All supported bands transmit & receive                                              |

| M1                | MIMO1 ANT            | 4x4 MIMO supported bands receive                                                    |

| M2                | MIMO2 ANT            | 4x4 MIMO supported bands receive<br>2 <sup>nd</sup> UL on inter band ULCA mode(TBD) |

| D/G               | Diversity & GNSS ANT | All supported bands and GNSS receive                                                |

## **3 Application Interface**

## 3.1 M.2 Interface

The NL952 module applies standard M.2 Key-B interface, with a total of 75 pins.

### 3.1.1 Pin Map

|                 |                                | CONFIG 2      | 75 |

|-----------------|--------------------------------|---------------|----|

| 74              | +3.3V                          | VIO_CFG       | 73 |

| 72              | +3.3V                          | GND           | 71 |

| 70              | +3.3V                          | CONFIG 1      | 69 |

| <mark>68</mark> | ANT_CONFIG(1.8V)               | RESET#(1.8V)  | 67 |

| 66              | SIM1_DETECT(1.8V)              | ANTCTL3(1.8V) | 65 |

| 64              | COEX_TXD(1.8V)                 | ANTCTL2(1.8V) | 63 |

| 62              | COEX_RXD(1.8V)                 | ANTCTL1(1.8V) | 61 |

| 60              | COEX3(1.8V)                    | ANTCTL0(1.8V) | 59 |

| 58              | RFE_RFFE_SDATA                 | GND           | 57 |

| 56              | RFE_RFFE_SCLK                  | REFCLKP       | 55 |

| 54              | PEWAKE# (3.3/1.8V)             |               | 53 |

| 52              | CLKREQ# (3.3/1.8V)             | REFCLKN       |    |

| 50              | PERST# (3.3/1.8V)              | GND           | 51 |

| 48              | UIM2_PWR                       | PERp0         | 49 |

| 46              | UIM2_RESET                     | PERn0         | 47 |

| 44              | UIM2_CLK                       | GND           | 45 |

| 42              | UIM2_DATA                      | PETp0         | 43 |

| 40              | SIM2_DETECT(1.8V)              | PETn0         | 41 |

| 38              | PCIE_EARLY_BOOT_DISABLE        | GND           | 39 |

| 36              | UIM1_PWR                       | USB3.0-Rx+    | 37 |

| 34              | UIM1_DATA                      | USB3.0-Rx -   | 35 |

| 32              | UIM1_CLK                       | GND           | 33 |

| 30              | UIM1_RESET                     | USB3.0-Tx+    | 31 |

| 28              | I2S_WA(1.8V)                   | USB3.0-Tx -   | 29 |

| 26              | W_DISABLE2#(3.3/1.8V)          | GND           | 27 |

| 24              | I2S_TX(1.8V)                   | DPR(3.3/1.8V) | 25 |

| 22              | I2S_RX(1.8V)                   | WOWWAN#(1.8V) | 23 |

| 20              | I2S_CLK(1.8V)                  | CONFIG_0      | 21 |

|                 | Notch                          | Notch         |    |

| 10              | LED1#(3.3V OD)                 | GND           | 11 |

| 8               | W_DISABLE1#(3.3/1.8V)          | USB D-        | 9  |

| 6               | FULL_CARD_POWER_OFF#(3.3/1.8V) | USB D+        | 7  |

| 4               | +3.3V                          | GND           | 5  |

| 2               | +3.3V                          | GND           | 3  |

|                 |                                | CONFIG_3      | 1  |

#### Note:

Pin "Notch" represents the gap of the gold fingers.

Figure 3-1 Pin Map

### 3.1.2 Pin Definition

The pin definition is as below table:

| Pin | Pin Name                 | I/O | Reset Value | Pin Description                                                                    | Level        |

|-----|--------------------------|-----|-------------|------------------------------------------------------------------------------------|--------------|

| 1   | CONFIG_3                 | 0   | NC          | NC, NL952 M.2 module is configured as<br>the WWAN - PCIe, USB3.0 interface<br>type |              |

| 2   | +3.3V                    | ΡI  | -           | Power input                                                                        | Power Supply |

| 3   | GND                      | -   | -           | GND                                                                                | Power Supply |

| 4   | +3.3V                    | ΡI  | -           | Power input                                                                        | Power Supply |

| 5   | GND                      | -   | -           | GND                                                                                | Power Supply |

| 6   | FULL_CARD_<br>POWER_OFF# | I   | PU          | Power enable, Module power on input, internal pull up(40K $\Omega$ )               | 3.3/1.8V     |

| 7   | USB D+                   | I/O |             | USB Data Plus                                                                      | 0.33V        |

| 8   | W_DISABLE1#              | I   | PD          | WWAN Disable, active low                                                           | 3.3/1.8V     |

| 9   | USB D-                   | I/O |             | USB Data Minus                                                                     | 0.33V        |

| 10  | LED1#                    | OD  | т           | System status LED, Output open drain, 3.3V                                         | 3.3V         |

| 11  | GND                      | -   | -           | GND                                                                                | Power Supply |

| 12  | Notch                    |     |             | Notch                                                                              |              |

| 13  | Notch                    |     |             | Notch                                                                              |              |

| 14  | Notch                    |     |             | Notch                                                                              |              |

| 15  | Notch                    |     |             | Notch                                                                              |              |

| 16  | Notch                    |     |             | Notch                                                                              |              |

| 17  | Notch                    |     |             | Notch                                                                              |              |

| 18  | Notch                    |     |             | Notch                                                                              |              |

| 19  | Notch                    |     |             | Notch                                                                              |              |

| 20  | I2S_CLK                  | 0   | PD          | I2S Serial clock, Reserved                                                         | 1.8V         |

| 21  | CONFIG_0                 |     | NC          | NC, NL952 M.2 module is configured as<br>the WWAN - PCIe, USB3.0 interface<br>type |              |

| 22  | I2S_RX                   | I   | PD          | I2S Serial receive data,<br>Reserved                                               | 1.8V         |

| 23  | WOWWAN#                  | 0   | PD          | Wake up host, Reserved                                                             | 1.8V         |

| 24  | I2S_TX                   | 0   | PD          | I2S Serial transmit data, Reserved                                                 | 1.8V         |

| 25  | DPR                      | I   | PD          | Body SAR Detect, active low                                                        | 3.3/1.8V     |

Reproduction forbidden without Fibocom Wireless Inc. written authorization - All Rights Reserved.

| Pin | Pin Name              | I/O | Reset Value | Pin Description                                                                                                                                                                     | Level        |

|-----|-----------------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 26  | W_DISABLE2#           | I   | PD          | GNSS disable, active low, Reserved                                                                                                                                                  | 3.3/1.8V     |

| 27  | GND                   | -   | -           | GND                                                                                                                                                                                 | Power Supply |

| 28  | I2S_WA                | 0   | PD          | I2S Word alignment/select, Reserved                                                                                                                                                 | 1.8V         |

| 29  | USB3.0_TX-            | 0   |             | USB3.0 Transmit data minus                                                                                                                                                          |              |

| 30  | UIM_RESET             | 0   | PD          | SIM reset signal                                                                                                                                                                    | 1.8V/3V      |

| 31  | USB3.0_TX+            | 0   |             | USB3.0 Transmit data plus                                                                                                                                                           |              |

| 32  | UIM_CLK               | 0   | PD          | SIM clock Signal                                                                                                                                                                    | 1.8V/3V      |

| 33  | GND                   | -   | -           | GND                                                                                                                                                                                 | Power Supply |

| 34  | UIM_DATA              | I/O | PD          | SIM data input/output                                                                                                                                                               | 1.8V/3V      |

| 35  | USB3.0_RX-            | I   |             | USB3.0 receive data minus                                                                                                                                                           |              |

| 36  | UIM_PWR               | 0   |             | SIM power supply, 1.8V/3V                                                                                                                                                           | 1.8V/3V      |

| 37  | USB3.0_RX+            | I   |             | USB3.0 receive data plus                                                                                                                                                            |              |

| 38  | PCIe_<br>BOOT_DISABLE | I   | PD          | PCIe early boot/USB normal boot select,<br>Reserved                                                                                                                                 | 1.8V         |

| 39  | GND                   | -   | -           | GND                                                                                                                                                                                 | Power Supply |

| 40  | SIM2_DETECT           | I   | PD          | SIM2 Detect, internal pull up(390K $\Omega$ ), active high                                                                                                                          | 1.8V         |

| 41  | PETn0                 | 0   |             | PCIe TX Differential signals<br>Negative                                                                                                                                            |              |

| 42  | UIM2_DATA             | I/O | PD          | SIM2 data input/output                                                                                                                                                              | 1.8V/3V      |

| 43  | PETp0                 | 0   |             | PCIe TX Differential signals Positive                                                                                                                                               |              |

| 44  | UIM2_CLK              | 0   | PD          | SIM2 clock Signal                                                                                                                                                                   | 1.8V/3V      |

| 45  | GND                   | -   | -           | GND                                                                                                                                                                                 | Power Supply |

| 46  | UIM2_RESET            | 0   | PD          | SIM2 reset signal                                                                                                                                                                   | 1.8V/3V      |

| 47  | PERn0                 | I   |             | PCIe RX Differential signals<br>Negative                                                                                                                                            |              |

| 48  | UIM2_PWR              | 0   |             | SIM2 power supply, 1.8V/3V                                                                                                                                                          | 1.8V/3V      |

| 49  | PERp0                 | I   |             | PCIe RX Differential signals Positive                                                                                                                                               |              |

| 50  | PERST#                | I   | PU          | Asserted to reset module PCIe interface default. If module went into core dump, it will reset whole module, not only PCIe interface.<br>Active low, internal pull up(10K $\Omega$ ) | 3.3/1.8V     |

| 51  | GND                   | -   | -           | GND                                                                                                                                                                                 | Power Supply |

| Pin | Pin Name    | I/O | Reset Value | Pin Description                                                                                                                                                                                                                                                                                                        | Level        |

|-----|-------------|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 52  | CLKREQ#     | I/O | PD          | Asserted by device to request a PCIe<br>reference clock be available (active clock<br>state) in order to transmit data. It also<br>used by L1 PM Sub states mechanism,<br>asserted by either host or device to<br>initiate an L1 exit.<br>Active low, open drain output and should<br>add external pull up on platform | 3.3/1.8V     |

| 53  | REFCLKN     | I   |             | PCIe Reference Clock signal<br>Negative                                                                                                                                                                                                                                                                                |              |

| 54  | PEWAKE#     | 0   | PD          | Asserted to wake up system and<br>reactivate PCIe link from L2 to L0, it<br>depends on system<br>whether supports wake up functionality.<br>Active low, open drain output and should<br>add external pull up on platform                                                                                               | 3.3/1.8V     |

| 55  | REFCLKP     | I   |             | PCIe Reference Clock signal<br>Positive                                                                                                                                                                                                                                                                                |              |

| 56  | RFFE_SCLK   | 0   | PD          | MIPI Interface Tunable ANT,<br>RFFE clock                                                                                                                                                                                                                                                                              | 1.8V         |

| 57  | GND         |     |             | GND                                                                                                                                                                                                                                                                                                                    | Power Supply |

| 58  | RFFE_SDATA  | I/O | PD          | MIPI Interface Tunable ANT,<br>RFFE data                                                                                                                                                                                                                                                                               | 1.8V         |

| 59  | ANTCTL0     | 0   | PD          | Tunable ANT CTRL0                                                                                                                                                                                                                                                                                                      | 1.8V         |

| 60  | COEX3       | I/O | TBD         | Wireless Coexistence between WWAN<br>and WiFi/BT modules, based on BT-SIG<br>coexistence protocol. COEX_EXT_FTA,<br>Reserved                                                                                                                                                                                           | 1.8V         |

| 61  | ANTCTL1     | 0   | PD          | Tunable ANT CTRL1                                                                                                                                                                                                                                                                                                      | 1.8V         |

| 62  | COEX_RXD    | I   | PD          | Wireless Coexistence between WWAN<br>and WiFi/BT modules, based on BT-SIG<br>coexistence protocol. UART receive<br>signal(WWAN module side), Reserved                                                                                                                                                                  | 1.8V         |

| 63  | ANTCTL2     | 0   | PD          | Tunable ANT CTRL2                                                                                                                                                                                                                                                                                                      | 1.8V         |

| 64  | COEX_TXD    | 0   | PD          | Wireless Coexistence between WWAN<br>and WiFi/BT modules, based on BT-SIG<br>coexistence protocol. UART transmit<br>signal(WWAN module side), Reserved                                                                                                                                                                 | 1.8V         |

| 65  | ANTCTL3     | 0   | PD          | Tunable ANT CTRL3                                                                                                                                                                                                                                                                                                      | 1.8V         |

| 66  | SIM1_DETECT | 1   | PD          | SIM1 Detect, internal pull up(390K $\Omega$ ), active high                                                                                                                                                                                                                                                             | 1.8V         |

| 67  | RESET#      | I   | PU          | WWAN reset input, active low, internal pull up(40K $\Omega$ )                                                                                                                                                                                                                                                          | 1.8V         |

| Pin | Pin Name   | I/O | Reset Value | Pin Description                                                                                       | Level        |

|-----|------------|-----|-------------|-------------------------------------------------------------------------------------------------------|--------------|

| 68  | ANT_CONFIG | I   | PD          | Host antenna configuration detect,<br>internal pull up(100K Ω ),<br>Reserved                          | 1.8V         |

| 69  | CONFIG_1   | 0   | GND         | GND, NL952 M.2 module is configured<br>as the WWAN - PCIe, USB3.0<br>interface type                   |              |

| 70  | +3.3V      | PI  | -           | Power input                                                                                           | Power Supply |

| 71  | GND        | -   | -           | GND                                                                                                   | Power Supply |

| 72  | +3.3V      | ΡI  | -           | Power input                                                                                           | Power Supply |

| 73  | VIO_CFG    | -   | NC          | Configuration of PCIe sideband signals<br>power domain<br>NC: support 1.8V/3.3V;<br>GND: support 3.3V |              |

| 74  | +3.3V      | PI  | -           | Power input                                                                                           | Power Supply |

| 75  | CONFIG_2   | 0   | NC          | NC, NL952 M.2 module is configured as<br>the WWAN - PCIe, USB3.0 interface<br>type                    |              |

Reset Value: The initial status after module reset, not the status when working.

- H: High Voltage Level

- L: Low Voltage Level

- PD: Pull-Down

- PU: Pull-Up

- T: Tristate

- OD: Open Drain

- **PI: Power Input**

- PO: Power Output

#### Note:

The unused pins can be left floating.

## 3.2 Power Supply

The power interface of NL952 module as shown in the following table:

|                  |          |     |                    | DC Parameter (V) |                  |                  |

|------------------|----------|-----|--------------------|------------------|------------------|------------------|

| Pin              | Pin Name | I/O | Pin Description    | Minimum<br>Value | Typical<br>Value | Maximum<br>Value |

| 2, 4, 70, 72, 74 | +3.3V    | PI  | Power supply input | 3.3              | 3.8              | 4.4              |

| 36               | UIM_PWR  | PO  | USIM power supply  | -                | 1.8V/3V          | -                |

| 48               | UIM2_PWR | PO  | USIM power supply  | -                | 1.8V/3V          | -                |

NL952 module uses PCIe interface, according to the PCIe specification, the PCIe Vmain should be used as the +3.3V power source, not the Vaux. The Vaux is the PCIe backup power source and it is not sufficient as the power supply. In addition, the DC/DC power supply other than PCIe ports should not be used as the external power cannot control the module status through the PCIe protocol.

### 3.2.1 Power Supply

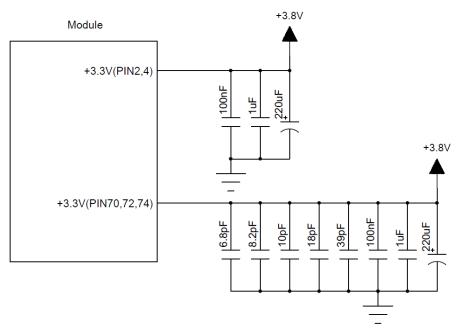

The NL952 module should be powered through the +3.3V pins, and the power supply design is shown in Figure 3-2:

Figure 3-2 Power Supply Design

The filter capacitor design for power supply as shown in the following table:

| Recommended capacitance     | Application                                         | Description                                                                                                                                                                                                                                                              |

|-----------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 220uF x 2                   | Voltage-stabilizing capacitors                      | <ul> <li>Reduce power fluctuations of the module in operation, requiring capacitors with low ESR.</li> <li>LDO or DC/DC power supply requires the capacitor of no less than 440uF</li> <li>The capacitor for battery power supply can be reduced to 100~200uF</li> </ul> |

| 1uF, 100nF                  | Digital signal noise                                | Filter out the interference generated from the clock and digital signals                                                                                                                                                                                                 |

| 39pF, 33pF                  | 700/800, 850/900 MHz frequency band                 | Filter out low frequency band RF interference                                                                                                                                                                                                                            |

| 18pF, 10pF,<br>8.2pF, 6.8pF | 1500/1800, 2100/2300,<br>2600MHz, 3500/3600/3700MHz | Filter out medium/high frequency band RF interference                                                                                                                                                                                                                    |

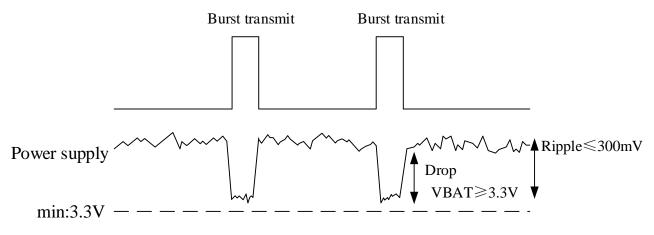

The stable power supply can ensure the normal operation of NL952 module; and the ripple of the power supply should be less than 300mV in design. Because module support 5CA download, when module operates with the maximum data transfer throughput, the peak current can reach to upper 2500mA. It requests the power source voltage should not be lower than 3.3V, otherwise module may shut down or restart. The power supply requirement is shown in Figure 3-3:

Figure 3-3 Power Supply Requirement

### 3.2.2 Logic level

The NL952 module 1.8V logic level definition as shown in the following table:

| Parameters       | Minimum | Typical | Maximum | Unit |

|------------------|---------|---------|---------|------|

| 1.8V logic level | 1.71    | 1.8     | 1.89    | V    |

| VIH              | 1.3     | 1.8     | 1.89    | V    |

| VIL              | -0.3    | 0       | 0.3     | V    |

Reproduction forbidden without Fibocom Wireless Inc. written authorization - All Rights Reserved.

The NL952 module 3.3V logic level definition as shown in the following table:

| Parameters       | Minimum | Typical | Maximum | Unit |

|------------------|---------|---------|---------|------|

| 3.3V logic level | 3.135   | 3.3     | 3.465   | V    |

| V <sub>IH</sub>  | 2.3     | 3.3     | 3.465   | V    |

| VIL              | -0.3    | 0       | 0.3     | V    |

### **3.2.3Power Consumption**

In the condition of 3.3V power supply, the NL952 power consumption as shown in the following table:

| Parameter            | Mode      | Condition                                    | Typical<br>Current<br>(mA) |

|----------------------|-----------|----------------------------------------------|----------------------------|

| I <sub>off</sub>     | Power off | Power supply, module power off               | TBD                        |

|                      | WCDMA     | DRX=8                                        | TBD                        |

| 1                    | LTE FDD   | Paging cycle #64 frames (0.64 sec DRx cycle) | TBD                        |

| I <sub>Sleep</sub>   | LTE TDD   | Paging cycle #64 frames (0.64 sec DRx cycle) | TBD                        |

|                      | Radio Off | AT+CFUN=4, Flight mode                       | TBD                        |

|                      |           | WCDMA Data call Band 2 @+23.5dBm             | TBD                        |

| Iwcdma-rms           | WCDMA     | WCDMA Data call Band 4 @+23.5dBm             | TBD                        |

|                      |           | WCDMA Data call Band 5 @+23.5dBm             | TBD                        |

|                      |           | LTE FDD Data call Band 2 @+23dBm             | TBD                        |

|                      |           | LTE FDD Data call Band 4 @+23dBm             | TBD                        |

|                      |           | LTE FDD Data call Band 5 @+23dBm             | TBD                        |

|                      |           | LTE FDD Data call Band 7 @+23dBm             | TBD                        |

|                      |           | LTE FDD Data call Band 12 @+23dBm            | TBD                        |

| I <sub>LTE-RMS</sub> | LTE FDD   | LTE FDD Data call Band 13 @+23dBm            | TBD                        |

|                      |           | LTE FDD Data call Band 14 @+23dBm            | TBD                        |

|                      |           | LTE FDD Data call Band 17 @+23dBm            | TBD                        |

|                      |           | LTE FDD Data call Band 25 @+23dBm            | TBD                        |

|                      |           | LTE TDD Data call Band 26 @+23dBm            | TBD                        |

|                      |           | LTE TDD Data call Band 30 @+22dBm            | TBD                        |

Reproduction forbidden without Fibocom Wireless Inc. written authorization - All Rights Reserved.

| Parameter | Mode    | Condition                           | Typical<br>Current<br>(mA) |

|-----------|---------|-------------------------------------|----------------------------|

|           |         | LTE TDD Data call Band 66 @+23dBm   | TBD                        |

|           |         | LTE FDD Data call Band 71 @+23dBm   | TBD                        |

|           | LTE TDD | LTE TDD Data call Band 41 @+23dBm   | TBD                        |

|           |         | LTE TDD Data call Band 48 @+21.5dBm | TBD                        |

#### Note:

The above data is the average value obtained by testing the sample for high/medium/low channels.

In 3CA mode, the NL952 power consumption is shown in the following table:

| 3CA Combination | Condition<br>(Max data transfer) | Typical<br>Current(mA) |

|-----------------|----------------------------------|------------------------|

|                 | Band 2 @+22dBm                   | TBD                    |

|                 | Band 4 @+22dBm                   | TBD                    |

|                 | Band 5 @+22dBm                   | TBD                    |

|                 | Band 7 @+22dBm                   | TBD                    |

| твр             | Band 12 @+22dBm                  | TBD                    |

|                 | Band 13 @+22dBm                  | TBD                    |

|                 | Band 30 @+21dBm                  | TBD                    |

|                 | Band 48 @+20.5dBm                | TBD                    |

|                 | Band 66 @+22dBm                  | TBD                    |

|                 | Band 71 @+22dBm                  | TBD                    |

### Note:

The data above is an average value tested on some samples at 25°C temperature.

## 3.3 Control Signal

The NL952 module provides two control signals for power on/off and reset operations, the pin defined as

shown in the following table:

| Pin | Pin Name                 | I/O | Reset Value | Functions                                                                                                                                                                            | Level    |

|-----|--------------------------|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 6   | FULL_CARD_POWER<br>_OFF# | I   | PU          | Module power on/off input,<br>internal pull up(40K Ω )<br>Power on: High/Floating<br>Power off: Low                                                                                  | 3.3/1.8V |

| 67  | RESET#                   | I   | PU          | WWAN reset input, active low, internal pull up(40K $\Omega$ )                                                                                                                        | 1.8V     |

| 50  | PERST#                   | 1   | PU          | Asserted to reset module PCIe<br>interface default. If module went into<br>core dump, it will reset whole<br>module, not only PCIe interface.<br>Active low, internal pull up(10K Ω) | 3.3/1.8V |

#### Note:

RESET# and PERST# need to be controlled by independent GPIO, and not shared with other devices on the host.

#### 3.3.1 Module Start-Up

#### 3.3.1.1 Start-up Circuit

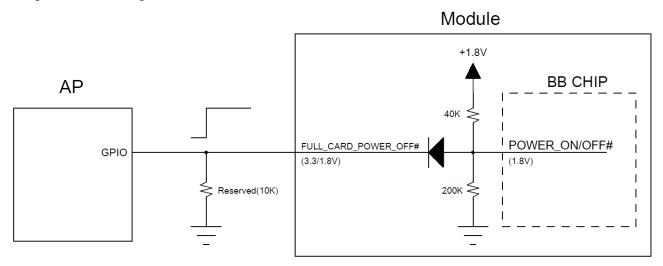

The FCPO#(FULL\_CARD\_POWER\_OFF #) pin needs an external 3.3V or 1.8V pull up for booting up. AP (Application Processor) controls the module start-up. We recommend to use a reset value low or pull down port to control FCPO#, and also reserve an external pull down resistor on FCPO#. The circuit design is shown in Figure3-4:

Figure 3-4 Circuit for Module Start-up Controlled by AP

#### 3.3.1.2 Start-up Timing Sequence

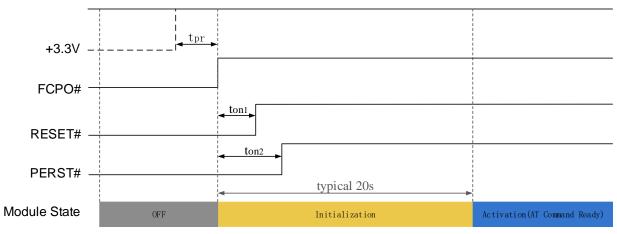

When power supply is ready, the PMU of module will power on and start initialization process by pulling high FCPO# signal. After about 20s, module will complete initialization process. The start-up timing is

shown in Figure 3-5:

Figure 3-5 Timing Control for Start-up

| Index            | Min. | Recommended | Max. | Comments                                                                                                 |

|------------------|------|-------------|------|----------------------------------------------------------------------------------------------------------|

| t <sub>pr</sub>  | 0ms  | -           | -    | The delay time of power supply rising from 0V up to 3.3V.If power supply always ready, it can be ignored |

| t <sub>on1</sub> | TBD  | TBD         | -    | RESET# should be de-asserted after FCPO#                                                                 |

| t <sub>on2</sub> | TBD  | TBD         | -    | The time delay of PERST# de-asserted after FCPO#,<br>PERST# must always be the last to get de-asserted   |

The minimum detection time of PCIe link is about TBD after PERST# de-asserted.

### Note:

When USB is used as data transfer interface, follow timing above in PERST# connecting with host, otherwise don't control PERST# in PERST# floating condition.

### 3.3.2 Module Shutdown

Module can be shut down by following control:

| Shutdown Control | Action                    | Condition                                                                           |

|------------------|---------------------------|-------------------------------------------------------------------------------------|

| Software         | Sending AT+CFUN=0 command | Normal shutdown(recommend)                                                          |

| Hardware         | Pull down FCPO# pin       | Only used when a hardware exception occurs and the software control cannot be used. |

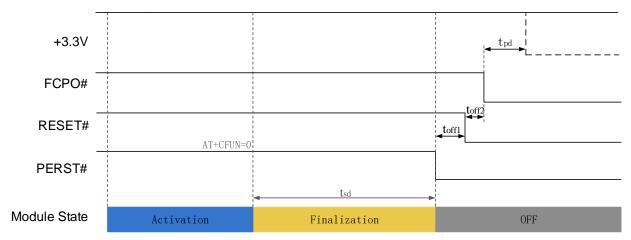

Module can be shut down by sending AT+CFUN=0 command. When the module receives the software shutdown command, the module will start the finalization process (the reverse process of initialization), and it will be completed after  $t_{sd}$  time( $t_{sd}$  is the time which AP receive OK of "AT+CFUN=0", if there is no

response, the max  $t_{sd}$  is 5s). In the finalization process, the module will save the network, SIM card and some other parameters from memory, then clear the memory and shut down PMU. The software control timing is shown in Figure 3-6:

Figure 3-6 Software control power off timing

| Index             | Min. | Recommended | Max. | Comments                                                                           |

|-------------------|------|-------------|------|------------------------------------------------------------------------------------|

| t <sub>off1</sub> | TBD  | TBD         | -    | RESET# should be asserted after PERST#                                             |

| t <sub>off2</sub> | TBD  | TBD         | -    | FCPO# should be asserted after RESET#                                              |

| t <sub>pd</sub>   | TBD  | TBD         | -    | +3.3V power supply goes down time. If power supply is always on, it can be ignored |

#### Note:

When USB is used as data transfer interface, follow timing above in PERST# connecting with host, otherwise don't control PERST# in PERST# floating condition.

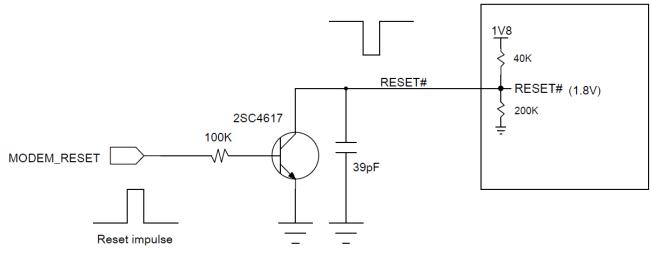

#### 3.3.3 Module Reset

The NL952 module can reset to its initial status by pulling down the RESET# signal for more than 2ms (10ms is recommended), and module will restart after RESET# signal is released. When customer executes RESET# function, the PMU remains its power inside the module. The recommended circuit design is shown in the Figure 3-7:

Figure 3-7 Recommended Design for Reset Circuit

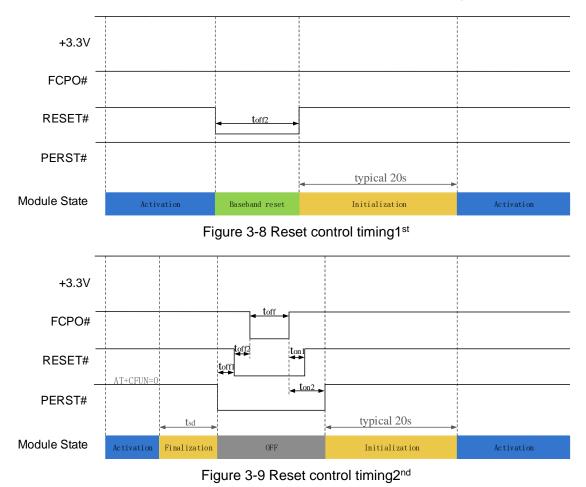

There are two reset control timings as below:

- Reset timing 1<sup>st</sup> in Figure 3-8, PMU of module internal always on in reset sequence, recommend using in FW upgrade and module recovery;

- Reset timing  $2^{nd}$  in Figure 3-9, PMU of module internal will be off in reset sequence (including whole power off and power on sequence,  $t_{sd}$  can refer section 3.3.2), recommend using in system warm boot.

| Index             | Min. | Recommended | Max. | Comments                                                                                                                                                                   |

|-------------------|------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>off1</sub> | TBD  | TBD         | -    | RESET# should be asserted after PERST#, refer section 3.3.2                                                                                                                |

| t <sub>off2</sub> | TBD  | TBD         | -    | FCPO# should be asserted after RESET#, refer section 3.3.2                                                                                                                 |

| t <sub>off</sub>  | TBD  | TBD         | -    | Time to allow the WWAN module to fully discharge any residual voltages before the pin could be de-asserted again. This is required for both Pre-OS as well as Runtime flow |

| t <sub>on1</sub>  | TBD  | TBD         | -    | RESET# should be de-asserted after FCPO#, refer section 3.3.1.2                                                                                                            |

| t <sub>on2</sub>  | TBD  | TBD         | -    | The time delay of PERST# de-asserted after FCPO#,<br>PERST# must always be the last to get de-asserted.<br>refer section 3.3.1.2                                           |

#### **Note:**

When USB is used as data transfer interface, follow timing above in PERST# connecting with host, otherwise don't control PERST# in PERST# floating condition.

#### 3.3.4 PCle Link State

#### 3.3.4.1 D0 L1.2

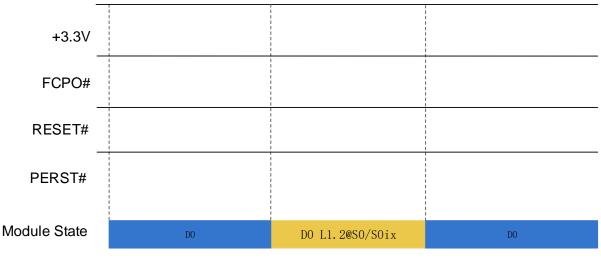

Module supports PCIe goes into D0 L1.2 state in Win10 system. The D0->D0 L1.2@S0/S0ix->D0 timing is shown in figure 3-10:

Figure 3-10 D0 L1.2 timing

#### Note:

When USB is used as data transfer interface in Chrome/Android/Linux OS, there is no PCIe link state. But when USB goes into suspend it also needs to follow the timing above (If PERST# is floating, don't control PERST#).

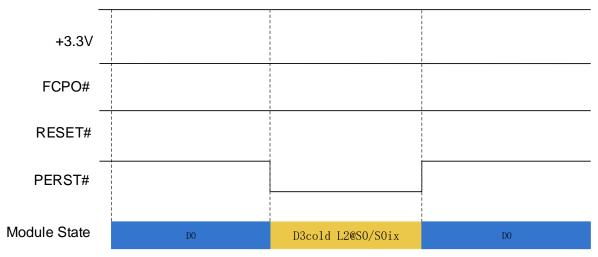

#### 3.3.4.2 D3cold L2

Module supports PCIe goes into D3cold L2 state in Win10 system. The D0->D3cold L2@S0/S0ix ->D0 timing is shown in figure 3-11:

#### Note:

When USB is used as data transfer interface in Chrome/Android/Linux OS, there is no PCIe link state, so don't need to follow timing above.

### 3.3.5 Timing application

The recommended timing application in Win10 OS is as below table:

| System status   |                          | Timing Application                                              |

|-----------------|--------------------------|-----------------------------------------------------------------|

| S0ix            | D0 L1.2                  | Refer to section 3.3.4.1 Figure 3-10 D0 L1.2 Timing             |

| (Modem standby) | D3cold L2                | Refer to section 3.3.4.2 Figure 3-11 D3cold L2 timing           |

| S3,S4,S5        | Power on<br>(back to S0) | Refer to section 3.3.1.2 Figure 3-5 Timing control for start-up |

| 55,54,55        | Power off<br>(out of S0) | Refer to section 3.3.2 Figure 3-6 Software power off timing     |

| G3 boot         | Power on                 | Refer to section 3.3.1.2 Figure 3-5 Timing control for start-up |

| Warm boot       |                          | Refer to section 3.3.3 Figure 3-9 Reset timing 2 <sup>nd</sup>  |

| Modem FW upgrac | le / Modem recovery      | Refer to section 3.3.3 Figure 3-8 Reset timing 1st              |

The recommended timing application in Chrome/Android/Linux OS is as below table:

| System status                     | Timing Application                                              |

|-----------------------------------|-----------------------------------------------------------------|

| Power on                          | Refer to section 3.3.1.2 Figure 3-5 Timing control for start-up |

| Shut down                         | Refer to section 3.3.2 Figure 3-6 Software power off timing     |

| Connect standby                   | Refer to section 3.3.4.1 Figure 3-10 D0 L1.2 Timing             |

| Restart                           | Refer to section 3.3.3 Figure 3-9 Reset timing 2 <sup>nd</sup>  |

| Modem FW upgrade / Modem recovery | Refer to section 3.3.3 Figure 3-8 Reset timing 1 <sup>st</sup>  |

## 3.4 IPC Interface

NL952 module supports PCIe and USB as IPC interface for data transfer. PCIe and USB interface functions are as below table:

| Interface | System        | Priority | Description                                                                                                                                  |

|-----------|---------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| PCle      | Win10 OS      | High     | Priority: PCIe>USB.<br>If PCIe and USB ports both connected with PC, module will<br>initial PCIe first, then disable USB port                |

| USB       | Chrome/Linux/ |          | It must disconnect PCIe port, only keep USB connecting.<br>If keep PCIe and USB connecting both, it needs disable PCIe<br>by BIOS/UEFI of PC |

### 3.4.1 PCIe Interface

NL952 module supports PCIe Gen2, one lane for data transmission channel, it is also compatible with PCIe Gen1. PCIe interface initialized with host driver, then mapped MBIM & GNSS port in Win10 OS and RMNET & AT port in Chrome/Linux/Android OS. The MBIM and RMNET interfaces are used for data transfer, GNSS port is used for receiving GNSS data, AT port is used for AT command.

#### 3.4.1.1 PCIe Interface Definition

| Pin# | Pin Name | I/O | Reset Value | Description                            | Level |

|------|----------|-----|-------------|----------------------------------------|-------|

| 41   | PETn0    | 0   | -           | PCIe TX Differential signals, Negative | -     |

| 43   | PETP0    | 0   | -           | PCIe TX Differential signals, Positive | -     |

| 47   | PERn0    | I   | -           | PCIe RX Differential signals, Negative | -     |

| 49   | PERP0    | I   | -           | PCIe RX Differential signals, Positive | -     |

| Pin# | Pin Name | I/O | Reset Value | Description                                                                                                                                                                                                                                                                                                         | Level    |

|------|----------|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 53   | REFCLKN  | I   | -           | PCIe Reference Clock signal<br>Negative                                                                                                                                                                                                                                                                             | -        |

| 55   | REFCLKP  | I   | -           | PCIe Reference Clock signal<br>Positive                                                                                                                                                                                                                                                                             | -        |

| 50   | PERST#   | 1   | PU          | Asserted to reset module PCIe interface default. If module went into coredump, it will reset whole module, not only PCIe interface. Active low, internal pull up( $10K \Omega$ )                                                                                                                                    | 3.3/1.8V |

| 52   | CLKREQ#  | I/O | PD          | Asserted by device to request a PCIe<br>reference clock be available (active clock<br>state) in order to transmit data. It also used by<br>L1 PM Sub states mechanism, asserted by<br>either host or device to initiate an L1 exit.<br>Active low, open drain output and should add<br>external pull up on platform | 3.3/1.8V |

| 54   | PEWAKE#  | 0   | PD          | Asserted to wake up system and reactivate<br>PCIe link from L2 to L0, it depends on system<br>whether supports wake up functionality.<br>Active low, open drain output and should add<br>external pull up on platform                                                                                               | 3.3/1.8V |

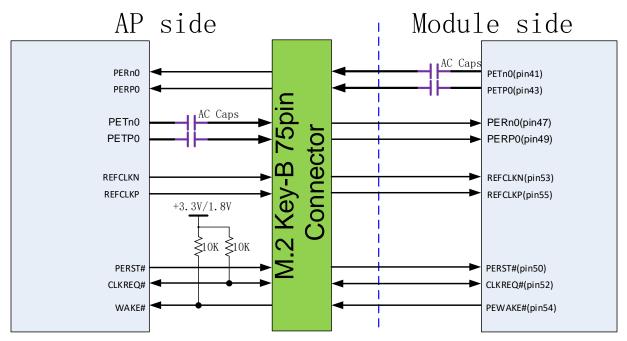

#### 3.4.1.2 PCIe Interface Application

The reference circuit is shown in Figure 3-12:

Figure 3-12 Reference Circuit for PCIe Interface

NL952 module supports PCIe Gen2 interface, including three difference pairs: transmit pair TXP/N,

Reproduction forbidden without Fibocom Wireless Inc. written authorization - All Rights Reserved. FIBOCOM\_NL952-NA\_Hardware\_User\_Manual Page

receiving pair RXP/N and clock pair CLKP/N.

PCIe can achieve the maximum transmission rate of 5 GT/s, and must strictly follow the rules below in PCB Layout:

- The differential signal pair lines shall be parallel and equal in length;

- The differential signal pair lines shall be short if possible and be controlled within 15 inch(380 mm) for AP end;

- The impedance of differential signal pair lines is recommended to be 100 ohm, and can be controlled to 80~120 ohm in accordance with PCIe protocol;

- It shall avoid the discontinuous reference ground, such as segment and space;

- When the differential signal lines go through different layers, the via hole of grounding signal should be in close to that of signal, and generally, each pair of signals require 1-3 grounding signal via holes and the lines shall never cross the segment of plane;

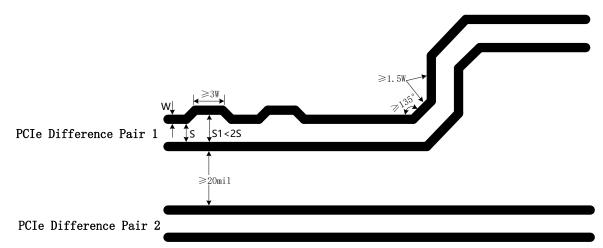

- Try to avoid bended lines and avoid introducing common-mode noise in the system, which will influence the signal integrity and EMI of difference pair. As shown in Figure 3-13, the bending angle of all lines should be equal or greater than 135°, the spacing between difference pair lines should be larger than 20mil, and the line caused by bending should be greater than 1.5 times line width at least. When a serpentine line is used for length match with another line, the bended length of each segment shall be at least 3 times the line width (≥3W). The largest spacing between the bended part of the serpentine line and another one of the differential lines must be less than 2 times the spacing of normal differential lines (S1<2S);</li>

#### Figure 3-13 Requirement of PCIe Line

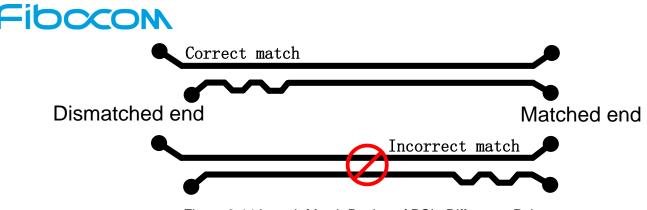

• The difference in length of two data lines in difference pair should be within 5mil, and the length match is required for all parts. When the length match is conducted for the differential lines, the designed position of correct match should be close to that of incorrect match, as shown in Figure 3-14. However, there is no specific requirements for the length match of transmit pair and receiving pair, that is, the length match is only required in the internal differential lines rather than between different difference pairs. The length match should be close to the signal pin and pass the small-angle bending design.

Figure 3-14 Length Match Design of PCIe Difference Pair

### 3.4.2 USB Interface

The NL952 module supports USB2.0 which is compatible with USB High-Speed (480 Mbit/s) and USB Full-Speed (12 Mbit/s). It supports USB3.0 using for LTE cat12 high speed data throughput at the same time. For the USB timing and electrical specification of NL952 module, please refer to Universal Serial Bus Specification 2.0" and "Universal Serial Bus Specification 3.0".

USB3.0 interface initialized with host driver, then mapped RMNET & AT port in Chrome/Linux/Android OS. The RMNET interfaces are used for data transfer, AT port is used for AT command. The port can be configured in practical application.

| Pin# | Pin Name   | I/O | Description                | Туре   |

|------|------------|-----|----------------------------|--------|

| 7    | USB D+     | I/O | USB Data Plus              | 0.33V, |

| 1    | 038_0+     | 1/0 | USD Data Flus              | USB2.0 |

| 9    |            | I/O | USB Data Minus             | 0.33V, |

| 9    | USB_D-     | 1/0 | USB Data Minus             | USB2.0 |

| 29   | USB3.0_TX- | 0   | USB3.0 Transmit data minus | -      |

| 31   | USB3.0_TX+ | 0   | USB3.0 Transmit data plus  | -      |

| 35   | USB3.0_RX- | 1   | USB3.0 receive data minus  | -      |

| 37   | USB3.0_RX+ | 1   | USB3.0 receive data plus   | -      |

#### 3.4.2.1 USB Interface Definition

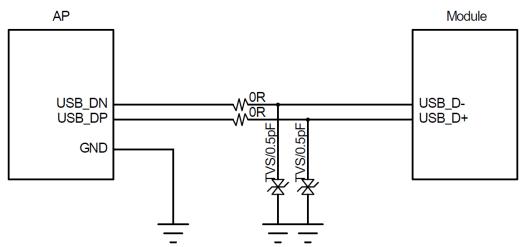

#### 3.4.2.2 USB2.0 Interface Application

The reference circuit is shown in Figure 3-15:

Figure 3-15 Reference Circuit for USB 2.0 Interface

Since the module supports USB 2.0 High-Speed, it is required to use TVS diodes with equivalent capacitance of 1pF or smaller ones on the USB\_D-/D+ differential signal lines, it is recommended to use 0.5pF TVS diodes.

USB\_D- and USB\_D+ are high speed differential signal lines with the maximum transfer rate of 480 Mbit/s, so the following rules shall be followed carefully in the case of PCB layout:

- USB\_D- and USB\_D+ signal lines should have the differential impedance of 90 ohms.

- USB\_D- and USB\_D+ signal lines should be parallel and have the equal length, the right angle routing should be avoided.

- USB\_D- and USB\_D+ signal lines should be routed on the layer that is adjacent to the ground layer, and wrapped with GND vertically and horizontally.

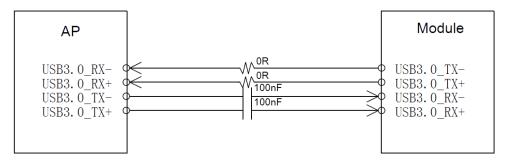

#### 3.4.2.3 USB3.0 Interface Application

The reference circuit is shown in Figure 3-16:

Figure 3-16 Reference Circuit for USB 3.0 Interface

USB 3.0 signals are super speed differential signal lines with the maximum transfer rate of 5Gbps.So the following rules shall be followed carefully in the case of PCB layout:

USB3.0\_TX-/USB3.0\_TX+ and USB3.0\_RX-/ USB3.0\_RX+ are two pairs differential signal lines, the differential impedance should be controlled as 100 ohms.

- Two pairs of differential signal lines should be parallel and have the equal length, the right angle routing should be avoided.

- The two pairs differential signal lines should be routed on the layer that is adjacent to the ground layer, and wrapped with GND vertically and horizontally.

### 3.5 USIM Interface

The NL952 module support dual SIM card single standby, has dual built-in USIM card interface, which supports 1.8V and 3V SIM cards.

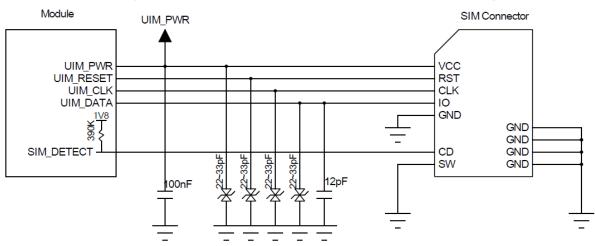

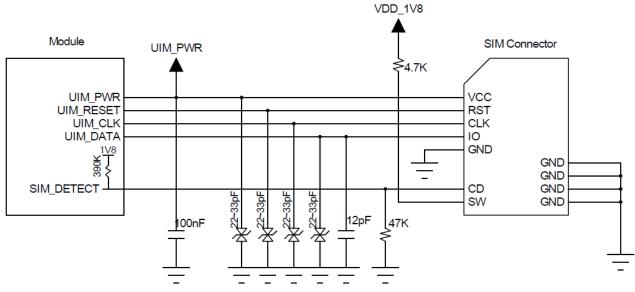

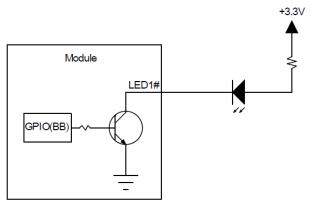

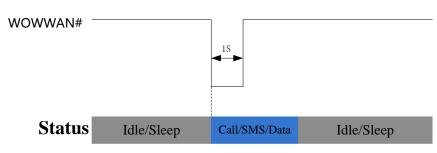

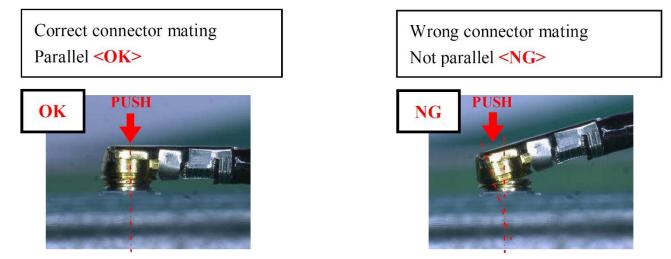

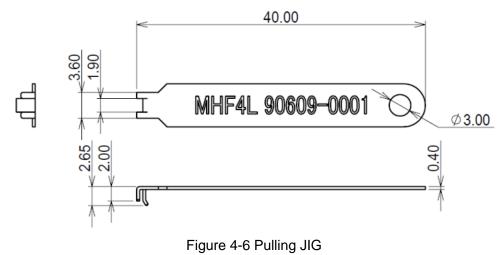

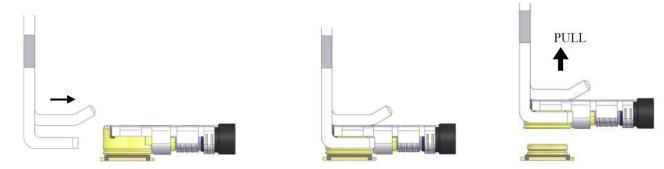

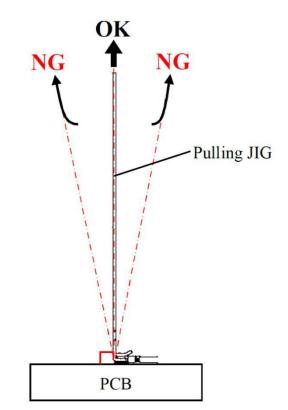

### 3.5.1 USIM1 Pins