Perfect Wireless Experience 完美无线体验

# FIBOCOM NL668-AM Hardware User Manual

Version: V1.0.1 Date: 2018-11-13

### Applicability type

| No. | Product model | Description                                          |  |

|-----|---------------|------------------------------------------------------|--|

| 1   | NL668-AM-00   | MCP is 4+2, and supports MAIN_ANT, DIV_ANT, GNSS_ANT |  |

| 2   | NL668-AM-01   | Based on NL668-AM-00 delete Band 71                  |  |

#### Copyright

Copyright ©2018 Fibocom Wireless Inc. All rights reserved.

Without the prior written permission of the copyright holder, any company or individual is prohibited to excerpt, copy any part of or the entire document, or transmit the document in any form.

#### Attention

The document is subject to update from time to time owing to the product version upgrade or other reasons. Unless otherwise specified, the document only serves as the user guide. All the statements, information and suggestions contained in the document do not constitute any explicit or implicit guarantee.

#### Trademark

Fibocom

The trademark is registered and owned by Fibocom Wireless Inc.

#### Versions

| Version | Author  | Assessor     | Approver | Update<br>Date | Description     |

|---------|---------|--------------|----------|----------------|-----------------|

| V1.0.0  | Gaoying | Chenguojiang | Tumin    | 2018-10-26     | Initial version |

| V1.0.1  | Gaoying | Chenguojiang | Tumin    | 2018-11-13     | Add Band 17     |

## Contents

| 1 | Foi | reword  | I                                                      | . 9  |

|---|-----|---------|--------------------------------------------------------|------|

|   | 1.1 | In      | troduction                                             | 9    |

|   | 1.2 | Sa      | afety Instruction                                      | 9    |

|   | 1.3 | Re      | eference Standards                                     | 10   |

|   | 1.4 | Re      | elated Document                                        | . 11 |

|   | 1.5 | Fe      | ederal Communication Commission Interference Statement | . 11 |

| 2 | Pro | oduct ( | Dverview                                               | 13   |

|   | 2.1 |         | oduct Introduction                                     |      |

|   | 2.2 |         | oduct Specifications                                   |      |

|   | 2.3 |         | ardware Diagram                                        |      |

| 3 | Ар  | plicati | on Interface                                           | 16   |

|   | 3.1 | LC      | CC Interface                                           | 16   |

|   |     | 3.1.1   | Pin distribution                                       |      |

|   |     | 3.1.2   | Pin definition                                         | 17   |

|   | 3.2 | Po      | ower Supply                                            |      |

|   |     | 3.2.1   | Power supply                                           |      |

|   |     | 3.2.2   | 1.8V Output                                            |      |

|   |     | 3.2.3   | Power consumption                                      | 24   |

|   | 3.3 | Co      | ontrol Signal                                          |      |

|   |     | 3.3.1   | Module power on                                        | 26   |

|   |     | 3.3.2   | Module power off                                       | 27   |

|   |     | 3.3.3   | Module reset                                           | 28   |

|   | 3.4 | U       | SB Interface                                           | 30   |

|   |     | 3.4.1   | USB interface definition                               | 30   |

|   | 3.5 | U       | SIM Interface                                          | 31   |

|   |     | 3.5.1   | USIM pin                                               | 31   |

|   |     | 3.5.2   | USIM interface circuit                                 | 31   |

|   |     | 3.5.3   | USIM hot plug                                          | 33   |

|   |     | 3.5.4   | USIM design requirements                               | 34   |

|   | 3.6 | U       | ART Interface                                          | 34   |

|   |     | 3.6.1   | UART interface definition                              | 34   |

|   |     | 3.6.2   | UART port application                                  | 35   |

|   | 3.7 | St      | atus Indicator                                         | 36   |

|    |      | 3.7.1 | NET_MODE Signal                                                 | 36 |

|----|------|-------|-----------------------------------------------------------------|----|

|    | 3.8  | I     | _ow Power Mode                                                  | 37 |

|    |      | 3.8.1 | Flight mode                                                     | 37 |

|    |      | 3.8.2 | Sleep Mode                                                      | 38 |

|    | 3.9  | I     | Digital audio interface PCM                                     | 40 |

|    |      | 3.9.1 | Support model                                                   | 40 |

|    |      | 3.9.2 | PCM interface definition                                        | 40 |

|    |      | 3.9.3 | PCM interface description                                       | 40 |

|    |      | 3.9.4 | PCM signal description                                          | 41 |

|    | 3.10 |       | ADC function                                                    |    |

| 4  | RF   |       | face                                                            |    |

|    | 4.1  |       | NL668-AM Operating Frequency                                    |    |

|    | 4.2  |       | RF Output Power of NL668-AM                                     |    |

|    | 4.3  | I     | RF Receiving Sensitivity of NL668-AM                            | 44 |

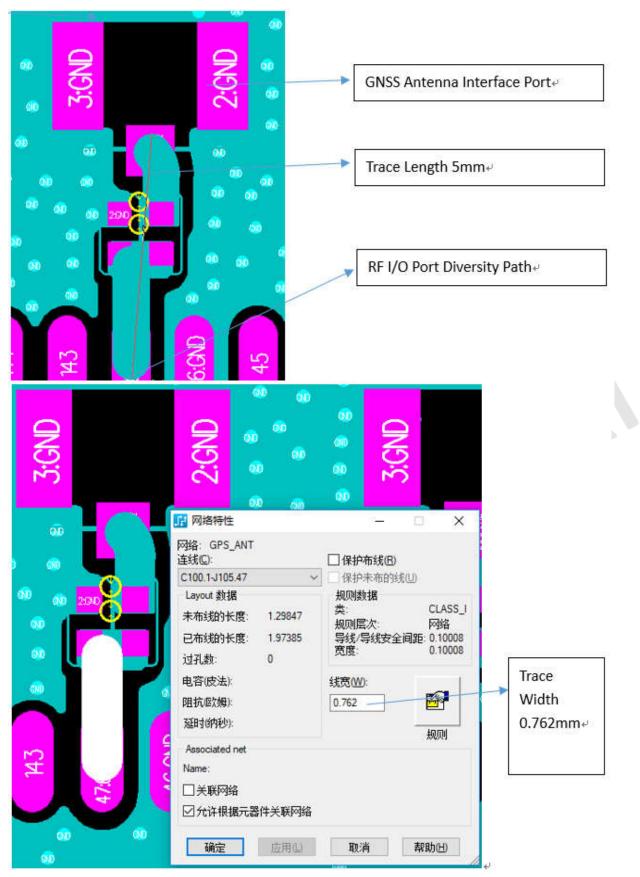

|    | 4.4  | (     | GNSS Receiver                                                   | 44 |

|    |      | 4.4.1 |                                                                 |    |

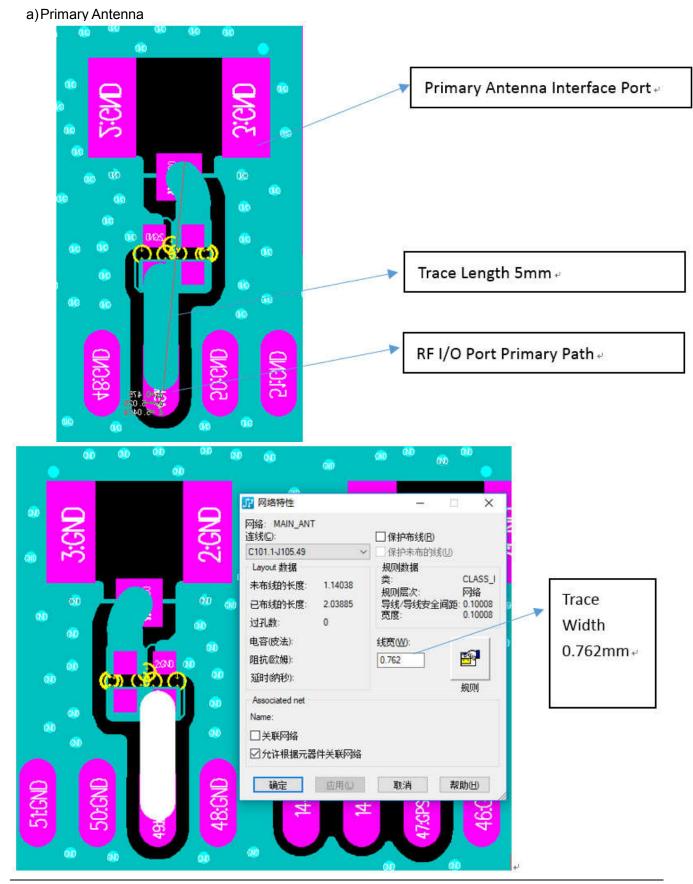

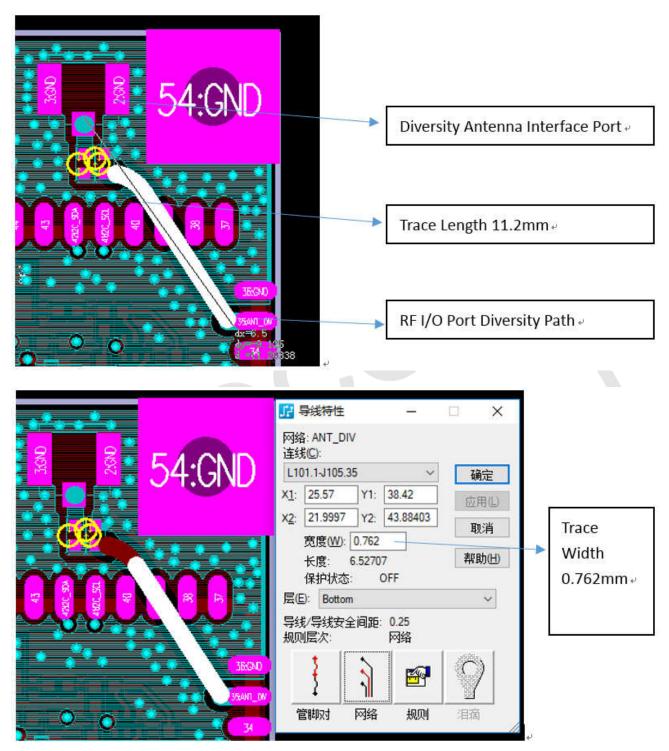

|    | 4.5  | I     | RF PCB Design                                                   | 45 |

|    |      | 4.5.1 | Antenna RF connector                                            | 45 |

|    | 4.6  |       | Antenna Design                                                  |    |

| 5  | Ele  |       | al Characteristics                                              |    |

|    | 5.1  |       | _imiting voltage range                                          |    |

|    | 5.2  | 1     | Environment temperature range                                   | 49 |

|    | 5.3  |       | Electrical characteristics of the interface in operating status | 49 |

|    | 5.4  | I     | Environmental reliability requirements                          | 50 |

|    | 5.5  | I     | ESD characteristics                                             | 51 |

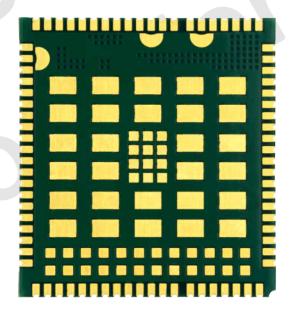

| 6  | Stru | uctu  | re Specification                                                | 52 |

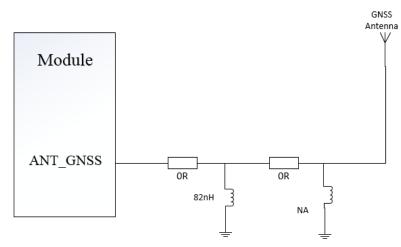

|    | 6.1  |       | Product Appearance                                              | 52 |

|    | 6.2  |       | Dimension of Structure                                          | 53 |

|    | 6.3  | ;     | SMT Patch                                                       | 53 |

| Ap | pend | A xib | Terms and Acronyms                                              | 54 |

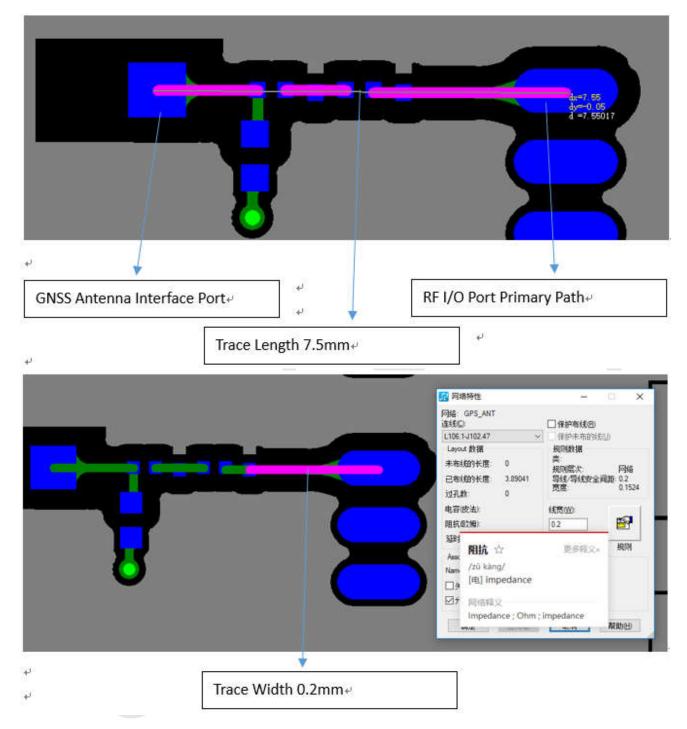

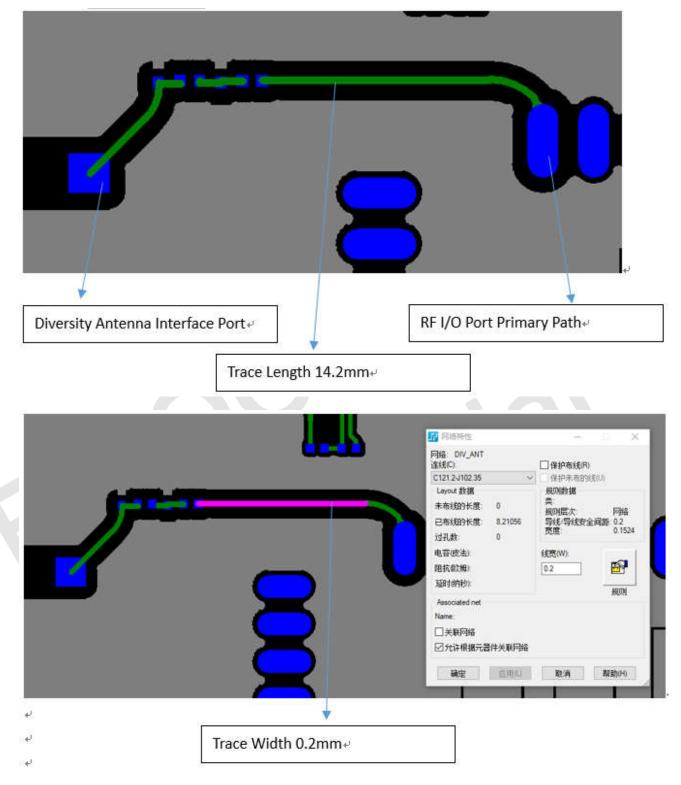

| Ap | pend | dix B | ADP & MiniPCle RF ports trace                                   | 57 |

### Figure

| Figure 2-1 Hardware Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-1 Pin Distribution Diagram(TOP plan perspective diagram)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                                                                                                 |

| Figure 3-2 Power Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23                                                                                                                                 |

| Figure 3-3 Power Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24                                                                                                                                 |

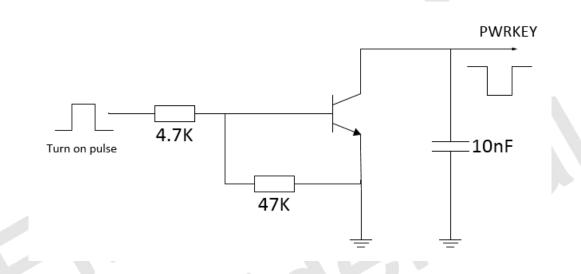

| Figure 3-4 OC/OD Drive Power on Reference Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26                                                                                                                                 |

| Figure 3-5 Button Power on Reference Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26                                                                                                                                 |

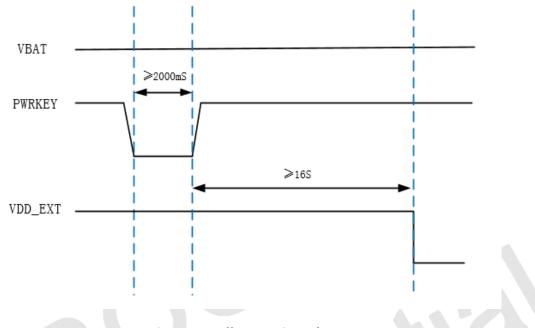

| Figure 3-6 Power on Timing Control Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27                                                                                                                                 |

| Figure 3-7 Power off Timing Control Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28                                                                                                                                 |

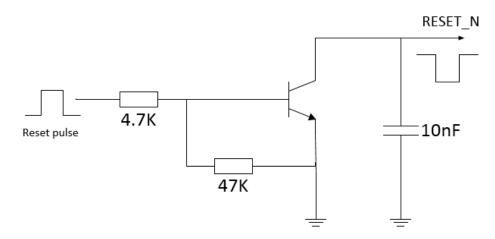

| Figure 3-8 RESET_N OC/OD Drive Reference Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29                                                                                                                                 |

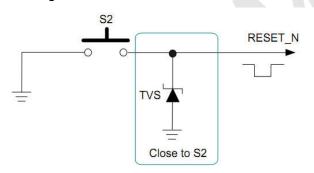

| Figure 3-9 RESET_N Button Reference Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                    |

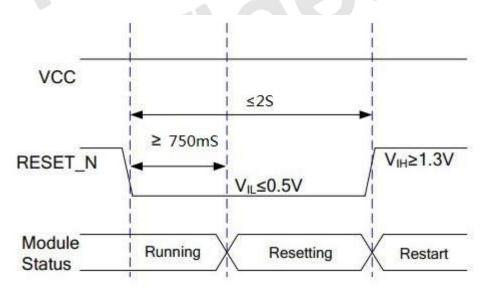

| Figure 3-10 Reset Control Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                    |

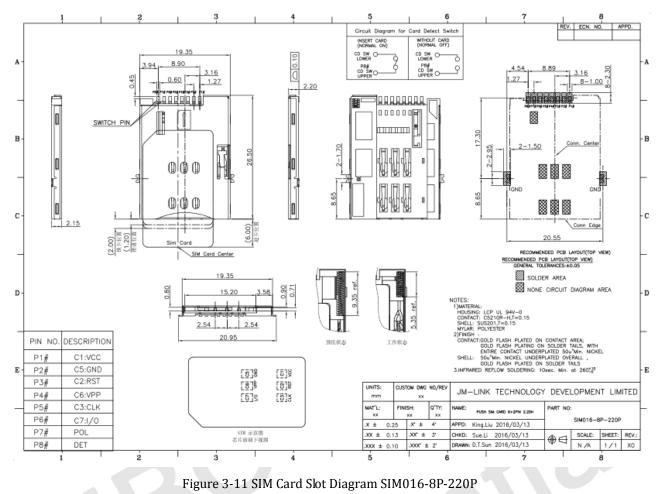

| Figure 3-11 SIM Card Slot Diagram SIM016-8P-220P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32                                                                                                                                 |

| Figure 3-12 USIM/SIM Interface with Detection Signal Reference Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                    |

| Figure 3-13 USIM/SIM Interface without Detection Signal Reference Design Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                    |

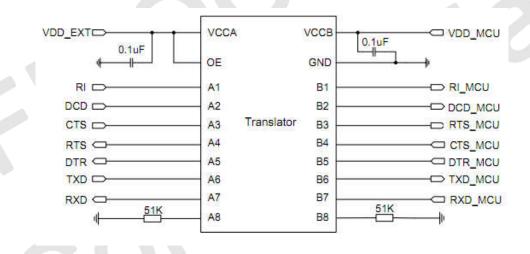

| Figure 3-13 USIM/SIM Interface without Detection Signal Reference Design Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35                                                                                                                                 |

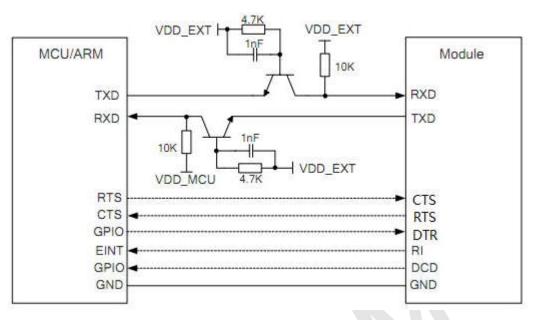

| Figure 3-13 USIM/SIM Interface without Detection Signal Reference Design Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35<br>36                                                                                                                           |

| Figure 3-13 USIM/SIM Interface without Detection Signal Reference Design Diagram       3         Figure 3-14 UART Level Translate Reference Circuit 1       3         Figure 3-15 UART Level Translate Reference Circuit 2       3                                                                                                                                                                                                                                                                                                                                        | 35<br>36<br>37                                                                                                                     |

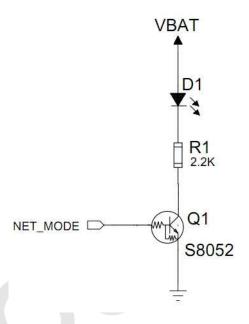

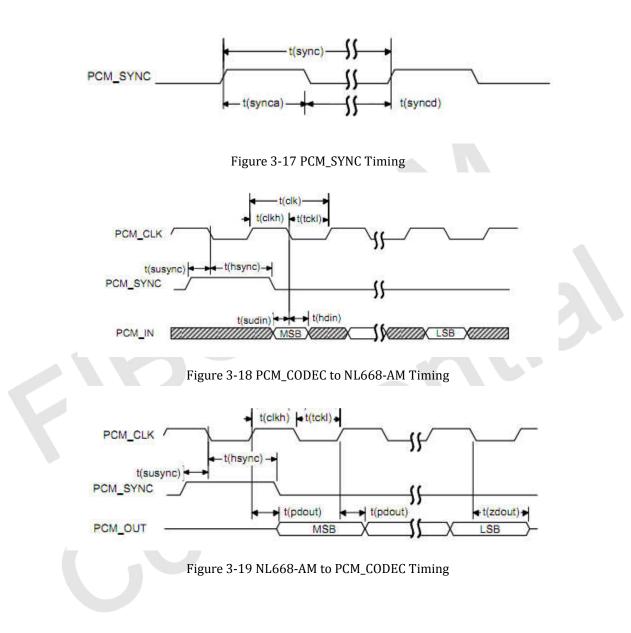

| Figure 3-13 USIM/SIM Interface without Detection Signal Reference Design Diagram       3         Figure 3-14 UART Level Translate Reference Circuit 1       3         Figure 3-15 UART Level Translate Reference Circuit 2       3         Figure 3-16 NET_MODE Reference Design Diagram       3         Figure 3-17 PCM_SYNC Timing       4         Figure 3-18 PCM_CODEC to NL668-AM Timing       4                                                                                                                                                                     | 35<br>36<br>37<br>41<br>41                                                                                                         |

| Figure 3-13 USIM/SIM Interface without Detection Signal Reference Design Diagram       3         Figure 3-14 UART Level Translate Reference Circuit 1       3         Figure 3-15 UART Level Translate Reference Circuit 2       3         Figure 3-16 NET_MODE Reference Design Diagram       3         Figure 3-17 PCM_SYNC Timing       3         Figure 3-18 PCM_CODEC to NL668-AM Timing       4         Figure 3-19 NL668-AM to PCM_CODEC Timing       4                                                                                                            | 35<br>36<br>37<br>41<br>41<br>41                                                                                                   |

| Figure 3-13 USIM/SIM Interface without Detection Signal Reference Design Diagram       3         Figure 3-14 UART Level Translate Reference Circuit 1       3         Figure 3-15 UART Level Translate Reference Circuit 2       3         Figure 3-16 NET_MODE Reference Design Diagram       3         Figure 3-17 PCM_SYNC Timing       4         Figure 3-18 PCM_CODEC to NL668-AM Timing       4                                                                                                                                                                     | 35<br>36<br>37<br>41<br>41<br>41                                                                                                   |

| Figure 3-13 USIM/SIM Interface without Detection Signal Reference Design Diagram       3         Figure 3-14 UART Level Translate Reference Circuit 1       3         Figure 3-15 UART Level Translate Reference Circuit 2       3         Figure 3-16 NET_MODE Reference Design Diagram       3         Figure 3-17 PCM_SYNC Timing       3         Figure 3-18 PCM_CODEC to NL668-AM Timing       4         Figure 3-19 NL668-AM to PCM_CODEC Timing       4                                                                                                            | 35<br>36<br>37<br>41<br>41<br>41<br>42                                                                                             |

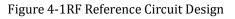

| Figure 3-13 USIM/SIM Interface without Detection Signal Reference Design Diagram       3         Figure 3-14 UART Level Translate Reference Circuit 1       3         Figure 3-15 UART Level Translate Reference Circuit 2       3         Figure 3-16 NET_MODE Reference Design Diagram       3         Figure 3-17 PCM_SYNC Timing       3         Figure 3-18 PCM_CODEC to NL668-AM Timing       4         Figure 3-19 NL668-AM to PCM_CODEC Timing       4         Figure 3-20 CODEC Timing Parameters       4                                                        | 35<br>36<br>37<br>41<br>41<br>41<br>42<br>45                                                                                       |

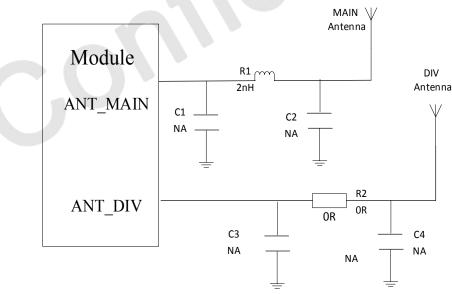

| Figure 3-13 USIM/SIM Interface without Detection Signal Reference Design Diagram       3         Figure 3-14 UART Level Translate Reference Circuit 1       3         Figure 3-15 UART Level Translate Reference Circuit 2       3         Figure 3-16 NET_MODE Reference Design Diagram       3         Figure 3-17 PCM_SYNC Timing       3         Figure 3-18 PCM_CODEC to NL668-AM Timing       4         Figure 3-19 NL668-AM to PCM_CODEC Timing       4         Figure 3-20 CODEC Timing Parameters       4         Figure 4-1RF Reference Circuit Design       4  | 35<br>36<br>37<br>41<br>41<br>41<br>42<br>45<br>46                                                                                 |

| Figure 3-13 USIM/SIM Interface without Detection Signal Reference Design Diagram       3         Figure 3-14 UART Level Translate Reference Circuit 1       3         Figure 3-15 UART Level Translate Reference Circuit 2       3         Figure 3-16 NET_MODE Reference Design Diagram       3         Figure 3-17 PCM_SYNC Timing       3         Figure 3-18 PCM_CODEC to NL668-AM Timing       4         Figure 3-19 NL668-AM to PCM_CODEC Timing       4         Figure 4-1RF Reference Circuit Design       4         Figure 4-2 GNSS RF Reference Circuit       4 | <ul> <li>35</li> <li>36</li> <li>37</li> <li>41</li> <li>41</li> <li>41</li> <li>42</li> <li>45</li> <li>46</li> <li>52</li> </ul> |

#### Table

| Table 2-1 Product Specifications                                          | 14 |

|---------------------------------------------------------------------------|----|

| Table 3-1 Pin Definitions                                                 | 22 |

| Table 3-2 Power Interfaces                                                | 22 |

| Table 3-3 Power Filter Capacitor Design                                   | 23 |

| Table 3-4 VDD_EXT Logic Level                                             | 24 |

| Table 3-5 Power Consumption                                               | 25 |

| Table 3-6 Control Signal                                                  | 26 |

| Table 3-7 Power Off Modes                                                 | 27 |

| Table 3-8 Module Reset                                                    | 28 |

| Table 3-9 USB Interface Definition                                        |    |

| Table 3-10 SIM Card Pin                                                   | 31 |

| Table 3-11SIM Card Hot Plug Function Configured AT Commands               | 33 |

| Table 3-12 USIM_PRESENCE Effective Level Switched AT command              | 34 |

| Table 3-13 Main Serial Port Pin                                           | 35 |

| Table 3-14 Debug Serial Port Pin                                          |    |

| Table 3-15 Network Indication pins                                        |    |

| Table 3-16 Network Indicator Status Description                           | 37 |

| Table 3-17 W_DISABLE# Pin Description                                     |    |

| Table 3-18 Module enter Fly Mode                                          |    |

| Table 3-19 Support model                                                  | 40 |

| Table 3-20 PCM Interface Definition                                       |    |

| Table 3-21 PCM Interface Description                                      | 40 |

| Table 3-22 ADC Interface                                                  | 42 |

| Table 4-1Operating Frequency                                              | 43 |

| Table 4-2 RF Output Power                                                 | 43 |

| Table 4-3 RF Receiving Sensitivity                                        | 44 |

| Table 4-4 GNSS Receiver                                                   | 45 |

| Table 4-5 Main Antenna Requirement                                        | 48 |

| Table 5-1 Voltage Range                                                   | 49 |

| Table 5-2Environment Temperature Range                                    | 49 |

| Table 5-3 Electrical Characteristics of the Interface in Operating Status | 50 |

| Table 5-4 Environmental Reliability Requirements                          | 50 |

| Table 5-5 ESD Allowable Discharge Range                                   | 51 |

| Table A-0-1 Terms and Acronyms    56 |

|--------------------------------------|

|--------------------------------------|

### **1** Foreword

### 1.1 Introduction

This document describes the electrical characteristics, RF performance, structure size, application environment, etc. of NL668-AM module. With the assistance of the document and other instructions, the developers can quickly understand the hardware functions of the NL668-AM module and develop products.

### 1.2 Safety Instruction

By following the safety guidelines below, you can ensure your personal safety and help protect the product and work environment from potential damage. Product manufacturers need to communicate the following safety instructions to end users. In case of failure to comply with these safety rules, Fibocom will not be responsible for the consequences caused by the user's misuse.

Road safety first! When you drive, do not use the handheld devices even if it has a hand-free feature. Please stop and call.

Please turn off the mobile device before boarding. The wireless feature of the mobile device is not allowed on the aircraft to prevent interference with the aircraft communication system. Ignoring this note may result in flight safety issue or even breaking the law.

•

When in a hospital or health care facility, please be aware of restrictions on the use of mobile devices. Radio frequency interference may cause medical equipment to malfunction, so it may be necessary to turn off the mobile device.

## SOS

The mobile device does not guarantee that an effective connection can be made under any circumstances, for example, when there is no prepayment for the mobile device or the SIM is invalid. When you encounter the above situation in an emergency, remember to use an emergency call, while keeping your device turned on and in areas where signal is strong.

Your mobile device receives and transmits RF signals when it is powered on. Radio interference occurs when it is near televisions, radios, computers, or other electronic devices.

Keep the mobile device away from flammable gases. Turn off the mobile device when near gas stations, oil depots, chemical plants or explosive workplaces. There is a safety hazard in operating electronic equipment in any potentially explosive environment.

### 1.3 Reference Standards

This design of the product complies with the following standards:

- 3GPP TS 51.010-1 V10.5.0: Mobile Station (MS) conformance specification; Part 1: Conformance specification

- 3GPP TS 34.121-1 V10.8.0: User Equipment (UE) conformance specification; Radio transmission and reception (FDD); Part 1: Conformance specification

- 3GPP TS 34.122 V10.1.0: Technical Specification Group Radio Access Network; Radio transmission and reception (TDD)

- 3GPP TS 36.521-1 V10.6.0: User Equipment (UE) conformance specification; Radio transmission and reception; Part 1: Conformance testing

- 3GPP TS 21.111 V10.0.0: USIM and IC card requirements

- 3GPP TS 51.011 V4.15.0: Specification of the Subscriber Identity Module -Mobile Equipment (SIM-ME) interface

- 3GPP TS 31.102 V10.11.0: Characteristics of the Universal Subscriber Identity Module (USIM) application

- 3GPP TS 31.11 V10.16.0: Universal Subscriber Identity Module (USIM) Application Toolkit(USAT)

- 3GPP TS 36.124 V10.3.0: Electro Magnetic Compatibility (EMC) requirements for mobile terminals and ancillary equipment

- 3GPP TS 27.007 V10.0.8: AT command set for User Equipment (UE)

- 3GPP TS 27.005 V10.0.1: Use of Data Terminal Equipment Data Circuit terminating Equipment (DTE - DCE) interface for Short Message Service (SMS) and Cell Broadcast Service (CBS)

Reproduction forbidden without Fibocom Wireless Inc. written authorization - All Rights Reserved. FIBOCOM NL668-AM Hardware User Manual

### **1.4 Related Document**

- FIBOCOM\_RF Antenna Application Design Instruction

- FIBOCOM\_ADP-NL668 Evaluation board instruction

- FIBOCOM\_NL668 AT Command Manual

- FIBOCOM\_EVK-GT8230-NL User Manual

- FIBOCOM\_ NL668 LCC SMT Application Design Instruction

### 1.5 Federal Communication Commission Interference Statement

#### FCC Regulations:

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) This device must accept any interference received, including interference that may cause undesired operation.

This device has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiated radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

-Reorient or relocate the receiving antenna.

-Increase the separation between the equipment and receiver.

-Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

-Consult the dealer or an experienced radio/TV technician for help.

Caution: Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

#### **RF Exposure Information:**

This device complies with FCC radiation exposure limits set forth for an uncontrolled environment. In order to avoid the possibility of exceeding the FCC radio frequency exposure limits, human proximity to the antenna shall not be less than 20cm (8 inches) during normal operation.

#### **IMPORTANT NOTE :**

This module is intended for OEM integrator. The OEM integrator is still responsible for the FCC compliance requirement of the end product, which integrates this module. 20cm minimum distance has to be able to be maintained between the antenna and the users for the host this module is integrated into. Under such configuration, the FCC radiation exposure limits set forth for an population/uncontrolled environment can be satisfied.

Any changes or modifications not expressly approved by the manufacturer could void the user's authority to operate this equipment.

#### **USERS MANUAL OF THE END PRODUCT :**

In the user manual of the end product, the end user has to be informed to keep at least 20cm separation with the antenna while this end product is installed and operated. The end user has to be informed that the FCC radio-frequency exposure guidelines for an uncontrolled environment can be satisfied. The end user has to also be informed that any changes or modifications not expressly approved by the manufacturer could void the user's authority to operate this equipment. If the size of the end product is smaller than 8x10cm, then additional FCC part 15.19 statement is required to be available in the users manual: This device complies with Part 15 of FCC rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference and (2) this device must accept any interference received, including interference that may cause undesired operation.

#### LABEL OF THE END PRODUCT :

The final end product must be labeled in a visible area with the following " Contains Transmitter Module FCC ID: ZMONL668AM01". If the size of the end product is larger than 8x10cm, then the following FCC part 15.19 statement has to also be available on the label: This device complies with Part 15 of FCC rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference and (2) this device must accept any interference received, including interference that may cause undesired operation.

### **2 Product Overview**

### 2.1 Product Introduction

The NL668-AM wireless module is a wideband wireless terminal product applicable to various network formats and multi-bands including FDD-LTE/UMTS.

### 2.2 Product Specifications

| Specification        |                                      |                                                            |  |  |

|----------------------|--------------------------------------|------------------------------------------------------------|--|--|

|                      | NL668-AM-00                          | LTE FDD: Band 2,4,5,12,13,17,66,71                         |  |  |

| Operating            | NL008-AIVI-UU                        | WCDMA: Band 2,4,5                                          |  |  |

| frequency            | NL668-AM-01                          | LTE FDD: Band 2,4,5,12,13,17,66                            |  |  |

|                      | NL008-ANI-01                         | WCDMA: Band 2,4,5                                          |  |  |

| Data                 | LTE FDD Rel.9                        | 150Mbps DL/50Mbps UL(Cat 4); LTE Downlink MIMO 2x2,<br>4x2 |  |  |

| transmission         | WCDMA Rel.8                          | WCDMA:384 kbps DL/384 kbps UL                              |  |  |

|                      | WCDWA Rel.o                          | DC-HSDPA+:42Mbps (Cat 24)/HSUPA:5.76Mbps (Cat 6)           |  |  |

| Power                | 3.3V~4.3V (3.8V rec                  | commended)                                                 |  |  |

|                      | Normal: -30°C~+75°C                  |                                                            |  |  |

| Temperature          | Extended: -40°C~+85°C                |                                                            |  |  |

|                      | Storage: -40°C~+85°C                 |                                                            |  |  |

| Damas                | Base current: <1.5mA                 |                                                            |  |  |

| Power<br>consumption | Sleep mode: ≤3mA                     |                                                            |  |  |

| consumption          | Idle mode: <20mA                     |                                                            |  |  |

| Physical             | Package: LCC 144PIN                  |                                                            |  |  |

| characteristics      | Size: 32.0×29.0×2.4 mm               |                                                            |  |  |

| characteristics      | Weight: About 5.5g                   |                                                            |  |  |

| Interface            |                                      |                                                            |  |  |

| Antenna              | Antenna: Main x 1, GNSS x 1, DIV x 1 |                                                            |  |  |

| Functional           | USIM 3.0V/1.8V                       |                                                            |  |  |

## **FIDCCON**

| Interface            | USB 2.0 x 1                                                                      |

|----------------------|----------------------------------------------------------------------------------|

|                      | UART, PCM, I2C, SGMII, SDIO, GPIO, SPI                                           |

|                      | System Indicator                                                                 |

|                      | ADC                                                                              |

| Software             |                                                                                  |

| Protocol Stack       | Embedded TCP/IP and UDP/IP protocol stack                                        |

| AT Command           | 3GPP TS 27.007 and 27.005, and proprietary FIBOCOM AT                            |

| Firmware update      | USB(UART does not support DOWNLOAD)                                              |

| Voice service        | VoLTE, HR, FR, EFR, AMR, DTMF, Caller ID, Call Transfer, Call Hold, Call Waiting |

| and Multi-Talk, etc. |                                                                                  |

| SMS                  | point-to-point MO, MT; cell broadcast; support Text and PDU modes                |

| MMS service          | Need AP to realize MMS protocol                                                  |

Table 2-1 Product Specifications

#### Note:

When the temperature is beyond the normal operating temperature range (-30 °C to + 75 °C), the RF performance of the module may slightly exceed the 3GPP specifications.

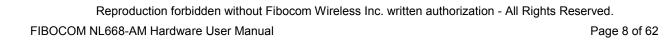

### 2.3 Hardware Diagram

Figure 2-2 hardware diagram shows the main hardware features of the NL668-AM module, including baseband and RF features.

Baseband includes:

- UMTS/ LTE FDD controller •

- PMIC

- MCP

- UART, USB, SIM, PCM, I2C, SPI, SGMII, SDIO, ADC

RF includes:

- **RF** Transceiver •

- RF PA

- **RF** filter ٠

- Antenna

Figure 2-1 Hardware Diagram

### **3 Application Interface**

### 3.1 LCC Interface

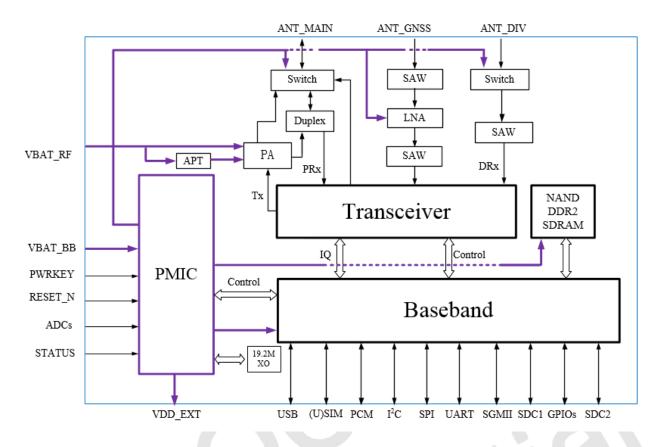

NL668-AM module adopts LCC packaging, with a total of 144 pins.

### 3.1.1 Pin distribution

Figure 3-1 Pin Distribution Diagram(TOP plan perspective diagram)

### Note:

"73 ~ 112" is the thermal pin, and the module is grounded internally. It is recommended that the heat sink pad is reserved for PCB packaging and welded.

#### 3.1.2 Pin definition

The pin definitions are shown in the following table:

| Pin | Pin Name      | I/O | Level                                                       | Description                             |

|-----|---------------|-----|-------------------------------------------------------------|-----------------------------------------|

| 1   | WAKEUP_IN     | I   | Vii.min=-0.3V<br>Vii.max=0.6V<br>Viimin=1.2V<br>Viimax=2.0V | External device wake-up module          |

| 2   | AP_READY      | I   | VILmin=-0.3V<br>VILmax=0.6V<br>VIHmin=1.2V<br>VIHmax=2.0V   | Reserved                                |

| 3   | RESERVED      |     | -                                                           | Reserved                                |

| 4   | W_DISABLE#    | I   | VILmin=-0.3V<br>VILmax=0.6V<br>VIHmin=1.2V<br>VIHmax=2.0V   | Module flight mode control              |

| 5   | NET_MODE      | 0   | Voнmin=1.35V<br>Volmax=0.45V                                | Module state indicate                   |

| 6   | NET_STATUS    | 0   | Voнmin=1.35V<br>VoLmax=0.45V                                | Reserved                                |

| 7   | VDD_EXT       | PO  | 1.8V                                                        | Module digital level, 1.8V output, 80mA |

| 8   | GND           | G   | -                                                           | Ground                                  |

| 9   | GND           | G   |                                                             | Ground                                  |

| 10  | GND           | G   |                                                             | Ground                                  |

| 11  | DBG_RXD       | 5   | Vı⊥min=-0.3V<br>Vı⊥max=0.6V<br>Vı⊧min=1.2V<br>Vı⊧max=2.0V   | DEBUG serial port Receive data          |

| 12  | DBG_TXD       | 0   | Vormax=0.45V<br>Voнmin=1.35V                                | DEBUG serial port Transmit data         |

| 13  | USIM_PRESENCE | I   | VILmin=-0.3V<br>VILmax=0.6V<br>VIHmin=1.2V<br>VIHmax=2.0V   | USIM card hot plug detection            |

| 14  | USIM_VDD      | 0   | For 1.8V USIM:<br>Vmax=1.9V<br>Vmin=1.7V                    | USIM power                              |

| Pin | Pin Name   | I/O | Level                 | Description                            |

|-----|------------|-----|-----------------------|----------------------------------------|

|     |            |     | For 3.0V USIM:        |                                        |

|     |            |     | Vmax=3.05V            |                                        |

|     |            |     | Vmin=2.7V             |                                        |

|     |            |     | lomax=150mA           |                                        |

|     |            |     | For 1.8V USIM:        |                                        |

|     |            |     | Vı⊥max=0.6V           |                                        |

|     |            |     | VIHmin=1.2V           |                                        |

|     |            |     | Volmax=0.45V          |                                        |

|     |            | •   | Voнmin=1.35V          |                                        |

| 15  | USIM _DATA | 0   | For 3.0V USIM:        | USIM data signal cable                 |

|     |            |     | V⊪max=1.0V            |                                        |

|     |            |     | VIHmin=1.95V          |                                        |

|     |            |     | Volmax=0.45V          |                                        |

|     |            |     | Vон <b>min=2</b> .55V |                                        |

|     |            |     | For 1.8V USIM:        |                                        |

|     |            |     | Volmax=0.45V          |                                        |

|     |            |     | Vонmin=1.35V          |                                        |

| 16  | USIM_CLK   | 0   | For3.0V USIM:         | USIM clock signal cable                |

|     |            |     | Volmax=0.45V          |                                        |

|     |            |     | Voн <b>min=2</b> .55V |                                        |

|     |            |     | For 1.8V USIM:        |                                        |

|     |            |     | Volmax=0.45V          |                                        |

|     |            |     | Voнmin=1.35V          |                                        |

| 17  | USIM_RST   | 0   | For 3.0V USIM:        | USIM reset signal cable                |

|     |            |     | Volmax=0.45V          |                                        |

|     |            |     | Voнmin=2.55V          |                                        |

| 18  | NC         | -   | -                     | NC                                     |

| 19  | GND        | G   | -                     | Ground                                 |

|     |            |     | VIHmax=2.1V           |                                        |

| 20  | RESET_N    | I   | VIHmin=1.3V           | Module reset signal, active low, no    |

|     | _          |     | V⊩max=0.5V            | need pull up externally                |

|     |            |     | VIHmax=2.1V           | Turn on/off the module active law me   |

| 21  | PWRKEY     | I   | VIIImin=1.3V          | Turn on/off the module, active low, no |

|     |            |     | VILmax=0.5V           | need pull up externally                |

| 22  | GND        | G   | -                     | Ground                                 |

| 23  | SD_INS_DET | I   | -                     | Reserved                               |

| 24  | PCM_IN     | I   | VILmin=-0.3V          | PCM input signal                       |

| Pin | Pin Name   | I/O | Level                 | Description                             |

|-----|------------|-----|-----------------------|-----------------------------------------|

|     |            |     | VILmax=0.6V           |                                         |

|     |            |     | VIHmin=1.2V           |                                         |

|     |            |     | Vнmax=2.0V            |                                         |

| 25  | PCM_OUT    | 0   | Volmax=0.45V          | PCM output signal                       |

| 25  |            | 0   | Vон <b>min=1.35</b> V | PCM output signal                       |

|     |            |     | Volmax=0.45V          |                                         |

|     |            |     | Voн <b>min=1.35V</b>  |                                         |

| 26  | PCM_SYNC   | I/O | V⊪min=-0.3V           | PCM synchronization signal              |

| 20  |            | 1/0 | V⊪max=0.6V            |                                         |

|     |            |     | VIHmin=1.2V           |                                         |

|     |            |     | V⊮max=2.0V            |                                         |

|     |            |     | Volmax=0.45V          |                                         |

|     |            |     | Voнmin=1.35V          |                                         |

| 27  | PCM_CLK    | I/O | Vı⊥min=-0.3V          | PCM clock signal                        |

| 21  |            | 1/0 | Vı⊥max=0.6V           |                                         |

|     |            |     | VIIImin=1.2V          |                                         |

|     |            |     | V⊮max=2.0V            |                                         |

| 28  | SDC2_DATA3 | I/O |                       | Reserved                                |

| 29  | SDC2_DATA2 | 1/0 | -                     | Reserved                                |

| 30  | SDC2_DATA1 | I/O | -                     | Reserved                                |

| 31  | SDC2_DATA0 | I/O | -                     | Reserved                                |

| 32  | SDC2_CLK   | 0   | -                     | Reserved                                |

| 33  | SDC2_CMD   | I/O |                       | Reserved                                |

| 34  | VDD_SDIO   | PO  |                       | Reserved                                |

| 35  | ANT_DIV    | 1   | -                     | Diversity antenna                       |

| 36  | GND        | G   | -                     | Ground                                  |

| 37  | SPI_CS_N   |     | -                     | Reserved                                |

| 38  | SPI_MOSI   | Ι   | -                     | Reserved                                |

| 39  | SPI_MISO   | 0   | -                     | Reserved                                |

| 40  | SPI_CLK    | 0   | -                     | Reserved                                |

| 41  | I2C_SCL    | OD  | -                     | I2C interface clock signal              |

| 42  | I2C_SDA    | OD  | -                     | I2C interface data signal               |

| 43  | NC         | -   | -                     | NC                                      |

| 44  | ADC1       | I   | -                     | Analog to digital converter interface   |

| 45  | ADC0       | I   | -                     | Analog to digital converter interface 0 |

| 46  | GND        | G   | -                     | Ground                                  |

| Pin | Pin Name | I/O | Level                                                     | Description                          |

|-----|----------|-----|-----------------------------------------------------------|--------------------------------------|

| 47  | ANT_GNSS | I   | -                                                         | GNSS antenna                         |

| 48  | GND      | G   | -                                                         | Ground                               |

| 49  | ANT_MAIN | I/O | -                                                         | Main antenna                         |

| 50  | GND      | G   | -                                                         | Ground                               |

| 51  | GND      | G   | -                                                         | Ground                               |

| 52  | GND      | G   | -                                                         | Ground                               |

| 53  | GND      | G   | -                                                         | Ground                               |

| 54  | GND      | G   | -                                                         | Ground                               |

| 55  | NC       | -   | -                                                         | NC                                   |

| 56  | GND      | G   | -                                                         | Ground                               |

| 57  | VBAT_RF  | I   | Vmax=4.3V<br>Vmin=3.3V<br>Vnorm=3.8V                      | RF power input (3.3V~4.3V)           |

| 58  | VBAT_RF  | I   | Vmax=4.3V<br>Vmin=3.3V<br>Vnorm=3.8V                      | RF power input (3.3V~4.3V)           |

| 59  | VBAT_BB  | I   | Vmax=4.3V<br>Vmin=3.3V<br>Vnorm=3.8V                      | Baseband power input (3.3V~4.3V)     |

| 60  | VBAT_BB  | I   | Vmax=4.3V<br>Vmin=3.3V<br>Vnorm=3.8V                      | Baseband Power Input (3.3V~4.3V)     |

| 61  | STATUS   | 0   | Voн <b>min=1.35</b> V<br>Vo∟max=0.45V                     | Reserved                             |

| 62  | RI       | 0   | Vol <b>max=0.45</b> V<br>Voнmin=1.35V                     | Module output ring indicator         |

| 63  | DCD      | 0   | Vot <b>max=0.45V</b><br>Voн <b>min=1.35V</b>              | Module output data carrier detection |

| 64  | CTS      | I   | Vı⊥min=-0.3V<br>Vı⊥max=0.6V<br>Vı⊦min=1.2V<br>Vı⊦max=2.0V | Clear to send                        |

| 65  | RTS      | 0   | Vol <b>max=0.45V</b><br>Voн <b>min=1.35V</b>              | Request to send                      |

| 66  | DTR      | I   | VILmin=-0.3V<br>VILmax=0.6V<br>VIHmin=1.2V                | Data ready                           |

| Pin    | Pin Name     | I/O | Level                                    | Description                       |

|--------|--------------|-----|------------------------------------------|-----------------------------------|

|        |              |     | Viнmax=2.0V                              |                                   |

| 67     | TXD          | 0   | Volmax=0.45V                             | Transmit data                     |

| 07     |              | 0   | Vон <b>min=1.35</b> V                    |                                   |

|        |              |     | V⊪min=-0.3V                              |                                   |

| 68     | RXD          | 1   | Vı⊥max=0.6V                              | Receive data                      |

|        |              |     | Vinmin=1.2V                              |                                   |

|        |              |     | Viнmax=2.0V                              |                                   |

| 69     | USB_DP       | I/O | Conform to USB2.0 standard specification | USB differential data bus (+)     |

|        |              |     | Conform to USB2.0                        |                                   |

| 70     | USB_DM       | I/O | standard specification                   | USB differential data bus (-)     |

|        |              |     | Vmax=5.25V                               |                                   |

| 71     | USB_VBUS     | I   | Vmin=3.0V                                | USB plug detection                |

|        | _            |     | Vnorm=5.0V                               |                                   |

| 72     | GND          | G   | -                                        | Ground                            |

| 73-112 | GND          | G   | -                                        | Ground                            |

| 113    | NC           |     |                                          | NC                                |

| 114    | NC           | -   | -                                        | NC                                |

|        |              |     | VILmin=-0.3V                             | Emergency download                |

| 115    | USB_BOOT     | I   | VILmax=0.6V                              | high level active                 |

| 110    | 036_6001     |     | VIHmin=1.2V                              | recommended to reserve test point |

|        |              |     | Vinmax=2.0V                              |                                   |

| 116    | NC           | -   |                                          | NC                                |

| 117    | NC           | -   |                                          | NC                                |

| 118    | WLAN&SDIO    | 1/0 |                                          | Reserved                          |

| 119    | EPHY_RST_N   | 0   |                                          | Reserved                          |

| 120    | EPHY_INT_N   |     |                                          | Reserved                          |

| 121    | SGMII_MDATA  | I/O |                                          | Reserved                          |

| 122    | SGMII_MCLK   | 0   |                                          | Reserved                          |

| 123    | SGMII_TX_M   | 0   |                                          | Reserved                          |

| 124    | SGMII_TX_P   | 0   |                                          | Reserved                          |

| 125    | SGMII_RX_P   | I   |                                          | Reserved                          |

| 126    | SGMII_RX_M   | Ι   |                                          | Reserved                          |

| 127    | PM_ENABLE    | -   |                                          | Reserved                          |

| 128    | VREG_L5_UIM2 | PO  |                                          | Reserved                          |

| 129    | SDC1_DATA_3  | I/O |                                          | Reserved                          |

| Pin | Pin Name      | I/O | Level | Description |

|-----|---------------|-----|-------|-------------|

| 130 | SDC1_DATA_2   | I/O |       | Reserved    |

| 131 | SDC1_DATA_1   | I/O |       | Reserved    |

| 132 | SDC1_DATA_0   | I/O |       | Reserved    |

| 133 | SDC1_CLK      | 0   |       | Reserved    |

| 134 | SDC1_CMD      | I/O |       | Reserved    |

| 135 | WAKE_WLAN     | 1   |       | Reserved    |

| 136 | WLAN_EN       | 1   |       | Reserved    |

| 137 | COEX_UART_RXD | T   |       | Reserved    |

| 138 | COEX_UART_TXD | I/O |       | Reserved    |

| 139 | BT_EN         | 1   |       | Reserved    |

| 140 | NC            | -   | -     | NC          |

| 141 | NC            | -   | -     | NC          |

| 142 | NC            | -   | -     | NC          |

| 143 | NC            | -   | -     | NC          |

| 144 | NC            | -   | -     | NC          |

#### Note:

Table 3-1 Pin Definitions

Keep the unused pins floating.

Pin73~Pin112 is the module thermal pad, and the corresponding ground pad is reserved for PCB

packaging and welded.

### 3.2 Power Supply

The power interfaces of NL668-AM module are shown in the following table:

| Pin Name | I/O | Pin                                       | Description                                       |

|----------|-----|-------------------------------------------|---------------------------------------------------|

| VBAT_RF  | L   | 57,58                                     | Module power supply, 3.3~4.3V, typical value 3.8V |

| VBAT_BB  | I   | 59,60                                     | Module power supply, 3.3~4.3V, typical value 3.8V |

| VDD_EXT  | 0   | 7                                         | Voltage Output, 1.8V, 80mA                        |

| GND      | -   | 8,9,10,19,22,36,46,48,5<br>0-54,56,72-112 | Ground                                            |

Note:

Table 3-2 Power Interfaces

In the rest of the document, VBAT\_BB, VBAT\_RF will be replaced with VBAT.

#### 3.2.1 Power supply

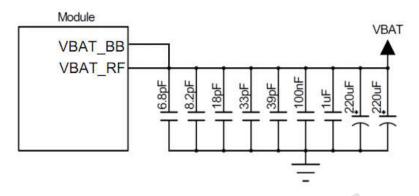

The NL668-AM module needs to be powered by the VBAT pin. The power design is shown in Figure 3-2:

Power filter capacitor design is shown in the following table:

| Recommended capacitor | Application                     | Description                      |

|-----------------------|---------------------------------|----------------------------------|

|                       |                                 | Reduce power fluctuations during |

|                       |                                 | module operation, requiring low  |

|                       |                                 | ESR Capacitor                    |

| 220uF x 2             | Regulating capacitor            | • LDO or DCDC power requires     |

|                       |                                 | not less than 440uF capacitor    |

|                       |                                 | Battery power can be properly    |

|                       |                                 | reduced to 100 ~ 220uF capacitor |

| 1                     | Disitel signal poiss            | Filter clock and digital signal  |

| 1uF,100nF             | Digital signal noise            | interference                     |

| 39pF,33pF             | 700, 850/900 MHz bands          | Filter low band RF interference  |

|                       | 1700/1800/1900,2100/2300,2500/2 | Filter middle/high band RF       |

| 18pF,8.2pF,6.8pF      | 600MHz bands                    | interference                     |

Table 3-3 Power Filter Capacitor Design

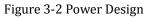

The power stability ensures the normal operation of NL668-AM module. The design requires special attention to the power ripple below 300mV(The circuit ESR < 100m $\Omega$ ). When the module is operating in WCDMA/LTE mode (Burst transmit), the maximum operating current can reach 2A, and the power voltage needs to be at least 3.3V. Otherwise, the module may power off or restart. The power limit is shown in Figure 3-3:

### 3.2.2 1.8V Output

The NL668-AM outputs a 1.8V voltage through the VDD\_EXT for use of the internal digital circuit of the module. The voltage is the logic level voltage of the module and can be used to indicate that the module is on or off, or for external low current (<80mA) circuit. If it is not in use, keep it in floating status. The logic level of VDD\_EXT is defined as follows:

| Parameter | Minimum | Typical | Maximum | Unit |

|-----------|---------|---------|---------|------|

| VDD_EXT   | 1.71    | 1.8     | 1.89    | V    |

Table 3-4 VDD\_EXT Logic Level

#### 3.2.3 Power consumption

The power consumption of NL668-AM module in the case of 3.8V power supply is shown in the following table.

| Parameter          | Mode      | Condition                      | Average<br>Typ.Current(mA) |

|--------------------|-----------|--------------------------------|----------------------------|

| I <sub>off</sub>   | Power off | Power supply, module power off | 0.015                      |

|                    | WCDMA     | DRX=8                          | ≤20                        |

| I <sub>ldle</sub>  | LTE FDD   | Paging cycle #256 frames       | ≤20                        |

|                    | Radio Off | AT+CFUN=4                      | ≤15                        |

|                    |           | DRX=6                          | ≤3                         |

| I <sub>sleep</sub> | WCDMA     | DRX=7                          | ≤3                         |

|                    |           | DRX=8                          | ≤3                         |

|                    |           | DRX=9                          | ≤3                         |

| Parameter              | Mode    | Condition                                | Average<br>Typ.Current(mA) |

|------------------------|---------|------------------------------------------|----------------------------|

|                        |         | Paging cycle #64 frames                  | ≤3                         |

|                        | FDD-LTE | Paging cycle #128 frames                 | ≤3                         |

|                        |         | Paging cycle #256 frames                 | ≤3                         |

|                        |         | WCDMA Data transfer Band II<br>@+23.5dBm | ≤630                       |

| I <sub>WCDMA-RMS</sub> | WCDMA   | WCDMA Data transfer Band IV<br>@+23.5dBm | ≤670                       |

|                        |         | WCDMA Data transfer Band V<br>@+23.5dBm  | ≤530                       |

|                        |         | LTE FDD Data transfer Band 2<br>@+23dBm  | ≤680                       |

|                        |         | LTE FDD Data transfer Band 4<br>@+23dBm  | ≤750                       |

|                        |         | LTE FDD Data transfer Band 5<br>@+23dBm  | ≤640                       |

|                        | LTE FDD | LTE FDD Data transfer Band 12<br>@+23dBm | ≤640                       |

| I <sub>LTE-RMS</sub>   |         | LTE FDD Data transfer Band 13<br>@+23dBm | ≤680                       |

|                        |         | LTE FDD Data transfer Band 17<br>@+23dBm | ≤680                       |

|                        |         | LTE FDD Data transfer Band 66<br>@+23dBm | ≤750                       |

|                        |         | LTE FDD Data transfer Band 71<br>@+23dBm | ≤680                       |

Table 3-5 Power Consumption

### 3.3 Control Signal

The NL668-AM module provides two control signals for power on/off and reset operations. The pin definitions are as follows.

| Pin name | I/O | Pin | Description                                                                                                                                        |

|----------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET_N  | I   | 20  | When the module is in work, give it a Tst (750ms~2s) low level, and then pull it high, the module is reset                                         |

| PWRKEY   | 1   | 21  | When module is in power off mode , give it a Tst (100ms~2s) low level,<br>and then pull it high, the module will power on; When module is in power |

| Pin name | I/O | Pin | Description                                                                        |

|----------|-----|-----|------------------------------------------------------------------------------------|

|          |     |     | on mode, give it a Tst (2s $\sim$ 8s) low level, and then pull it high, the module |

|          |     |     | will power off                                                                     |

Table 3-6 Control Signal

#### 3.3.1 Module power on

#### 3.3.1.1 power on circuit reference

When the NL668-AM module is in power off mode, the module will power on by pulling down PWRKEY for 100ms~ 2s . It is recommended to use OC/OD drive circuit to control PWRKEY pin. The reference circuit is shown in Figure 3-4:

Figure 3-4 OC/OD Drive Power on Reference Circuit

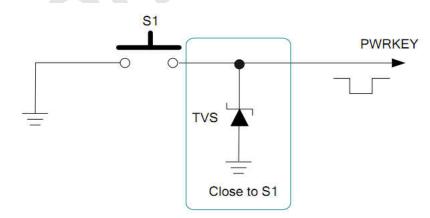

Another method to control PWRKEY pin is to directly control through a button, and place a TVS

(recommended : ESD9X5VL-2/TR) near the button for ESD protection.

The reference circuit is shown in Figure 3-5.

#### 3.3.1.2 Power on Timing

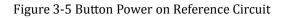

The power on timing is shown in Figure 3-6:

Figure 3-6 Power on Timing Control Diagram

Note:

Before pulling down the PWRKEY pin, make sure the VBAT voltage is stable. It is recommended that the interval between power up VBAT and pull down PWRKEY pin should not be less than 30ms.

### 3.3.2 Module power off

The module supports the following three power off modes:

| Power off mode           | Power off methods                                                 | Applicable scenarios                                                                                           |

|--------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Low-voltage power<br>off | When VBAT voltage is low or power down, the module will power off | The module does not power off through<br>normal process, i.e. does not logout<br>process from the base station |

| Hardware power off       | Pull down PWRKEY (2s~ 8s)                                         | Normal power off                                                                                               |

| AT power off             | AT+ CPWROFF                                                       | Software power off                                                                                             |

Table 3-7 Power Off Modes

#### 3.3.2.1 Power off Timing

1. When the module is working properly, do not cut off the power of the module immediately to avoid

damaging the internal Flash . It is strongly recommended to power off the module by PWRKEY or AT

command before cut off the power supply.

2. When using the AT command to power off, make sure that the PWRKEY is in a high level state after the power off command is executed, otherwise the module will power on again after the power off complete.

Figure 3-7 Power off Timing Control Diagram

#### 3.3.3 Module reset

NL668-AMmodule can reset by hardware and AT command.

| Reset mode | Reset method                                                |

|------------|-------------------------------------------------------------|

| Hardware   | Pull down RESET_N about 750ms~2s and then pull up the level |

| AT command | AT+RESET                                                    |

Table 3-8 Module Reset

#### 3.3.3.1 Reset circuit

Refer to Figure 3-8 reset circuit. It is similar to the PWRKEY control circuit. The client can control the RESET\_N pin using an OC/OD drive circuit or push button.

Figure 3-8 RESET\_N OC/OD Drive Reference Circuit

Another reset control is shown in Figure 3-9.

Figure 3-9 RESET\_N Button Reference Circuit

#### 3.3.3.2 RESET control Timing

Figure 3-10 Reset Control Timing

#### Note:

RESET is a sensitive signal, so it is recommended to add an avoid debouncing capacitor close to the module. In case of PCB layout, the RESET signal lines should keep away from the RF interference and protected by Ground. Also, the RESET signal lines shall neither near the PCB edge nor route on the surface planes( avoid module reset caused by ESD problems).

### 3.4 USB Interface

The NL668-AM module supports USB2.0 and is compatible with USB High-Speed (480Mbits/s) and USB Full-Speed (12Mbits/s). Refer to "Universal Serial Bus Specification 2.0" for the timing and electrical characteristics of the NL668-AM module USB bus.

#### 3.4.1 USB interface definition

| Pin name | I/O | Pin | Description                      |

|----------|-----|-----|----------------------------------|

| USB_DM   | I/O | 70  | USB differential data bus ( D+ ) |

| USB_DP   | I/O | 69  | USB differential data bus ( D- ) |

| USB_VBUS | PI  | 71  | USB_DET                          |

Table 3-9 USB Interface Definition

At present, USB just support USB\_VBUS detect.

For more information about the USB 2.0 specification, please refer to http://www.usb.org/home

#### Note:

Since the module supports USB 2.0 High-Speed, TVS tube equivalent capacitance on the USB\_DM/DP differential signal cable is required to be less than 1pF, and a 0.5pF capacitance TVS is recommended.

Connect a 0 ohm resistor to USB\_DM / DP differential line to help analyze problems.

USB\_DM and USB\_DP are high-speed differential signal cables, can achieve the maximum transmission rate of 480Mbits/s, and must follow the rules below in PCB Layout:

- USB\_DM and USB\_DP signal cable's control differential impedance is 90 ohm

- USB\_DM and USB\_DP signal cables shall be parallel and equal in length, and avoid the right-angle route;

- USB\_DM and USB\_DP signal cables are routed on the signal layer closest to the ground layer, and the cables shall be grounded;

### 3.5 USIM Interface

NL668-AM module has built-in USIM card interface, and supports 1.8V and 3.0V SIM card.

#### 3.5.1 USIM pin

USIM pin is shown in the following table:

| Pin name      | I/O | Pin | Description                       |

|---------------|-----|-----|-----------------------------------|

| USIM_DATA     | I/O | 15  | USIM/SIM DATA                     |

| USIM_CLK      | 0   | 16  | Clock Signal                      |

| USIM_RESET    | 0   | 17  | RESET Signal                      |

| USIM_VDD      | 0   | 14  | USIM/SIM Power                    |

| USIM_PRESENCE | I   | 13  | Detect USIM/SIM card for Hot-swap |

Table 3-10 SIM Card Pin

#### 3.5.2 USIM interface circuit

#### 3.5.2.1 SIM card slot with detection signal

USIM/SIM design requires the use of SIM card slot (Fibocom recommend: SIM016-8P-220P). We

recommend using hot plug slot with SIM\_DECTECT function.

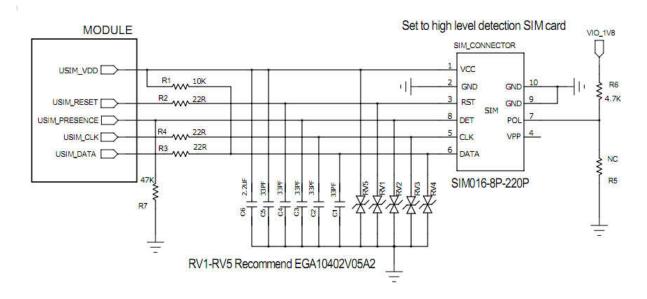

Figure 3-12 USIM/SIM Interface with Detection Signal Reference Design

Principles of SIM card slot with detection signal are as follows:

SIM card is insert, USIM\_PRESENCE pin is high level

SIM card is no insert, USIM\_PRESENCE pin is low level

#### 3.5.2.2 SIM card slot without detection signal

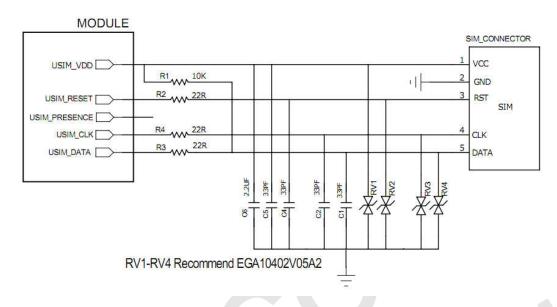

SIM card slot without detection signal, and USIM\_ PRESENCE pin remains floating.

Figure 3-13 USIM/SIM Interface without Detection Signal Reference Design Diagram

#### 3.5.3 USIM hot plug

NL668-AM SIM card supports hot plug function. It determines the insertion and removal of SIM card on the slot by detecting the USIM\_PRESENCE pin state to support hot plug function.

The SIM card hot plug function can be configured by the "AT+MSMPD" command, and the AT commands are shown in the following table:

| AT command | SIM card hot plug detection | Function description                                  |

|------------|-----------------------------|-------------------------------------------------------|

|            |                             | Default, SIM card hot plug detection is enabled       |

| AT+MSMPD=1 | Enabled                     | The module detects whether the SIM card is inserted   |

|            |                             | through the USIM_PRESENCE pin state                   |

|            |                             | SIM card hot plug detection function is disabled      |

| AT+MSMPD=0 | Disabled                    | The module reads the SIM card when the device starts, |

|            |                             | and does not detect the USIM_PRESENCE state           |

Table 3-11SIM Card Hot Plug Function Configured AT Commands

After enabled the hot plug detection function of the SIM card, when USIM\_PRESENCE is in high level, the module will detect the SIM card insertion and then execute the initialization program of the SIM card. After reading the SIM card information, the module will register network. When the USIM\_PRESENCE is in low level, the module detects that the SIM card is removed, then it will not read the SIM card.

#### Note:

The USIM\_PRESENCE is in active high by default, and can be switched to active low by AT command.

| AT command            | Function description       |  |

|-----------------------|----------------------------|--|

| AT+GTSET="SIMPHASE",1 | Default ,high level detect |  |

| AT+GTSET="SIMPHASE",0 | Low level detect           |  |

Table 3-12 USIM\_PRESENCE Effective Level Switched AT command

#### 3.5.4 USIM design requirements

SIM card circuit design shall meet EMC standards and ESD requirements, and at the same time, shall

improve anti-interference ability to ensure that the SIM card can work stably. The design needs to strictly

observe the following rules:

- SIM card slot is placed as close to the module as possible, away from the RF antenna, DCDC power, clock signal lines and other strong interference sources;