Perfect Wireless Experience 完美无线体验

# FIBOCOM N510-GL Hardware User Manual

Version: V1.0.0 Date: 2019-06-13

## **Applicability type**

| No. | Product model | Description                                         |  |

|-----|---------------|-----------------------------------------------------|--|

| 1   | N510-GL       | The manual is suitable for N510-GL series products. |  |

#### Copyright

Copyright ©2019 Fibocom Wireless Inc. All rights reserved.

Without the prior written permission of the copyright holder, any company or individual is prohibited to excerpt, copy any part of or the entire document, or transmit the document in any form.

#### **Notice**

The document is subject to update from time to time owing to the product version upgrade or other reasons. Unless otherwise specified, the document only serves as the user guide. All the statements, information and suggestions contained in the document do not constitute any explicit or implicit guarantee.

#### **Trademark**

The trademark is registered and owned by Fibocom Wireless Inc.

#### **Versions**

| Version | Author         | Assessor | Approver     | Update Date | Description     |

|---------|----------------|----------|--------------|-------------|-----------------|

| V1.0.0  | Wang yuanguang | Liuke    | Chenguojiang | 2019-06-13  | Initial Version |

#### **Contents**

| Co  | ntents    |           |                                    | 5  |

|-----|-----------|-----------|------------------------------------|----|

| Tab | ole Index |           |                                    | 9  |

| 1   | Forewo    | ord       |                                    | 10 |

|     | 1.1       | Intro     | duction                            | 10 |

|     | 1.2       | Safet     | y Instructions                     | 11 |

| 2   | Produc    | t Overv   | riew                               | 12 |

|     | 2.1       | Prod      | uct Introduction                   | 12 |

|     | 2.2       | Appli     | cation Diagram                     | 16 |

|     | 2.3       | Deve      | lopment Board                      | 16 |

| 3   | Pin Dis   | tributio  | n                                  | 17 |

|     | 3.1       | Pin D     | Distribution Chart                 | 17 |

|     | 3.2       | Pin F     | unction Description                | 17 |

| 4   | Work N    | /lode     |                                    | 22 |

|     | 4.1       | Off M     | lode                               | 22 |

|     | 4.2       | Stand     | dby Mode                           | 22 |

|     | 4.3       | Data      | Service                            | 23 |

|     | 4.4       | Low       | power mode                         | 23 |

| 5   | Electric  | cal Cha   | racteristics                       | 24 |

|     | 5.1       | Powe      | er Supply                          | 24 |

|     | 5.′       | 1.1 [     | Description of Power Pin           | 24 |

|     | 5.′       | 1.2 F     | Power Supply Design Requirements   | 24 |

|     | 5.2       | Elect     | rostatic Protection Capability     | 25 |

|     | 5.3       | Mode      | Power Consumption                  | 26 |

| 6   | Function  | onal Inte | erface                             | 30 |

|     | 6.1       | Cont      | rol Interface                      | 30 |

|     | 6.1       | 1.1 [     | Module Startup                     | 30 |

|     |           | 6.1.1     | .1 Explanation of switch pin       | 30 |

|     |           | 6.1.1     | .2 Startup Operation Requirements  | 30 |

|     |           | 6.1.1     | .3 Boot Time Sequence              | 31 |

|     | 6.1       | 1.2       | Module Shutdown                    | 31 |

|     |           | 6.1.2     | .1 Shutdown Operation Requirements | 31 |

|     |           | 6.1.2     | .2 Shutdown Mode                   | 32 |

|     |           | 6.1.2     | .3 Shutdown Time                   | 32 |

|     |           |           |                                    |    |

7

8

|     | 6.1.3     | Reset                                  | 33 |

|-----|-----------|----------------------------------------|----|

|     | 6.1       | .3.1 Reposition Pin Description        | 33 |

|     | 6.1       | .3.2 Instructions for the Use of Reset | 33 |

|     | 6.1.4     | Flight Mode                            |    |

| 6.2 | Ind       | licator Interface                      | 34 |

|     | 6.2.1     | Pin Description                        |    |

|     | 6.2.2     | Working State Indication               | 34 |

| 6.3 | Lov       | w Power Design                         | 40 |

|     | 6.3.1     | DRX                                    | 40 |

|     | 6.3.2     | eDRX                                   | 40 |

|     | 6.3.3     | PSM                                    | 41 |

| 6.4 | SIM       | M Card Interface                       | 35 |

|     | 6.4.1     | SIM Pin Description                    |    |

|     | 6.4.2     | SIM Interface Circuit                  |    |

|     | 6.4.3     | SIM Card Circuit Design Requirements   | 36 |

| 6.5 | UA        | \RT                                    | 36 |

|     | 6.5.1     | UART Pin Description                   | 36 |

|     | 6.5.2     | UART Interface Application             | 37 |

| 6.6 | 120       | D                                      |    |

| 6.7 | AD        | OC                                     |    |

|     | 6.7.1     | ADC Pin Description                    |    |

|     | 6.7.2     | ADC Instructions for Use               | 39 |

| RF  | Specifica | ations                                 | 43 |

| 7.1 | ope       | erating Frequency Band                 | 43 |

| 7.2 | Tra       | ansmission Power                       | 43 |

| 7.3 | Re        | ception Sensitivity                    | 44 |

| 7.4 | Co        | mmunication Antenna                    | 45 |

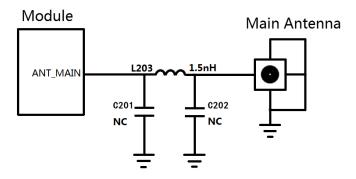

|     | 7.4.1     | Antenna Interface                      | 45 |

|     | 7.4.2     | Antenna Design Requirements            | 45 |

| 7.5 | RF        | PCB Design                             | 46 |

|     | 7.5.1     | Route Principle                        | 46 |

|     | 7.5.2     | Impedance Design                       | 47 |

| Rel | liability |                                        | 48 |

| 8.1 | Am        | nbient Temperature Range               | 48 |

|    | 8.2       | Environmental Reliability Requirements                  | . 48 |

|----|-----------|---------------------------------------------------------|------|

|    | 8.3       | ESD Design Requirements                                 | . 49 |

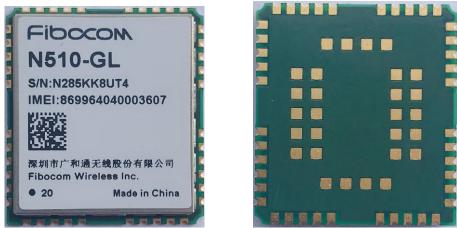

| 9  | Structura | al Specifications                                       | . 50 |

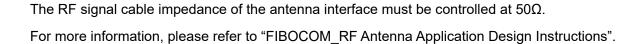

|    | 9.1       | Product Appearance                                      | . 50 |

|    | 9.2       | Structure Size                                          | . 50 |

|    | 9.3       | Packing                                                 | . 51 |

| 10 | Cer       | tification                                              | . 52 |

| 11 | Def       | ault Setting                                            | . 53 |

|    | 11.1      | Default Settings of UART                                | . 53 |

|    | 11.2      | Default Settings for Low Power Mode                     | . 53 |

|    | 11.3      | Inspection Function Default Setting of Plug-In SIM Card | . 53 |

|    | 11.4      | USB Default Settings                                    | . 53 |

| 12 | Ord       | er Information                                          | . 54 |

| 13 | Арр       | endix                                                   | . 55 |

|    | 13.1      | Terminology                                             | . 55 |

|    | 13.2      | Relevant Documents                                      | . 55 |

|    | 13.3      | Reference Standard                                      | . 56 |

|    | 13.4      | Contact Information                                     | . 56 |

# **Figure Index**

| Figure2-1 Application diagram                                     | 16    |

|-------------------------------------------------------------------|-------|

| Figure2-2 Hardware block diagram                                  | 16    |

| Figure3-1 Pin Distribution Map (TOP Plane Perspective)            | 17    |

| Figure5-1 Capacitance Combination Design of Power Supply Input    | 24    |

| Figure5-2 Power Supply Limitation                                 | 25    |

| Figure6-1 OC/OD Driver Reference Switch-on Circuit                | 30    |

| Figure6-2 Key Boot Reference Circuit                              | 31    |

| Figure6-3 Bootup Sequence Diagram                                 | 31    |

| Figure6-4 Hardware shutdown control sequence                      | 32    |

| Figure6-5 Reset control timing                                    | 33    |

| Figure6-6 SIM Card Reference Circuit with Detection Signal        | 35    |

| Figure6-7 Diagram of UART Signal Connection between Module and Mo | CU 37 |

| Figure6-8 Module and MCU UART Level Conversion Circuit            | 38    |

| Figure7-1 Current Diagram of PSM Working Time                     | 41    |

| Figure7-2 AT instruction description entering PSM mode            | 41    |

| Figure8-1 Modular Antenna Pi Circuit                              | 46    |

| Figure10-1 Module Appearance Diagram                              | 50    |

| Figure 10-2 N510-GL structural dimensions                         | 50    |

# **Table Index**

| Table2-1   | Product Specifications                                                            | 12   |

|------------|-----------------------------------------------------------------------------------|------|

| Table3-1   | N510-GL Pin Definitions                                                           | 17   |

| Table3-2   | I/O parameter description                                                         | 20   |

| Table4-1   | N510-GL Mode of Work                                                              | 22   |

| Table5-1   | Definition of External Power Supply Interface Pin for Module                      | 24   |

| Table5-2 ( | Capacitance Design Description of External Power Supply Circuit                   | 24   |

| Table5-5   | Explanation of electrostatic protection capability of module pins (temperature: 2 | 25℃, |

| humid      | dity: 45%)                                                                        | 26   |

| Table5-6 N | Module Power Statistics Table                                                     | 26   |

| Table6-1   | Definition of Switch Interface Pin                                                | 30   |

| Table6-2   | Shutdown Mode                                                                     | 32   |

| Table6-3 F | Reposition pin description                                                        | 33   |

| Table6-4 I | nstructions for Interface Pins of Indicators                                      | 34   |

| Table6-5   | Description of the Working State of Indicator Lamp                                | 34   |

| Table6-6 F | PSM Timer Configuration Correspondence Table                                      | 42   |

| Table6-7 N | Module SIM Card Pin Description                                                   | 35   |

| Table8-1   | Description of working frequency band of module                                   | 43   |

| Table8-2   | Explanation of Transmitting Power of Modules in Each Frequency Band               | 43   |

| Table8-3   | Description of Line Interface Pins                                                | 45   |

| Table8-4   | Modular Antenna Design Requirements                                               | 45   |

| Table9-1   | Ambient Temperature Range for Module Operation                                    | 48   |

| Table9-2   | Environmental Reliability Requirements for Module Work                            | 48   |

| Table13-1  | Order Information Table for N510-GL Products                                      | 54   |

| Table14-1  | Documents on Terminology                                                          | 55   |

# 1 Foreword

This paper describes the electrical characteristics, RF performance, structure size and application environment of N510-GL module. With the help of this document and other related documents, developers can guickly understand the hardware functions of N510-GL module and develop products.

#### 1.1 Introduction

This product is designed with reference to the following criteria:

- 3GPP TS 36.521-1 R13: User Equipment (UE) conformance specification; Radio transmission and reception; Part 1: Conformance testing

- 3GPP TS 36.521-1 V14.5.0 \*R14: User Equipment (UE) conformance specification; Radio transmission and reception; Part 1: Conformance testing

- 3GPP TS 21.111 V10.0.0: USIM and IC card requirements

- 3GPP TS 51.011 V4.15.0: Specification of the Subscriber Identity Module -Mobile Equipment (SIM-ME) interface

- 3GPP TS 31.102 V10.11.0: Characteristics of the Universal Subscriber Identity Module (USIM) application

- 3GPP TS102.223 V07.06.0: Universal Subscriber Identity Module (USIM) Application Toolkit(USAT)

Cooperating with the following documents will help us to better understand and use this product:

- N510-GL Family AT Command Manual

- Fibocom N510-GL LCC+LGA SMT Application Design Description

- ADP-N510 Instruction Manual

## 1.2 Safety Instructions

By following the following safety principles, personal safety can be ensured and products and work environments can be protected from potential damage. The product manufacturer needs to communicate the following safety instructions to the end user. If these safety rules are not complied with, Fibocom will not bear any responsibility for the consequences of user misuse.

Road safety first! When you drive, do not use handheld mobile devices, even if they have hands-free functions.

Please stop before you call!

Please close the mobile terminal before boarding. The wireless function of the mobile terminal is prohibited from opening on the aircraft to prevent interference to the aircraft communication system. Ignorance of this prompt may lead to flight safety and even violation of the law.

When in hospitals or health care settings, please pay attention to whether there are restrictions on the use of mobile devices. Radio frequency interference may cause malfunction of medical equipment, so it may be necessary to turn off mobile terminal equipment.

Mobile terminal devices do not guarantee effective connection under any circumstances, such as when mobile terminal devices are not charged or (U) SIM is invalid. When you encounter these situations in an emergency, remember to use emergency calls, while ensuring that your device is on and in an area with sufficient signal strength.

Your mobile terminal device receives and transmits radio frequency signals at boot time. Radio Frequency Interference (RFI) occurs when it is close to TV, radio, computer or other electronic devices.

Please keep mobile terminal equipment away from flammable gas. Close the mobile terminal when you are near the gas station, oil depot, chemical plant or explosion workplace. Operating electronic equipment in any potentially explosive dangerous place has potential safety hazards.

## 2 Product Overview

#### 2.1 Product Introduction

N510-GL is a highly integrated NB-IoT wireless communication module, which supports the R13 standard of NB-IoT specification. The product specifications of N510-GL are as follows:

**Table2-1 Product Specifications**

| Specifications    |                                                                       |  |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------|--|--|--|--|--|--|

| Operating Band    | Band 1,2,3,4,5,8,12,13,17,18,19,20,25,26*,28,66,71,85                 |  |  |  |  |  |  |

|                   | Single-tone UL: 15.6kbps  Multi-tone UL: 62.5kbps, DL: 26.15kbps      |  |  |  |  |  |  |

| Data Transmission | R14* Single-tone UL: 18.1kbps Multi-tone UL:158.5Kbps DL/126.8Kbps UL |  |  |  |  |  |  |

| Power             | DC:3.3V~5V (3.8V DC power supply is recommended)                      |  |  |  |  |  |  |

|                   | Operating temperature: -30°C~+75°C①                                   |  |  |  |  |  |  |

| Temperature       | Extended temperature: -40°C~+85°C②                                    |  |  |  |  |  |  |

|                   | Storage: -40°C~+90°C                                                  |  |  |  |  |  |  |

| Physical          | Package: LCC 42pin+LGA 28pin                                          |  |  |  |  |  |  |

| Characteristics   | Dimension: 22.2 x 20.2 x 2.1 mm                                       |  |  |  |  |  |  |

| Onaraciensies     | Weight:1.6g                                                           |  |  |  |  |  |  |

| Interface         |                                                                       |  |  |  |  |  |  |

| Antenna           | Antenna x 1                                                           |  |  |  |  |  |  |

| Functional        | USIM 1.8V/3.0V                                                        |  |  |  |  |  |  |

| Interface         | 2 wire UART x 2, 4 wire UART x 1                                      |  |  |  |  |  |  |

| interface         | EINT、I2C、GPIO、System Indicator、ADC                                    |  |  |  |  |  |  |

| Software          |                                                                       |  |  |  |  |  |  |

| Protocol Stack    | Embedded TCP/IP and UDP/IP protocol stack                             |  |  |  |  |  |  |

| AT Command        | 3GPP TS 27.007 and 27.005, and proprietary FIBOCOM AT                 |  |  |  |  |  |  |

| Firmware update   | UART                                                                  |  |  |  |  |  |  |

#### Remarks:

- 1.<sup>①</sup>It represents that the module can work normally in this temperature range, and the related performance meets the requirements of 3GPP standard.

- 2.<sup>2</sup>It indicates that the module can work normally in this temperature range and the baseband RF function is normal, but individual RF indicators may exceed the standard range of 3GPP. When the temperature returns to the normal working range of the module, the indicators of the

module will still meet the standard of 3GPP.

3.\* B26 software is closed

NB1 Band: 1/2/3/4/5/8/12/13/17/18/19/20/25/26\*/28/66/71/85 Max power 23dBm

#### Restriction of Hazardous Substances Directive (RoHS)

**European Union**

FIBOCOM products sold in the European Union, on or after 3 January 2013 meet the requirements of Directive 2011/65/EU on the restriction of the use of certain hazardous substances in electrical and electronic equipment ("RoHS recast" or "RoHS 2").

#### uropean Union compliance statement

CE

European Union conformity The following information is applicable to mobile devices that carry a CE mark.

#### **EU Regulatory Conformance**

Hereby, We, Manufacturer (Fibocom Wireless Inc.) declares that the radio equipment type N510-GL is in compliance with

the Directive 2014/53/EU.

In all cases assessment of the final product must be mass against the Essential requirements of the Directive 2014/53/EU Articles 3.1(a) and (b), safety and EMC respectively, as well as any relevant Article

#### RF exposure

This product meets the applicable national or international RF exposure guidance

(EN62133) At normal use, the device is at least 20cm away from the human body. The RF exposure guidance includes a considerable safety margin designed to assure the safety of all persons, regardless of age and health.

#### FCC Certification Requirements.

According to the definition of mobile and fixed device is described in Part 2.1091(b), this device is a mobile device.

And the following conditions must be met:

- 1. This Modular Approval is limited to OEM installation for mobile and fixed applications only. The antenna installation and operating configurations of this transmitter, including any applicable source-based timeaveraging

- duty factor, antenna gain and cable loss must satisfy MPE categorical Exclusion Requirements of 2.1091.

- 2. The EUT is a mobile device; maintain at least a 20 cm separation between the EUT and the user's body and must not transmit simultaneously with any other antenna or transmitter.

- 3.A label with the following statements must be attached to the host end product: This device contains FCC ID: ZMON510GL

- 4.To comply with FCC regulations limiting both maximum RF output power and human exposure to RF radiation, maximum antenna gain (including cable loss) must not exceed:

| Operating Band  | FCC Max Antenna Gain(dBi) |

|-----------------|---------------------------|

| LTE NB1 BAND 2  | 9.00                      |

| LTE NB1 BAND 4  | 6.00                      |

| LTE NB1 BAND 5  | 10.41                     |

| LTE NB1 BAND 12 | 9.69                      |

| LTE NB1 BAND 13 | 10.15                     |

| LTE NB1 BAND 17 | 9.72                      |

| LTE NB1 BAND 25 | 9.00                      |

| LTE NB1 BAND 66 | 6                         |

| LTE NB1 BAND 71 | 9.46                      |

| LTE NB1 BAND 85 | 9.69                      |

- 5. This module must not transmit simultaneously with any other antenna or transmitter

- 6. The host end product must include a user manual that clearly defines operating requirements and conditions that must be observed to ensure compliance with current FCC RF exposure guidelines. For portable devices, in addition to the conditions 3 through 6 described above, a separate approval is required to satisfy the SAR requirements of FCC Part 2.1093

If the device is used for other equipment that separate approval is required for all other operating configurations, including portable configurations with respect to 2.1093 and different antenna configurations.

For this device, OEM integrators must be provided with labeling instructions of finished products. Please refer to KDB784748 D01 v07, section 8. Page 6/7 last two paragraphs:

A certified modular has the option to use a permanently affixed label, or an electronic label. For a

permanently affixed label, the module must be labeled with an FCC ID - Section 2.926 (see 2.2 Certification (labeling requirements) above). The OEM manual must provide clear instructions explaining to the OEM the labeling requirements, options and OEM user manual instructions that are required (see next paragraph).

For a host using a certified modular with a standard fixed label, if (1) the module's FCC ID is not visible when installed in the host, or (2) if the host is marketed so that end users do not have straightforward commonly used methods for access to remove the module so that the FCC ID of the module is visible; then an additional permanent label referring to the enclosed module: "Contains Transmitter Module FCC ID: ZMON510GL" or "Contains FCC ID: ZMON510GL" must be used. The host OEM user manual must also contain clear instructions on how end users can find and/or access the module and the FCC ID.

The final host / module combination may also need to be evaluated against the FCC Part 15B criteria for unintentional radiators in order to be properly authorized for operation as a Part 15 digital device. The user's manual or instruction manual for an intentional or unintentional radiator shall caution the user that changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment. In cases where the manual is provided only in a form other than paper, such as on a computer disk or over the Internet, the information required by this section may be included in the manual in that alternative form, provided the user can reasonably be expected to have the capability to access information in that form.

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions:

(1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

Changes or modifications not expressly approved by the manufacturer could void the user's authority to operate the equipment.

To ensure compliance with all non-transmitter functions the host manufacturer is responsible for ensuring compliance with the module(s) installed and fully operational. For example, if a host was previously authorized as an unintentional radiator under the Supplier's Declaration of Conformity procedure without a transmitter certified module and a module is added, the host manufacturer is responsible for ensuring that the after the module is installed and operational the host continues to be compliant with the Part 15B unintentional radiator requirements.

#### Manual Information To the End User

The OEM integrator has to be aware not to provide information to the end user regarding how to install or remove this RF module in the user's manual of the end product which integrates this module. The end user manual shall include all required regulatory information/warning as show in this manual.

# 2.2 Application Diagram

Figure2-2 Hardware block diagram

# 2.3 Development Board

ADP-N510 is a development board for debugging of N510-GL module. With this development board, we can quickly master module functions and complete basic function testing. Refer to ADP-N510 Instructions for the Specific Use of Development Board.

# 3 Pin Distribution

# 3.1 Pin Distribution Chart

# 3.2 Pin Function Description

The pin definitions of the N510-GL module are as follows:

Table3-1 N510-GL Pin Definitions

| PIN   | PIN Name   | I/O | PIN Description                                   | DC Characteristics | Note                                     |

|-------|------------|-----|---------------------------------------------------|--------------------|------------------------------------------|

| 1     | GND        |     | GND                                               | -                  |                                          |

| 2     | GND        |     | GND                                               | -                  |                                          |

| 3     | RF ANT     | I/O | Antenna                                           | -                  |                                          |

| 4     | GND        | -   | GND                                               | -                  |                                          |

| 5     | GND        | -   | GND                                               | -                  |                                          |

| 6     | NC         | -   | -                                                 | -                  | keep it open                             |

| 7     | GND        | -   | GND                                               | -                  |                                          |

| 8     | GND        | -   | GND                                               | -                  |                                          |

| 9     | VBAT       | PI  | Power supply for                                  | 3.8V(3.3V-5V)      |                                          |

|       |            |     | module                                            |                    |                                          |

| 10    | VBAT       | PI  | Power supply for module                           | 3.8V(3.3V-5V)      |                                          |

| 11-12 | NC         | _   | -                                                 | _                  | keep it open                             |

| 13    | VDD        | РО  | Power supply for external GPIO's pull up circuits | 2.8V               | If the pin is<br>unused, keep<br>it open |

| 14    | POWER_ON_N | 1   | POWER_ON                                          | 3.3V               |                                          |

| PIN   | PIN Name    | I/O | PIN Description      | DC Characteristics | Note          |

|-------|-------------|-----|----------------------|--------------------|---------------|

|       |             |     | UART1 Terminal       |                    | If the pin is |

| 15    | UART1_DTR*  | 1   | Ready, Can Reusable  | 2.8V               | unused, keep  |

|       |             |     | for GPIO             |                    | it open       |

|       |             |     | UART1 Data Set       |                    | If the pin is |

| 16    | UART1_DSR*  | 0   | Ready, Can Reusable  | 2.8V               | unused, keep  |

|       |             |     | for GPIO             |                    | it open       |

|       |             |     | UART1 Data Carrier   |                    | If the pin is |

| 17    | UART1_DCD*  | 0   | Detect, Can Reusable | 2.8V               | unused, keep  |

|       |             |     | for GPIO             |                    | it open       |

|       |             |     |                      |                    | If the pin is |

| 18    | UART1_RXD   | ļ   | UART1_RXD            | 2.8V               | unused, keep  |

|       |             |     |                      |                    | If the pin is |

| 19    | UART1_TXD   | 0   | UART1_TXD            | 2.8V               | unused, keep  |

|       |             |     |                      |                    | it open       |

|       |             |     |                      |                    | If the pin is |

| 20    | UART1_RTS   | 0   | UART1_RTS            | 2.8V               | unused, keep  |

|       | _           |     | _                    |                    | it open       |

|       |             |     |                      |                    | If the pin is |

| 21    | UART1 CTS   | 1   | UART1_CTS            | 2.8V               | unused, keep  |

|       | _           |     | _                    |                    | it open       |

|       |             |     | UART1 Ring           |                    | If the pin is |

| 22    | UART1 RING* | I/O | indicator ,Can       | 2.8V               | unused, keep  |

|       | _           |     | Reusable for GPIO    |                    | it open       |

| 23    | SIM SIO     | I/O | SIM DATA             | 1.8/3V             |               |

| 24    | SIM SCLK    | 0   | SIM SCL              | 1.8/3V             |               |

| 25    | SIM SRST    | 0   | SIM RST              | 1.8/3V             |               |

| 26    | VSIM        | РО  | VSIM                 | 1.8/3V             |               |

|       |             |     |                      |                    | If the pin is |

| 27    | SIM_DET     | I   | SIM_DET              | 2.8V               | unused, keep  |

|       |             |     |                      |                    | it open       |

| 28-31 | NC          | _   | -                    | -                  | keep it open  |

| 32    | GND         | -   | GND                  | -                  | -             |

| 33-36 | NC          | -   | -                    | -                  | keep it open  |

| PIN   | PIN Name  | I/O | PIN Description | DC Characteristics | Note          |

|-------|-----------|-----|-----------------|--------------------|---------------|

|       |           |     |                 |                    | If the pin is |

| 37    | RESET     | I   | RESET           |                    | unused, keep  |

|       |           |     |                 | 3.3V               | it open       |

|       |           |     |                 |                    | If the pin is |

| 38    | LPG       | 0   | LPG             |                    | unused, keep  |

|       |           |     |                 | 2.8V               | it open       |

|       |           |     |                 |                    | If the pin is |

| 39    | UART2_RXD | I   | UART2_RXD       |                    | unused, keep  |

|       |           |     |                 | 2.8V               | it open       |

| 40    |           |     |                 |                    | If the pin is |

| 40    | UART2_TXD | 0   | UART2_TXD       | 2.8V               | unused, keep  |

|       |           |     |                 |                    | If the pin is |

| 41    | WAKEUP_IN | 1   | WAKEUP_IN       |                    | unused, keep  |

|       |           |     |                 | 2.8V               | it open       |

| 42-51 | GND       | -   | GND             | -                  |               |

|       |           |     |                 |                    | If the pin is |

| 52    | I2C_SDA   | I/O |                 | 2.8V               | unused, keep  |

|       |           |     |                 |                    | it open       |

| 53    | NC        |     | -               | -                  | keep it open  |

|       |           |     |                 |                    | If the pin is |

| 54    | GPIO1     |     | -               | -                  | unused, keep  |

|       |           | -   |                 |                    | it open       |

| 55    | GND       | -   | GND             | -                  |               |

|       |           |     |                 |                    | If the pin is |

| 56    | I2C_SCL   | 0   |                 | 2.8V               | unused, keep  |

|       |           |     |                 |                    | it open       |

| 57    | GND       | _   | GND             | -                  |               |

|       |           |     |                 |                    | If the pin is |

| 58    | GPIO2     | _   | -               | -                  | unused, keep  |

|       |           |     |                 |                    | it open       |

| PIN | PIN Name   | I/O | PIN Description                              | DC Characteristics | Note                                     |

|-----|------------|-----|----------------------------------------------|--------------------|------------------------------------------|

| 59  | ADC1       | ı   | General purpose analog to digital            | -                  | If the pin is<br>unused, keep<br>it open |

| 60  | GND        | -   | GND                                          | -                  |                                          |

| 61  | WAKEUP_OUT | 0   | Wakeup HOST                                  | 2.8V               | If the pin is<br>unused, keep<br>it open |

| 62  | GPIO3      | -   | -                                            | -                  | If the pin is<br>unused, keep<br>it open |

| 63  | GND        | -   | GND                                          | -                  |                                          |

| 64  | ADC0       | ı   | General purpose analog to digital converter. | 1.4V               | If the pin is<br>unused, keep<br>it open |

| 65  | GND        | -   | GND                                          | -                  |                                          |

| 66  | GND        | -   | GND                                          | -                  |                                          |

| 67  | GND        | -   | GND                                          | -                  |                                          |

| 68  | GND        | -   | GND                                          | -                  |                                          |

| 69  | GPIO4      | -   | -                                            | -                  | If the pin is<br>unused, keep<br>it open |

| 70  | GND        | -   | GND                                          | -                  |                                          |

I/O parameter description:

Table3-2 I/O parameter description

| I/O Parameter | Description             |

|---------------|-------------------------|

| Ю             | Bidirectional interface |

| PI            | Power input             |

| РО            | Power output            |

| I             | Input                   |

| 0             | Output                  |

| *             | TBD                     |

#### Remarks:

The I/O interface power domain of the module defaults to 2.8V, and the power domain of ADC is

1.4V.

# 4 Work Mode

N510-GL provides the following four working modes.

Table4-1 N510-GL Mode of Work

| Working mode      | Describe                                                                                                                                          | Characteristic                                                                                                                                                                                                                              |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Off Mode          | the power supply of Vbat is on, but the module is power off.                                                                                      | The module is shut down.                                                                                                                                                                                                                    |

| Standby Mode      | The module is powered on and the VDD outputs 2.8V voltage. The LPG signal lamp pin state is slow flash (70ms low level/3000ms high level).        | The module is fully started, and has been registered on the network, ready to communicate at any time. This is the default mode of operation after the module is booted.                                                                    |

| Data Service      | Module boot-up and successful network injection and data communication. The LPG signal lamp operates as a flash (70ms low level/70ms high level). | The module is transmitting data.  When the transmission is over, the module returns to standby or low power mode.                                                                                                                           |

| Low Power<br>Mode | The AT command enables the module to enter a low power mode.                                                                                      | The module serial communication in DRX mode is normal, while the serial communication in PSM and eDRX mode is closed. In low power mode, the module is still registered on the network and does not need to be re-attached after waking up. |

## 4.1 Off Mode

The module needs to provide 3.3V-5V DC power supply through the VBAT pin. The module can turn on power by control POWER\_ON pin.

## 4.2 Standby Mode

The module is powered on and the VDD outputs 2.8V voltage, which can be operated by AT command through serial port. Has registered on the network, no business processing, can communicate at any time, this is the default mode of operation after the module boots.

#### 4.3 Data Service

The module boots up and successfully injects the network for business transmission. The LPG signal lamp indicates the working state. The AT instruction can be operated through the serial port, and the module carries out data transmission. When the transmission is over, the module returns to standby or low power mode.

## 4.4 Low power mode

The module is powered on and successfully injected into the network for business transmission. After that, the AT command operation control module enters the low power mode, or the module is in standby state for a long time, the module will enter the low power mode.

# 5 Electrical Characteristics

## 5.1 Power Supply

## 5.1.1 Description of Power Pin

The power interface of the N510-GL module is shown in the following table:

Table5-1 Definition of External Power Supply Interface Pin for Module

|      |          |     |                   | DC Parameter (V) |           |         |

|------|----------|-----|-------------------|------------------|-----------|---------|

| Pin  | Pin Name | I/O | Pin Description   | Minimum          | Typical   | Maximum |

|      |          |     |                   | Value            | Value     | Value   |

| 9,10 | VBAT     | PI  | Power input       | 3.3V             | 3.8V      | 5V      |

| 13   | VDD      | РО  | 2.8V power output | 2.6V             | 2.8V      | 3-      |

| 26   | VSIM     | РО  | SIM power supply  | -                | 1.8V/3.0V | -       |

## **5.1.2 Power Supply Design Requirements**

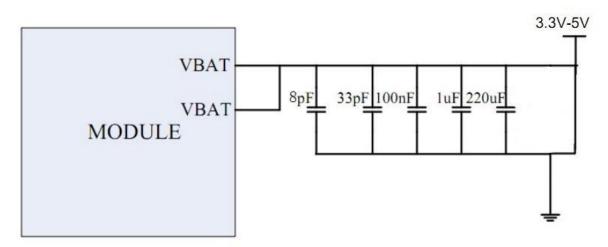

N510-GL module needs to supply power through VBAT pin. In order to ensure the stability of power supply, it needs to use capacitance to filter DC power supply. The specific design is shown in Fig. 5-1.

Figure 5-1 Capacitance Combination Design of Power Supply Input Capacitance combination design for power supply is described in the following table:

Table5-2 Capacitance Design Description of External Power Supply Circuit

| Recommended Capacitor | Function                       | Instruction                                                                                                                        |

|-----------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 220uF x 2             | Voltage stabilizing capacitor  | Low ESR capacitance is required to reduce power fluctuation when the module is working.  No less than 440uF capacitor is required. |

| 1uF、100nF             | Digital Signal Noise           | Eliminate interference from clocks and digital signals                                                                             |

| 33pF、8pF              | 900,1800 MHz<br>Frequency Band | Elimination of Low and Medium Frequency Radio Frequency Interference                                                               |

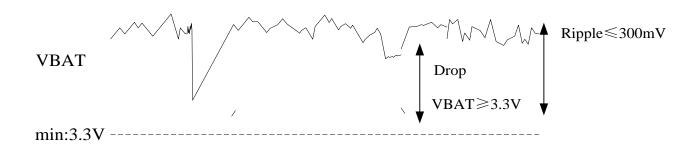

The stability of the power supply can ensure the normal operation of the N510-GL module. Special attention should be paid to the ripple of the power supply less than 300 mV in the design. When the module works, it is necessary to ensure that the DC power supply voltage is not less than 3.3V and not higher than 3.8V. The power supply limitation is shown in Figure 5-2.

Figure 5-2 Power Supply Limitation

Schematic design: it is necessary to stabilize and filter the power supply to ensure the power supply stability of the module.

PCB design: Ensure that the external power supply to VBAT is wide enough. It is suggested that the width of VBAT should be more than 1 mm and the small capacitance should be placed close to the module.

# 5.2 Electrostatic Protection Capability

ESD protection should be considered in the design of N510-GL module. The anti-static capability of the module pin is limited. The key input/output signal interface must be anti-static. The anti-static capability of the equipment can be improved by reasonable structure design and PCB layout design to ensure that the metal shield shell is completely grounded. The ESD voltage withstanding of the module pin is as follows:

Table5-3 Explanation of electrostatic protection capability of module pins (temperature: 25℃, humidity: 45%)

| Test Location                   | Test Method                                               | Contact<br>Discharge | Air<br>Discharge | Unit |

|---------------------------------|-----------------------------------------------------------|----------------------|------------------|------|

| Other interfaces                | Contact and non-contact testing with an electrostatic gun | ±1                   | ±2               | KV   |

| Antenna core and antenna ground | Contact and non-contact testing with an electrostatic gun | ±8                   | ±15              | KV   |

# 5.3 Mode Power Consumption

In the case of 3.8V power supply, the power consumption of the N510-GL module is shown in the following table:

Table5-4 Module Power Statistics Table

| Param               | Pattern | Describe      |                                           | Typical Value |

|---------------------|---------|---------------|-------------------------------------------|---------------|

| eter                |         |               |                                           |               |

|                     | DRX     | 2.56s         |                                           | 2.1mA         |

| Isleep              | eDRX    | 20.48s        |                                           | 154uA         |

|                     | PSM     | Sleep mode    |                                           | 2.7uA         |

|                     |         |               | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 117 mA        |

|                     | Active  | Active BAND 2 | RF Transmit mode, NB-LTE 3.75KHz,23dBm    | 184 mA        |

|                     |         |               | RF Receive mode                           | 19.4 mA       |

| I <sub>active</sub> |         |               | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 115 mA        |

|                     |         |               | RF Transmit mode, NB-LTE<br>3.75KHz,23dBm | 180 mA        |

|                     |         |               | RF Receive mode                           | 19.4 mA       |

|                     |         | BAND 3        | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 115 mA        |

| Param eter | Pattern | Describe        |                                           | Typical Value |

|------------|---------|-----------------|-------------------------------------------|---------------|

|            |         |                 | RF Transmit mode, NB-LTE<br>3.75KHz,23dBm | 183 mA        |

|            |         |                 | RF Receive mode                           | 19.4 mA       |

|            |         |                 | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 113 mA        |

|            |         | BAND 4          | RF Transmit mode, NB-LTE<br>3.75KHz,23dBm | 174 mA        |

|            |         |                 | RF Receive mode                           | 19.4 mA       |

|            |         |                 | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 135 mA        |

|            |         | BAND 5          | RF Transmit mode, NB-LTE<br>3.75KHz,23dBm | 201 mA        |

|            |         |                 | RF Receive mode                           | 19.4 mA       |

|            | Active  | BAND 8  BAND 12 | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 120 mA        |

|            |         |                 | RF Transmit mode, NB-LTE<br>3.75KHz,23dBm | 190 mA        |

|            |         |                 | RF Receive mode                           | 19.4 mA       |

|            |         |                 | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 130 mA        |

| lactive    |         |                 | RF Transmit mode, NB-LTE<br>3.75KHz,23dBm | 198 mA        |

|            |         |                 | RF Receive mode                           | 19.4 mA       |

|            |         |                 | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 146 mA        |

|            |         | BAND 13         | RF Transmit mode, NB-LTE 3.75KHz,23dBm    | 226 mA        |

|            |         |                 | RF Receive mode                           | 19.4 mA       |

|            |         | Band 17         | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 130 mA        |

| Param eter          | Pattern | Describe |                                           | Typical Value |

|---------------------|---------|----------|-------------------------------------------|---------------|

|                     |         |          | RF Transmit mode, NB-LTE<br>3.75KHz,23dBm | 191 mA        |

|                     |         |          | RF Receive mode                           | 19.4 mA       |

|                     |         |          | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 140 mA        |

|                     |         | Band 18  | RF Transmit mode, NB-LTE<br>3.75KHz,23dBm | 215 mA        |

|                     | Active  |          | RF Receive mode                           | 19.4 mA       |

|                     |         |          | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 134 mA        |

|                     |         | Band 19  | RF Transmit mode, NB-LTE<br>3.75KHz,23dBm | 208 mA        |

|                     |         |          | RF Receive mode                           | 19.4 mA       |

|                     |         |          | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 132 mA        |

|                     |         | Band 20  | RF Transmit mode, NB-LTE<br>3.75KHz,23dBm | 202 mA        |

|                     |         |          | RF Receive mode                           | 19.4 mA       |

|                     |         |          | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 112 mA        |

|                     |         | Band 25  | RF Transmit mode, NB-LTE<br>3.75KHz,23dBm | 173 mA        |

| l <sub>active</sub> | Active  |          | RF Receive mode                           | 19.4 mA       |

|                     |         | Band 28  | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 130 mA        |

|                     |         |          | RF Transmit mode, NB-LTE 3.75KHz,23dBm    | 200 mA        |

|                     |         |          | RF Receive mode                           | 19.4 mA       |

|                     |         | Band 66  | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 113 mA        |

| Param eter | Pattern | Describe |                                           | Typical Value                             |        |

|------------|---------|----------|-------------------------------------------|-------------------------------------------|--------|

|            |         |          | RF Transmit mode, NB-LTE<br>3.75KHz,23dBm | 176 mA                                    |        |

|            |         |          | RF Receive mode                           | 19.4 mA                                   |        |

|            |         |          | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 121 mA                                    |        |

|            | Active  | Band 71  | Band 71                                   | RF Transmit mode, NB-LTE<br>3.75KHz,23dBm | 191 mA |

|            |         |          | RF Receive mode                           | 19.4 mA                                   |        |

| lactive    |         |          | RF Transmit mode, NB-LTE<br>15KHz,23dBm   | 120 mA                                    |        |

|            |         | Band 85  | RF Transmit mode, NB-LTE 3.75KHz,23dBm    | 190 mA                                    |        |

|            |         |          | RF Receive mode                           | 19.4 mA                                   |        |

|            |         |          |                                           |                                           |        |

|            |         |          |                                           | -                                         |        |

|            |         |          |                                           |                                           |        |

# **6 Functional Interface**

#### 6.1 Control Interface

## 6.1.1 Module Startup

#### 6.1.1.1 Explanation of switch pin

N510-GL module switch pins are defined as follows:

Table6-1 Definition of Switch Interface Pin

| PIN | Pin Name | I/O | Pin Description | Power Domain (TYP) |

|-----|----------|-----|-----------------|--------------------|

| 14  | POWER_ON | I   | Power ON        | 3.3V               |

#### 6.1.1.2 Startup Operation Requirements

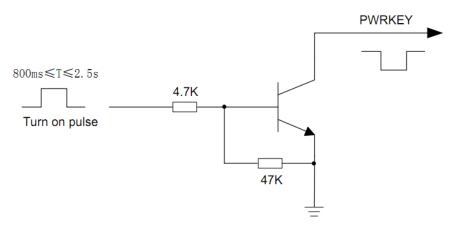

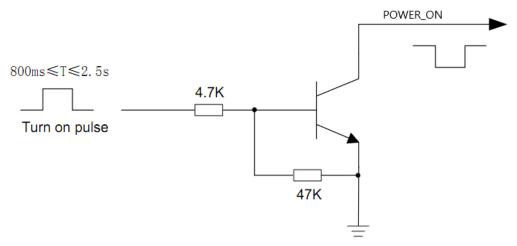

When the N510-GL module is in shutdown mode, the module can be turned on by lowering POWER\_ON (800 ms < lowering time < 2.5s). It is recommended that OC/OD drive circuit be used to control POWER\_ON pin, and the low-level voltage must be less than or equal to 0.5V when POWER\_ON is turned on. The reference circuit is shown in the following figure:

Figure6-1 OC/OD Driver Reference Switch-on Circuit

Another way to control the POWER\_ON pin is to use a button switch directly. A TVS (recommended ESD9X5VL-2/TR) is placed near the button for ESD protection. The reference circuit is shown in the following figure:

Figure6-2 Key Boot Reference Circuit

#### 6.1.1.3 Boot Time Sequence

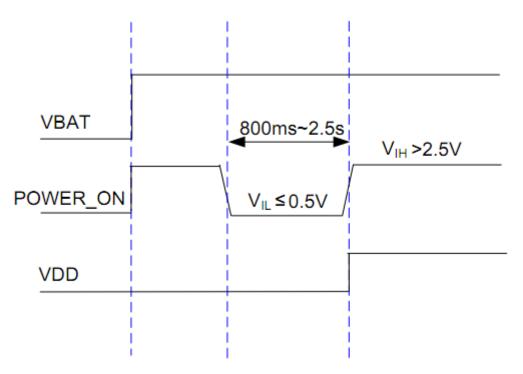

After the module is powered on, pull down POWER\_ON greater than 800 ms less than 2.5s, and the module will start. At this time, the module VDD outputs 2.8V voltage, and the module starts the initialization process.

The start-up sequence is shown in the following figure:

Figure 6-3 Bootup Sequence Diagram

## 6.1.2 Module Shutdown

#### **6.1.2.1 Shutdown Operation Requirements**

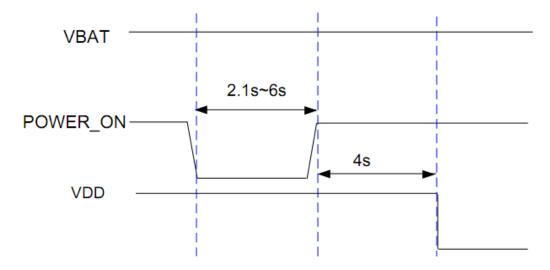

When the N510-GL module is in boot mode, the module can be shut down by pulling down

POWER\_ON (2.1s < pull down time < 6s). It is recommended to use OC/OD driver circuit to control POWER\_ON pin, and to lower the low-level voltage when POWER\_ON is turned off must be less than 0.5V.

#### 6.1.2.2 Shutdown Mode

The module supports the following shutdown modes:

Shutdown Mode

Shutdown Method

Applicable Scenario

Hardware shutdown

Pull down PWRKEY (2.1s ≤ Pull down time <6s) and release it.</td>

Normal shutdown

Software shutdown

AT+CPWROFF

Shutdown needs to be achieved through software control

When VBAT voltage is too low (less than 3.3V) or

power off, the module will shut down.

Table6-2 Shutdown Mode

#### 6.1.2.3 Shutdown Time

Low

Voltage

Shutdown

By lowering the VBAT, the power management unit (PMU) of the module will power off, and the module will realize hardware shutdown. The timing of hardware shutdown control is shown in the following figure:

Figure 6-4 Hardware shutdown control sequence

Module exceptions

After the first POWER\_ON power off, 4s is needed between the second POWER\_ON power on

#### **6.1.3** Reset

#### 6.1.3.1 Reposition Pin Description

Table6-3 Reposition pin description

| PIN | Pin Name | I/O | Pin Description | Power Domain (TYP) |

|-----|----------|-----|-----------------|--------------------|

| 37  | RESET    | I   | Reset signal    | 3.3V               |

#### 6.1.3.2 Instructions for the Use of Reset

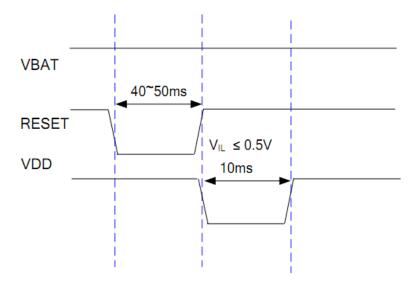

The module supports reset function. By pulling down the RESET signal more than 40 ms (recommended value is 50 ms), over 60ms, the module will RESET again ,the module can be reset to the initial state. After releasing the RESET, the module will restart. RESET can be suspended when not in use. The low level voltage when pulling down RESET to start must be less than or equal to 0.5V.

RESET control sequence is shown in the following figure:

Figure 6-5 Reset control timing

#### Remarks:

RESET is a sensitive signal. It is recommended to add a de-jitter capacitor near the module end. PCB layouts should be far away from radio frequency interference and do a good job of packet processing, while avoiding the edge and surface alignment of PCB (to avoid ESD causing module reset).

## 6.1.4 Flight Mode

The module supports software-controlled flight mode switches and sends AT instructions to the module through serial port 1 (AT serial port):

AT+CFUN=4

The module can enter the flight mode.

The module exits the flight mode by sending the following AT instructions to the module through the serial port 1 (AT serial port):

AT+CFUN=1

The module can exit the flight mode and enter the normal working mode.

#### 6.2 Indicator Interface

## 6.2.1 Pin Description

The N510-GL module provides a signal to display the working status of the module. The status indicator pin is shown in the following table:

Table6-4 Instructions for Interface Pins of Indicators

| PIN | Pin Name | I/O | Pin Description                                    | Power Domain (TYP) |

|-----|----------|-----|----------------------------------------------------|--------------------|

| 38  | LPG      | 0   | Indicate the work and network status of the module | 2.8V               |

## 6.2.2 Working State Indication

N510-GL module network indicator LPG status description.

Table6-5 Description of the Working State of Indicator Lamp

| Mode | NET_MODE                          | Describe                                |  |  |

|------|-----------------------------------|-----------------------------------------|--|--|

|      |                                   | No SIM card                             |  |  |

| 1    | Flash(600ms High /600ms Low)      | Registration Network(T<15S)             |  |  |

|      |                                   | Net failure                             |  |  |

| 2    | Slow flash(70ms Low /3000ms High) | Successful standby of network injection |  |  |

| 3    | Fast flash(70ms Low /70ms High)   | Data Link Establishment                 |  |  |

|      |                                   | Shutdown                                |  |  |

| 4    | Low                               | Sleep                                   |  |  |

|      |                                   | PSM/eDRX                                |  |  |

## 6.3 SIM Card Interface

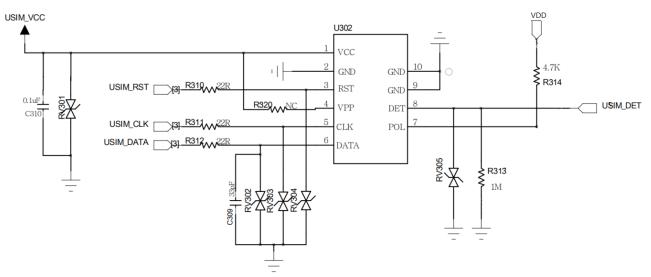

The N510-GL module supports 1.8V and 3V SIM cards.

## 6.3.1 SIM Pin Description

The SIM pin is shown in the following table:

Table6-6 Module SIM Card Pin Description

| PIN | Pin Name | I/O | Pin Description                                                                                                                | Power (TYP) | Domain |

|-----|----------|-----|--------------------------------------------------------------------------------------------------------------------------------|-------------|--------|

| 23  | SIM_SIO  | Ю   | USIM card data pin                                                                                                             | 1.8V/3.0V   |        |

| 24  | SIM_SCLK | 0   | USIM card clock pin                                                                                                            | 1.8V/3.0V   |        |

| 25  | SIM_SRST | 0   | USIM card reset pin                                                                                                            | 1.8V/3.0V   |        |

| 26  | VSIM     | РО  | USIM card power supply                                                                                                         | 1.8V/3.0V   |        |

| 27  | SIM_DET  | I   | USIM card in-place detection pin, high level effective, high level means SIM card insertion, low level means SIM card pullout. | 2.8V        |        |

#### 6.3.2 SIM Interface Circuit

The reference circuit of SIM card holder with detection signal is designed as follows:

## SIM

Figure 6-8 SIM Card Reference Circuit with Detection Signal

The principle of SIM card holder with detection signal is explained as follows:

• SIM card insertion, SIM\_DET and SIM card socket pin 7 short circuit, SIM\_DET is high level.

- SIM card pull out, SIM\_DET and SIM card socket pin 7 open circuit, SIM\_DET is low level.

- SIM plug-in check function is turned off by default, and this function should be turned on through software settings.

## 6.3.3 SIM Card Circuit Design Requirements

The circuit design of SIM card needs to meet the requirements of EMC standard and ESD. At the same time, it needs to improve the anti-interference ability to ensure that the SIM card can work steadily. The following points should be strictly observed in the design:

- The layout of SIM card holder is as close as possible to the module and away from strong interference sources such as RF antenna, DCDC power supply and clock signal line.

- The SIM card with metal shielding case is adopted to improve the anti-interference ability.

- The line length from module to SIM card holder should not exceed 100 mm, too long line will reduce the signal quality.

- SIM\_CLK and SIM\_DATA signals are packaged and isolated to avoid mutual interference. If it is

difficult to do so, at least SIM signals need to be protected as a group of packets.

- The filter capacitor of SIM card signal line and ESD device are placed near the SIM card holder. The equivalent capacitance of ESD device should be 22-33 pF capacitor.

#### **6.4 UART**

## 6.4.1 UART Pin Description

The N510-GL module provides two UART interfaces for asynchronous serial communication with a default baud rate of 115200. UART1 and UART2 interface supports AT command, but cannot be used at the same time, The UART interface definition is shown in the following table:

Table6-8 Module UART Pin Description

| PIN | Pin Name   | I/O | Pin Description           | Power Domain(TYP) |

|-----|------------|-----|---------------------------|-------------------|

| 15  | UART1_DTR* | I/O | UART1 Terminal Ready      | 2.8V              |

| 16  | UART1_DSR* | I/O | UART1 Data Set Ready      | 2.8V              |

| 17  | UART1_DCD* | I/O | UART1 Data Carrier Detect | 2.8V              |

| 18  | UART1_RXD  | I   | UART1 Receive Data        | 2.8V              |

| 19  | UART1_TXD  | 0   | UART1 Transmit Data       | 2.8V              |

| 20  | UART1_RTS  | 0   | UART1 Clear To Send       | 2.8V              |

| 21  | UART1_CTS  | I   | UART1 Request To Send     | 2.8V              |

| PIN | Pin Name    | I/O | Pin Description      | Power Domain(TYP) |

|-----|-------------|-----|----------------------|-------------------|

| 22  | UART1_RING* | I/O | UART1 Ring indicator | 2.8V              |

| 39  | UART2_RXD   | I   | UART2 Receive Data   | 2.8V              |

| 40  | UART2_TXD   | 0   | UART2 Transmit Data  | 2.8V              |

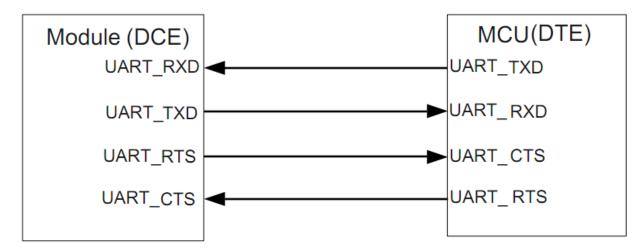

### 6.4.2UART Interface Application

The connection between the N510-GL module (DCE) UART interface and the MCU (DTE) signal is shown in the following figure:

Figure 6-9 Diagram of UART Signal Connection between Module and MCU

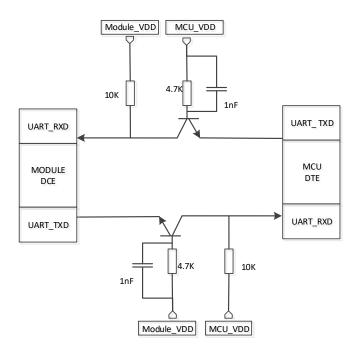

The UART interface level of N510-GL module is 2.8V. If the serial level of the system used by the customer is not 2.8V, we need to add a level conversion circuit in the serial connection between the module and the customer system. We can choose the serial level conversion chip directly according to our own needs. Customers can also use the level conversion circuit shown below. Module\_VDD is 2.8V output level of 20 pins of N510-GL module, and MCU\_VDD is the system serial port level for customers.

Figure 6-10 Module and MCU UART Level Conversion Circuit

For more information on the application of UART serial port, please refer to "FIBOCOM UART Application Design Instructions".

#### 6.5 I2C

N510-GL provides a set of I2C interfaces, which are defined as follows:

Table6-9 I2C pin definition description

| PIN | Pin Name | 1/0 | Pin Description                                                        | Power Domain (TYP) |

|-----|----------|-----|------------------------------------------------------------------------|--------------------|

| 56  | I2C_SCL  | I/O | I2C Serial Clock Signal (The pin can be suspended when not in use.)    | 2.8V               |

| 52  | I2C_SDA  | 0   | I2C Serial Port Data Signal(The pin can be suspended when not in use.) |                    |

Because the N510-GL module has pulled up the I2C signal to 2.8V through 4.7K resistance, it is not necessary to pull up the I2C signal in the actual use process.

### 6.6 ADC

### 6.6.1 ADC Pin Description

The definition of ADC pin is as follows:

Table6-10 Module A/D Conversion Pin Description

| PIN | Pin Name | I/O | Pin Description                           | Power Domain (TYP) |

|-----|----------|-----|-------------------------------------------|--------------------|

| 64  | ADC0     | ı   | Input pin of analog-to-digital conversion | 1.4V               |

| 59  | ADC1     | I   | Input pin of analog-to-digital conversion | 1.4V               |

#### 6.6.2 ADC Instructions for Use

The N510-GL module provides a 10-bit analog-to-digital conversion input pin with an accuracy of about 1.4 mV. Users can use the pin to measure the input voltage, ranging from 0 to 1.4 V. The analog-to-digital conversion function can not work properly in the PSM/eDRX mode.

# 7 Low Power Design

#### 7.1.1 DRX

N510-GL supports DRX mode. Modules access the network normally. Without applying for PSM and eDRX, if there is no data service interaction, the module will automatically enter the lower power DRX mode (sending configuration messages automatically from the network side). In this mode, the bottom current of the module entering low power consumption is about 200 uA, and the average power consumption is reduced to 3.7 mA. UART and GPIO work normally in DRX mode.

#### 7.1.2 eDRX

N510-GL can enter eDRX low-power mode, which can greatly reduce power consumption to 140uA. When the module needs to enter eDRX, it sends the request in the request message. The network configures the request value of the module in the reply message, and the module enters the eDRX mode. In this mode, UART and GPIO can work properly when the internal part of the module is powered off; moreover, the module has been registered on the network and can quickly enter standby state after waking up.

Entering eDRX requires sending the following AT instructions:

Send commands: AT + CEDRXS = 1 or AT + CEDRXS = 2,5, "0011"

Description: The module will save the eDRX configuration. Once the eDRX is set successfully, if the instruction to exit the eDRX is not sent, the module will enter the eDRX mode. Even if the module is powered on and off again, the module can automatically enter the eDRX mode after reboot. Users can enter eDRX mode by sending the following AT instructions and request the period of eDRX on the network side. When the period of eDRX downward from the network side is more than 81.92 s, the module goes into deep sleep mode, otherwise it is shallow sleep mode. 0011 represents the period of eDRX requests from users to the network, which is 40.96 seconds. Users can set their own eDRX according to the protocol.

Users can use AT + CEDRXRDP command to query the period value of eDRX and PTW window time issued on the network side.

To exit eDRX, you need to send the following AT instructions:

Send command: AT + CEDRXS = 0

Description: The module will save the eDRX configuration. Once the instructions are successfully sent out of the eDRX mode, the module will not enter the eDRX mode unless the instructions are re-sent into the eDRX mode. Even if the module is powered on and off again, the module will not automatically enter the eDRX mode after restart.

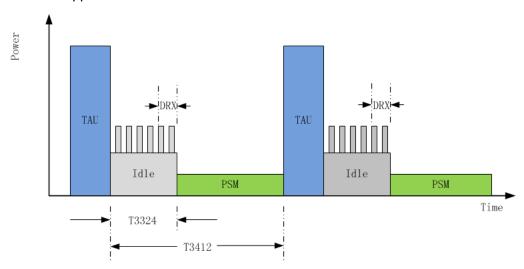

#### 7.1.3 PSM

N510-GL can enter the power saving mode, which has lower power consumption and a typical value of 2.8uA. In this mode, the module is basically powered off, only the clock circuit is powered on, and the wake-up function is supported.

Figure 7-1 Current Diagram of PSM Working Time

When the module needs to enter the PSM, it will send the application to enter the PSM in the request message, and the network will send the agreed entry message in the reply message, and configure the T3324 and T3412 timers. The timer T3324 enters the PSM after timeout; after entering the PSM, the timer T3412 timeout, the module will automatically wake up and start paging.

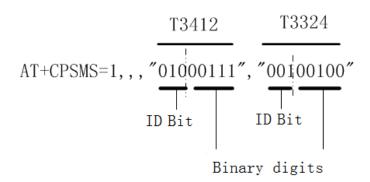

#### **PSM Entry:**

1.Send commands: AT+CPSMS=1 or AT+CPSMS=1,,,"01000111","00100100"

Figure 7-2AT instruction description entering PSM mode

The parameters can be customized, as shown in the table below. Actually, the network download configuration is used.

Table6-7 PSM Timer Configuration Correspondence Table

| T3324 ID Bit |             | T3412 ID Bit |             |

|--------------|-------------|--------------|-------------|

| Code         | Time        | Code         | Time        |

| 000          | 2s          | 000          | 10min       |

| 001          | 1min        | 001          | 1h          |

| 010          | 6min        | 010          | 10h         |

| 011          | 1min        | 011          | 2s          |

| 100          | 1min        | 100          | 30s         |

| 101          | 1min        | 101          | 1min        |

| 110          | 1min        | 110          | 320h        |

| 111          | Timer Close | 111          | Timer Close |

After T3324 timeout, the module automatically enters the PSM; after T3412 timeout, the module automatically exits the PSM.

2. The module is rebooted, powered on and off, saved and configured. After booting, there is no data transmission service in the time of T3324 timer configuration, and it can automatically enter the PSM.

#### **PSM Exit:**

- 1. Pull down the WAKEUP\_IN pin to wake up and automatically try to access the network, the descent edge is valid.

- 2. Pull down the POWER\_ON module (700-800ms) to wake up and automatically try to access the network.

- 3. T3412 clock timeout module will automatically wake up and automatically access the network. If any of the above three conditions are satisfied, the module can exit the PSM mode.

# 8 RF Specifications

### 8.1 operating Frequency Band

The N510-GL module provides a main antenna interface for receive and transmit radio frequency signals. The operating frequency band of the module is shown in the following table:

Table8-1 Description of operating frequency band of module

| Band    | Description | Mode   | Tx (MHz)  | Rx (MHz)  |

|---------|-------------|--------|-----------|-----------|

| Band 1  | 2100MHz     | NB-IOT | 1920-1980 | 2110-2170 |

| Band 2  | 1900MHz     | NB-IOT | 1850-1910 | 1930-1990 |

| Band 3  | 1800MHz     | NB-IOT | 1710-1785 | 1805-1880 |

| Band 4  | 2100MHz     | NB-IOT | 1710-1755 | 2110-2155 |

| Band 5  | 850MHz      | NB-IOT | 824-849   | 869-894   |

| Band 8  | 900 MHz     | NB-IOT | 880-915   | 925-960   |

| Band 12 | 700 MHz     | NB-IOT | 699-716   | 729-746   |

| Band 13 | 700 MHz     | NB-IOT | 777–787   | 746-756   |

| Band 17 | 700 MHz     | NB-IOT | 704–716   | 734-746   |

| Band 18 | 800 MHz     | NB-IOT | 815–830   | 860-875   |

| Band 19 | 800 MHz     | NB-IOT | 830-845   | 875-890   |

| Band 20 | 800 MHz     | NB-IOT | 832-862   | 791-821   |

| Band 25 | 1900 MHz    | NB-IOT | 1850-1915 | 1930-1995 |

| Band 28 | 700MHz      | NB-IOT | 703-748   | 758-803   |

| Band 66 | 2100 MHz    | NB-IOT | 1710-1780 | 2110-2180 |

| Band 71 | 600 MHz     | NB-IOT | 663-698   | 617-652   |

| Band 85 | 700 MHz     | NB-IOT | 698-716   | 728-746   |

|         |             |        |           |           |

### 8.2 Transmission Power

The transmission power of each band of the N510-GL module is shown in the following table:

Table8-2 Explanation of Transmitting Power of Modules in Each Frequency Band

| Mode   | Band   | Tx Power(dBm) |

|--------|--------|---------------|

| NB-IOT | Band 1 | 23±1          |

| NB-IOT | Band 2 | 23±1          |

| NB-IOT | Band 3 | 23±1          |

| NB-IOT | Band 4 | 23±1          |

| NB-IOT | Band 5 | 23±1          |

| Mode   | Band    | Tx Power(dBm) |

|--------|---------|---------------|

| NB-IOT | Band 8  | 23±1          |

| NB-IOT | Band 12 | 23±1          |

| NB-IOT | Band 13 | 23±1          |

| NB-IOT | Band 17 | 23±1          |

| NB-IOT | Band 18 | 23±1          |

| NB-IOT | Band 19 | 23±1          |

| NB-IOT | Band 20 | 23±1          |

| NB-IOT | Band 25 | 23±1          |

| NB-IOT | Band 28 | 23±1          |

| NB-IOT | Band 66 | 23±1          |

| NB-IOT | Band 71 | 23±1          |

| NB-IOT | Band 85 | 23±1          |

|        |         |               |

### 8.3 Reception Sensitivity

The receiving sensitivity of N510-GL module with and without retransmit is as follows:

Table 8-3 Module Frequency Band Sensitivity Description

| Mode   | Band    | Rx Sensitivity Level with Retransmit (dBm) | Rx Sensitivity Level without Retransmit (dBm) |

|--------|---------|--------------------------------------------|-----------------------------------------------|

| NB-IOT | Band 1  | -129±1                                     | -115                                          |

| NB-IOT | Band 2  | -129±1                                     | -115                                          |

| NB-IOT | Band 3  | -129±1                                     | -115                                          |

| NB-IOT | Band 4  | -129±1                                     | -115                                          |

| NB-IOT | Band 5  | -129±1                                     | -115                                          |

| NB-IOT | Band 8  | -129±1                                     | -115                                          |

| NB-IOT | Band 12 | -129±1                                     | -115                                          |

| NB-IOT | Band 13 | -129±1                                     | -115                                          |

| NB-IOT | Band 17 | -129±1                                     | -115                                          |

| NB-IOT | Band 18 | -129±1                                     | -115                                          |

| NB-IOT | Band 19 | -129±1                                     | -115                                          |

| NB-IOT | Band 20 | -129±1                                     | -115                                          |

| NB-IOT | Band 25 | -129±1                                     | -115                                          |

| NB-IOT | Band 28 | -129±1                                     | -115                                          |

| NB-IOT | Band 66 | -129±1                                     | -115                                          |

| NB-IOT | Band 71 | -129±1                                     | -115                                          |

| NB-IOT | Band 85 | -129±1                                     | -115                                          |

|        |         |                                            |                                               |

NB-IoT supports more retransmissions than traditional methods. Every time the number of retransmissions doubled, the rate would be halved and the gain would be 3 dB.

### 8.4 Communication Antenna

#### 8.4.1 Antenna Interface

The N510-GL module provides an antenna interface as shown in the following table:

Table8-3 Description of Line Interface Pins

| PIN | Pin Name | I/O | Pin Description | Power (TYP) | Domain |

|-----|----------|-----|-----------------|-------------|--------|

| 3   | RF_ANT   | I   | Antenna         | -           |        |

### 8.4.2 Antenna Design Requirements

The antenna design requirements are shown in the following table:

Table8-4 Modular Antenna Design Requirements

| N510-GL Module Main Antenna Requirements |                                                              |  |  |  |  |  |  |

|------------------------------------------|--------------------------------------------------------------|--|--|--|--|--|--|

| Eroguenou Dongo                          | The most suitable antenna must be used to adapt the relevant |  |  |  |  |  |  |

| Frequency Range                          | frequency band.                                              |  |  |  |  |  |  |

|                                          | NB-IOT Band1:250MHz                                          |  |  |  |  |  |  |

|                                          | NB-IOT Band2:140MHz                                          |  |  |  |  |  |  |

|                                          | NB-IOT Band3:170MHz                                          |  |  |  |  |  |  |