# 802.11b/g/n + BT2.1 + FM Radio 3-in-1 SiP Module

Data Sheet Dec 14 2010 Rev 4.2

# Introduction

The 802.11b/g/n + BT + FM receiver Wireless SiP module WM-BN-BM-01 which refers as "SiP 3-in-1 module" is a small size module that provides full function of 802.11b/g/n(draft n), Bluetooth 2.1/class 1 /class2 and FM Receiver in a tiny module via 66 pins LGA Foot Print.

This multi- functionality and board to board physical interface provides SDIO/SPI interface for WiFi, UART for Bluetooth and FM receiver.

The small size & low profile physical design make it easier for system design to enable high performance wireless connectivity without space constrain. The low power consumption and excellent radio performance make it the best solution for OEM customers who require embedded 802.11b/g/n Wi-Fi + Bluetooth features, such as, Wireless PDA, Smart phone, MP3, PMP, slim type Notebook, VoIP phone etc.

The module is based on Broadcom 4329 chipset which is a WiFi+BT+FM Transceiver SOC. The Radio architecture & high integration MAC/BB chip provide excellent sensitivity with rich system performance. The module is designed as single antenna for WiFi and Bluetooth for the application of small size hand held device.

In addition to WEP 64/128, WPA and TKIP, AES, CCX is supported to provide the latest security requirement on your network.

For the software and driver development, USI provides extensive technical document and reference software code for the system integration under the agreement of Broadcom International Ltd.

Hardware evaluation kit and development utilities will be released base on listed OS and processors to OEM customers.

# **Features**

- Lead Free design which supporting Green design requirement, RoHS Compliance.

- The module can support Halogen Free

- Support single Antenna for WiFi and Bluetooth

- Small size suitable for low volume system integration.

- Low power consumption & excellent power management performance extend battery life.

- 2.412-2.484 GHz two SKUs for worldwide market.

- Easy for integration into mobile and handheld device with flexible system configuration and antenna design.

- Supports per packet Rx Antenna diversity

|      |            |                         |            | Change Sheet                                                                                                                           |                    |

|------|------------|-------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Rev. | Date       | Description             | on of cha  | nge                                                                                                                                    | Approval & Date    |

|      | Bate       | Page                    | Par        | Change(s)                                                                                                                              | Approvar a Bate    |

| 1.0  | 04/20/09   | All                     | All        | Draft version for Review                                                                                                               | Jason Tsai         |

| 1.1  | 06/10/09   | 11,29                   |            | BT spec update                                                                                                                         | Jason Tsai         |

| 1.1  | 00/10/09   | 11,29                   |            | Recommended Footprint update                                                                                                           | Jason rsai         |

| 1.3  | 07/01/09   | All                     |            | Power consumption, add Power topology for WM-BN-BM-01, update WLAN specific                                                            |                    |

| 1.4  | 07/27/09   | 11,12,29                | 8          | WLAN spect update: power level of 11n change to 17dBm, BT spec update: sensitivity change to -88dBm as typical, update module top view |                    |

| 1.5  | 08/28/09   | 2,<br>9,10,11,<br>12,29 | 5.2.2,5.   | Add Halogen Free, Operation voltage, power consumption, WLAN RX spec, BT maximum input level, remove FM RX spec,                       | Jason Tsai         |

| 2.0  | 09/22/09   | 35                      | 10.4       | Add life cycle                                                                                                                         | Jason Tsai         |

| 2.1  | 10/15/09   | 11                      | 5.4        | Add hint for CE and FCC requirement                                                                                                    | Jason Tsai         |

| 2.2  | 11/25/09   | 35                      | 10.4       | Add the Half-Sine Shock                                                                                                                | Jason Tsai/Scarrie |

| 2.3  | 12/11/09   | 6<br>13                 |            | Update Block Diagram Update Reference Circuit                                                                                          | Jason Tsai/Scarrie |

| 2.4  | 01/14/2010 | 11<br>12                | 5.4<br>5.6 | Update Specifications 802.11b/g/n Bluetooth Radio Characteristics                                                                      | Jason Tsai/Scarrie |

| 2.5  | 01/18/2010 | 35                      | 10.4       | Update the Half-Sine Shock                                                                                                             | Jason Tsai/Scarrie |

| 2.6  | 01/22/2010 | 11                      | 5.4        | Remove the "Hint:"                                                                                                                     | Scarrie            |

| 2.7  | 01/25/2010 | 11                      | 5.4        | Update Specifications 802.11b output power                                                                                             | Scarrie            |

| 2.8  | 01/26/2010 | 11<br>27<br>13          |            | Update Specifications Pin Description Update Reference Circuit                                                                         | Scarrie            |

| 3.1  | 02/25/2010 |                         |            | Reference PRD to PDS                                                                                                                   | Scarrie            |

| 3.2  | 03/08/2010 | 10<br>11,12<br>13       |            | Update Power Topology Update Specifications Update Reference Circuit                                                                   | Scarrie            |

| 3.3  | 03/23/2010 | 25                      |            | Add module high tolerance                                                                                                              | Scarrie            |

| 3.4  | 04/06/2010 | 25                      | 5.9        | Update Module actual dimension                                                                                                         | Scarrie            |

| 3.5  | 06/14/2010 | 20                      |            | Add PCM interface pin define description                                                                                               | Scarrie            |

| 4.0  | 06/28/2010 | 31<br>32                |            | Add middle-ground pad recommended past_mask Recommanded reflow profile                                                                 | Scarrie            |

| 4.1  | 07/19/2010 | 12                      | 5.6        | Update Bluetooth output power to add class2 specification                                                                              | Scarrie            |

|      |            |                         |            | Modify Laser Mark                                                                                                                      |                    |

# **TABLE OF CONTENTS**

| 1.          | EXECUTIVE SUMMARY                               | 5   |

|-------------|-------------------------------------------------|-----|

| 2.          | BLOCK DIAGRAM                                   | 6   |

|             |                                                 |     |

| 3.          |                                                 |     |

| 4.          | REFERENCE DOCUMENTS                             | 8   |

| 5.          | TECHNICAL SPECIFICATION                         | 9   |

|             | 5.1 ABSOLUTE MAXIMUM RATING                     | C   |

| ;           | 5.2. RECOMMENDABLE OPERATION CONDITION          | 9   |

|             | 5.2.1. TEMPERATURE, HUMIDITY                    | 9   |

|             | 5.2.1. VOLTAGE                                  | 9   |

|             | 5.3. WIRELESS SPECIFICATIONS                    | 11  |

|             | 5.4. RADIO SPECIFICATIONS 802.11B/G/N           |     |

|             | 5.6. BLUETOOTH RADIO CHARACTERISTICS            | 12  |

|             | 5.7. FM SPECIFICATIONS                          | 13  |

| ;           | 5.8 TIMING DIAGRAM OF INTEFACE                  | 15  |

| ;           | 5.9. DIMENSIONS, WEIGHT AND MOUNTING            | 27  |

|             |                                                 |     |

| 6.          | LEGAL, REGULATORY & OTHER TECHNICAL CONSTRAINTS | 28  |

| 7.          | PIN OUT AND PIN DESCRIPTION                     | 26  |

|             |                                                 |     |

| 8.          | RECOMMEND FOOTPRINT                             | 32  |

|             |                                                 |     |

| <b>9.</b> ] | RECOMMANDED REFLOW PROFILE                      | 32  |

| 1 /         | DA CIZA CIE AND OUTODA CIE COMPUNIONI           | 2.4 |

#### 1. EXECUTIVE SUMMARY

The WM-BN-BM-01 module - is one of the product families in USI's product offering, targeting for system integration requiring a smaller form factor. It also provides the standard migration to high data rate to USI's current SIP customers.

The purpose of this document is to define the product specification for 802.11b/g/n (draft n) WiFi + BT 2.1 +FM module WM-BN-BM-01. All the data in this document is based on Broadcom 4329 data sheet and other documents provided from Broadcom. The data will be updated after implementing the measurement of the module.

This product is designated for use in embedded applications mainly in the mobile device, which required small size and high data rate wireless connectivity. The application such as, Wireless PDA, slim type Notebook, Media Adapter, Barcode scanner, mini-Printer, VoIP phone, Data storage device could be the potential application for wireless WM-BN-BM-01.

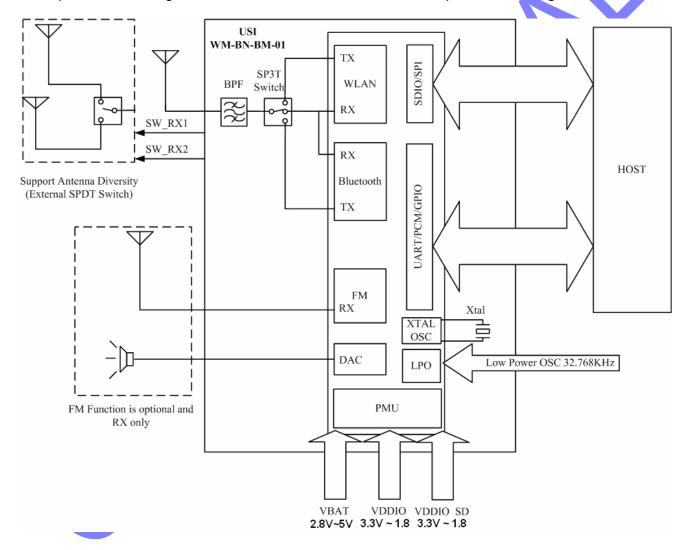

#### 2. BLOCK DIAGRAM

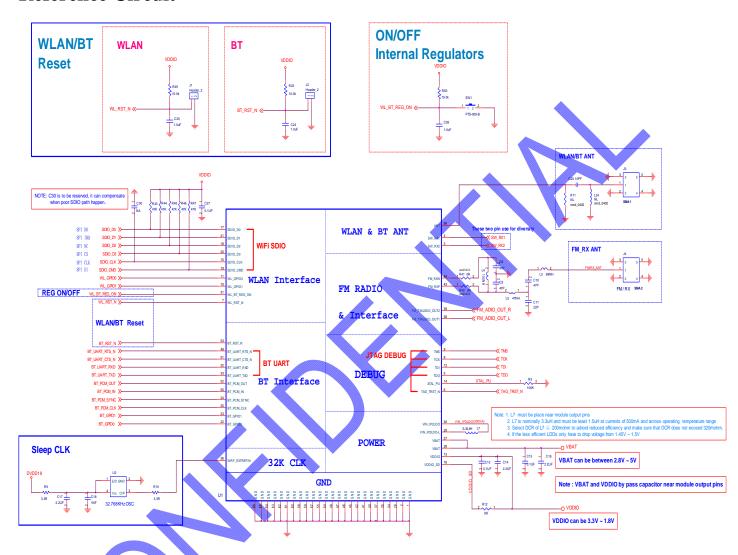

The WM-BN-BM-01 module is designed based on Broadcom 4329 chipset solution.

It supports generic SPI (G-SPI), SDIO interface to connect the WLAN to the host processor. High speed UART is available to connect the Bluetooth2.1 + EDR and FM to the host processor. A Bluetooth co-existence interface is supported for external, co-located Bluetooth devices. If Antenna be diversity, Antenna should add one SPDT switch outside module and control by module.

A simplified block diagram of the WM-BN-BM-01 module is depicted in the Fig. below.

#### 3. DELIVERABLES

The following products and software will be part of the product.

- ♣ WM-BN-BM-01 Module with packaging

- Evaluation kits (with SDIO / SPI interface)

- ♣ Software utility which supporting customer for integration, performance test and homologation. Capable of testing, loading (firmware) and configuring (MAC, CIS) for the WM-BN-BM-01 module.

- ♣ Unit Test / Qualification report

- Product Specifications.

- ♣ Agency certification pre-test report base on adapter boards

# 4. REFERENCE DOCUMENTS

| C.I.S.P.R.<br>Pub. 22   | "Limits and methods of measurement of radio interference characteristics of information technology equipment." International Special Committee on Radio Interference (C.I.S.P.R.), Third Edition, 1997.                                                                                   |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CB Bulletin<br>No. 96A  | "Adherence to IEC Standards: "Requirements for IEC 950, 2 <sup>nd</sup> Edition and Amendments 1 (1991), 2(1993), 3 (1995) and 4(1996). Product Categories: Meas, Med, Off, Tron." IEC System for Conformity Testing to Standards for Safety of Electrical Equipment (IECEE), April 2000. |

| CFR 47,<br>Part 15-B    | "Unintentional Radiators". Title 47 of the Code of Federal Regulations, Part 15, FCC Rules, Radio Frequency Devices, Subpart B.                                                                                                                                                           |

| CFR 47,<br>Part 15-C    | "Intentional Radiators". Title 47 of the Code of Federal Regulations, Part 15, FCC Rules, Subpart C. URL: <a href="http://www.access.gpo.gov/nara/cfr/waisidx">http://www.access.gpo.gov/nara/cfr/waisidx</a> 98/47cfr15 98.html                                                          |

| CSA C22.2<br>No. 950-95 | "Safety of Information Technology Equipment including Electrical Business Equipment, Third Edition." Canadian Standards Association, 1995, including revised pages through July 1997.                                                                                                     |

| EN 60 950               | "Safety of Information Technology Equipment Including Electrical Business Equipment." European Committee for Electrotechnical Standardization (CENELEC), 1996, (IEC 950, Second Edition, including Amendment 1, 2, 3 and 4).                                                              |

| IEC 950                 | "Safety of Information Technology Equipment Including Electrical Business Equipment." European Committee for Electrotechnical Standardization, Intentional Electrotechnical Commission. 1991, Second Edition, including Amendments 1, 2, 3, and 4.                                        |

| IEEE 802,11             | "Wireless LAN Medium Access Control (MAC) And Physical Layer (PHY) Specifications." Institute of Electrical and Electronics Engineers. 1999.                                                                                                                                              |

#### 5. TECHNICAL SPECIFICATION

#### 5.1. ABSOLUTE MAXIMUM RATING

| ∕lax +5 Volt       |                                             |

|--------------------|---------------------------------------------|

| 40° to 85° Celsius |                                             |

| -/- 2%             | Max. Values not exceeding Operating voltage |

| 4                  | 40° to 85° Celsius                          |

#### 5.2. RECOMMENDABLE OPERATION CONDITION

# **5.2.1. TEMPERATURE, HUMIDITY**

The WM-BN-BM-01 module has to withstand the operational requirements as listed in the table below.

| Operating Temperature | -20° to 70° Celsius |                                   |

|-----------------------|---------------------|-----------------------------------|

| Humidity range        | Max 95%             | Non condensing, relative humidity |

#### **5.2.1. VOLTAGE**

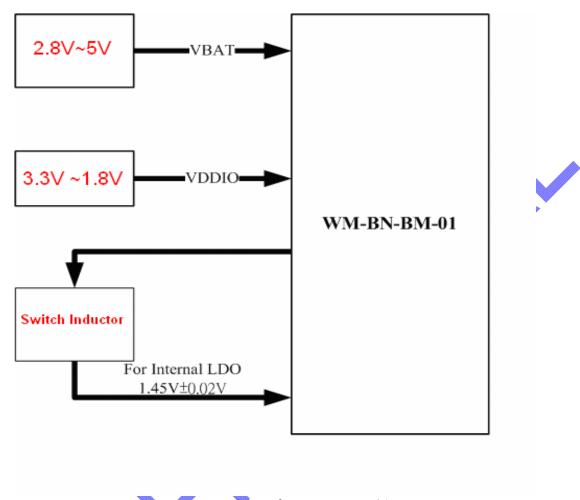

Power supply for the WM-BN-BM-01 module will be provided by the host via the power pins

| Symbol             | Parameter                   | Min              | Тур | Max  | Unit |

|--------------------|-----------------------------|------------------|-----|------|------|

| VBAT               | 3.3V Power Supply           | 2.8 <sup>a</sup> | 3.3 | 5.0  | V    |

| VDDIO <sup>b</sup> | Host Interface Power Supply | 1.62             | 1.8 | 1.98 | V    |

| VDDIO              |                             | 2.97             | 3.3 | 3.63 | V    |

♦ a: 2.8V is the minimum voltage to keep PA performance of TX path

◆ b: I/O interface DC level depends on VDDIO

Power Topology of WM-BN-BM-01

# 5.2.2. Power consumption

|      |               | Power consumption        | Typical | Max   |

|------|---------------|--------------------------|---------|-------|

|      | Tx @ 17dBm    | output power @ 25C (11b) | 275mA   | 320mA |

| WiFi | Tx @ 17dBm    | output power @ 25C (11g) | 220mA   | 280mA |

|      | TX@17dBm      | output power @ 25C (11n) | 220mA   | 280mA |

|      | Rx @25C (11   | b)                       | 77mA    | 90mA  |

|      | Rx @25C (11   | g)                       | 77mA    | 90mA  |

| ВТ   | Tx @ 10dBm    | output power @ 25C       | 50mA    | 60mA  |

| DI   | Rx (multi-sen | sitivity)@25C            | 40mA    | 50mA  |

Condition: VBAT=3.6V, VDDIO=3.3V, WL\_BT\_REG\_ON=H, WL\_RST\_ON=H, BT\_RST\_ON=H

# 5.3. WIRELESS SPECIFICATIONS

The WM-BN-BM-01 module complies with the following features and standards;

| Features       | Description                                       |   |  |  |

|----------------|---------------------------------------------------|---|--|--|

| WLAN Standards | IEEE 802 Part 11b/g/n (802.11b/g/n <sup>a</sup> ) |   |  |  |

| Bluetooth      | Bluetooth <sup>™</sup> 2.1 compliance             | _ |  |  |

| Antenna Port   | Support Single Antenna for WiFi and BT            |   |  |  |

| Frequency Band | 2.400 GHz – 2.484 GHz                             |   |  |  |

<sup>♦</sup> a: 802.11n in this module only support HT20

# 5.4. RADIO SPECIFICATIONS 802.11B/G/N

| Features                          | Description                                                                   |

|-----------------------------------|-------------------------------------------------------------------------------|

| Frequency Band                    | 2.4000 GHz – 2.497 GHz (2.4 GHz ISM Band)                                     |

| Number of selectable Sub channels | 14 channels                                                                   |

| Modulation                        | OFDM, DSSS (Direct Sequence Spread Spectrum), DBPSK, DQPSK, CCK, 16QAM, 64QAM |

| Supported rates                   | 1,2, 5.5,11,6,9,12,24,36,48,54 Mbps                                           |

| Maximum receive level             | -10dBm (with PER < 8%)                                                        |

| Output Power                      | 17 dBm +2.0/-2.0 dBm for 802.11b<br>15 dBm +2.0/-2.0 dBm for 802.11g          |

| Output Power                      | 15 dBm +2.0/-2.0 dBm for 802.11g                                              |

|                                   | -160 dBm/Hz (max.)@869 MHz~960 MHz                                            |

| Wide-Band Noise                   | -160 dBm/Hz (max.)@1800 MHz~1990 MHz                                          |

|                                   | -152 dBm/Hz (max.)@2110 MHz~2170MHz                                           |

# EVM:

| Characteristic                |          | Typical | Maximum | Unit |

|-------------------------------|----------|---------|---------|------|

| RF Average Output EVM (11b)   | @11 Mbps | -13     | -10     | dB   |

| Transport Livin (11b)         | @1 Mbps  | -13     | -10     | dB   |

| RF Average Output EVM (11g)   | @54 Mbps | -30     | -25     | dB   |

| Kr Average Output Evivi (119) | @6 Mbps  | -30     | -25     | dB   |

| DE Avere de Outeut EVA (44 a) | @ MCS7   | -30     | -28     | dB   |

| RF Average Output EVM (11n)   | @ MCS0   | -30     | -25     | dB   |

# Sensitivity:

| Receiver Characteristics ( 3.3V, 25 degree C ) | Typical | Max. | Unit |

|------------------------------------------------|---------|------|------|

| PER <8%, Rx Sensitivity @ 1 Mbps               | -92     | -90  | dBm  |

| PER <8%, Rx Sensitivity @ 11 Mbps              | -85     | -82  | dBm  |

| PER <10% Rx Sensitivity @ 6 Mbps               | -86     | -83  | dBm  |

| PER <10%, Rx Sensitivity @ 54 Mbps             | -72     | -69  | dBm  |

| PER <10%, Rx Sensitivity @ MCS0                | -88     | -85  | dBm  |

| PER <10%, Rx Sensitivity @ MCS7                | -70     | -67  | dBm  |

# 5.5. RADIO SPECIFICATIONS 802.15 BLUETOOTH

The Radio specification is compliant with the Bluetooth<sup>™</sup> 2.1 + EDR specification

| Features           | Description                               |

|--------------------|-------------------------------------------|

| Frequency Band     | 2400 MHz ~ 2483.5 MHz                     |

| Number of Channels | 79 channels                               |

| Modulation         | FHSS (Frequency Hopping Spread Spectrum), |

|                    | GFSK                                      |

| Antenna Port       | Single Antenna for WiFi and BT            |

# 5.6. BLUETOOTH RADIO CHARACTERISTICS

| Features          |        | Description                        |                 |            |  |  |  |

|-------------------|--------|------------------------------------|-----------------|------------|--|--|--|

|                   |        | Max.                               | Typical         | Min.       |  |  |  |

| Maximum Receive L | evel   | -                                  | •               | -20dBm     |  |  |  |

| Output Power      | Class1 | 15dBm                              | 8.5dBm          | 7.5dBm     |  |  |  |

|                   | Class2 | 4 dBm                              | 0 dBm           | -6 dBm     |  |  |  |

| Sensitivity <     |        | -84dBm                             | -86 dBm         | -88dBm     |  |  |  |

| EDR Sensitivity   |        | -78dBm                             | -80dBm          | -83dBm     |  |  |  |

|                   |        | -145 dBm/Hz (max.)@869 MHz~960 MHz |                 |            |  |  |  |

| Wide-Band Noise   |        | -145 dBm/Hz                        | (max.)@1800 MHz | z~1990 MHz |  |  |  |

|                   |        | -145 dBm/Hz                        | (max.)@2110 MHz | z~ 2170MHz |  |  |  |

# 5.7. FM SPECIFICATIONS

FM RX TBD

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI

# **Reference Circuit**

Note: 1. It is highly recommended that keeping the top layer of the module mounting area as GND-plane

2. Do not rout any traces going through the underneath of the module

# 5.8. TIMING DIAGRAM OF INTEFACE

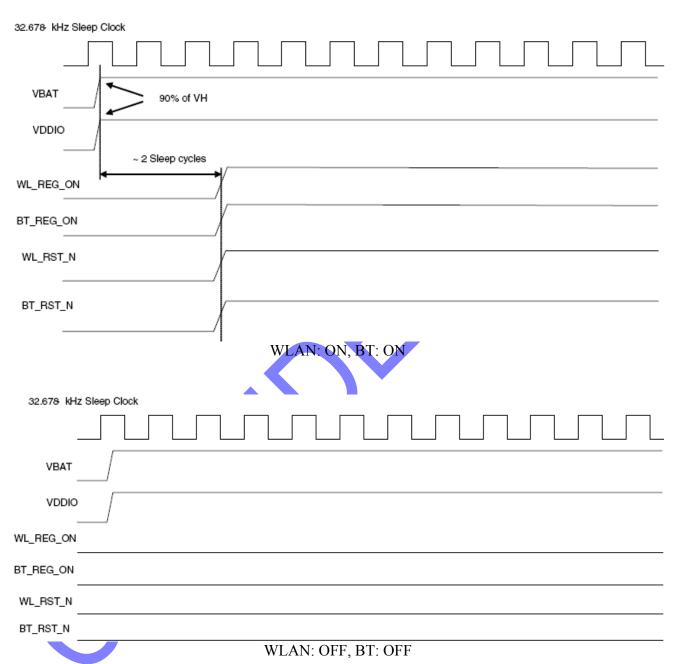

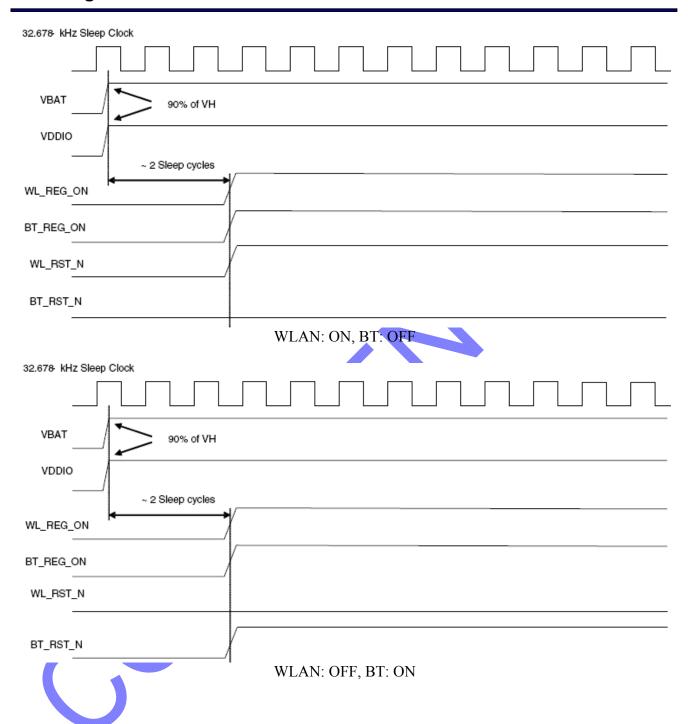

CONTROL SIGNAL TIMING DIAGRAMS

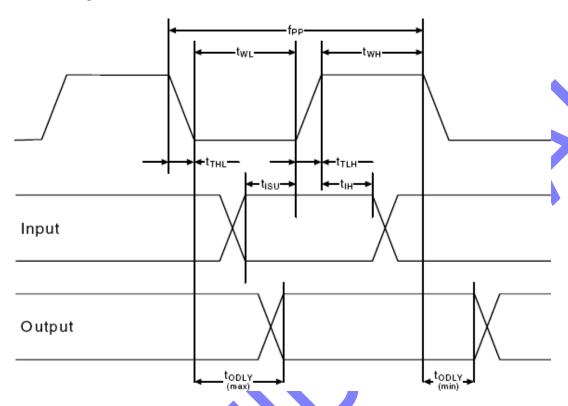

# **SDIO TIMING**

SDIO timing in default mode

# **SDIO Bus Timing Parameters (Default Mode)**

| Parameter                                                    | Symbol                                                       | Min | Typical | Max | Unit |  |  |  |

|--------------------------------------------------------------|--------------------------------------------------------------|-----|---------|-----|------|--|--|--|

| Clock CLK (All values are referred to min. VIH and max. VIL) | Clock CLK (All values are referred to min. VIH and max. VIL) |     |         |     |      |  |  |  |

| FrequencyData Transfer Mode                                  | fPP                                                          | 0   | -       | 25  | МНz  |  |  |  |

| FrequencyIdentification Mode                                 | fOD                                                          | 0   | -       | 400 | kHz  |  |  |  |

| Clock Low Time                                               | tWL                                                          | 10  | -       | -   | ns   |  |  |  |

| Clock High Time                                              | tWH                                                          | 10  | -       | -   | ns   |  |  |  |

| Clock Rise time                                              | tTLH                                                         | -   | -       | 10  | ns   |  |  |  |

| Clock Low Time                                               | tTHL                                                         | -   | -       | 10  | ns   |  |  |  |

| Inputs: CMD, DAT (referenced to CLK)                         |                                                              |     |         |     |      |  |  |  |

| Input Setup Time                                             | tISU                                                         | 5   | -       | -   | ns   |  |  |  |

| Input Hold Time                                              | tIH                                                          | 5   | -       | -   | ns   |  |  |  |

| Outputs: CMD, DAT (referenced to CLK)                        |                                                              |     |         |     |      |  |  |  |

| Output Delay timeData Transfer Mode                          | tODLY                                                        | 0   | _       | 14  | ns   |  |  |  |

| Output Delay timeIdentification Mode                         | tODLY                                                        | 0   | -       | 50  | ns   |  |  |  |

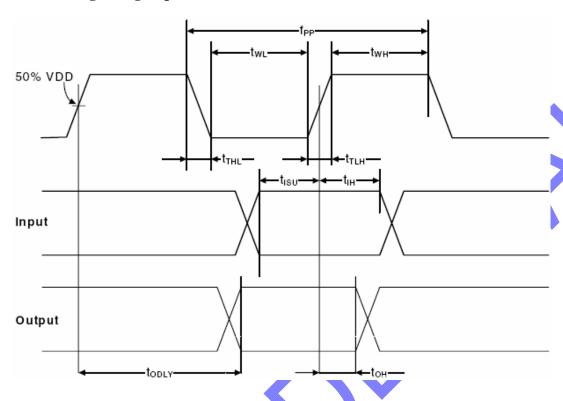

# SDIO timing in High-Speed Mode

# **SDIO Bus Timing Parameters (High-Speed Mode)**

| Parameter                                                    | Symbol | Min | Typical | Max | Unit |  |  |

|--------------------------------------------------------------|--------|-----|---------|-----|------|--|--|

| Clock CLK (all values are referred to min. VIH and max. VIL) |        |     |         |     |      |  |  |

| FrequencyData Transfer Mode                                  | fPP    | 0   | -       | 50  | MHz  |  |  |

| FrequencyIdentification Mode                                 | fOD    | 0   | -       | 400 | kHz  |  |  |

| Clock Low Time                                               | tWL    | 7   | -       | -   | ns   |  |  |

| Clock High Time                                              | tWH    | 7   | -       | -   | ns   |  |  |

| Clock Rise time                                              | tTLH   | -   | -       | 3   | ns   |  |  |

| Clock Low Time                                               | tTHL   | -   | -       | 3   | ns   |  |  |

| Inputs: CMD, DAT (referenced to CLK)                         |        |     |         |     |      |  |  |

| Input Setup Time                                             | tISU   | 6   | -       | -   | ns   |  |  |

| Input Hold Time                                              | tIH    | 2   | -       | -   | ns   |  |  |

| Outputs: CMD, DAT (referenced to CLK)                        |        |     |         |     |      |  |  |

| Output Delay timeData Transfer Mode                          | tODLY  | -   | -       | 14  | ns   |  |  |

| Output Hold time                                             | tOH    | 2.5 | -       | -   | ns   |  |  |

| Total System Capacitance (each line)                         | CL     | -   | -       | 40  | pF   |  |  |

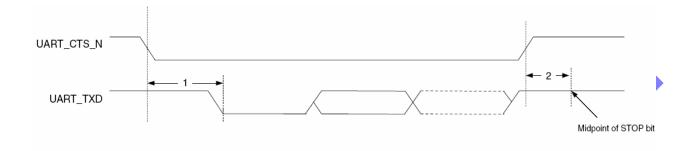

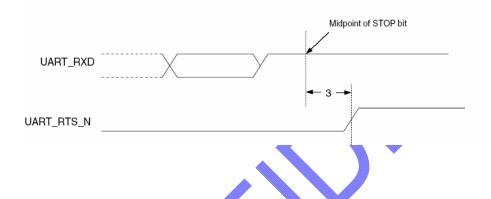

# **UART Timing**

| Reference | Description                                                | Min | Тур | Max | Unit           |

|-----------|------------------------------------------------------------|-----|-----|-----|----------------|

| 1         | Delay time, BT_UART_CTS_N low to UART_TXD valid            | -   | ı   | 24  | Baudout cycles |

| 2         | Setup time, BT_UART_CTS_N high before midpoint of stop bit | -   | ı   | 10  | ns             |

| 3         | Delay time, midpoint of stop bit to BT_UART_RTS_N high     | _   | -   | 2   | Baudout cycles |

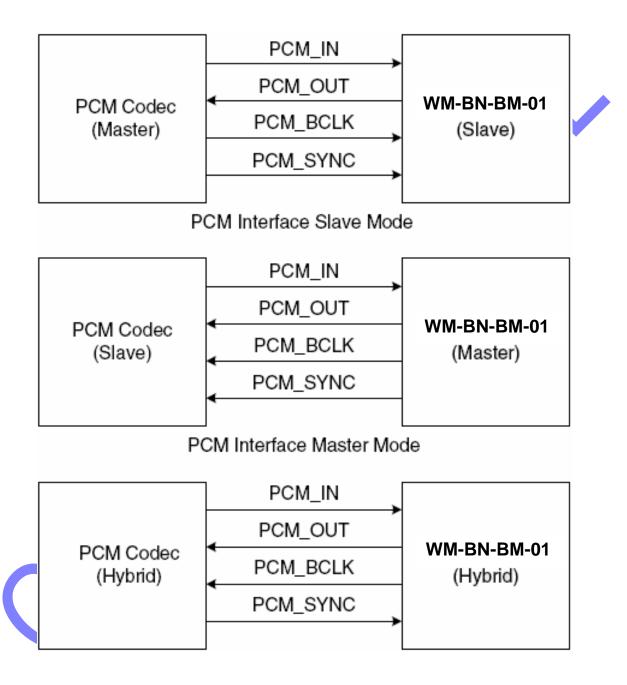

# **PCM INTERFACE TIMING**

|               | Module Pin Define of PCM Interface Table |             |      |                                                         |  |  |  |  |

|---------------|------------------------------------------|-------------|------|---------------------------------------------------------|--|--|--|--|

| Module<br>Pin | Pin-Define                               | PCM-Define  | Type | Description                                             |  |  |  |  |

| 22            | BT_GPIO0                                 |             | Ι    |                                                         |  |  |  |  |

| 23            | BT_GPIO1                                 |             | О    | •                                                       |  |  |  |  |

| 24            | BT_PCM_SYNC                              | BT_PCM_SYNC | I/O  | PCM sync signal, can be master (output) or slave (input |  |  |  |  |

| 25            | BT_PCM_CLK                               | PCM_CLK     | I/O  | PCM clock, can be master (output) or slave (input)      |  |  |  |  |

| 50            | BT_PCM_IN                                | PCM_IN      | I/O  | PCM data input                                          |  |  |  |  |

| 53            | BT_PCM_OUT                               | PCM_OUT     | I/O  | PCM data output                                         |  |  |  |  |

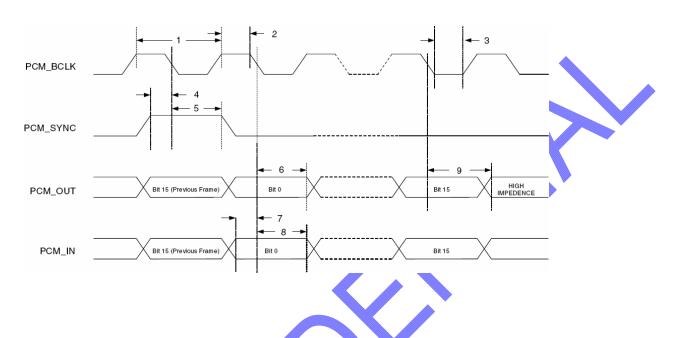

# PCM\_BCLK PCM\_SYNC Bit 15 (Previous Frame) Bit 0 Bit 15 (Previous Frame) Bit 0 Bit 15 Bit 15 Bit 15

| Description                                                                                        | Minimum | Typical | Maximum | Unit |

|----------------------------------------------------------------------------------------------------|---------|---------|---------|------|

| PCM bit clock frequency                                                                            | 128     | -       | 2048    | kHz  |

| PCM bit clock high time                                                                            | 128     | _       | _       | ns   |

| PCM bit clock low time                                                                             | 209     | -       | _       | ns   |

| Delay from BT_PCM_CLK rising edge to BT_PCM_SYNC high                                              | -       | -       | 50      | ns   |

| Delay from BT_PCM_CLK rising edge to BT_PCM_SYNC low                                               | -       |         | 50      | ns   |

| Delay from BT_PCM_CLK rising edge to data valid on BT_PCM_OUT                                      |         | -       | 50      | ns   |

| Setup time for BT_PCM_IN before BT_PCM_CLK falling edge                                            | 50      | _       | -       | ns   |

| Hold time for BT_PCM_IN after BT_PCM_CLK falling edge                                              | 10      | -       | _       | ns   |

| Delay from falling edge of BT_PCM_CLK during last bit period to BT_PCM_OUT becoming high impedance | _       | _       | 50      | ns   |

# **Short Frame Sync, Slave Mode**

| Reference | Description                                                                                        | Min | Тур | Max  | Unit |

|-----------|----------------------------------------------------------------------------------------------------|-----|-----|------|------|

| l         | PCM bit clock frequency                                                                            | 128 | 1   | 2048 | kHz  |

| 2         | PCM bit clock high time                                                                            | 209 | 1   | -    | ns   |

| 3         | PCM bit clock low time                                                                             | 209 | ı   | -    | ns   |

| 4         | Setup time for BT_PCM_SYNC before falling edge of BT_PCM_BCLK                                      | 50  | 1   | -    | ns   |

| 5         | Hold time for BT_PCM_SYNC after falling edge of BT_PCM_CLK                                         | 10  | -   | -    | ns   |

| 6         | Hold time of BT_PCM_OUT after BT_PCM_CLK falling edge                                              | -   | 1   | 175  | ns   |

| 7         | Setup time for BT_PCM_IN before BT_PCM_CLK falling edge                                            | 50  | 1   | -    | ns   |

| 8         | Hold time for BT_PCM_IN after BT_PCM_CLK falling edge                                              | 10  | -   | -    | ns   |

| 9         | Delay from falling edge of BT_PCM_CLK during last bit period to BT_PCM_OUT becoming high impedance | -   | 1   | 100  | ns   |

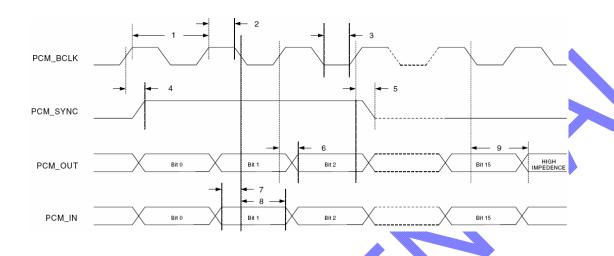

# Long Frame Sync, Master Mode

| Reference | Description                                                                                        | Min | Тур | Max  | Unit |

|-----------|----------------------------------------------------------------------------------------------------|-----|-----|------|------|

| 1         | PCM bit clock frequency                                                                            | 128 | -   | 2048 | kHz  |

| 2         | PCM bit clock high time                                                                            | 209 | -   | -    | ns   |

| 3         | PCM bit clock low time                                                                             | 209 | -   | -    | ns   |

| 4         | Delay from BT_PCM_CLK rising edge to BT_PCM_SYNC high                                              | -   | -   | 50   | ns   |

| 5         | Delay from BT_PCM_CLK rising edge to BT_PCM_SYNC low                                               | -   | -   | 50   | ns   |

| 6         | Delay from BT_PCM_CLK rising edge to data valid on BT_PCM_OUT                                      | -   | -   | 50   | ns   |

| 7         | Setup time for BT_PCM_IN before BT_PCM_CLK falling edge                                            | 50  | -   | -    | ns   |

| 8         | Hold time for BT_PCM_IN after BT_PCM_CLK falling edge                                              | 10  | -   | -    | ns   |

| 9         | Delay from falling edge of BT_PCM_CLK during last bit period to BT_PCM_OUT becoming high impedance | -   | -   | 50   | ns   |

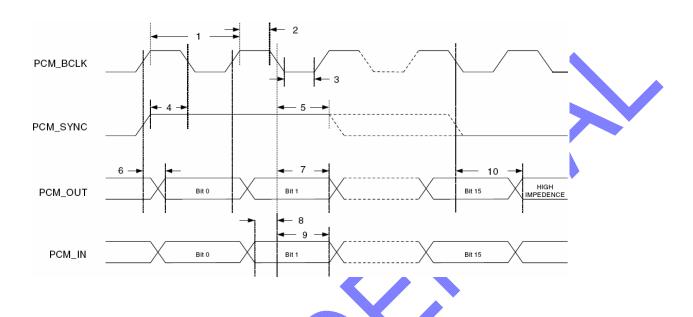

# Long Frame Sync, Slave Mode

| Reference | Description                                                                                                                                                      | Min | Тур | Max  | Unit |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| 1         | PCM bit clock frequency                                                                                                                                          | 128 | _   | 2048 | kHz  |

| 2         | PCM bit clock high time                                                                                                                                          | 209 | _   | -    | ns   |

| 3         | PCM bit clock low time                                                                                                                                           | 209 | _   | _    | ns   |

| 4         | Setup time for BT_PCM_SYNC before falling edge of BT_PCM_CLK during first bit                                                                                    | 50  | _   | _    | ns   |

|           | Hold time for BT_PCM_SYNC after falling edge of BT_PCM_CLK during second bit period. (BT_PCM_SYNC may go low any time from second bit period to last bit period) | 10  | -   | -    | ns   |

| 6         | Delay from rising edge of BT_PCM_CLK or BT_PCM_SYNC (whichever is later) to data valid for first bit on BT_PCM_OUT                                               |     | _   | 50   | ns   |

| 7         | Hold time of BT_PCM_OUT after BT_PCM_CLK falling edge                                                                                                            | _   | _   | 175  | ns   |

| 8         | Setup time for BT_PCM_IN before BT_PCM_CLK falling edge                                                                                                          | 50  | _   | _    | ns   |

| 9         | Hold time for BT_PCM_IN after BT_PCM_CLK falling edge                                                                                                            | 10  | _   | _    | ns   |

| 10        | Delay from falling edge of BT_PCM_CLK or BT_PCM_SYNC (whichever is later) during last bit in slot to BT_PCM_OUT becoming high impedance                          | _   | _   | 100  | ns   |

**Module Interface during Sleep mode**

| Module Interface during Sleep mode  |          |               |        |         |      |  |  |

|-------------------------------------|----------|---------------|--------|---------|------|--|--|

| WM-BN-BM-01                         | During   | Sleep         |        |         |      |  |  |

| Reset/Control                       | I/O Type | I/O           | Pull R |         |      |  |  |

| BT_RST_N                            | Digital  | Input         | None   |         |      |  |  |

| WL_RST_N (WLAN_ENABLE)              | Digital  | Input         | PD     |         |      |  |  |

| BT_GPIO_0 (BT_WAKE)                 | Digital  | Input         | None   |         |      |  |  |

| BT_GPIO_1 (UART_WAKEUP) Digital     | None     | Output (low)  | None   |         |      |  |  |

| UART                                |          |               |        |         |      |  |  |

| BT_UART_RXD                         | Digital  | Input         | None   |         |      |  |  |

| BT_UART_TXD                         | Digital  | Output (high) | None   |         |      |  |  |

| BT_UART_CTS_N                       | Digital  | Input         | None   |         |      |  |  |

| BT_UART_RTS_N                       | Digital  | Output (high) | None   |         |      |  |  |

| SPI (WLAN)                          |          |               |        |         |      |  |  |

| SPI_SDI                             | Digital  | Input         | None   |         |      |  |  |

| SPI_SDO                             | Digital  | Output        | None   |         |      |  |  |

| SPI_CLK                             | Digital  | Input         | None   |         |      |  |  |

| SPI_CS                              | Digital  | Input         | None   |         |      |  |  |

| SPI_IRQ                             | Digital  | Output        | None   |         |      |  |  |

| SDIO (WLAN)                         |          |               |        |         |      |  |  |

| SDIO_CLK                            | Digital  | Input         | None   |         |      |  |  |

| SDIO_CMD                            | Digital  | Bidirectional | PU     |         |      |  |  |

| SDIO_DATA0                          | Digital  | Bidirectional | PU     |         |      |  |  |

| SDIO_DATA1                          | Digital  | Bidirectional | PU     |         |      |  |  |

| SDIO_DATA2                          | Digital  | Bidirectional | PU     |         |      |  |  |

| SDIO_DATA3                          | Digital  | Bidirectional | PU     |         |      |  |  |

| Clock                               |          |               |        |         |      |  |  |

| XTAL_PU (CLK_REQ)                   | Digital  | -             | -      |         |      |  |  |

| WRF_EXTREFIN (32.768 kHz LPO Clock) | CLK      | Input         | None   |         |      |  |  |

| OSCIN (Ref Clock)                   | CLK      | Input         | None   |         |      |  |  |

| 4-Wire (PCM)                        |          | Master Mo     | de     | Slave I | Mode |  |  |

| BT_PCM_IN                           | Digital  | Input         | None   | Input   | None |  |  |

| BT_PCM_OUT                          | Digital  | High Z        | None   | High Z  | None |  |  |

| BT_PCM_CLK                          | Digital  | Output (low)  | None   | Input   | None |  |  |

| BT_PCM_SYNC                         | Digital  | Output (low)  | None   | Input   | None |  |  |

PD: Pull Down, PU: Pull UP

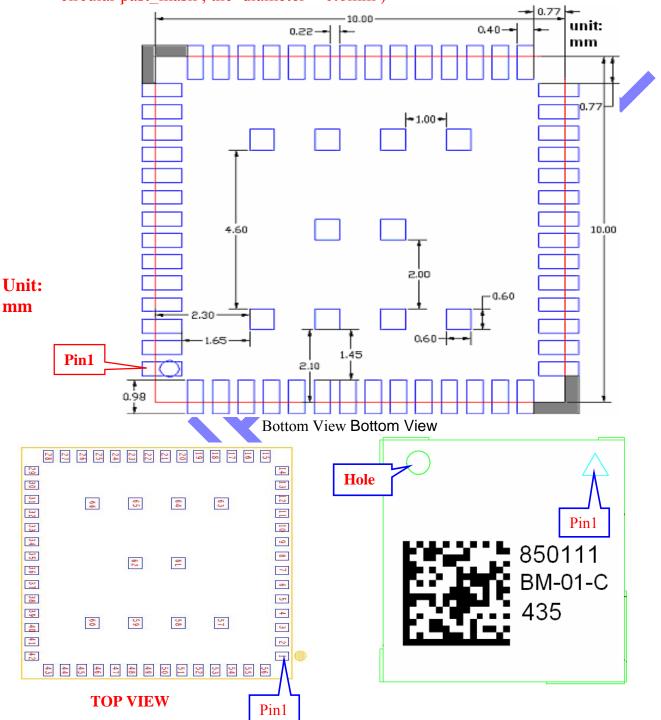

#### 5.9. DIMENSIONS, WEIGHT AND MOUNTING

The following paragraphs provide the requirements for the size, weight and mounting of the WM-BN-BM-01 module.

#### 5.9.1. DIMENSIONS

The size and thickness of the WM-BN-BM-01 module is "10 mm (W) x 10 mm (L) x 1.3 mm (H) +0.05/-0.13 mm "(Including Metal Shielding)

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI 27

#### 6. LEGAL, REGULATORY & OTHER TECHNICAL CONSTRAINTS

7. PIN OUT AND PIN DESCRIPTION

09

The WM-BN-BM-01 module is pre-tested to ensure that all requirements met as set forth in the following sections.

Final certification (module certification) requires the antenna of targeted system with a lead-time of 6 weeks. The product deliverable shall be a pre-tested WM-BN-BM-01 module. No module level certification on WM-BN-BM-01 module.

# 14 13 12 11 10 9 8 7 15 16 17 18 20 64 21 21 22 65 66 25 66 26 28 29 30 31 32 33 34 35 36

57

Top View

5 B

59

# **Pin Description**

| Pin-Nmnber | Pin-Define | Туре | Description                                                                                          |

|------------|------------|------|------------------------------------------------------------------------------------------------------|

| 1          | GND        | I    | Ground                                                                                               |

| 2          | GND        | I    | Ground                                                                                               |

| 3          | SW_RX2     | О    | Control signal for Antenna Diversity RF2                                                             |

| 4          | SW_RX1     | О    | Control signal for Antenna Diversity RF1                                                             |

| 5          | TDO        | I    | For debug only                                                                                       |

| 6          | TAG_TRST_N | I    | For debug only                                                                                       |

| 7          | WL_RST_N   | I    | Low asserting reset for WLAN core                                                                    |

| 8          | TCK        | I    | For debug only                                                                                       |

| 9          | TMS        | I    | For debug only                                                                                       |

|            |            |      | HOST_WAKE                                                                                            |

|            |            |      | Host wake up: Signal from the module to the host indicating that the module requires attention.      |

| 10         | WL GPIO 1  | О    | Asserted: Host device must wake-up or remain awake.                                                  |

|            |            |      | Deasserted: Host device may sleep when sleep criteria are met.                                       |

|            |            |      | The polarity of this signal is software configurable and can be asserted high or low.                |

|            |            |      |                                                                                                      |

|            |            | . 1  | WLAN_WAKE                                                                                            |

|            |            |      | WLAN device wake-up: Signal from the host to the module indicating that the host requires attention. |

| 11         | WL_GPIO_0  | I    | • Asserted: WLAN device must wake-up or remain awake.                                                |

|            |            |      | Deasserted: WLAN device may sleep when sleep criteria are met.                                       |

|            |            |      | The polarity of this signal is software configurable and can be asserted high or low.                |

| 12         | TDI        | I    | For debug only                                                                                       |

| 13         | VDDIO      | I    | Digital I/O supply $(1.8V \sim 3.3V)$                                                                |

| 14         | XTAL_PU    | О    | Crystal circuit/reference clock enable (programmable polarity, default is active high)               |

| 15         | SDIO_CLK   | I/O  | SDIO clock. This pin has an internal weak pull-up resistor.                                          |

| 16         | VDDIO_SD   | I    | SDIO/SPI I/O supply (1.8V ~ 3.3V)                                                                    |

| 17         | SDIO_D0    | I/O  | SDIO data 0. This pin has an internal weak pull-up resistor.                                         |

| 18         | SDIO_D2    | I/O  | SDIO data 2. This pin has an internal weak pull-up resistor.                                         |

| 19         | SDIO_CMD   | I/O  | SDIO command. This pin has an internal weak pull-up resistor.                                        |

| 20 | SDIO_D3      | I/O | SDIO data 3. This pin has an internal weak pull-up resistor.                                                                                                                         |

|----|--------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21 | SDIO_D1      | I/O | SDIO data 1. This pin has an internal weak pull-up resistor.                                                                                                                         |

|    |              |     | BT_WAKE Bluetooth device wake-up: Signal from the host to the module indicating that the host requires attention.  • Asserted: Bluetooth device must wake-up or remain awake.        |

| 22 | BT_GPIO0     | I   | Deasserted: Bluetooth device may sleep when sleep criteria are met.  The polarity of this signal is software configurable and can be asserted high or low.                           |

|    |              |     | HOST_WAKE Host wake up. Signal from the module to the host indicating that the module requires attention.                                                                            |

| 23 | BT_GPIO1     | О   | Asserted: Host device must wake-up or remain awake.                                                                                                                                  |

|    | _            |     | • Deasserted: Host device may sleep when sleep criteria are met.  The polarity of this signal is software configurable and can be asserted high or low.                              |

| 24 | BT_PCM_SYNC  | I/O | PCM sync signal, can be master (output) or slave (input)                                                                                                                             |

| 25 | BT_PCM_CLK   | I/O | PCM clock, can be master (output) or slave (input)                                                                                                                                   |

| 26 | GND          | I   | Ground                                                                                                                                                                               |

| 27 | VBAT         | I   | Battery supply input (2.8V~5V)                                                                                                                                                       |

| 28 | VBAT         | I   | Battery supply input (2.8V~5V)                                                                                                                                                       |

| 29 | VIN_IP2LDO-L | 0   | Connect to Boost L (3.3uH is required)                                                                                                                                               |

| 30 | VIN_1P2LDO   | I   | Connect to Boost L (3.3uH is required)                                                                                                                                               |

| 31 | WL_BT_REG_ON | I   | Used by PMU (along with WL_REG_ON) to decide whether or not to power down internal BCM4329 regulators. If both BT_REG_ON and WL_REG_ON are low then the regulators will be disabled. |

| 32 | BT_UART_RXD  | I/O | Bluetooth UART Serial Input. Serial data input for the HCI UART Interface.                                                                                                           |

| 33 | BT_UART_TXD  | I/O | Bluetooth UART Serial Output. Serial data output for the HCI UART Interface.                                                                                                         |

| 34 | GND          | I   | Ground                                                                                                                                                                               |

| 35 | GND          | I   | Ground                                                                                                                                                                               |

| 36 | WRF_EXTREFIN | I   | 32.768kHz external reference clock input                                                                                                                                             |

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI 30

| 1     | l             | 1 _ | l                                                                                             |  |

|-------|---------------|-----|-----------------------------------------------------------------------------------------------|--|

| 37    | GND           | I   | Ground                                                                                        |  |

| 38    | FM_AUDIO_OUT1 | О   | FM analog audio output channel 1                                                              |  |

| 39    | FM_ADIO_OUT_R | О   | FM analog audio output channel 2                                                              |  |

| 40    | GND           | I   | Ground                                                                                        |  |

| 41    | GND           | I   | Ground                                                                                        |  |

| 42    | GND           | I   | Ground                                                                                        |  |

| 43    | FM_RXP        | I   | FM radio RF antenna Port                                                                      |  |

| 44    | FM_RXN        | I   | FM radio RF antenna Port                                                                      |  |

| 45    | GND           | I   | Ground                                                                                        |  |

| 46    | GND           | I   | Ground                                                                                        |  |

| 47    | GND           | I   | Ground                                                                                        |  |

| 48    | GND           | I   | Ground                                                                                        |  |

| 49    | BT_UART_RTS_N | I/O | Bluetooth UART Request to Send. Active-low request-to-send signal for the HCI UART interface. |  |

| 50    | BT_PCM_IN     | I/O | PCM data input                                                                                |  |

| 51    | BT_UART_CTS_N | I/O | Bluetooth UART Clear to Send. Active-low clear-to-send signal for the HCI UART interface.     |  |

| 52    | BT_PCM_OUT    | I/O | PCM data output                                                                               |  |

| 53    | BT_RST_N      | 1   | Low asserting reset for BT core                                                               |  |

| 54    | GND           | I   | Ground                                                                                        |  |

| 55    | GND           | I   | Ground                                                                                        |  |

| 56    | ANT           | I/O | Antenna port for WLAN and Bluetooth                                                           |  |

| 57~66 | GND           | I   | Ground                                                                                        |  |

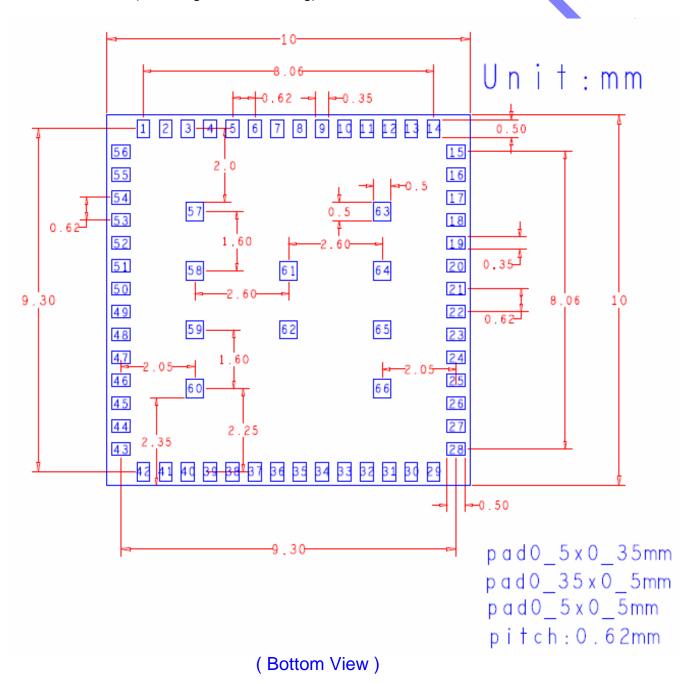

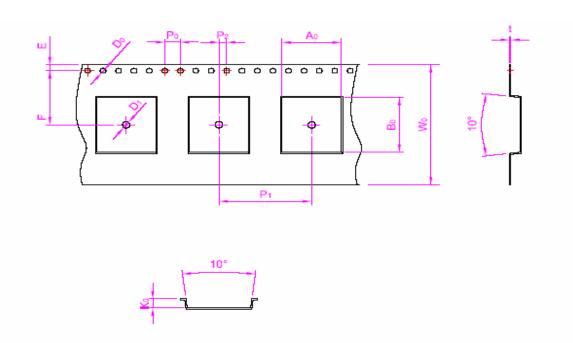

# 8. RECOMMEND FOOTPRINT

# 8.1 Footprint

(the Middle Ground PAD Past\_mask recommend use 2/3 pad size or the corner open circular past\_mask, the diameter = 0.6mm)

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI 32

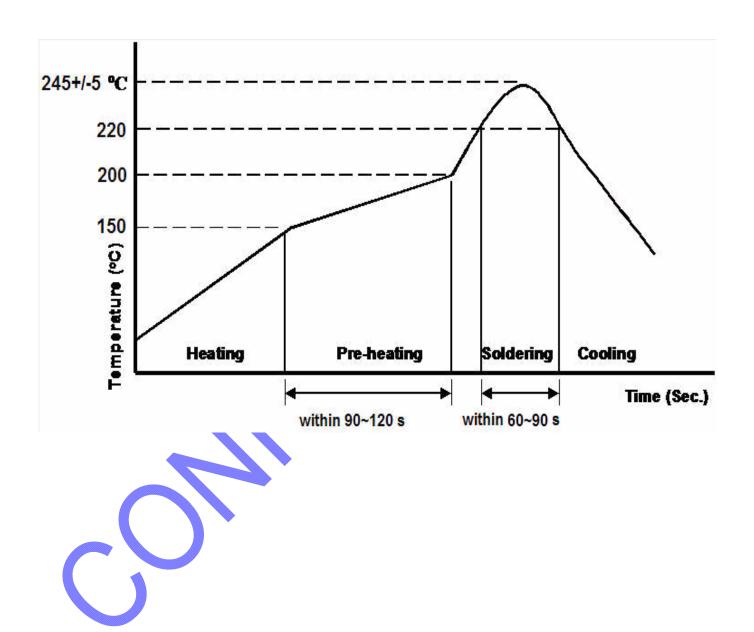

# 9. RECOMMANDED REFLOW PROFILE

# 10. PACKAGE AND STORAGE CONDITION

# 10.1 Package Dimension

# 10.2 ESD Level

# Note:

Surface Resistivity: Interior:  $10^9 \sim 10^{11} \Omega/\text{SQUARE}$ EXTERIOR:  $10^8 \sim 10^{12} \Omega/\text{SQUARE}$

Dimension:475\*420mm

3. Tolerance:+5,0mm

4. Color:

Background: Gray

Text: Red

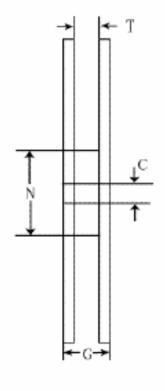

# 10.3 Tap/Reel Dimension

| Embossed        | Top cover |                |       |       |       |       |       |       |

|-----------------|-----------|----------------|-------|-------|-------|-------|-------|-------|

| carrier<br>tape | tape      | Each Item Size |       |       |       |       |       |       |

| W±0.15m/m       | W±0.15m/m | A              | B±0.5 | D±1.0 | C±0.2 | N±1.0 | T±0.1 | G±2.0 |

| 8               | 5.3/5.5   | 330            | 2.2   | 20.2  | 13    | 100   | 8.5   | 13.1  |

| 12              | 9.3       | 330            | 2.2   | 20.2  | 13    | 100   | 12.5  | 17.1  |

| 16              | 13.3      | 330            | 2.2   | 20.2  | 13    | 100   | 16.5  | 21.1  |

| 24              | 21.3      | 330            | 2.2   | 20.2  | 13    | 100   | 24.5  | 29.1  |

| 32              | 25.5      | 330            | 2.2   | 20.2  | 13    | 100   | 32.5  | 37.1  |

| 44              | 37.5      | 330            | 2.2   | 20.2  | 13    | 100   | 44.5  | 49.1  |

| 56              | 49.5      | 330            | 2.2   | 20.2  | 13    | 100   | 56.5  | 61.1  |

USI P/N:59-730113-02

| ITEM | Ao               | Bo             | D <sub>0</sub> | D <sub>1</sub> | E                            | F         | Ko             |

|------|------------------|----------------|----------------|----------------|------------------------------|-----------|----------------|

| SPEC | 9.9 <u>±</u> 0.1 | 9.9±0.1        | 1.50+0.1/=0    | 1.5+0.1/=0     | 1.75±0.1                     | 11.5±0.1  | 1.95±0.1       |

| ITEM | K1               | P <sub>0</sub> | P <sub>1</sub> | P <sub>2</sub> | P₀ X10                       | t         | W <sub>0</sub> |

| SPEC |                  | 4.00±0.1       | 12.0±0.1       | 2.00±0.1       | Cumulative Tolerance<br>±0.2 | 0.40±0.05 | 24±0.3         |

Length leader / trailer tape:

Leader tape:  $\geq$ 550mm which includes  $\geq$ 100mm of carrier tape with empty compartments and covered with tape; remaining part might be of cover tape only.

Trailer tape:  $\geq 160$ mm with empty compartments and covered with tape.

#### NOTES:

1.Material: Conductive Polystyrene (Recycle)

2.Color: Black

3.Surface resistance: 10<sup>6</sup> Ohms/square 以下

3.Cumulative tolerance per 10 pictches(Po) is ±0.2mm.

4.Carrier camber shall be not more than 1mm per 100mm,noncumulative over 250mm

5.A<sub>0</sub> & B<sub>0</sub> are measured on the plane by 0.3 mm above the bottom of the pocket,

6.K₀ Is measured from the Inside bottom of the pocket to the top surface of the carrier.

7.Pocket position relative to sprocket hold is measured as true position of pocket, not sprocket hold.

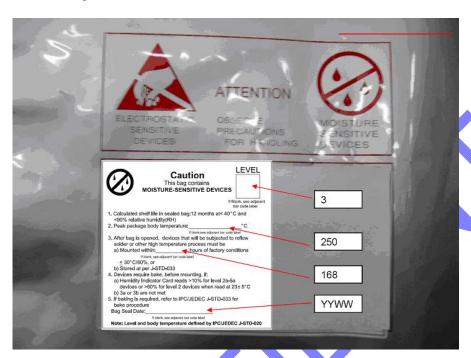

# 10.4 MSL Level / Storage Condition

| CAUTION This bag contains MOISTURE-SENSITIVE DEVICES                                                                                                                                                                                                                                                                                                                                                                                                            | 3                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 1. Calculated Shelf life in sealed bag: 12 months at < 40°C and < 90%Relative hurs. 2. Peak package body temperature 250 °C  If Blank, see adjacent bar code label. 3. After bag is opened, Devices that will be subjected to reflow solder or other high (a) Mounted within: 168 hrs. Of factory conditions ≤ 30°C/60% RH, (b) Stored at < 10°CRH.                                                                                                             | temperature process must |

| 4. Devices require bake, before mounting, it:  (a) Humidity indicator Card is >10% when read at 23±5°C  (b) 3a or 3b not met.  5. If baking is required, Devices may be baked for 24 hrs at 125±5°C  Note: If device containers cannot be subjected to high temperature  Or shorter bake times are desired. Reference IPC/JEDEC J-STD-033 for bake probable Seal Date:  Note: Level and body temperature defined by IPC, If Blank, see adjacent bar code label. |                          |

Half-Sine Shock

Sustained for Mechanical Shock under 2000G

Life cycle: 2 years

Broadcom is Trademark of 3'rd Party.

For Additional information, please contact the following:

Universal Scientific Industrial Co., Ltd.

#### Headquarters

141, Lane 351, Taiping Road, Sec. 1, Tsao-Tuen, Taiwan,

Http://www.usi.com.tw

Tel: + 886-49-2350876, 2325876

Fax: +886-49-3439561, 2337360,2351093

E-mail:usi@ms.usi.com.tw