# FCC ID: YNIJAZWARES13595

# **Technical Description :**

The brief circuit description is listed as follows :

- U1 and associated circuit act as optical mouse sensor.

- U2 and associated circuit act as 2.4GHz RF transceiver module.

- U3 and associated circuit act as MCU.

- U4 and associated circuit act as EEPROM.

- Y2 and associated circuit act as Clock Oscillator of U2.

- Y1 and associated circuit act as Clock Oscillator of U3.

# Antenna Used :

A patch antenna has been used.

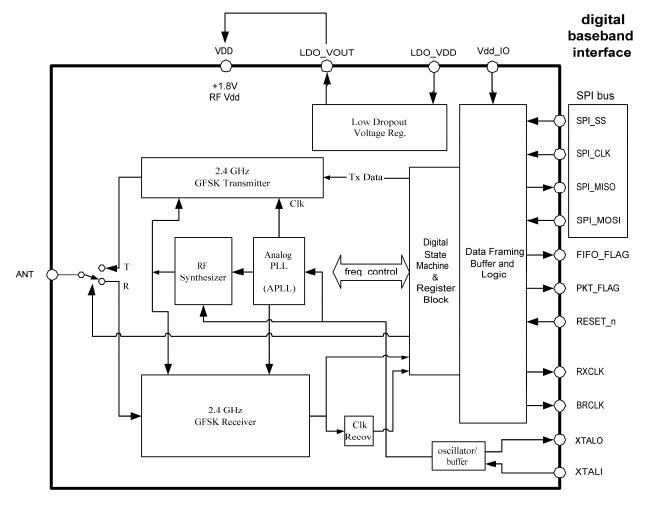

# SGN6210 RF Transceiver/Framer

**Production Data Sheet**

## **Product Description:**

The Signia SGN6210 IC is a low-cost, fully integrated CMOS radio frequency (RF) transceiver block, combined with a 64byte buffered framer block. In normal applications, the SGN6210 is connected to a low-cost microcomputer (MCU). The on-chip framer processes and stores the RF data in the background, unloading this critical timing function from the MCU. This lowers MCU speed requirements, expedites product development time, and frees the MCU for implementing additional product features.

The RF transceiver block is a self-contained, fast-hopping GFSK data modem, optimized for use in the widely available 2.4 GHz ISM band. It contains transmit, receive, VCO and PLL functions, including an on-chip channel filter and resonator, thus minimizing the need for external components. The receiver utilizes extensive digital processing for excellent overall performance, even in the presence of interference and transmitter impairments. Transmit power is digitally controlled. The low-IF receiver architecture results in sensitivity to -80 dBm or better, with impressive selectivity.

The framer register settings determine the over-the-air formatting characteristics. Transmit data is easily sent overthe-air as a complete frame of data, with preamble, address, payload, and CRC. Receiving data is just the opposite, using the preamble to train the receiver clock recovery, then the address is checked, then the data is reverse formatted for receive, followed by CRC. All of this is done in hardware to ease the programming and overhead requirements of the baseband MCU.

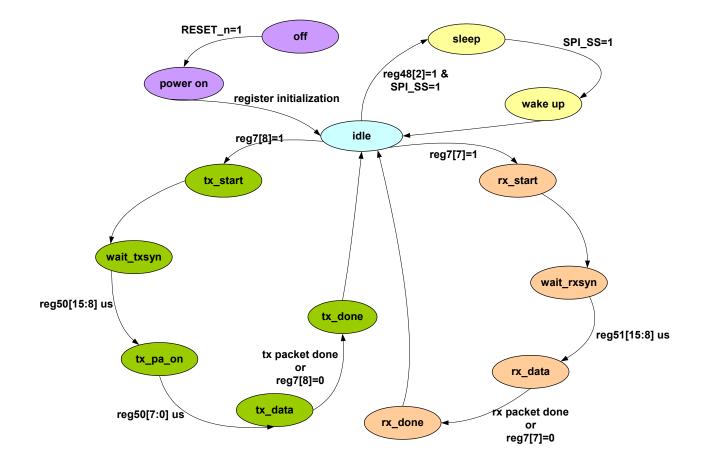

For longer battery life, power consumption is minimized by automatic enabling of the various transmit, receive, PLL, and PA sections, depending on the instantaneous state of the chip. A sleep mode is also provided for ultra low current consumption.

This product is supplied in lead-free, RoHS compliant, 32-lead 5x5 mm JEDEC standard QFN package, featuring an exposed pad on the bottom for best RF characteristics.

# Ordering Information

#### SGN6210

Signia Technologies, Inc. 500 Yosemite Dr., Suite 100 Milpitas, CA 95035 USA RF Transceiver/Framer

Phone: (408) 945-9988 FAX: (408) 945-9119 sales@signiatech.com

### **Key Features:**

- Combines 2.4 GHz GFSK RF transceiver with 8-bit data framer function

- Eliminates need for external software or hardware FIFO; offloads MCU for other tasks

- Simple microprocessor interface 4 wires for SPI, plus 3 wires for RST/buffer control

- Each transmit, receive buffer is 64 bytes deep

- Long packets are possible if buffers are read/written before overflow/underflow occurs

- Always 1 Mbps over-the-air symbol rate, regardless of MCU speed or architecture

- Preamble can be 1 to 8 bytes

- Supports 1, 2, 3, or 4 word address (up to 64 bits)

- Various Payload data formats to eliminate DC

offset, enhance receive clock recovery and BER

- Programmable data whitening

- Supports Forward Error Correction (FEC): none, 1/3, or 2/3

- Supports 16-bit CRC

- Power management for minimizing current consumption

- Lead-free 5x5mm QFN package with minimum RF parasitics

### **Applications:**

- Wireless devices that need quick time-to-market

- Battery Powered wireless devices

- Wireless streaming audio

- Home and factory automation

- Simple and fast wireless data networks

- Cordless headsets and Cellular Phones

- Wireless voice and VOIP

- Wireless security and access control

# SGN6210

### **Block Diagram**

### **Ratings**

| Absolute Maximum Ratings                |                             |      |      |      |      |  |

|-----------------------------------------|-----------------------------|------|------|------|------|--|

| Parameter                               | Symbol                      |      | Unit |      |      |  |

| i alameter                              |                             | MIN  | TYP  | MAX  | onic |  |

| Operating Temp.                         | T <sub>OP</sub>             | -40  |      | +85  | °C   |  |

| Storage Temp.                           | T <sub>STORAGE</sub>        | -55  |      | +125 | °C   |  |

| V <sub>DD_IO</sub> Supply Volt.         | V <sub>DDIO_MAX</sub>       |      |      | +3.7 | VDC  |  |

| V <sub>DD</sub> Supply Volt.            | $V_{\text{DD}\_\text{MAX}}$ |      |      | +2.5 |      |  |

| Applied Voltages to<br>Other Pins       | V <sub>OTHER</sub>          | -0.3 |      | +3.7 | VDC  |  |

| Input RF Level                          | P <sub>IN</sub>             |      |      | +10  | dBm  |  |

| Output Load mismatch ( $Z_0=50\Omega$ ) | VSWR <sub>OUT</sub>         |      |      | 10:1 | VSWR |  |

#### Notes:

- Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended operating conditions indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics section below.

- These devices are electro-static sensitive. Devices should be transported and stored in anti-static containers. Equipment and personnel contacting the devices need to be properly grounded. Cover workbenches with grounded conductive mats.

# **Electrical Characteristics**

The following specifications are guaranteed for  $T_A = 25 \degree C$ ,  $V_{DD} = 1.80 \pm 0.18$  VDC, unless otherwise noted:

| Parameter                          | Symbol                 | Specification             |                            |                    | Units | Test Condition and Notes                                                                                                                                         |  |

|------------------------------------|------------------------|---------------------------|----------------------------|--------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Falameter                          | Symbol                 | MIN                       | TYP                        | MAX                | Units | Test condition and notes                                                                                                                                         |  |

| Current Consumption                |                        |                           |                            |                    |       |                                                                                                                                                                  |  |

| Current Consumption - TX           | I <sub>DD_TX</sub>     |                           | 26                         |                    | mA    | P <sub>OUT</sub> = nominal output power                                                                                                                          |  |

| Current Consumption - RX           | I <sub>DD_RX</sub>     |                           | 25                         |                    | mA    |                                                                                                                                                                  |  |

| Current Consumption –<br>DEEP IDLE | I <sub>DD_D_IDLE</sub> |                           | 1.9                        |                    | mA    | RF Synthesizer and VCO: OFF<br>(see Reg. 21)                                                                                                                     |  |

| Current Consumption -<br>SLEEP     | I <sub>DD_SLP</sub>    |                           | 3.5                        |                    | uA    |                                                                                                                                                                  |  |

| Digital Inputs                     |                        |                           |                            |                    |       |                                                                                                                                                                  |  |

| Logic input high                   | V <sub>IH</sub>        | 0.8<br>V <sub>DD_io</sub> |                            | V <sub>DD_io</sub> | V     |                                                                                                                                                                  |  |

| Logic input low                    | VIL                    | 0                         |                            | 0.8                | V     |                                                                                                                                                                  |  |

| Input Capacitance                  | C_IN                   |                           |                            | 10                 | pF    |                                                                                                                                                                  |  |

| Input Leakage Current              | I_LEAK_IN              |                           |                            | 10                 | uA    |                                                                                                                                                                  |  |

| Digital Outputs                    |                        |                           |                            |                    |       |                                                                                                                                                                  |  |

| Logic output high                  | V <sub>он</sub>        | 0.8<br>V <sub>DD_io</sub> |                            | V <sub>DD_io</sub> | V     |                                                                                                                                                                  |  |

| Logic output low                   | V <sub>OL</sub>        |                           |                            | 0.4                | V     |                                                                                                                                                                  |  |

| Output Capacitance                 | C_OUT                  |                           |                            | 10                 | pF    |                                                                                                                                                                  |  |

| Output Leakage Current             | I_LEAK_OUT             |                           |                            | 10                 | uA    |                                                                                                                                                                  |  |

| Rise/Fall Time                     | T_RISE_OUT             |                           |                            | 5                  | nS    |                                                                                                                                                                  |  |

| Clock Signals                      |                        |                           |                            |                    |       |                                                                                                                                                                  |  |

| BRCLK output frequency             | F <sub>BRCLK</sub>     |                           | 1, 12,<br>or xtal<br>Freq. |                    | MHz   | Depends on Register settings. Always<br>either: 1 MHz Tx clock, 12 MHz APLL clock<br>(Tx, Rx, and Idle), or the buffered 12 MHz<br>crystal oscillator frequency. |  |

| SPI_CLK rise, fall time            | T <sub>r_spi</sub>     |                           |                            | 200                | nS    | Requirement for error-free register reading, writing.                                                                                                            |  |

| SPI_CLK frequency range            | F <sub>SPI</sub>       | 0                         | 12                         |                    | MHz   |                                                                                                                                                                  |  |

| Overall Transceiver                |                        |                           |                            |                    |       |                                                                                                                                                                  |  |

| Operating Frequency<br>Range       | F_op                   | 2400                      |                            | 2482               | MHz   |                                                                                                                                                                  |  |

| Antenna port mismatch              | VSWR_I                 |                           | <2:1                       |                    | VSWR  | Receive mode. Meas. using 50 Ohm balun.                                                                                                                          |  |

| (Z <sub>0</sub> =50Ω)              | VSWR_o                 |                           | <2:1                       |                    | VSWR  | Transmit mode. Meas. using 50 Ohm balun                                                                                                                          |  |

٦

Г

| Parameter                              |                       | Symbol                                | Specification |       |       | Units                    | Test Condition and Notes                                                        |                                                                                      |

|----------------------------------------|-----------------------|---------------------------------------|---------------|-------|-------|--------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|                                        | Gymbol                | MIN                                   | TYP           | MAX   | Units | rest condition and notes |                                                                                 |                                                                                      |

| Receive Sectio                         | n                     |                                       |               |       |       |                          | For BER ≤ 0.1%:                                                                 |                                                                                      |

| Receiver sensiti                       | vity                  |                                       |               | -85   | -80   | dBm                      | Meas. at ANT pin.                                                               |                                                                                      |

| Maximum useat                          | ole signal            |                                       | -20           |       |       | dBm                      |                                                                                 |                                                                                      |

| Input 3rd order i                      | ntercept point        | IIP <sub>3</sub>                      | -14           | -11   |       | dBm                      |                                                                                 |                                                                                      |

| Data (Symbol) ra                       | ate                   | Ts                                    |               | 1     |       | us                       |                                                                                 |                                                                                      |

| Min. Carrier/Inte                      | rference ratio        |                                       |               |       |       |                          | For BER $\leq 0.1\%$                                                            |                                                                                      |

| Co-Channel                             | Interference          | CI_cochannel                          |               | 9     | 11    | dB                       | -60 dBm desired signal.                                                         |                                                                                      |

| Adjacent Ch.<br>1MHz offset            | . Interference,       | CI_1                                  |               | -1.5  | 0     | dB                       | -60 dBm desired signal.                                                         |                                                                                      |

| Adjacent Ch<br>2MHz offset             | . Interference,       | Cl_2                                  |               | -30   |       | dB                       | -60 dBm desired signal.<br>Interference at 2 MHz below                          | desired signal.                                                                      |

| Adjacent Ch.<br><u>&gt;</u> 3MHz offse | . Interference,<br>et | Cl_3                                  |               | -40   |       | dB                       | -67 dBm desired signal.                                                         |                                                                                      |

| Image Frequ<br>Interference            | lency                 | CI_Image                              |               | -23   | -9    | dB                       | -60 dBm desired signal. Image freq. is always 2 MHz higher than desired signal. |                                                                                      |

| Adjacent (1M<br>interference           |                       | Cl_Image_11                           |               | -34   | -20   | dB                       | -67 dBm desired signal. Always 3 MHz higher than desired signal.                |                                                                                      |

| Out-of-Band Blo                        | ocking                | OBB_1                                 | -10           |       |       | dBm                      | 30 MHz to 2000 MHz                                                              | Meas. with                                                                           |

|                                        |                       | OBB_2                                 | -27           |       |       | dBm                      | 2000 MHz to 2400 MHz                                                            | ACX BF2520<br>ceramic filter<br>on ant. pin.<br>Desired<br>sig70 dBm,<br>BER ≤ 0.1%. |

|                                        |                       | OBB_3                                 | -27           |       |       | dBm                      | 2500 MHz to 3000 MHz                                                            |                                                                                      |

|                                        |                       | OBB_4                                 | -10           |       |       | dBm                      | 3000 MHz to 12.75 GHz                                                           |                                                                                      |

| Transmit Section                       |                       |                                       |               |       |       |                          | Reg. 9, bits 15-8 set to 000                                                    | 00000                                                                                |

| RF Output Powe                         | er                    | P <sub>AV</sub>                       |               | +2    |       | dBm                      | Power Level 0.<br>Meas. using ACX BL2012 50 Ohm balun.                          |                                                                                      |

| Modulation Cha                         | racteristics          |                                       |               |       |       |                          |                                                                                 |                                                                                      |

| Peak FM<br>Deviation                   | 00001111<br>pattern   | ∆f1 <sub>avg</sub>                    | 280           | 314   | 350   | kHz                      |                                                                                 |                                                                                      |

|                                        | 01010101<br>pattern   | Δf2 <sub>max</sub>                    | 230           |       |       | kHz                      | For at least 99.9% of all $\Delta f2_{max}$ meas.                               |                                                                                      |

| ISI, % Eye C                           | pen                   | $\Delta f2_{avg}$ / $\Delta f1_{avg}$ | 80            |       |       | %                        | 1010 data sequence referenced to<br>00001111 data sequence                      |                                                                                      |

| Zero Crossin                           | ng Error              | ZCERR                                 | -125          |       | 125   | ns                       | +/- 1/8 of Symbol Period                                                        |                                                                                      |

| In-Band Spuriou                        | is Emission           |                                       |               |       |       |                          |                                                                                 |                                                                                      |

| (+/- 550kHz)                           |                       | IBS_1                                 |               |       | -20   | dBc                      |                                                                                 |                                                                                      |

| 2MHz offset                            |                       | IBS_2                                 |               |       | -40   | dBm                      | ı                                                                               |                                                                                      |

| >3MHz offset                           |                       | IBS_3                                 |               |       | -60   | dBm                      |                                                                                 |                                                                                      |

| Out-of-Band Spurious                   |                       | OBS_O_1                               |               | < -60 | -36   | dBm                      | 30 MHz ~ 1 GHz                                                                  |                                                                                      |

| Emission, Opera                        | auon                  | OBS_O_2                               |               | -45   | -30   | dBm                      | 1 GHz ~ 12.75 GHz,<br>excludes desired signal.                                  |                                                                                      |

|                                        |                       | OBS_O_3                               |               | < -60 | -47   | dBm                      | 1.8 GHz ~ 1.9 GHz                                                               |                                                                                      |

|                                        |                       | OBS_O_4                               |               | < -65 | -47   | dBm                      | 5.15 GHz ~ 5.3 GHz                                                              |                                                                                      |

| Parameter                                               | Symbol           | Specification |       |       | Units  | Test Condition and Notes                    |                            |

|---------------------------------------------------------|------------------|---------------|-------|-------|--------|---------------------------------------------|----------------------------|

| i arameter                                              | Cymbol           | MIN           | TYP   | MAX   | Omto   | rest condition and notes                    |                            |

| RF VCO and PLL Section                                  |                  |               |       |       |        |                                             |                            |

| Typical PLL lock range                                  | FLOCK            | 2340          |       | 2560  | MHz    |                                             |                            |

| Tx, Rx Frequency Tolerance                              |                  |               |       |       | ppm    | Same as XTAL pins fre                       | equency tolerance          |

| Channel (Step) Size                                     |                  |               | 1     |       | MHz    |                                             |                            |

| SSB Phase Noise                                         |                  |               | -95   |       | dBc/Hz | 550kHz offset                               |                            |

|                                                         |                  |               | -115  |       | dBc/Hz | 2MHz offset                                 |                            |

| Crystal oscillator freq. range<br>(Reference Frequency) |                  |               | 12    |       | MHz    | Designed for 12 MHz crystal reference freq. |                            |

| Crystal oscillator<br>digital trim range, typ.          |                  | -12           |       | +12   | ppm    |                                             |                            |

| RF PLL Settling Time                                    | T <sub>HOP</sub> |               | 75    | 150   | uS     |                                             |                            |

| Out-of-Band Spur. Emissions                             | OBS_1            |               | < -75 | -57   | dBm    | 30 MHz ~ 1 GHz                              | IDLE state,                |

|                                                         | OBS_2            |               | -68   | -47   | dBm    | 1 GHz ~ 12.75 GHz                           | Synthesizer and<br>VCO ON. |

| LDO Voltage Regulator<br>Section                        |                  |               |       |       |        |                                             |                            |

| Dropout Voltage                                         | V <sub>do</sub>  |               |       | (tbd) | V      | Measured during Receive state               |                            |

| Quiescent current                                       | ۱ <sub>q</sub>   |               |       | 6     | uA     | No-load current consumed by LDO reg.        |                            |

# **Pin Description**

| Pin No.     | Pin Name  | Туре   | Description                                                                                                                                     |

|-------------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2        | VDD       | PWR    | Power supply voltage.                                                                                                                           |

| 3           | NC        |        | DO NOT CONNECT. Reserved for factory test.                                                                                                      |

| 4           | GND       | GND    | Ground connection.                                                                                                                              |

| 5           | ANT       | 50Ω RF | RF input/output.                                                                                                                                |

| 6           | VDD       | PWR    | Power supply voltage.                                                                                                                           |

| 7, 8        | NC        |        | DO NOT CONNECT. Reserved for factory test.                                                                                                      |

| 9, 10       | VDD       | PWR    | Power supply voltage.                                                                                                                           |

| 11, 12, 13  | NC        |        | DO NOT CONNECT. Reserved for factory test.                                                                                                      |

| 14          | BRCLK     | 0      | Outputs 1MHz Tx symbol clock, 12 MHz APLL, or crystal clock.                                                                                    |

|             |           |        | See register definitions for details.                                                                                                           |

| 15          | PKT_FLAG  | 0      | Transmit/Receive packet process flag.                                                                                                           |

| 16          | RXCLK     | 0      | Receiver symbol timing clock recovery output.<br>Fixed at 1 MHz fundamental rate.                                                               |

| <u>17</u>   | FIFO_FLAG | 0      | FIFO full/empty flag.                                                                                                                           |

| 18          | VDD       | PWR    | Power supply voltage.                                                                                                                           |

| 19          | GND       | GND    | Ground connection.                                                                                                                              |

| 20          | SPI_SS    | I      | Enable line for the SPI bus. Active low.                                                                                                        |

| 21          | SPI_MOSI  | I      | Data input for the SPI bus.                                                                                                                     |

| 22          | SPI_CLK   |        | Clock line for the SPI bus.                                                                                                                     |

| 23          | RESET_n   | I      | When RESET_n is low, most of the chip shuts down to conserve power.                                                                             |

|             |           |        | When raised high, RESET_n is used to turn on the chip, restoring all registers to their default value.                                          |

| 24          | SPI_MISO  | 0      | Data output for the SPI bus.                                                                                                                    |

| 25          | VDD_IO    | PWR    | Vdd for the digital i/o pins. Nominally +3.3 VDC.                                                                                               |

| 26          | LDO_VDD   | PWR    | Unregulated input to the on-chip LDO volt. regulator.                                                                                           |

| 27          | LDO_VOUT  | PWR    | +1.8V output of the on-chip LDO voltage regulator.                                                                                              |

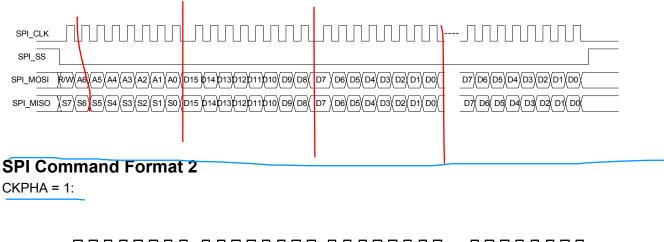

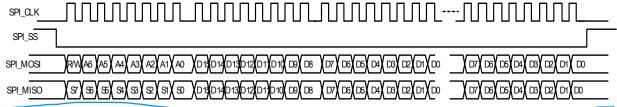

| 28          | СКРНА     | DI     | SPI Clock phase.<br>When 0, SPI MOSI data clocked in on rising edge of SPI_CLK.<br>When 1, SPI_MOSI data clocked in on falling edge of SPI_CLK. |

| 29          | GND       | GND    | Ground connection.                                                                                                                              |

| 30          | VDD       | PWR    | Power supply voltage.                                                                                                                           |

| 31          | XTALO     | ΑO     | Output of the crystal oscillator gain block.                                                                                                    |

| 32          | XTALI     | AI     | Input to the crystal oscillator gain block.                                                                                                     |

| Exposed pad | GND       | GND    | Ground connection.                                                                                                                              |

# **SPI Command Format 1**

CKPHA = 0:

## **Register Information**

For the latest register value recommendations, please contact your Signia technical representative.

## **State Diagram**

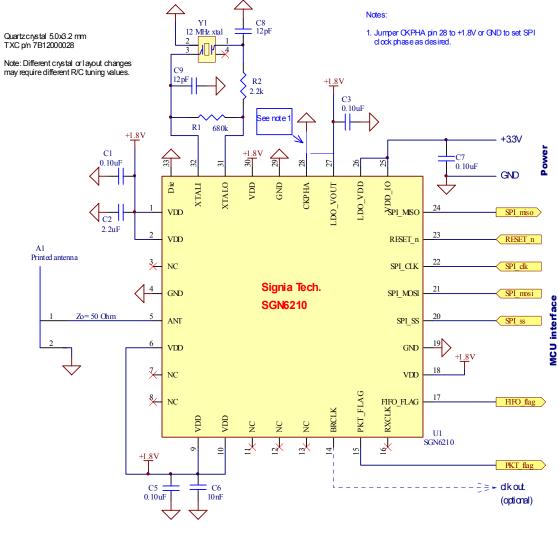

# **Typical Application**

Simple, low-power (0 dBm) 2.4 GHz RF Transceiver with Framing and data buffers

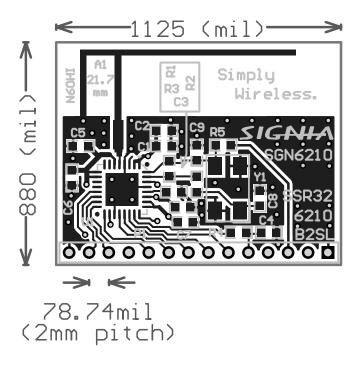

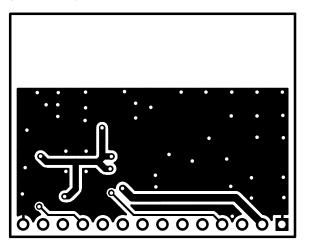

# **Typical 2-Layer PCB Layout**

Top Layer:

Bottom Layer, as viewed through the top layer:

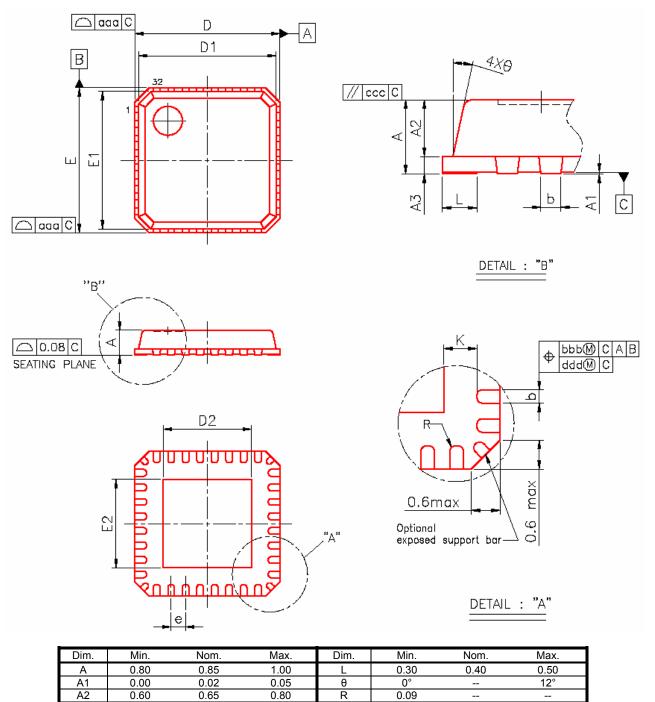

## Package Outline

QFN 32 Lead Exposed Pad Package, 5x5 mm Pkg. 0.5mm Pitch (JEDEC) MO-220-A

A3

b

D/E

D1/E1

D2/E2

е

0.18

3.15

0.20 REF

0.25

5.00 BSC

4.75 BSC

3.30

0.50 BSC

Κ

aaa

bbb

ccc

ddd

0.30

3.45

0.20

--

--

--

---

--

---

--

---

--

---

0.15

0.10

0.10

0.05

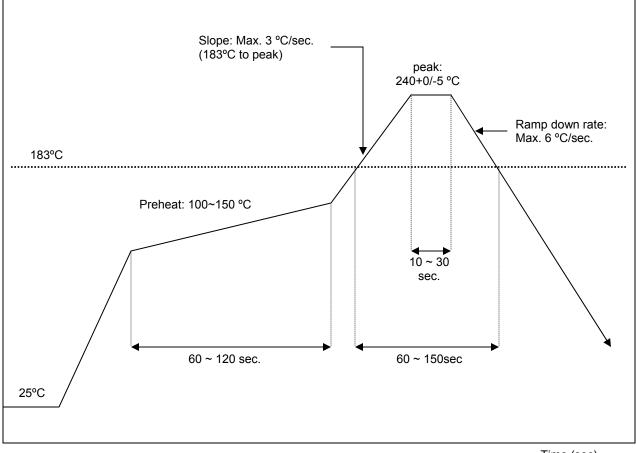

## **IR Reflow Standard**

Follow : IPC/JEDEC J-STD-020 B

Condition :

Average ramp-up rate (183°C to peak): 3 °C/sec. max. Preheat: 100~150°C 60~120sec

Temperature maintained above 183°C: 60~150 seconds

Time within 5°C of actual peak temperature: 10 ~ 30 sec.

Peak temperature: 240+0/-5 °C

Ramp-down rate: 6 °C/sec. max.

Time 25°C to peak temperature: 6 minutes max.

Cycle interval: 5 minutes

Time (sec)

### **Contact Information**

#### Signia U.S.

Signia Technologies, Inc. 500 Yosemite Drive, Suite 100 Milpitas, CA 95035 USA

Phone: (408) 945-9988 Fax: (408) 945-9119

sales@signiatech.com

#### Signia Taiwan

Signia Technologies Co., Ltd. 7F., No.68, Sec. 3, Nanjing E. Rd., Jhongshan District, Taipei City 104, Taiwan

(Tel) 886-02-2515-1956 (Fax) 886-02-2515-1963

<u>AlexJ@signiatech.com</u>

#### Internet

http://www.signiatech.com/

Information given in this data sheet is believed to be accurate and reliable at the time of printing; however, Signia reserves the right to make changes to products and specifications without notice.

Signia makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Signia assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages.

#### LIFE SUPPORT POLICY

SIGNIA PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF SIGNIA.

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.