# **JODY-W3** series

## Host-based modules with Wi-Fi 6 and Bluetooth 5.3

System integration manual

#### Abstract

This document describes the system integration of JODY-W3 series modules. These host-based modules support concurrent dual-band Wi-Fi 802.11n/ac/ax and Bluetooth® 5.3 and are designed for both simultaneous and independent operations. JODY-W3 modules include an integrated MAC/baseband processor and RF front-end components of automotive grade.

## **Document information**

| Title                         | JODY-W3 series            |            |  |

|-------------------------------|---------------------------|------------|--|

| Subtitle                      | nd Bluetooth 5.3          |            |  |

| Document type                 | System integration manual |            |  |

| Document number               | UBX-19011209              |            |  |

| Revision and date             | R09                       | 4-May-2023 |  |

| <b>Disclosure Restriction</b> | C1-Public                 |            |  |

| Product status                   | Corresponding content status |                                                                                        |  |  |  |  |

|----------------------------------|------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|

| Functional Sample                | Draft                        | For functional testing. Revised and supplementary data will be published later.        |  |  |  |  |

| In Development /<br>Prototype    | Objective Specification      | Target values. Revised and supplementary data will be published later.                 |  |  |  |  |

| Engineering Sample               | Advance Information          | Data based on early testing. Revised and supplementary data will be published later.   |  |  |  |  |

| Initial Production               | Early Production Information | Data from product verification. Revised and supplementary data may be published later. |  |  |  |  |

| Mass Production /<br>End of Life | Production Information       | Document contains the final product specification.                                     |  |  |  |  |

#### This document applies to the following products:

| Product name |  |

|--------------|--|

| JODY-W354-A  |  |

| JODY-W374-A  |  |

| JODY-W374    |  |

| JODY-W377-A  |  |

| JODY-W377    |  |

For information about the related hardware, software, and status of listed product types, see the JODY-W3 series data sheet [1].

u-blox or third parties may hold intellectual property rights in the products, names, logos, and designs included in this document. Copying, reproduction, or modification of this document or any part thereof is only permitted with the express written permission of u-blox. Disclosure to third parties is permitted for clearly public documents only. The information contained herein is provided "as is" and u-blox assumes no liability for its use. No warranty, either express or implied, is given, including but not limited to, with respect to the accuracy, correctness, reliability, and fitness for a particular purpose of the information. This document may be revised by u-blox at any time without notice. For the most recent documents, visit www.u blox.com . Copyright © u-blox AG.

Ŧ

## Contents

| D | ocur | men         | t information                | 2    |

|---|------|-------------|------------------------------|------|

| C | onte | ents        | 5                            | 3    |

| 1 | Sy   | /ste        | em description               | 7    |

|   | 1.1  | Ove         | erview                       | 7    |

|   | 1.2  | Мос         | dule architecture            | 7    |

|   | 1.2  | 2.1         | Block diagrams               | 8    |

|   | 1.3  | Pin         | definition                   | 9    |

|   | 1.3  | 3.1         | Pin attributes               | 9    |

|   | 1.3  | 3.2         | Pin assignment               | . 10 |

|   | 1.3  | 3.3         | Pin list                     | . 10 |

|   | 1.4  | Sup         | pply interfaces              | . 13 |

|   | 1.4  | l.1         | Main supply inputs           | . 13 |

|   | 1.4  | 1.2         | Regulated DC power supply    | . 14 |

|   | 1.5  | Sys         | tem function interfaces      | . 14 |

|   | 1.5  | 5.1         | Power-up sequence            | . 14 |

|   | 1.5  | 5.2         | Reset                        | . 15 |

|   | 1.5  | 5.3         | Power-off sequence           | . 15 |

|   | 1.5  | 5.4         | Wake-up signals              | . 16 |

|   | 1.5  | 5.5         | Configuration pins           | . 16 |

|   | 1.5  | 5.6         | Power states                 | 17   |

|   | 1.6  | Dat         | a communication interfaces   | 17   |

|   | 1.6  | 6.1         | SDIO 3.0 interface           | 17   |

|   | 1.6  | 6.2         | PCle interface               | . 18 |

|   | 1.6  | 6.3         | High-speed UART interface    | . 19 |

|   | 1.6  | 6.4         | PCM/I2S - Audio interface    | . 19 |

|   | 1.7  | Coe         | existence interfaces         | . 19 |

|   | 1.7  | '.1         | РТА                          | . 19 |

|   | 1.7  | <b>'</b> .2 | WCI-2                        | .20  |

|   | 1.8  | Ant         | enna interfaces              | .20  |

|   | 1.8  | 3.1         | Wi-Fi and Bluetooth antennas | .20  |

|   | 1.8  | 3.2         | Approved antenna designs     | .20  |

|   | 1.9  | Oth         | er remarks                   | 21   |

|   | 1.9  | 9.1         | Unused pins                  | 21   |

|   | 1.9  | 9.2         | GPIO usage                   | 21   |

| 2 | De   | esig        | n-in                         | .22  |

|   | 2.1  | Ove         | erview                       | .22  |

|   | 2.2  | Ant         | enna interfaces              | .22  |

|   | 2.2  | 2.1         | Antenna design               | .23  |

|   | 2.3  | Sup         | ply interfaces               | .28  |

|   | 2.3  | 3.1         | Module supply design         | .28  |

|   | 2.4 Dat  | a communication interfaces                                         | 29 |

|---|----------|--------------------------------------------------------------------|----|

|   | 2.4.1    | PCI Express                                                        |    |

|   | 2.4.2    | SDIO 3.0                                                           |    |

|   | 2.4.3    | High-speed UART interface                                          |    |

|   | 2.5 Oth  | er interfaces and notes                                            |    |

|   | 2.6 Ger  | eral high-speed layout guidelines                                  |    |

|   | 2.6.1    | General considerations for schematic design and PCB floor-planning | 32 |

|   | 2.6.2    | Component placement                                                |    |

|   | 2.6.3    | Layout and manufacturing                                           |    |

|   | 2.7 Mo   | dule footprint and paste mask                                      |    |

|   | 2.8 The  | rmal guidelines                                                    |    |

|   | 2.9 ESI  | ) guidelines                                                       |    |

|   | 2.10 Des | ign-in checklists                                                  |    |

|   | 2.10.1   | Schematic checklist                                                |    |

|   | 2.10.2   | Layout checklist                                                   |    |

| 3 | Softv    | /are                                                               |    |

|   | 3.1 Ava  | ilable software packages                                           |    |

|   | 3.1.1    | Open-source Linux/Android drivers                                  |    |

|   | 3.1.2    | Proprietary drivers                                                |    |

|   | 3.1.3    | Additional u-blox software deliverables                            |    |

|   | 3.2 Sup  | ported kernel versions                                             |    |

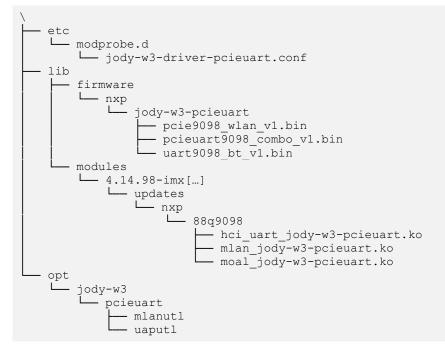

|   | 3.3 Driv | ver package structure                                              |    |

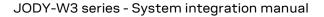

|   | 3.4 Sof  | tware architecture                                                 |    |

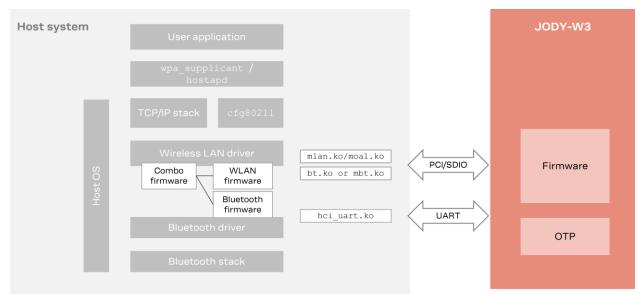

|   | 3.4.1    | Wi-Fi driver                                                       |    |

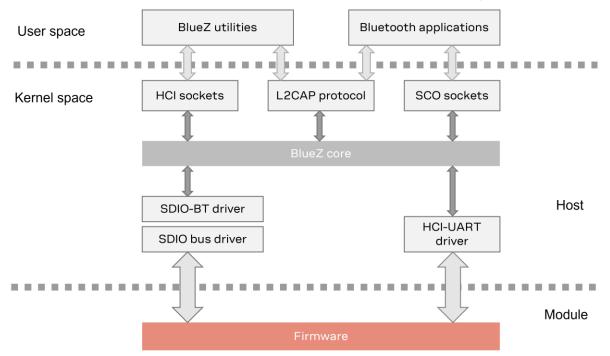

|   | 3.4.2    | Bluetooth driver                                                   | 41 |

|   | 3.5 Cor  | npiling the drivers                                                |    |

|   | 3.5.1    | Prerequisites                                                      |    |

|   | 3.6 Dep  | ploying the drivers                                                |    |

|   | 3.6.1    | Firmware                                                           | 43 |

|   | 3.6.2    | Configuration utilities                                            | 43 |

|   | 3.6.3    | Additional software requirements                                   |    |

|   | 3.7 Yoc  | to meta layer                                                      |    |

|   | 3.8 Rur  | itime usage                                                        | 45 |

|   | 3.8.1    | Device detection                                                   | 45 |

|   | 3.8.2    | Driver and firmware loading                                        | 45 |

|   | 3.8.3    | Verification                                                       |    |

|   | 3.8.4    | Assigning MAC addresses                                            |    |

|   | 3.8.5    | Antenna configuration                                              |    |

|   | 3.8.6    | Access point                                                       |    |

|   | 3.8.7    | Station mode                                                       |    |

|   | 3.8.8    | Bluetooth usage                                                    | 53 |

|   | 3.9 Cor  | figuration of TX power limits and energy detection                 | 54 |

|   | 3.9.1    | Wi-Fi power table                                                  | 54 |

|   |          |                                                                    |    |

| 3.9  | 9.2                                                                                                                                        | Bluetooth TX power levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57                                                      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 3.9  | 9.3                                                                                                                                        | Adaptivity configuration (energy detection)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58                                                      |

| 3.9  | 9.4                                                                                                                                        | OFDMA resource unit TX power configuration for 802.11ax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59                                                      |

| 3.10 | Drive                                                                                                                                      | er debugging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60                                                      |

| 3.1  | 10.1                                                                                                                                       | Compile-time debug options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 60                                                      |

| 3.1  | 10.2                                                                                                                                       | Runtime debug options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 60                                                      |

| Ha   | andli                                                                                                                                      | ng and soldering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61                                                      |

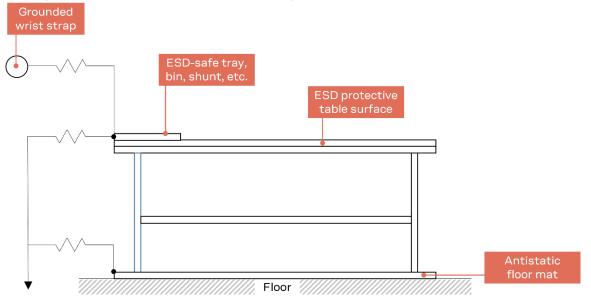

| 4.1  | Spec                                                                                                                                       | cial ESD handling precautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61                                                      |

| 4.2  | Pack                                                                                                                                       | aging, shipping, storage, and moisture preconditioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61                                                      |

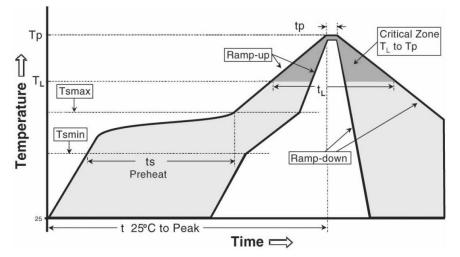

| 4.3  | Reflo                                                                                                                                      | ow soldering process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 62                                                      |

| 4.3  | 3.1                                                                                                                                        | Cleaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 63                                                      |

| 4.3  | 3.2                                                                                                                                        | Other notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63                                                      |

| Re   | egula                                                                                                                                      | atory compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64                                                      |

| 5.1  | Gene                                                                                                                                       | eral requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64                                                      |

| 5.2  | Euro                                                                                                                                       | pean Union regulatory compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64                                                      |

| 5.2  | 2.1                                                                                                                                        | CE End-product regulatory compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64                                                      |

| 5.2  | 2.2                                                                                                                                        | Compliance with the RoHS directive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 65                                                      |

| 5.3  | Grea                                                                                                                                       | t Britain regulatory compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65                                                      |

| 5.3  | 3.1                                                                                                                                        | UK Conformity Assessed (UKCA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65                                                      |

| 5.4  | Unit                                                                                                                                       | ed States/Canada end-product regulatory compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 65                                                      |

| 5.4  | 4.1                                                                                                                                        | United States compliance statement (FCC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66                                                      |

| 5.4  | 4.2                                                                                                                                        | Canada compliance statement (ISED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67                                                      |

| 5.4  | 4.3                                                                                                                                        | Referring to the u-blox FCC/ISED certification ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68                                                      |

| 5.4  | 4.4                                                                                                                                        | Obtaining own FCC/ISED certification ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 68                                                      |

| 5.4  | 4.5                                                                                                                                        | Antenna requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 69                                                      |

| 5.4  | 4.6                                                                                                                                        | Configuration control and software security of end-products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 70                                                      |

| 5.4  | 4.7                                                                                                                                        | Operating frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .71                                                     |

| 5.4  | 4.8                                                                                                                                        | End product labeling requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .71                                                     |

| 5.5  | Аррі                                                                                                                                       | roved antennas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73                                                      |

| Pr   | oduo                                                                                                                                       | ct testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 74                                                      |

| 6.1  | u-blo                                                                                                                                      | ox in-line production testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 74                                                      |

| 6.2  | OEN                                                                                                                                        | 1 manufacturer production test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 75                                                      |

| pper | ndix                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76                                                      |

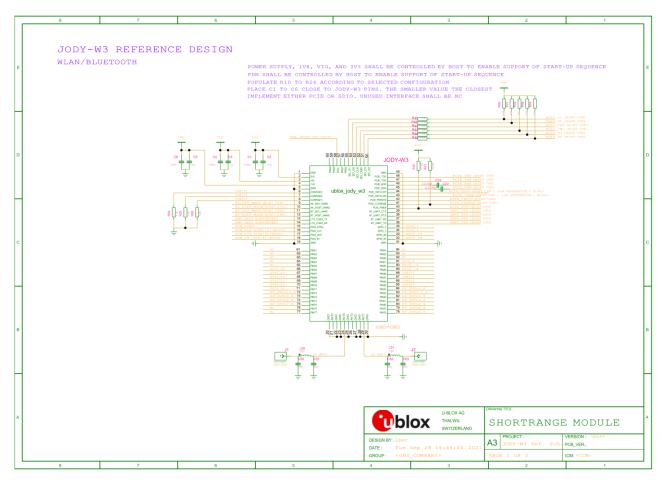

| Re   | efere                                                                                                                                      | ence schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76                                                      |

| W    | i-Fi t                                                                                                                                     | transmit output power limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77                                                      |

| B.1  | FCC,                                                                                                                                       | /ISED regulatory domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 77                                                      |

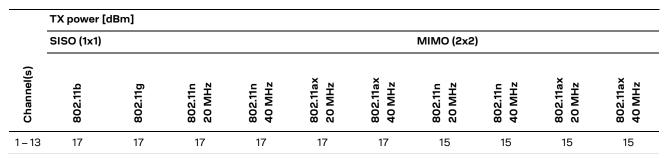

| B.1  | 1.1                                                                                                                                        | Wi-Fi output power for 2.4 GHz band                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 77                                                      |

| B.1  |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |

| B.1  | 1.3                                                                                                                                        | 802.11ax OFDMA power limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 78                                                      |

| B.2  |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |

| В.2  | 2.1                                                                                                                                        | Wi-Fi output power for 2.4 GHz band                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 79                                                      |

| В.2  |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |

|      | 3.9<br>3.10<br>3.10<br>3.1<br>4.1<br>4.2<br>4.3<br>4.2<br>4.3<br>5.1<br>5.2<br>5.3<br>5.4<br>5.4<br>5.4<br>5.4<br>5.4<br>5.4<br>5.4<br>5.4 | 3.9.3<br>3.9.4<br>3.10 Drive<br>3.10.1<br>3.10.2<br>Handli<br>4.1 Spec<br>4.2 Pack<br>4.3 Refle<br>4.3.1<br>4.3.2<br><b>Regula</b><br>5.1 Gene<br>5.2 Euro<br>5.2.1<br>5.2.2<br>5.3 Great<br>5.3.1<br>5.4 Unit<br>5.4.2<br>5.4.3<br>5.4.4<br>5.4.5<br>5.4.5<br>5.4.6<br>5.4.5<br>5.4.6<br>5.4.7<br>5.4.8<br>5.4.5<br>5.4.6<br>5.4.7<br>5.4.8<br>5.4.5<br>5.4.6<br>5.4.7<br>5.4.8<br>5.4.5<br>5.4.6<br>5.4.7<br>5.4.8<br>5.4.5<br>5.4.6<br>5.4.7<br>5.4.8<br>5.5 Apple<br><b>Produe</b><br>6.1 u-ble<br>6.2 OEN<br><b>Produe</b><br>6.1 u-ble<br>5.4.7<br>5.4.8<br>5.5 Apple<br><b>B</b> .1.1<br><b>B</b> .1.2<br><b>B</b> .1.3<br><b>B</b> .2.1<br><b>B</b> .2.1 | 3.9.3       Adaptivity configuration (energy detection) |

|    | B.2.3 802.11ax OFDMA power limits | 79 |

|----|-----------------------------------|----|

| С  | Glossary                          |    |

|    | -                                 |    |

| Re | evision history                   |    |

| Co | ontact                            |    |

## 1 System description

## 1.1 Overview

JODY-W3 series modules provide complete short range transceiver solutions that can be easily integrated into automotive and industrial applications. The modules are intended for the most advanced in-car infotainment and connectivity systems and deliver the highest data rates in Wi-Fi using advanced Wi-Fi 6 802.11ax technology. JODY-W3 series modules operate in concurrent dual-bands, Wi-Fi 2.4 and 5 GHz, dual-MAC, and 2x2 MIMO. They also support Bluetooth 5.3 features, like extended advertising, long range, and 2 Mbit/s (PHY) data rate.

JODY-W3 series modules are provided in a surface-mount device (SMD) component packages based on the NXP AW690/88Q9098/88W9098 chipsets. The modules require a host processor running on a Linux or Android operating system and connect to the host processor through either PCIe or SDIO for Wi-Fi, high-speed UART for Bluetooth, and PCM/I2S for Bluetooth audio.

## 1.2 Module architecture

JODY-W3 series modules support Wi-Fi 6 802.11a/b/g/n/ac/ax and Bluetooth 5.3 operations:

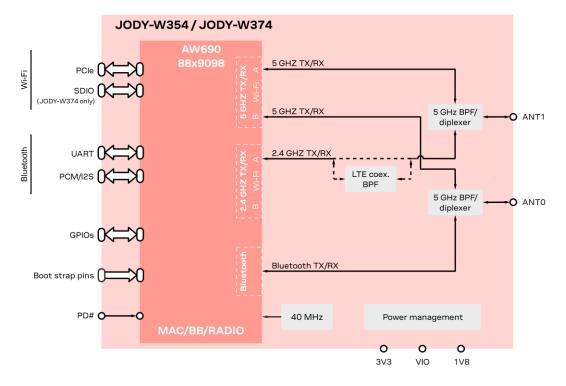

- JODY-W354 and JODY-W374 provide two antenna ports, one for dual band Wi-Fi (2.4 GHz and 5 GHz) and one for 5 GHz Wi-Fi and Bluetooth.

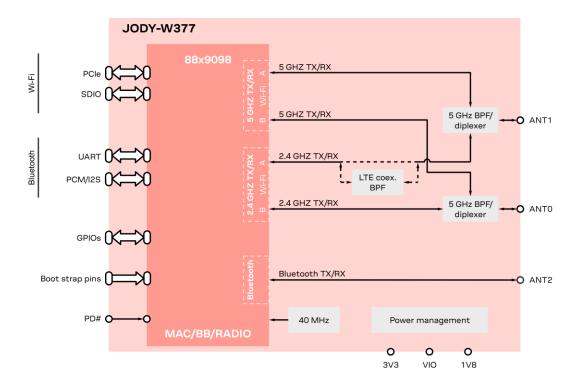

- JODY-W377 provides three antenna ports, two for dual band Wi-Fi (2.4 GHz and 5 GHz) and one dedicated for Bluetooth.

| Variant /     | LTE    | Antenna configurat             | Host inter                 | Host interfaces |         |           |

|---------------|--------|--------------------------------|----------------------------|-----------------|---------|-----------|

| Ordering code | filter | ANTO                           | ANT1                       | ANT2            | Wi-Fi   | Bluetooth |

| JODY-W354-00A | -      |                                | 2.4 GHz and 5 GHz<br>Wi-Fi |                 | DOI-    |           |

| JODY-W354-20A | •      | — 5 GHz Wi-Fi and<br>Bluetooth |                            |                 | PCle    | UART      |

| JODY-W374-00A | -      |                                |                            | -               |         |           |

| JODY-W374-20A | •      | Blaetooth                      |                            |                 |         |           |

| JODY-W374-00B | -      |                                |                            |                 | PCle or | UART      |

| JODY-W377-00A | -      | 2.4 GHz and 5 GHz              | 2.4 GHz and 5 GHz          | Bluetooth       | SDIO    |           |

| JODY-W377-00B | -      | Wi-Fi                          | Wi-Fi                      |                 |         |           |

Table 1 shows the available antenna and host interface configurations for JODY-W3 series modules.

Table 1: Supported configurations of the JODY-W3 module series

Some JODY-W3 series modules use a dedicated LTE coexistence band-pass filter in the 2.4 GHz Wi-Fi path. Module variants equipped with an LTE coexistence filter, as shown in Table 1, are recommended for designs with co-located LTE devices operating in bands 7, 38, 40, or 41.

## 1.2.1 Block diagrams

Figure 1 shows the block diagram for the JODY-W354 and JODY-W374 module variants.

#### Figure 1: JODY-W354 and JODY-W374 block diagram

Figure 2 shows the block diagram for the JODY-W377 module variant.

#### Figure 2: JODY-377 block diagram

## 1.3 Pin definition

#### 1.3.1 Pin attributes

- Function: Pin function

- **Pin name:** Name of the package pin or terminal

- **Pin number:** Package pin numbers associated with each signal

- **Power:** Voltage domain that powers the pin

- **Type:** Signal type description:

- I = Input

- O = Output

- I/O = Input and Output

- D = Open drain

- DS = Differential

- PWR = Power

- GND = Ground

- PU = Internal Pull-Up

- PD = Internal Pull-Down

- H = High-impedance pin

- RF = Radio interface

- Description: Pin description and notes, including alternate pin functions

- Active: Pin state in Active mode

- **Power down:** Pin state in Power Down mode

## 1.3.2 Pin assignment

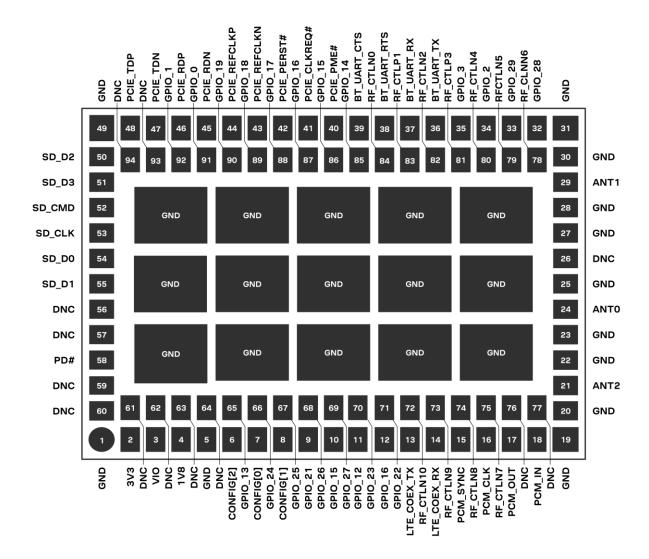

Figure 3: JODY-W3 series module pin assignments (top view)

## 1.3.3 Pin list

| Function               | Pin name     | Pin no.                                                     | Power | Туре | Description               | Active | Power down |

|------------------------|--------------|-------------------------------------------------------------|-------|------|---------------------------|--------|------------|

| Power                  | 3V3          | 2                                                           |       | PWR  | 3.3 V power supply        | PWR    | -          |

| and                    | VIO          | 3                                                           |       | PWR  | 1.8 V or 3.3 V VIO supply | PWR    | -          |

| ground                 | 1V8          | 4                                                           |       | PWR  | 1.8 V power supply        | PWR    | -          |

|                        | GND          | 1, 5, 19,<br>20, 22,<br>23, 25,<br>27, 28,<br>30, 31,<br>49 | GND   | GND  | Ground                    | GND    | -          |

|                        | Exposed pins | -                                                           | GND   | GND  | Connect to Ground         | GND    | -          |

| SDIO                   | SD_CLK       | 53                                                          | 1V8   | I    | SDIO clock input          | I      | Tristate   |

| host                   | SD_CMD       | 52                                                          | 1V8   | I/O  | SDIO command line         | I/O    | Tristate   |

| interface <sup>1</sup> | SD_D0        | 54                                                          | 1V8   | I/O  | SDIO data line bit [0]    | I/O    | Tristate   |

|                        |              |                                                             |       |      |                           |        |            |

<sup>1</sup> SDIO pins not used on JODY-W354

| Function                     | Pin name     | Pin no. | Power | Туре    | Description                                                                                                                                     | Active | Power dowr |

|------------------------------|--------------|---------|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|

|                              | SD_D1        | 55      | 1V8   | I/O     | SDIO data line bit [1]                                                                                                                          | I/O    | Tristate   |

|                              | SD_D2        | 50      | 1V8   | I/O     | SDIO data line bit [2]                                                                                                                          | I/O    | Tristate   |

|                              | SD_D3        | 51      | 1V8   | I/O     | SDIO data line bit [3]                                                                                                                          | I/O    | Tristate   |

| Bluetooth<br>host            | BT_UART_TX   | 36      | VIO   | 0       | BT UART output signal.<br>Connect to Host RX                                                                                                    | 0      | Drive low  |

| nterface                     | BT_UART_RX   | 37      | VIO   | I       | BT UART input signal.<br>Connect to Host TX                                                                                                     | I      | Tristate   |

|                              | BT_UART_RTS  | 38      | VIO   | 0       | BT UART request-to-send output signal.<br>Connect to Host CTS                                                                                   | 0      | Drive high |

|                              | BT_UART_CTS  | 39      | VIO   | I       | BT UART clear-to-send input signal.<br>Connect to Host RTS                                                                                      | I      | Tristate   |

| Digital<br>audio<br>nterface | PCM_SYNC     | 15      | VIO   | I/O     | PCM frame sync.<br>Input if slave, Output if master<br>Alternate function: I2S Word Select                                                      | I/O    | Tristate   |

|                              | PCM_CLK      | 16      | VIO   | I/O     | PCM clock<br>Input if slave, Output if master<br>Alternate function: I2S bit clock<br>Configuration pin CON[10]<br>See also Configuration pins. | I/O    | Tristate   |

|                              | PCM_IN       | 18      | VIO   | Ι       | PCM data input<br>Alternate function: I2S data in<br>Configuration pin CON[8]<br>See also Configuration pins.                                   | I      | Tristate   |

|                              | PCM_OUT      | 17      | VIO   | 0       | PCM data output<br>Alternate function: I2S data out<br>Configuration pin CON[9]<br>See also Configuration pins.                                 | 0      | Tristate   |

| <b>SPIO</b>                  | GPIO_21      | 9       | VIO   | I/O     | GPIO[21]/W_DISABLE1n                                                                                                                            | I/O    | Tristate   |

| nterface                     | WL_HOST_WAKE | 10      | VIO   | I/O     | Wi-Fi wake-up from Module / GPIO[15]<br>Configuration pin CON[5]<br>See also Configuration pins.                                                | I/O    | Tristate   |

|                              | GPIO_12      | 11      | VIO   | I/O     | GPIO[12]/UART_DSRn/W_DISABLE2n                                                                                                                  | I/O    | Tristate   |

|                              | BT_HOST_WAKE | 12      | VIO   | I/O     | BT wake-up from Module / GPIO[16]<br>Configuration pin CON[6]<br>See also Configuration pins.                                                   | I/O    | Tristate   |

|                              | GPIO_31      | 13      | VIO   | 0       | JTAG_TDO (output) / GPIO[31]<br>LTE coexistence UART TX <sup>2</sup>                                                                            | 0      | Tristate   |

|                              | GPIO_30      | 14      | VIO   | I       | JTAG_TDI (input) / GPIO[30]<br>LTE coexistence UART RX <sup>2</sup>                                                                             | I      | Tristate   |

|                              | GPIO_28      | 32      | VIO   | I/O     | JTAG_TCK (input) / GPIO[28]                                                                                                                     | I/O    | Tristate   |

|                              | GPIO_29      | 33      | VIO   | I/O     | JTAG_TMS (input) / GPIO[29]                                                                                                                     | I/O    | Tristate   |

|                              | GPIO_2       | 34      | VIO   | I/O     | GPIO[2] /<br>PTA external radio state signal (input)                                                                                            | I/O    | Tristate   |

|                              | GPIO_3       | 35      | VIO   | I/O     | GPIO[3]                                                                                                                                         | I/O    | Tristate   |

|                              | GPIO_14      | 85      | VIO   | I/O, PD | GPIO[14]<br>Configuration pin CON[4]<br>See also Configuration pins.                                                                            | I/O    | Tristate   |

|                              | WL_HOST_WAKE | 86      | VIO   | I/O     | Wi-Fi wake-up from Module / GPIO[15]<br>Configuration pin CON[5]<br>See also Configuration pins.                                                | I/O    | Tristate   |

<sup>2</sup> LTE coexistence UART not supported in current firmware releases

| Function               | Pin name     | Pin no. | Power | Туре | Description                                                                                                                    | Active | Power down |

|------------------------|--------------|---------|-------|------|--------------------------------------------------------------------------------------------------------------------------------|--------|------------|

|                        |              |         |       |      | Same function as pin 10.                                                                                                       |        |            |

|                        | GPIO_13      | 65      | VIO   | I/O  | GPIO[13] / UART_DTRn                                                                                                           | I/O    | Drive high |

|                        | GPIO_24      | 66      | VIO   | I/O  | GPIO[24]                                                                                                                       | I/O    | Tristate   |

|                        | GPIO_25      | 67      | VIO   | I/O  | GPIO[25]                                                                                                                       | I/O    | Drive high |

|                        | GPIO_26      | 68      | VIO   | I/O  | GPIO[26]                                                                                                                       | I/O    | Tristate   |

|                        | GPIO_27      | 69      | VIO   | I/O  | GPIO[27]                                                                                                                       | I/O    | Tristate   |

|                        | GPIO_23      | 70      | VIO   | I/O  | GPIO[23]                                                                                                                       | I/O    | Drive low  |

|                        | GPIO_22      | 71      | VIO   | I/O  | GPIO[22]                                                                                                                       | I/O    | Drive high |

|                        | BT_HOST_WAKE | 87      | VIO   | I/O  | Bluetooth wake-up from module/GPIO[16]<br>Configuration pin CON[6]<br>See also Configuration pins.<br>Same function as pin 12. | I/O    | Tristate   |

|                        | GPIO_17      | 88      | VIO   | I/O  | GPIO[17] /<br>PTA external radio grant signal (output)<br>Configuration pin CON[7]<br>See also Configuration pins.             | I/O    | Tristate   |

|                        | GPIO_18      | 89      | VIO   | I/O  | GPIO[18] /<br>Independent software reset for Wi-Fi<br>subsystem (input) /<br>PTA request from the external radio<br>(input)    | I/O    | Tristate   |

|                        | GPIO_19      | 90      | VIO   | I/O  | GPIO[19] /<br>Independent software reset for<br>Bluetooth subsystem (input) /<br>PTA external radio priority signal (input)    | I/O    | Tristate   |

|                        | GPIO_0       | 91      | VIO   | I/O  | GPIO[0]                                                                                                                        | I/O    | Drive low  |

|                        | GPIO_1       | 92      | VIO   | I/O  | GPIO[1] /<br>Independent software reset for<br>Bluetooth subsystem (input) /<br>PTA external radio priority signal (input)     | I/O    | Tristate   |

| PCle host<br>interface | PCIE_PME#    | 40      | VIO   | I/O  | PCle wake signal<br>(input/output, active low)<br>Note: Pull-up required on host side                                          | I/O    | -          |

|                        | PCIE_CLKREQ# | 41      | VIO   | I/O  | PCle clock request<br>(input/output, active low)<br>Note: Pull-up required on host side                                        | I      | -          |

|                        | PCIE_PERST#  | 42      | VIO   | I/O  | PCle host indication to reset the device<br>(input, active low)<br>Note: Muxed with GPIO[20]                                   | I/O    | Drive high |

|                        | PCIE_REFCLKN | 43      | 1V8   | I    | PCle negative differential clock input                                                                                         | I      | -          |

|                        | PCIE_REFCLKP | 44      | 1V8   | I    | PCle positive differential clock input                                                                                         | I      | -          |

|                        | PCIE_RDN     | 45      | 1V8   | I    | PCle negative differential data input<br>Note: place a 220nF coupling capacitor<br>close to host CPU output.                   | I      | -          |

|                        | PCIE_RDP     | 46      | 1V8   | I    | PCle positive differential data input<br>Note: place a 220nF coupling capacitor<br>close to host CPU output.                   | I      | -          |

|                        | PCIE_TDN     | 47      | 1V8   | 0    | PCle negative differential data output                                                                                         | 0      | -          |

|                        | PCIE_TDP     | 48      | 1V8   | 0    | PCle positive differential data output                                                                                         | 0      | -          |

| Host<br>interface      | CONFIG[0]    | 7       | 1V8   | I    | Host interface configuration pin<br>See also Configuration pins.                                                               | I      | Tristate   |

|                        | CONFIG[1]    | 8       | 1V8   | 1    | Host interface configuration pin                                                                                               | 1      | Tristate   |

| Function                  | Pin name    | Pin no.                                                              | Power | Туре  | Description                                                                                                              | Active | Power down               |

|---------------------------|-------------|----------------------------------------------------------------------|-------|-------|--------------------------------------------------------------------------------------------------------------------------|--------|--------------------------|

| config-                   |             |                                                                      |       |       | See also Configuration pins.                                                                                             |        |                          |

| uration                   | CONFIG[2]   | 6                                                                    | 1V8   | I     | Host interface configuration pin                                                                                         | I      | Tristate                 |

|                           |             |                                                                      |       |       | See also Configuration pins.                                                                                             |        |                          |

| RF                        | RF_CNTL10_N | 72                                                                   | VIO   | 0     | RF Control output low                                                                                                    | 0      | Drive low                |

| control <sup>3</sup>      | RF_CNTL9_N  | 73                                                                   | VIO   | 0     | RF Control output high                                                                                                   | 0      | Drive high               |

|                           | RF_CNTL8_N  | 74                                                                   | VIO   | 0     | RF Control output low                                                                                                    | 0      | Drive low                |

|                           | RF_CNTL7_N  | 75                                                                   | VIO   | 0     | RF Control output high                                                                                                   | 0      | Drive high               |

|                           | RF_CNLT6_N  | 78                                                                   | VIO   | 0     | RF Control output low                                                                                                    | 0      | Drive low                |

|                           | RF_CNTL5_N  | 79                                                                   | VIO   | 0     | RF Control output high                                                                                                   | 0      | Drive high               |

|                           | RF_CNTL4_N  | 80                                                                   | VIO   | 0     | RF Control output low                                                                                                    | 0      | Drive low                |

|                           | RF_CNTL3_P  | 81                                                                   | VIO   | 0     | RF Control output high                                                                                                   | 0      | Drive high               |

|                           | RF_CNTL2_N  | 82                                                                   | VIO   | 0     | RF Control output low                                                                                                    | 0      | Drive low                |

|                           | RF_CNTL1_P  | 83                                                                   | VIO   | 0     | RF Control output high                                                                                                   | 0      | Drive high               |

|                           | RF_CNTL0_N  | 84                                                                   | VIO   | 0     | RF Control output low                                                                                                    | 0      | Drive low                |

| Clock /<br>Power-<br>down | PD#         | 58                                                                   | 1V8   | I, PU | Full Power-down of the chipset<br>(input, active low) (51 kΩ to 1V8)<br>O = full power-down mode<br>1 = normal operation | I      | Drive high<br>through PU |

| Radio                     | ANTO        | 24                                                                   |       | RF    | Antenna signal 0<br>See also Antenna interfaces                                                                          | RF     | -                        |

|                           | ANT1        | 29                                                                   |       | RF    | Antenna signal 1<br>See also Antenna interfaces                                                                          | RF     | -                        |

|                           | ANT2        | 21                                                                   |       | RF    | Antenna signal 2 (JODY-W377)<br>Not used (JODY-W354, JODY-W374)<br>See also Antenna interfaces                           | RF     | -                        |

| Other                     | DNC         | 26, 56,<br>57, 59,<br>60, 61,<br>62, 63,<br>64, 76,<br>77, 93,<br>94 | -     | -     | Do not connect                                                                                                           | -      | -                        |

Table 2: JODY-W3 series module pinout

## 1.4 Supply interfaces

## 1.4.1 Main supply inputs

JODY-W3 series modules are powered through the **3V3/VIO/1V8** pins. An integrated Buck converter supplied from the **1V8** generates the core voltage to the embedded systems ASIC. The **3V3** power rail is mainly used to supply the internal power amplifiers.

The current consumed through the **VIO** and **1V8**, and **3V3** pins by JODY-W3 series modules can vary by several orders of magnitude depending on the operation mode and state. Current consumption can change from the high current consumption during Wi-Fi transmission at maximum RF power level in connected-mode, to the low current consumption during low power idle-mode with the power saving configuration enabled.

For a detailed description on the supply voltage requirements, see the JODY-W3 series data sheet [1].

<sup>&</sup>lt;sup>3</sup> Not implemented

| Rail | Allowable ripple (peak to peak) <sup>4</sup> over DC supply | Current consumption, peak |

|------|-------------------------------------------------------------|---------------------------|

| 3V3  | 30 mV <sub>pk-pk</sub>                                      | 800 mA⁵                   |

| 1V8  | 30 mV <sub>pk-pk</sub>                                      | 1300 mA⁵                  |

| VIO  | 30 mV <sub>pk-pk</sub>                                      | 5 mA <sup>6</sup>         |

Table 3: Summary of voltage supply requirements

## **1.4.2** Regulated DC power supply

JODY-W3 series modules must be powered by a regulated DC power supply, such as an LDO or SMPS. The appropriate type for your design depends on the main power source of the application.

SMPS is the ideal choice when the source of the main supply has a significantly higher voltage than that of the JODY-W3 series module. SMPS then provides the best power efficiency for your application and minimizes the current drawn from the main supply source. LDO is a better choice if the main supply voltage is close to the JODY-W3 series module supply voltages. Linear regulators are not recommended to step-down high voltages as these devices dissipate a considerable amount of energy.

⚠ When choosing SMPS, ensure that the AC ripple voltage at switching frequency does not violate the requirements specified in Table 3.

Regardless of the chosen DC power regulator, it is crucial that it can supply the high-peak current consumed by the module. When designing the module supply, a contingency of at least 20% over the stated peak current is recommended.

## 1.5 System function interfaces

#### 1.5.1 Power-up sequence

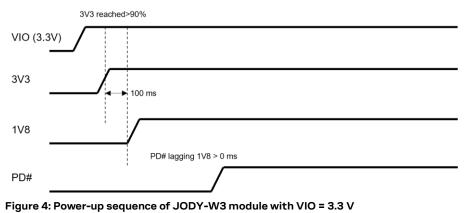

**PD#** is ideally held low during start up and released when the power is stable, or later when the module must be turned on. **PD#** is powered by the **1V8** voltage domain and is connected by a 51 k $\Omega$  pull-up resistor to **1V8. PD#** follows the **1V8** supply if it is not actively driven by the host.

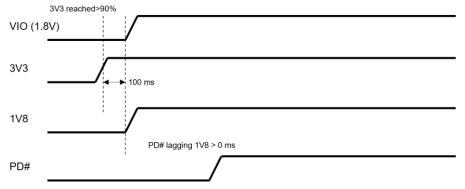

The power-up sequence of JODY-W3 with **VIO** set to 3.3 V is shown in Figure 4. In this configuration, enable **VIO** first, followed by other supplies shortly thereafter.

<sup>&</sup>lt;sup>4</sup> Ripple measured on the power connectors of u-blox EVK.

<sup>&</sup>lt;sup>5</sup> Peak current during concurrent dual band 2x2 operation.

<sup>&</sup>lt;sup>6</sup> The current consumption for VIO depends on how GPIO's and other digital pins are used and could significantly exceed the number stated here for specific customizations.

The power up sequence for JODY-W3 with **VIO** set to 1.8 V is shown in Figure 5. In this configuration, the start-up sequence must start with **3V3** followed by **VIO** and **1V8**.

Figure 5. Power-up sequence of JODY-W3 module with VIO=1.8 V

Power down mode can only be entered through PD# assertion by the host. PD# must be asserted for a minimum of 100 ms.

#### 1.5.2 Reset

Although external reset is not a prerequisite for correct operation, it can be asserted by the host controller through **PD#** in the event of any abnormal module behavior. The **PD#** pin may be connected to a reset signal from the host.

JODY-W3 series modules are reset to a default operating state by any of the following events:

- Power on: Module is powered on and internal voltages are good

- **PD#** assert: The device is reset when the **PD#** input pin is <0.2 V and transitions from low to high

- A firmware download to the module is required after each reset. For information describing how to download the firmware, see also Software.

#### **1.5.3** Power-off sequence

JODY-W3 modules enter Power Down mode when **PD#** is asserted. After assertion when **PD#** has reached below 0.2 V, the power on **3V3/VIO/1V8** supplies can be removed and the module enters the Power Off mode. **3V3/VIO/1V8** can be switched low simultaneously or with **1V8** leading **3V3**. The timing of **VIO** does not care.

## 1.5.4 Wake-up signals

JODY-W3 series modules provides module-to-host wake-up signals, used to exit the host from any sleep mode over Wi-Fi or Bluetooth. Wake-up signals are powered by the **VIO** voltage domain.

| Name         | I/O | Description                                                                                                            |

|--------------|-----|------------------------------------------------------------------------------------------------------------------------|

| WL_HOST_WAKE | I/O | Wi-Fi Module-to-host wake-up signal (output) / GPIO[15]<br>Used as configuration pin, see also Configuration pins.     |

| BT_HOST_WAKE | I/O | Bluetooth Module-to-host wake-up signal (output) / GPIO[16]<br>Used as configuration pin, see also Configuration pins. |

Table 4: Wake-up signal definitions

#### 1.5.5 Configuration pins

JODY-W3 series modules support configuration pins to set specific parameters following a reset. The definition and function of these configuration pins changes immediately (approx. 1 ms) to their initial function after reset, as described in the pin definitions, Table 2.

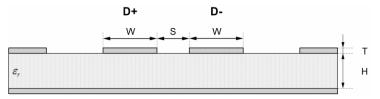

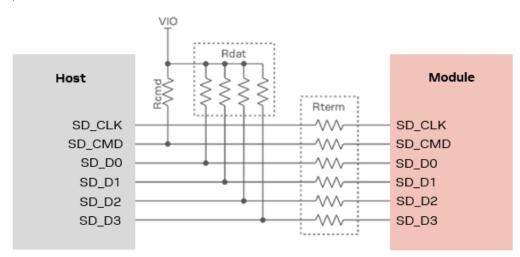

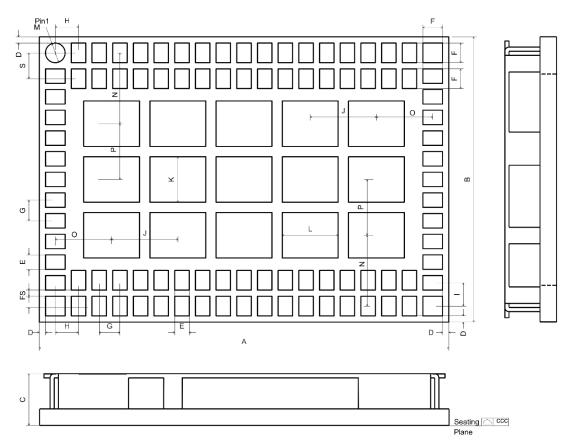

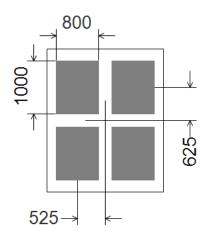

The interface combinations associated with each boot option are as follows: