**Lingo**

**RF Tune\_Up Information**

**2008/12/01 (REV.1.0)**

CONFIDENTIAL

---

## Radio Control

This chapter describes the different modes the nRF24L01 radio transceiver can operate in and the parameters used to control the radio.

The nRF24L01 has a built-in state machine that controls the transitions between the different operating modes of the chip. The state machine takes input from user defined register values and internal signals.

### 1. Operational Modes

The nRF24L01 can be configured in four main modes of operation. This section describes these modes.

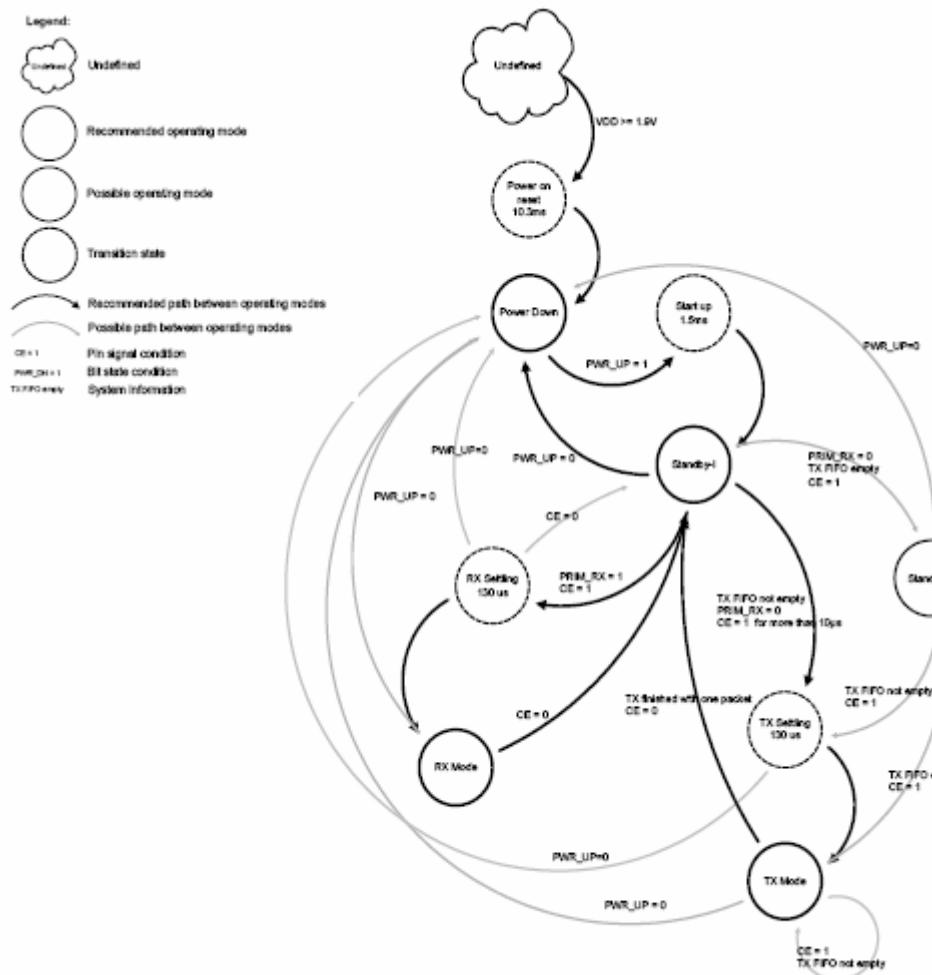

#### 1.1. State diagram

The state diagram (Figure 3.) shows the modes the nRF24L01 can operate in and how they are accessed. The nRF24L01 is undefined until the VDD becomes 1.9V or higher. When this happens nRF24L01 enters the Power on reset state where it remains in reset until it enters the Power Down mode. Even when the nRF24L01 enters Power Down mode the MCU can control the chip through the SPI and the Chip Enable (CE) pin. Three types of states are used in the state diagram. “Recommended operating mode” is a state that is used during normal operation. “Possible operating mode” is a state that is allowed to use, but it is not used during normal operation. “Transition state” is a time limited state used during start up of the oscillator and settling of the PLL.

Figure 3. Radio control state diagram

### 1.2. Power Down Mode

In power down mode nRF24L01 is disabled with minimal current consumption. In power down mode all the register values available from the SPI are maintained and the SPI can be activated. For start up time see Table 13. on page 22. Power down mode is entered by setting the PWR\_UP bit in the CONFIG register low.

### 1.3. Standby Modes

By setting the PWR\_UP bit in the CONFIG register to 1, the device enters standby-I mode. Standby-I mode is used to minimize average current consumption while maintaining short start up times. In this mode part of the crystal oscillator is active. This is the mode the nRF24L01 returns to from TX or RX mode when CE is set low.

In standby-II mode extra clock buffers are active compared to standby-I mode and much more current is used compared to standby-I mode. Standby-II occurs when CE is held high on a PTX device with empty TX FIFO. If a new packet is uploaded to the TX FIFO, the PLL starts and the packet is transmitted.

The register values are maintained during standby modes and the SPI may be activated. For start up

---

time see Table 13. on page 22.

#### 1.4. RX mode

The RX mode is an active mode where the nRF24L01 radio is a receiver. To enter this mode, the nRF24L01 must have the PWR\_UP bit set high, PRIM\_RX bit set high and the CE pin set high.

In this mode the receiver demodulates the signals from the RF channel, constantly presenting the demodulated data to the baseband protocol engine. The baseband protocol engine constantly searches for a valid packet. If a valid packet is found (by a matching address and a valid CRC) the payload of the packet is presented in a vacant slot in the RX FIFO. If the RX FIFO is full, the received packet is discarded.

The nRF24L01 remains in RX mode until the MCU configures it to standby-I mode or power down mode. If the automatic protocol features (Enhanced ShockBurst™) in the baseband protocol engine are enabled, the nRF24L01 can enter other modes in order to execute the protocol.

In RX mode a carrier detect signal is available. The carrier detect is a signal that is set high when a RF signal is detected inside the receiving frequency channel. The signal must be FSK modulated for a secure detection. Other signals can also be detected. The Carrier Detect (CD) is set high when an RF signal is detected in RX mode, otherwise CD is low. The internal CD signal is filtered before presented to CD register. The RF signal must be present for at least 128  $\mu$ s before the CD is set high. How to use the CD is described in Appendix E on page 74.

#### 1.5. TX mode

The TX mode is an active mode where the nRF24L01 transmits a packet. To enter this mode, the nRF24L01 must have the PWR\_UP bit set high, PRIM\_RX bit set low, a payload in the TX FIFO and, a high pulse on the CE for more than 10  $\mu$ s.

The nRF24L01 stays in TX mode until it finishes transmitting a current packet. If CE = 0 nRF24L01 returns to standby-I mode. If CE = 1, the next action is determined by the status of the TX FIFO. If the TX FIFO is not empty the nRF24L01 remains in TX mode, transmitting the next packet. If the TX FIFO is empty the nRF24L01 goes into standby-II mode. The nRF24L01 transmitter PLL operates in open loop when in TX mode. It is important to never keep the nRF24L01 in TX mode for more than 4ms at a time. If the auto retransmit is enabled, the nRF24L01 is never in TX mode long enough to disobey this rule.

## 1.6. Operational modes configuration

The following table (Table 12.) describes how to configure the operational modes.

| Mode       | PWR_UP register | PRIM_RX register | CE                      | FIFO state                                                       |

|------------|-----------------|------------------|-------------------------|------------------------------------------------------------------|

| RX mode    | 1               | 1                | 1                       | -                                                                |

| TX mode    | 1               | 0                | 1                       | Data in TX FIFO. Will empty all levels in TX FIFO <sup>a</sup> . |

| TX mode    | 1               | 0                | minimum 10µs high pulse | Data in TX FIFO. Will empty one level in TX FIFO <sup>b</sup> .  |

| Standby-II | 1               | 0                | 1                       | TX FIFO empty                                                    |

| Standby-I  | 1               | -                | 0                       | No ongoing packet transmission                                   |

| Power Down | 0               | -                | -                       | -                                                                |

- a. In this operating mode if the **CE** is held high the TX FIFO is emptied and all necessary ACK and possible retransmits are carried out. The transmission continues as long as the TX FIFO is refilled. If the TX FIFO is empty when the **CE** is still high, nRF24L01 enters standby-II mode. In this mode the transmission of a packet is started as soon as the **CSN** is set high after a upload (UL) of a packet to TX FIFO.

- b. This operating mode pulses the **CE** high for at least 10µs. This allows one packet to be transmitted. This is the normal operating mode. After the packet is transmitted, the nRF24L01 enters standby-I mode.

Table 12. nRF24L01 main modes

## 1.7. Timing Information

The timing information in this section is related to the transitions between modes and the timing for the **CE** pin. The transition from TX mode to RX mode or vice versa is the same as the transition from standby-I to TX mode or RX mode, Tstby2a.

| Name      | nRF24L01                                         | Max.  | Min. | Comments                    |

|-----------|--------------------------------------------------|-------|------|-----------------------------|

| Tpd2stby  | Power Down → Standby mode                        | 1.5ms |      | Internal crystal oscillator |

| Tpd2stby  | Power Down → Standby mode                        | 150µs |      | With external clock         |

| Tstby2a   | Standby modes → TX/RX mode                       | 130µs |      |                             |

| Thce      | Minimum <b>CE</b> high                           |       | 10µs |                             |

| Tpece2csn | Delay from <b>CE</b> pos. edge to <b>CSN</b> low |       | 4µs  |                             |

Table 13. Operational timing of nRF24L01

When nRF24L01 is in power down mode it must settle for 1.5ms before it can enter the TX or RX modes. If an *external clock* is used this delay is reduced to 150µs, see [Table 13. on page 22](#). The settling time must be controlled by the MCU.

**Note:** The register value is lost if **VDD** is turned off. In this case, nRF24L01 must be configured before entering the TX or RX modes.

## 2. Air data rate

The air data rate is the modulated signaling rate the nRF24L01 uses when transmitting and receiving data.

The air data rate can be 1Mbps or 2Mbps. The 1Mbps data rate gives 3dB better receiver sensitivity

---

compared to 2Mbps. High air data rate means lower average current consumption and reduced probability of on-air collisions.

The air data rate is set by the RF\_DR bit in the RF\_SETUP register.

A transmitter and a receiver must be programmed with the same air data rate to be able to communicate with each other.

For compatibility with nRF2401A, nRF24E1, nRF2402 and nRF24E2 the air data rate must be set to 1Mbps.

### 3. RF channel frequency

The RF channel frequency determines the center of the channel used by the nRF24L01. The channel occupies a bandwidth of 1MHz at 1Mbps and 2MHz at 2Mbps. nRF24L01 can operate on frequencies from 2.400GHz to 2.525GHz. The resolution of the RF channel frequency setting is 1MHz.

At 2Mbps the channel occupies a bandwidth wider than the resolution of the RF channel frequency setting. To ensure non-overlapping channels in 2Mbps mode, the channel spacing must be 2MHz or more. At 1Mbps the channel bandwidth is the same as the resolution of the RF frequency setting.

The RF channel frequency is set by the RF\_CH register according to the following formula:

$$F_0 = 2400 + RF\_CH \text{ [MHz]}$$

A transmitter and a receiver must be programmed with the same RF channel frequency to be able to communicate with each other.

### 4. PA control

The PA control is used to set the output power from the nRF24L01 power amplifier (PA). In TX mode PA control has four programmable steps, see Table 14.

The PA control is set by the RF\_PWR bits in the RF\_SETUP register.

| SPI RF-SETUP (RF_PWR) | RF output power | DC current consumption |

|-----------------------|-----------------|------------------------|

| 11                    | 0dBm            | 11.3mA                 |

| 10                    | -6dBm           | 9.0mA                  |

| 01                    | -12dBm          | 7.5mA                  |

| 00                    | -18dBm          | 7.0mA                  |

Conditions: VDD = 3.0V, VSS = 0V, TA = 27°C, Load impedance = 15Ω+j88Ω.

Table 14. RF output power setting for the nRF24L01

---

## 5. LNA gain

The gain in the Low Noise Amplifier (LNA) in the nRF24L01 receiver is controlled by the LNA gain setting. The LNA gain makes it possible to reduce the current consumption in RX mode with 0.8mA at the cost of 1.5dB reduction in receiver sensitivity.

The LNA gain has two steps and is set by the LNA\_HCURR bit in the RF\_SETUP register.

## 6. RX/TX control

The RX/TX control is set by PRIM\_RX bit in the CONFIG register and sets the nRF24L01 in transmit/receive.