# CYW20829B0-P4TAI100, CYW20829B0-P4EPI100, CYW20829B0S-P4TAI100, CYW20829B0S-P4EPI100

# **AIROC™ Bluetooth® LE module**

# **General description**

The CYW20829B0-P4xxI100 is a fully integrated Bluetooth® LE wireless module. The CYW20829B0-P4xxI100 includes an onboard crystal oscillator, passive components, flash memory, and the CYW20829 silicon device. Refer to the CYW20829 datasheet for additional details on the capabilities of the silicon device used in this module.

The CYW20829B0-P4xxI100 supports high-performance analog-to-digital conversion audio input, I $^2$ S/PCM, CAN, LIN for automotive use cases and other standard communication and timing peripherals. The CYW20829B0-P4xxI100 includes a royalty-free Bluetooth $^8$  stack compatible with Bluetooth $^8$  5.4 core spec in a 14.5 × 19 × 1.95 mm package.

The CYW20829B0-P4xxI100 includes 1 MB of onboard serial flash memory and is designed for standalone operation. The CYW20829B0-P4xxI100 uses an integrated power amplifier to achieve Class I or Class II output power capability.

The CYW20829B0-P4xxI100 is fully qualified by Bluetooth® SIG and is targeted at applications requiring cost-optimized Bluetooth® wireless connectivity.

The CYW20829B0-P4xxI100 is offered in two certified versions CYW20829B0-P4TAI100, and CYW20829B0-P4EPI100. The CYW20829B0-P4TAI100 includes an integrated trace antenna. The CYW20829B0-P4EPI100 supports an external antenna through a RF solder pad output.

# Module description

- Module size: 14.5 × 19 × 1.95 mm

- Bluetooth® 5.4 core spec qualified module

- QDID: TBD

- Declaration ID: TBD

- Certified to FCC, ISED, MIC, and CE regulations

- · Castelated solder pad connections for ease-of-use

- 1-MB on-module serial flash memory

- Up to 26 GPIOs

- Temperature range: -30°C to +85°C

- 96-MHz Arm® Cortex®-M33 CPU with single-cycle multiply and memory protection unit (MPU)

- Maximum TX output power

- Programmable TX power: up to 11 dBm

- Bluetooth® LE connection range of up to 500 meters at 10 dBm<sup>[1]</sup>

- RX sensitivity:

- LE-1 Mbps: -98 dBm

- LE-2 Mbps: -95 dBm

- Coded PHY 500 kbps (LE-LR): -101 dBm

- Coded PHY 125 kbps (LE-LR): -106 dBm

#### Note

1. Connection range tested module-to-module in full line-of-sight environment, free of obstacles or interference sources with output power of +10.0 dBm. Actual range will vary based on end product design, environment, receive sensitivity, and transmit output power of the central device.

infineon

Power consumption

# **Power consumption**

- Bluetooth® LE current consumption

- RX current: 5.6 mA @ LE 1 Mbps

- TX current: 5.2 mA @ 0 dBm

- Deep Sleep mode current with 64 KB SRAM retention:  $4.5~\mu A$

- HIDOFF (Deep Sleep): 0.5 μA

# **Functional capabilities**

- · Flexible clocking options

- 8-MHz internal main oscillator (IMO) with ±2% accuracy

- Ultra-low-power 32-kHz internal low-speed oscillator (ILO)

- Two oscillators: High-frequency (24-MHz) for radio PLL and low-frequency (32-kHz watch crystal) for LPO

- 48-MHz low power IHO (internal oscillator)

- Frequency-locked loop (FLL) for multiplying IMO frequency

- Integer and fractional peripheral clock dividers

- Quad SPI (QSPI)/serial memory interface (SMIF)

- eXecute-In-Place (XIP) from external quad SPI flash

- On-the-fly encryption and decryption

- Support for DDR

- Supports single, dual, and quad interfaces with throughput up to 384-Mbps

- Serial Communication

- Three run-time configurable Serial Communication Blocks (SCBs)

- First SCB: Configurable as SPI or I<sup>2</sup>C

- Second SCB: Configurable as SPI or UART

- Third SCB: Configurable as I<sup>2</sup>C or UART

- Audio subsystem

- Two pulse density modulation (PDM) channels and one I2 S channel with time division multiplexed (TDM) mode

- Timing and pulse-width modulation

- Seven 16-bit and two 32-bit Timer/Counter Pulse-Width Modulator (TCPWM) blocks, for MCU. Multiple PWMs needed for color LEDs.

- PWM supports center-aligned, edge, and pseudo-random modes

- ADC and MIC

- Sigma-delta switched cap ADC for audio and DC measurements

- Up to 32 programmable GPIOs

- One I/O port (8 I/Os) enables Boolean operations on GPIO pins; available during system Deep Sleep

- Programmable drive modes, strengths, and slew rates

- Two overvoltage-tolerant (OVT) pins

- Up to six, used for SMIF

#### **Benefits**

- Security built into platform architecture

- ROM-based root of trust via uninterruptible "Secure Boot"

- Step-wise authentication of execution images

- Secure execution of code in execute-only mode for protected routines

- All debug and test ingress paths can be disabled

- Up to four protection contexts (One available for customer code)

- Secure debug support via authenticated debug token

- Encrypted image support for external SMIF memory

- · Cryptography hardware

- Hardware Acceleration for symmetric cryptographic methods and hash functions

- True Random Number Generation (TRNG) function

#### **Benefits**

CYW20829B0-P4xxI100 provides all necessary components required to operate Bluetooth® LE communication standards.

- Proven ready-to-use hardware design

- Cost optimized for applications without space constraints

- · Nonvolatile memory for self-sufficient operation and over-the-air updates

- Bluetooth® SIG listed with QDID and declaration ID

- Fully certified module eliminates the time needed for design, development, and certification processes

- ModusToolbox<sup>™</sup> provides an easy-to-use integrated design environment (IDE) to configure, develop, and program a Bluetooth<sup>®</sup> application

### More information

Infineon provides a wealth of data at **www.infineon.com** to help you to select the right module for your design, and to help you to quickly and effectively integrate the module into your design.

#### References

More information

- Overview: AIROC™ Bluetooth® LE & Bluetooth® portfolio, Module portfolio

- CYW20829 Bluetooth® silicon datasheet

- Development kits:

- CYW920829B0M2P4TAI100-EVK, CYW20829B0-P4TAI100 evaluation board

- CYW920829B0M2P4EPI100-EVK, CYW20829B0-P4EPI100 evaluation board

- Test and debug tools:

- CYSmart, Bluetooth® LE test and debug tool (Windows)

- CYSmart Mobile, Bluetooth® LE test and debug tool (Android/iOS Mobile App)

- Knowledge base article

- KBA97095 EZ-Bluetooth® LE module placement

- KBA213976 FAQ for Bluetooth® LE and regulatory certifications with EZ-BLE modules

- KBA210802 Queries on Bluetooth® LE qualification and declaration processes

- KBA218122 3D Model Files for EZ-BLE/EZ-BT modules

# **Development environments**

ModusToolbox™ software is a modern, extensible development environment supporting a wide range of Infineon microcontroller devices. It provides a flexible set of tools and a diverse, high-quality collection of application-focused software. These include configuration tools, low-level drivers, libraries, and operating system support, most of which are compatible with Linux®, macOS®, and Windows®-hosted environments. ModusToolbox™ software does not include proprietary tools or custom build environments. This means you choose your compiler, your IDE, your RTOS, and your ecosystem without compromising usability or access to our industry leading CAPSENSE™, AIROC™, Bluetooth®, Wi-Fi, security, and low-power features.

# Technical support

- Infineon community: Whether you are a customer, partner, or a developer interested in the latest innovations, the developer community offers you a place to learn, share, and engage with both Infineon experts and other embedded engineers around the world.

- Visit our **support** page and contact a **local sales representatives**. If you are in the United States, you can talk to our technical support team by calling our toll-free number: +1-800-541-4736. Select option 2 at the prompt.

Table of contents

# Table of contents

| General description                                                        |    |

|----------------------------------------------------------------------------|----|

| Module description                                                         |    |

| Power consumption                                                          |    |

| Functional capabilities                                                    |    |

| Benefits                                                                   |    |

| More information                                                           |    |

| References                                                                 |    |

| Development environments                                                   |    |

| Technical support                                                          | 4  |

| Table of contents                                                          | 5  |

| 1 Overview                                                                 | 7  |

| 1.1 Functional block diagram                                               |    |

| 1.2 Module description                                                     |    |

| 1.2.1 Module dimensions and drawing                                        |    |

| 2 Pad connection interface                                                 |    |

| 3 Recommended host PCB layout                                              |    |

| 4 Module connections                                                       |    |

| 5 Connections and optional external components                             |    |

| 5.1 Power connections (VBAT)                                               |    |

| 5.1.1 Considerations and optional components for Brown Out (BO) conditions |    |

| 5.2 External reset (XRES)                                                  |    |

| 5.3 Critical components list                                               |    |

| 5.4 Antenna design                                                         |    |

| 6 Functional description                                                   |    |

| 6.1 CPU and memory subsystem                                               |    |

| 6.1.1 CPU                                                                  |    |

| 6.1.2 Interrupts                                                           |    |

| 6.1.3 Datawire                                                             |    |

| 6.1.4 Cryptography accelerator (Cryptolite)                                |    |

| 6.1.6 AES-128                                                              |    |

| 6.1.7 Vector unit (VU)                                                     |    |

| 6.1.8 Controller area network flexible data-rate (CAN FD)                  |    |

| 6.1.9 Local interconnect network (LIN)                                     |    |

| 6.1.10 Real time clock (RTC)                                               |    |

| 6.1.11 Memory                                                              |    |

| 6.1.12 Boot code                                                           |    |

| 6.1.13 Memory map                                                          |    |

| 7 System resources                                                         |    |

| 7.1 Power system                                                           |    |

| 7.1.1 Power modes                                                          |    |

| 7.1.2 CYW20829 clock system                                                |    |

| 7.1.3 Internal main oscillator (IMO)                                       |    |

| 7.1.4 Internal low-speed oscillator (ILO)                                  |    |

| 7.1.5 External crystal oscillators (ECO)                                   |    |

| 7.1.6 Watchdog timers (WDT, MCWDT)                                         |    |

| 7.1.7 Clock dividers                                                       |    |

| 7.1.8 Trigger routing                                                      | 26 |

| 7.1.9 Reset                                                                |    |

| 7.2 Bluetooth® LE radio and subsystem                                      |    |

| 7.3 Programmable analog-to-digital converter (ADC)                         | 28 |

5

### Table of contents

| 7.3.1 Sigma delta ADC                                   | 28 |

|---------------------------------------------------------|----|

| 7.4 Programmable digital                                | 28 |

| 7.5 Fixed-function digital                              | 29 |

| 7.5.1 Timer/counter/pulse-width modulator (TCPWM) block | 29 |

| 7.5.2 Serial communication blocks (SCB)                 |    |

| 7.5.3 QSPI interface serial memory interface (SMIF)     | 30 |

| 7.6 GPIO                                                | 31 |

| 7.7 Special-function peripherals                        | 32 |

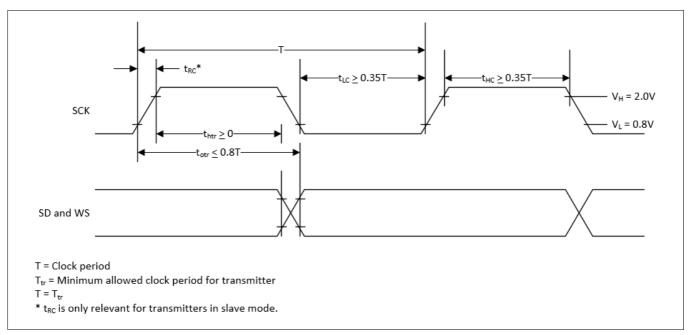

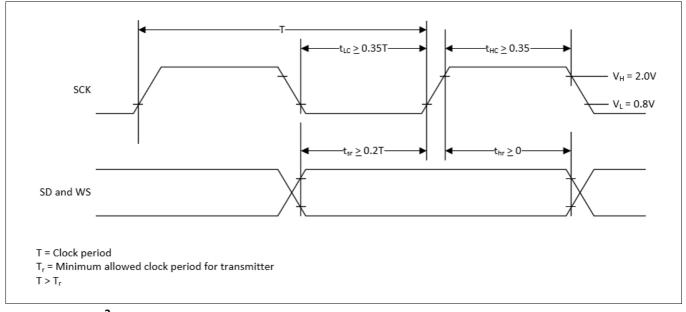

| 7.7.1 Audio subsystem                                   | 32 |

| 8 Pinouts                                               | 33 |

| 9 Power management unit                                 | 38 |

| 9.1 RF power management                                 |    |

| 9.2 Host controller power management                    |    |

| 9.3 BBC power management                                |    |

| 10 Electrical characteristics                           |    |

| 11 Chipset RF specifications                            |    |

| 12 Timing and AC characteristics                        |    |

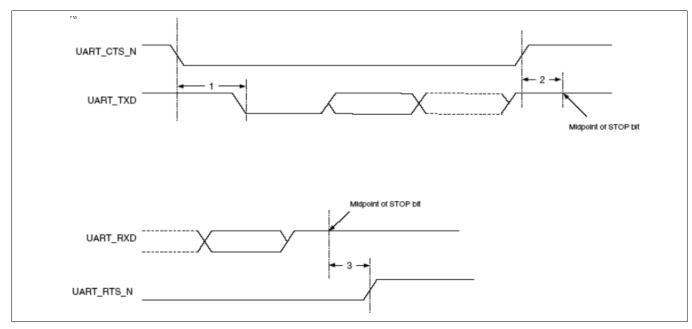

| 12.1 UART timing                                        |    |

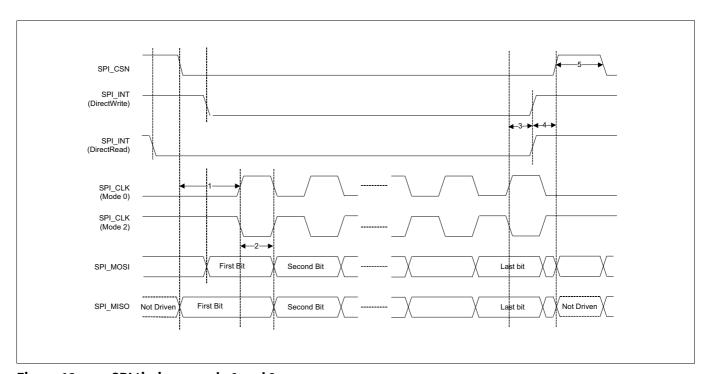

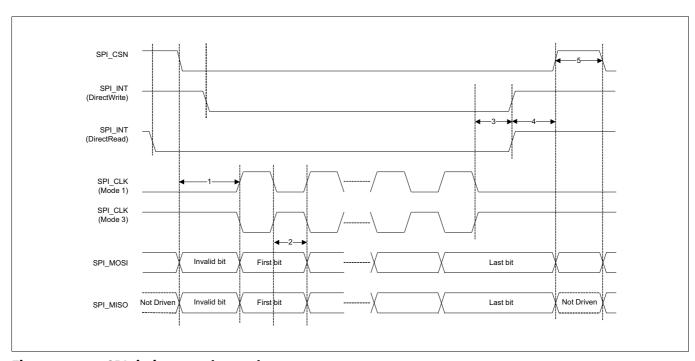

| 12.2 SPI timing                                         |    |

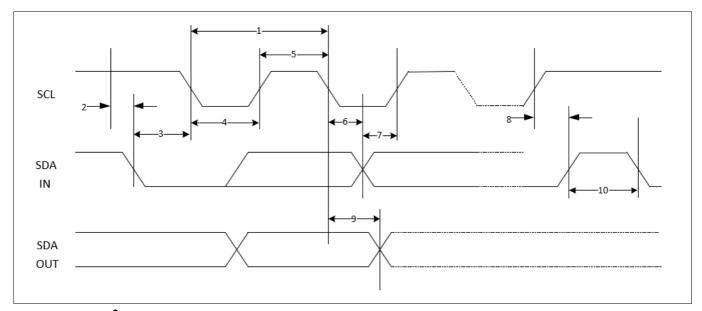

| 12.3 I2C interface timing                               |    |

| 13 Environmental specifications                         |    |

| 13.1 Environmental compliance                           |    |

| 13.2 RF certification                                   |    |

| 13.3 Safety certification                               |    |

| 13.4 Environmental conditions                           |    |

| 13.5 ESD and EMI protection                             |    |

| 14 Regulatory information                               |    |

| 14.1 FCC                                                |    |

| 14.2 ISED                                               |    |

| 14.3 European declaration of conformity                 |    |

| 14.4 MIC Japan                                          |    |

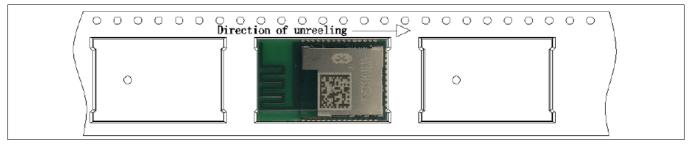

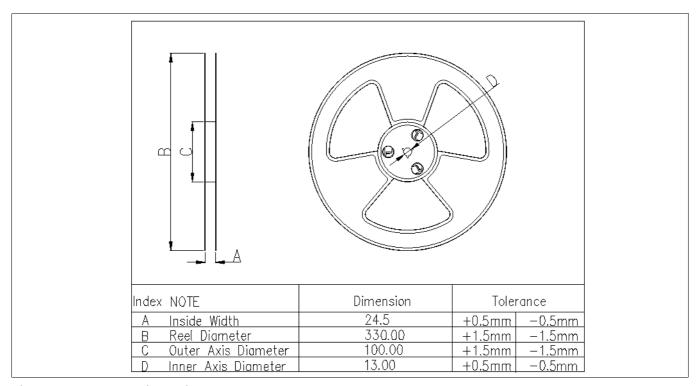

| 15 Packaging                                            |    |

| 16 Ordering information                                 |    |

| 17 Acronyms                                             |    |

| 18 Document conventions                                 |    |

| 18.1 Units of measure                                   | 60 |

| νωνικική πικτ <b>λγ</b> ν                               |    |

2023-12-20

Overview

# 1 Overview

# 1.1 Functional block diagram

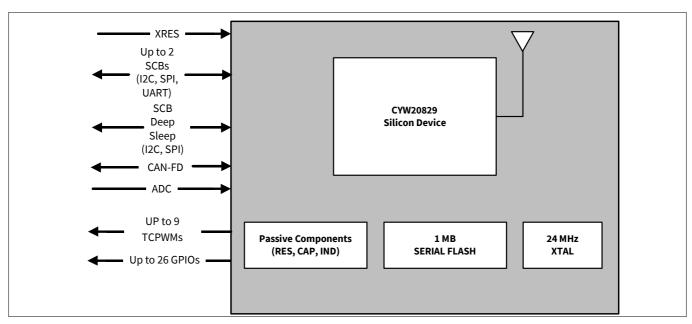

Figure 1 illustrates the CYW20829B0-P4xxI100 functional block diagram.

Figure 1 Functional block diagram (GPIOs)

# 1.2 Module description

The CYW20829B0-P4xxI100 module is a complete module designed to be soldered to the application's main board.

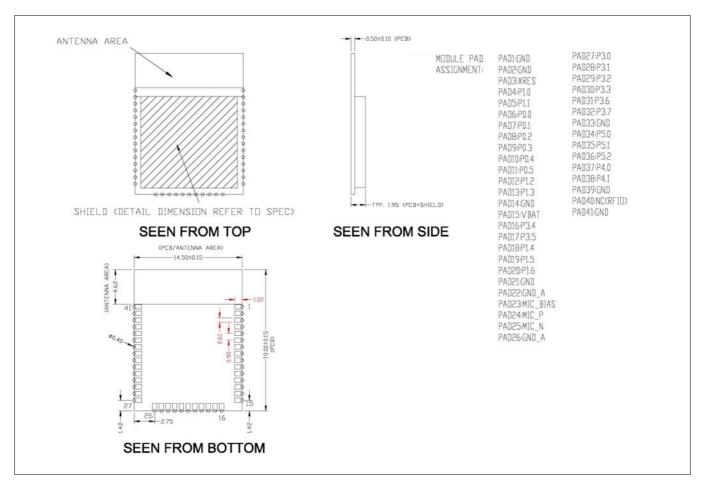

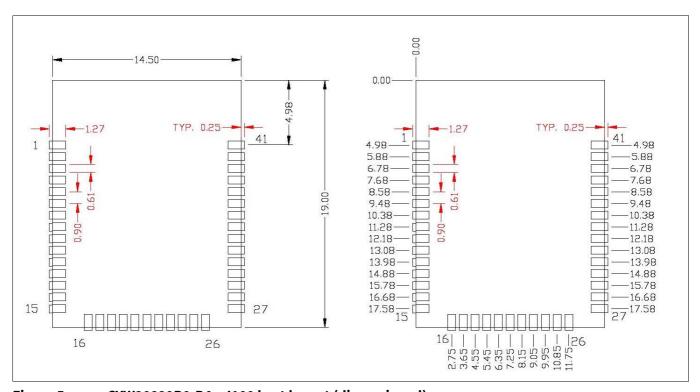

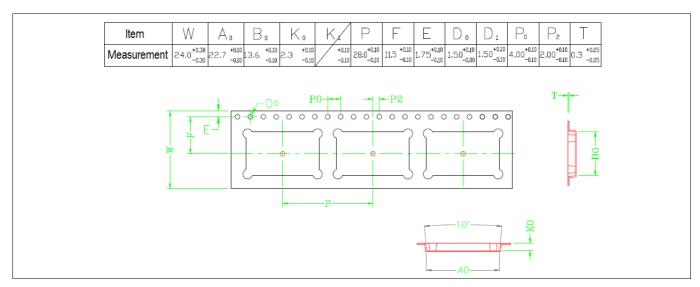

# 1.2.1 Module dimensions and drawing

Infineon reserves the right to select components from various vendors to achieve the Bluetooth® module functionality. Such selections will still guarantee that all mechanical specifications and module certifications are maintained. Designs should be held within the physical dimensions shown in the mechanical drawings in Figure 2. All dimensions are in millimeters (mm).

Table 1 Module design dimensions

| Dimension item                                                 | Specification |                 |

|----------------------------------------------------------------|---------------|-----------------|

| Module dimensions                                              | Length (X)    | 14.5 ± 0.15 mm  |

| Module differisions                                            | Width (Y)     | 19 ± 0.15 mm    |

| Antenna connection location dimensions                         | Length (X)    | 14.5 mm         |

| Antenna connection location dimensions                         | Width (Y)     | 4.62 mm         |

| PCB thickness                                                  | Height (H)    | 0.50 ± 0.05 mm  |

| Shield height                                                  | Height (H)    | 1.45-mm typical |

| Maximum component height                                       | Height (H)    | 1.45-mm typical |

| Total module thickness (bottom of module to highest component) | Height (H)    | 1.95-mm typical |

Overview

See **Figure 2** for the mechanical reference drawing for CYW20829B0-P4xxI100.

Figure 2 Module mechanical drawing

#### **Notes**

- 2. No metal should be located beneath or above the antenna area. Only bare PCB material should be located beneath the antenna area. For more information on recommended host PCB layout, see "Recommended host PCB layout" on page 11.

- 3. The CYW20829B0-P4TAI100, CYW20829B0-P4EPI100 includes castellated pad connections, denoted as the circular openings at the pad location above.

Pad connection interface

# 2 Pad connection interface

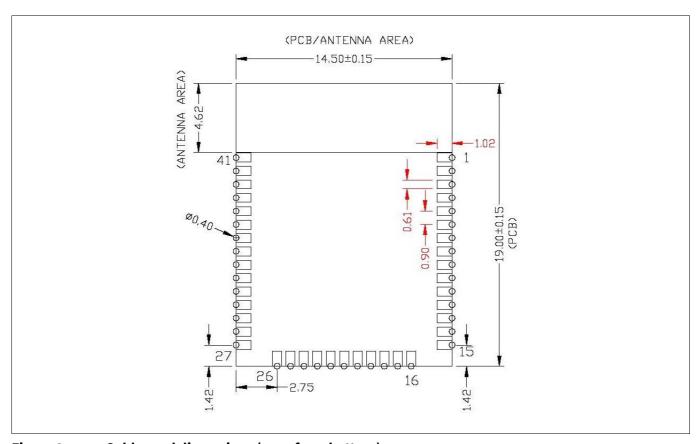

As shown in the bottom view of **Figure 2**, the CYW20829B0-P4xxI100 connects to the host board via solder pads on the backside of the module. **Table 2** and **Figure 3** detail the solder pad length, width, and pitch dimensions of the CYW20829B0-P4xxI100 module.

Table 2 Connection description

| Part number         | Name | Connections | Connection type | Pad length dimension | Pad width dimension | Pad pitch |

|---------------------|------|-------------|-----------------|----------------------|---------------------|-----------|

| CYW20829B0-P4TAI100 | SP   | 41          | Solder pads     | 1.02 mm              | 0.61 mm             | 0.90 mm   |

| CYW20829B0-P4EPI100 | SP   | 41          | Solder pads     | 1.02 mm              | 0.61 mm             | 0.90 mm   |

Figure 3 Solder pad dimensions (seen from bottom)

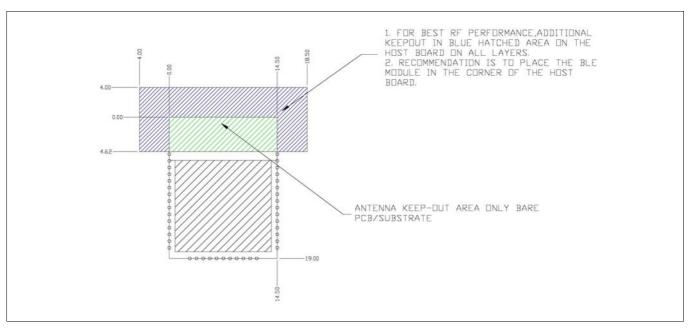

To maximize RF performance, the host layout should follow these recommendations:

- 1. Antenna Area Keepout: The host board directly below the antenna area of the module (see **Figure 2**) must not contain ground or signal traces. This keepout area requirement applies to all layers of the host board.

- 2. Module Placement: The ideal placement of the Bluetooth® module is in a corner of the host board with the PCB trace antenna located at the far corner. This placement minimizes the additional recommended keepout area stated in item 2. Refer to AN96841 for module placement best practices.

Pad connection interface

Figure 4 Recommended host PCB keepout area around the CYW20829B0-P4xxI100 antenna

Recommended host PCB layout

# 3 Recommended host PCB layout

**Figure 5** provides details that can be used for the recommended host PCB layout pattern for the CYW20829B0-P4xxI100. Dimensions are in millimeters unless otherwise noted. Pad length of 1.27 mm (0.64 mm from center of the pad on either side) shown in **Figure 4** is the minimum recommended host pad length. The host PCB layout pattern can be completed using either **Figure 5**. It is not necessary to use all figures to complete the host PCB layout pattern.

Figure 5 CYW20829B0-P4xxI100 host layout (dimensioned)

Module connections

# 4 Module connections

**Table 3** details the solder pad connection definitions and available functions for the pad connections for the CYW20829B0-P4xxI100 module. **Table 3** lists the solder pads on the CYW20829B0-P4xxI100 module, the silicon device pin, and denotes what functions are available for each solder pad.

Table 3 Pin assignments

| Module pad name | Pin<br>number                  | Silicon pin name | Pin<br>number | I/O | Power domain | Description                                          |

|-----------------|--------------------------------|------------------|---------------|-----|--------------|------------------------------------------------------|

| Microphone      |                                | Microphone       |               |     |              |                                                      |

| MIC_P           | 24                             | MIC_P            | 54            |     |              | Microphone positive input                            |

| MIC_N           | 25                             | MIC_N            | 55            | I   | VDDA         | Microphone negative input                            |

| MIC_BIAS        | 23                             | MIC_BIAS         | 53            | 0   |              | Microphone bias supply                               |

| GND_A           | 22, 26                         |                  |               |     |              | Analog ground for microphone                         |

| Power supply    |                                |                  |               |     |              |                                                      |

| VBAT            | 15                             | 2.75 V~3.6 V     |               |     |              |                                                      |

| Ground pins     |                                |                  |               |     |              |                                                      |

| GND             | 1, 2, 14,<br>21, 33,<br>39, 41 |                  |               |     |              |                                                      |

| Radio I/O       |                                |                  |               |     |              |                                                      |

| RFIO            | 40                             |                  |               | I/O |              | External antenna port (only for CYW20829B0-P4EPI100) |

|                 |                                |                  |               |     |              |                                                      |

Module connections

Table 4 GPIO pin descriptions

| Module<br>pad name | Pad<br>number | Silicon<br>pin name | Silicon<br>pin<br>number | Direction<br>Default | POR state | Power<br>domain | Description                                  |

|--------------------|---------------|---------------------|--------------------------|----------------------|-----------|-----------------|----------------------------------------------|

| P0.0               | 6             | P0.0                | 32                       | I/O                  | Floating  | VDDO            |                                              |

| P0.1               | 7             | P0.1                | 33                       | I/O                  | Floating  | VDDO            | -                                            |

| P0.2               | 8             | P0.2                | 34                       | I/O                  | Floating  | VDDO            |                                              |

| P0.3               | 9             | P0.3                | 35                       | I/O                  | Floating  | VDDO            |                                              |

| P0.4               | 10            | P0.4                | 36                       | I/O                  | Floating  | VDDO            |                                              |

| P0.5               | 11            | P0.5                | 37                       | I/O                  | Floating  | VDDO            |                                              |

| P1.0               | 4             | P1.0                | 38                       | I/O                  | Floating  | VDDO            |                                              |

| P1.1               | 5             | P1.1                | 39                       | I/O                  | Floating  | VDDO            |                                              |

| P1.2               | 12            | P1.2                | 40                       | I/O                  | Floating  | VDDO            |                                              |

| P1.3               | 13            | P1.3                | 41                       | I/O                  | Floating  | VDDO            |                                              |

| P1.4               | 18            | P1.4                | 43                       | I/O                  | Floating  | VDDO            |                                              |

| P1.5               | 19            | P1.5                | 44                       | I/O                  | Floating  | VDDO            |                                              |

| P1.6               | 20            | P1.6                | 45                       | I/O                  | Floating  | VDDO            |                                              |

| P3.0               | 27            | P3.0                | 1                        | I/O                  | Floating  | VDDO            | General input and output                     |

| P3.1               | 28            | P3.1                | 2                        | I/O                  | Floating  | VDDO            | port.                                        |

| P3.2               | 29            | P3.2                | 3                        | I/O                  | Floating  | VDDO            | See <b>Table 13</b> for alternate functions. |

| P3.3               | 30            | P3.3                | 4                        | I/O                  | Floating  | VDDO            |                                              |

| P3.4               | 16            | P3.4                | 5                        | I/O                  | Floating  | VDDO            |                                              |

| P3.5               | 17            | P3.5                | 6                        | I/O                  | Floating  | VDDO            |                                              |

| P3.6               | 31            | P3.6                | 8                        | I/O                  | Floating  | VDDO            |                                              |

| P3.7               | 32            | P3.7                | 9                        | I/O                  | Floating  | VDDO            |                                              |

| P4.0               | 37            | P4.0                | 13                       | I/O                  | Floating  | VDDO            |                                              |

| P4.1               | 38            | P4.1                | 14                       | I/O                  | Floating  | VDDO            |                                              |

| P5.0/<br>WCO_OUT   | 34            | P5.0/<br>WCO_OUT    | 10                       | I/O                  | Floating  | VDDO            |                                              |

| WCO_OUT            | 1             | WCO_OUT             |                          |                      |           |                 |                                              |

| P5.1/<br>WCO_IN    | 35            | P5.1/<br>WCO_IN     | 11                       | I/O                  | Floating  | VDDO            |                                              |

| P5.2               | 36            | P5.2                | 12                       |                      | Floating  | VDDO            |                                              |

| XRES               | 3             | XRES                | 23                       | I                    | Floating  | VDDO            |                                              |

#### Notes

<sup>4.</sup> The CYW20829B0-P4xxI100 contains a single SPI (SPI1) peripheral supporting both master or slave configurations. SPI2 is used for on-module serial memory interface.

<sup>5.</sup> In Master mode, any available GPIO can be configured as SPI1\_CS. This function is not explicitly shown in **Table 23**.

Connections and optional external components

# 5 Connections and optional external components

### **5.1** Power connections (VBAT)

The CYW20829B0-P4xxI100 contains one power supply connection, VBAT, which accepts a supply input range of 2.75 V to 3.6 V for CYW20829B0-P4xxI100. **Table 15** provides this specification. The maximum power supply ripple for this power connection is 100 mV, as shown in **Table 15**.

It is not required to place any power supply decoupling or noise reduction circuitry on the host PCB. If desired, an external ferrite bead between the supply and the module connection can be included, but is not necessary. If used, the ferrite bead should be positioned as close as possible to the module pin connection and the recommended ferrite bead value is 330  $\Omega$ , 100 MHz.

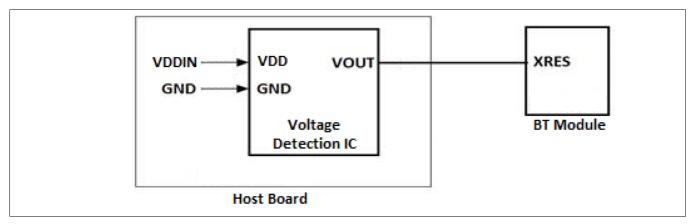

# 5.1.1 Considerations and optional components for Brown Out (BO) conditions

Power supply design must be completed to ensure that the CYW20829B0-P4xxI100 module does not encounter a Brown Out condition, which can lead to unexpected functionality, or module lock up. A Brown Out condition may be met if power supply provided to the module during power up or reset is in the following range:

$$V_{IL} \le VDDIN \le V_{IH}$$

Refer to **Table 16** for the  $V_{II}$  and  $V_{IH}$  specifications.

System design should ensure that the condition above is not encountered when power is removed from the system. In the event that this cannot be guaranteed (that is, battery installation, high-value power capacitors with slow discharge), it is recommended that an external voltage detection device be used to prevent the Brown Out voltage range from occurring during power removal. Refer to **Figure 6** for the recommended circuit design when using an external voltage detection IC.

Figure 6 Reference circuit block diagram for external voltage detection IC

In the event that the module does encounter a Brown Out condition, and is operating erratically or is not responsive, power cycling the module will correct this issue and once reset, the module should operate correctly. Brown Out conditions can potentially cause issues that cannot be corrected, but in general, a power-on-reset operation will correct a Brown Out condition.

Connections and optional external components

# 5.2 External reset (XRES)

The CYW20829B0-P4xxI100 has an integrated power-on reset circuit, which completely resets all circuits to a known power-on state. This action can also be evoked by an external reset signal, forcing it into a power-on reset state. The XRES signal is an active-low signal, which is an input to the CYW20829B0-P4xxI100 module (solder pad 3). The CYW20829B0-P4xxI100 module does not require an external pull-up resistor on the XRES input

During power-on operation, the XRES connection to the CYW20829B0-P4xxI100 is required to be held low 50 ms after the VBAT power supply input to the module is stable. This can be accomplished in the following ways:

- The host device should connect a GPIO to the XRES of the CYW20829B0-P4xxI100 module and pull XRES low until VBAT is stable. XRES is recommended to be released 50 ms after VBAT is stable.

- If the XRES connection of the CYW20829B0-P4xxl100 module is not used in the application, a 10-μF capacitor

may be connected to the XRES solder pad of the CYW20829B0-P4xxl100 to delay the XRES release. The capacitor

value for this recommended implementation is approximate, and the exact value may differ depending on the

VBAT power supply ramp time of the system. The capacitor value should result in an XRES release timing of

50 ms after VBAT stability.

- The XRES release timing may be controlled by an external voltage detection IC. XRES should be released 50 ms after VBAT is stable.

Connections and optional external components

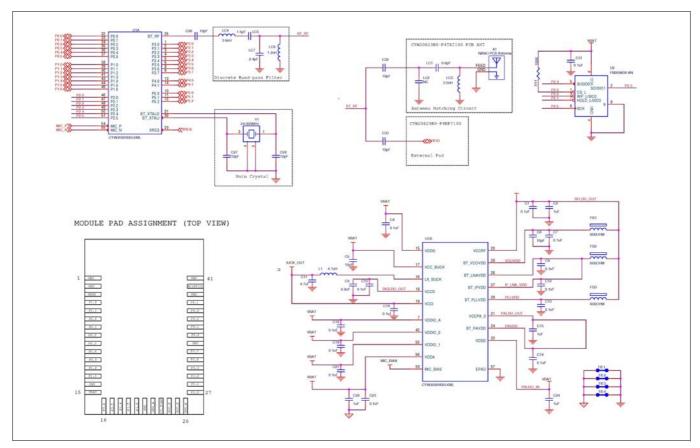

Figure 7 illustrates the CYW20829B0-P4xxI100 schematic.

Figure 7 CYW20829B0-P4xxI100 schematic diagram

Connections and optional external components

# 5.3 Critical components list

Table 5 details the critical components used in the CYW20829B0-P4xxI100 module.

Table 5 Critical component list

| Component | Reference designator | Description                                        |

|-----------|----------------------|----------------------------------------------------|

| Silicon   | U1                   | 56-pin QFN Bluetooth® LE silicon device - CYW20829 |

| Silicon   | U2                   | 8-pin TDF8N, 1 MB Serial Flash                     |

| Crystal   | Y1                   | 24 MHz, 8 pF                                       |

# 5.4 Antenna design

Table 6 details trace antenna used in the CYW20829B0-P4TAI100 module. For more information, see Table 6.

Table 6 Trace antenna specifications

| Item            | Description       |

|-----------------|-------------------|

| Frequency range | 2400 MHz-2500 MHz |

| Peak gain       | -0.5-dBi typical  |

| Return loss     | 10-dB minimum     |

**Table below** details the qualified dipole antenna used in the CYW20829B0-P4EPI100 module. Any antenna of equivalent or less gain can be used without additional application and testing for FCC regulations. For more information, see **Table below**.

Table Dipole antenna specifications

| Item            | Description       |

|-----------------|-------------------|

| Manufacture     | Pulse             |

| Part number     | W1010             |

| Frequency range | 2400 MHz-2500 MHz |

| Peak gain       | 2.0-dBi typical   |

**Functional description**

# 6 Functional description

The following sections provide an overview of the features, capabilities and operation of each functional block identified in the block diagram in **Figure 1**. For more detailed information, refer to the following documentation:

- Board Support Package (BSP) documentation

BSPs are available on GitHub. They are aligned with Infineon kits and provide files for basic device

functionality such as hardware configuration files, startup code, and linker files. The BSP also includes other

libraries that are required to support a kit. Each BSP has its own documentation, but typically includes an API

reference such as the example here. This search link finds all currently available BSPs on the Infineon GitHub

site.

- Hardware Abstraction Layer (HAL) API reference manual

The Infineon HAL provides a high-level interface to configure and use hardware blocks on Infineon MCUs. It is

a generic interface that can be used across multiple product families. You can leverage the HAL's simpler and

more generic interface for most of an application, even if one portion requires finer-grained control. The HAL

API Reference provides complete details. Example applications that use the HAL download it automatically

from the GitHub repository.

# 6.1 CPU and memory subsystem

AIROC™ CYW20829 has multiple bus masters, as **Figure 1** shows. They are: CPU, datawire, QSPI, and a Crypto block. Generally, all memory and peripherals can be accessed and shared by all bus masters through multi-layer Arm® AMBA high-performance bus (AHB) arbitration. An interprocessor communication block (IPC) provides communication between the CPU and the Bluetooth® LE sub-system.

infineon

**Functional description**

#### 6.1.1 CPU

The Cortex®-M33 has single-cycle multiply and a memory protection unit (MPU). It can run at up to 96 MHz in LP mode and 48 MHz in ULP mode. This is the main CPU, designed for a short interrupt response time, high code density, and high throughput.

Cortex®-M33 implements a version of the Thumb instruction set based on Thumb-2 technology (defined in the **Armv8-M architecture reference manual**).

The main MCU also implements device-level security, safety, and protection features. Cortex®-M33 provides a secure, interruptible boot function. This guarantees that post boot, system integrity is checked and memory and peripheral access privileges are enforced.

The CPU has the following power draw, at  $V_{DDD} = 3.0 \text{ V}$  and using the internal buck regulator.

Table 7 Active current slope at V<sub>DDD</sub> = 3.0 V using the internal buck regulator

| System power mode |           |           |  |  |

|-------------------|-----------|-----------|--|--|

| CPU               | ULP       | LP        |  |  |

| CFU               | 22 μA/MHz | 40 μA/MHz |  |  |

The CPU can be selectively placed in Sleep and Deep Sleep power modes as defined by Arm®. The CPU also implements a Deep Sleep RAM (DS-RAM) mode in which almost all the circuits except RAM are powered OFF. Data in RAM is retained to maintain state. Upon exit, the CPU goes through a reset but can use the data in RAM to skip software initialization.

The CPU also has nested vectored interrupt controllers (NVIC) for rapid and deterministic interrupt response, and wakeup interrupt controllers (WIC) for CPU wakeup from Deep Sleep power mode.

CYW20829 has a debug access port (DAP) that acts as the interface for device programming and debug. An external programmer or debugger (the "host") communicates with the DAP through the device serial wire debug (SWD) or Joint Test Action Group (JTAG) interface pins. Through the DAP (and subject to device security restrictions), the host can access the device memory and peripherals as well as the registers in the CPU.

CPU debug and trace features are as follows:

• Six hardware breakpoints and four watchpoints, serial wire viewer (SWV), and printf()-style debugging through the single wire output (SWO) pin.

#### 6.1.2 Interrupts

The CPU has interrupt request lines (IRQ), with the interrupt source 'n' directly connected to IRQn.

Each interrupt supports eight configurable priority levels. One system interrupt can be mapped to the CPU non-maskable interrupts (NMI). Multiple interrupt sources are capable of waking the device from Deep Sleep power mode using the WIC.

#### 6.1.3 Datawire

Datawire is a light weight DMA controller with 16 channels, which support CPU-independent accesses to memory and peripherals. The descriptors for the channels are in SRAM and the number of descriptors is limited only by the size of the memory. Each descriptor can transfer data in two nested loops with configurable address increments to the source and destination.

**Functional description**

# **6.1.4** Cryptography accelerator (Cryptolite)

A combination of HW and SW is able to support several cryptographic functions. Specifically it supports the following functions:

- Encryption/decryption

- AES-128 hardware accelerator with following supported modes:

- Electronic Code Book (ECB)

- Cipher Block Chaining (CBC)

- Cipher Feedback (CFB)

- Output Feedback (OFB)

- Counter (CTR)

- Hashing

- Secure Hash Algorithm (SHA-256) hardware accelerator

- Message Authentication Functions (MAC)

- Hashed Message Authentication Code (HMAC) acceleration using SHA-256 hardware

- True Random Number Generator (TRNG)

- Vector unit hardware accelerator

- Digital Signature Verification using RSA

- Digital Signature Verification using ECDSA

#### 6.1.5 Protection units

CYW20829 has multiple types of protection to control erroneous or unauthorized access to memory and peripheral registers.

Protection units support memory and peripheral access attributes including address range, read/write, code/data, privilege level, secure/non-secure, and protection context.

Protection units are configured at "Secure Boot" to control access privileges and rights for bus masters and peripherals. Up to eight protection contexts ("Secure Boot" is in protection context 0) allow access privileges for memory and system resources to be set by the "Secure Boot" process per protection context by bus master and code privilege level. Multiple protection contexts are available.

#### 6.1.6 AES-128

AES-128 component to accelerate block cipher functionality. This functionality supports forward encryption of a single 128 bit block with a 128 bit key. SHA-256 component to accelerate hash functionality. This component supports message schedule calculation for a 512-bit message chunk and processing of a 512-bit message chunk.

# 6.1.7 Vector unit (VU)

VU component to accelerate asymmetric key cryptography (for example, RSA and ECC). This component supports large integer multiplication, addition, and so on. TRNG component based on a set of ring oscillators. The TRNG includes a HW health monitor.

# 6.1.8 Controller area network flexible data-rate (CAN FD)

CYW20829 supports the CAN FD controller that supports one CAN FD channel. All CAN FD controllers are compliant with the ISO 11898-1:2015 standard; an ISO 16845:2015 certificate is available. It also implements the time-triggered CAN (TTCAN) protocol specified in ISO 11898-4 (TTCAN protocol levels 1 and 2) completely in hardware. All functions concerning the handling of messages are implemented by the RX and TX handlers. The RX handler manages message acceptance filtering, transfer of received messages from the CAN core to a message RAM, and provides receive-message status. The TX handler is responsible for the transfer of transmit messages from the message RAM to the CAN core, and provides transmit-message status.

**Functional description**

# 6.1.9 Local interconnect network (LIN)

CYW20829 contains a LIN channel. Each channel supports transmission/reception of data following the LIN protocol according to ISO standard 17987. Each LIN channel connects to an external transceiver through a 3-pin interface (including an enable function) and supports master and slave functionality. Each block also supports classic and enhanced checksum, along with break detection during message reception and wake-up signaling. Break detection, sync field, checksum calculations, and error interrupts are handled in hardware.

### 6.1.10 Real time clock (RTC)

- Year/Month/Date, Day-of-week, Hour:Minute:Second fields

- 12- and 24-hour formats

- · Automatic leap-year correction

#### **6.1.11** Memory

CYW20829 contains the SRAM, ROM, and eFuse memory blocks.

- SRAM: CYW20829 has 256-KB of SRAM. Power control and retention granularity is 64-KB blocks allowing the user to control the amount of memory retained in Deep Sleep. Memory is not retained in Hibernate mode.

- ROM: The 64-KB ROM, also referred to as the supervisory ROM (SROM), provides code (ROM Boot) for several system functions. The ROM contains, primarily device initialization and security. ROM code is executed, in protection context 0.

- eFuse: A one-time programmable (OTP) eFuse array consists of 1024 bits, which are reserved for system use such as Die ID, Device ID, initial trim settings, device life cycle, and security settings. Some of the bits are available for storing security key information and hash values and can be programmed by the user for device security.

Each fuse is individually programmed; once programmed (or "blown"), its state cannot be changed. Blowing a fuse transitions it from the default state of '0' to '1'. To program an eFuse, VDDIO1 must be at 2.5 V ± 5%.

Because blowing an eFuse is an irreversible process, programming is recommended only in mass production under controlled factory conditions by Infineon provided provisioning tools.

### **6.1.12** Boot code

On a device reset, the boot code in ROM is the first code to execute. This code performs the following:

- Device trim setting (calibration)

- Setting the device protection units

- Setting device access restrictions for secure life cycle states

- · Configures the Debug Access Port

- In secure life cycle supports secure debug via authenticated debug token

- Configures the SMIF for external flash access

- In secure life cycle validates first user code in external flash by checking its digital signature. Supports OTF decryption of encrypted images in external flash

- Copies the application bootstrap from the external flash to SRAM and jumps to the ROM. It cannot be changed and acts as the Root of Trust in a secure system.

It should also be noted that the ROM code sets the system clock to 48 MHz IHO source.

infineon

Functional description

# 6.1.13 Memory map

The 32-bit (4 GB) address space is divided into the regions shown in **Table 9**. Note that code can be executed from the Code, and Internal RAM or External flash.

Table 8 Address map

| Address range               | Name                   | Use                                                                                                                                 |

|-----------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000 0000 to 0x1FFF FFFF  | Code                   | Program code region. It includes the exception vector table, which starts at address 0.                                             |

| 0x2000 0000 to 0x3FFF FFFF  | SRAM                   | Data region                                                                                                                         |

| 0x4000 0000 to 0x5FFF FFFF  | Peripheral             | All peripheral registers. Code cannot be executed from this region. Bit-band in this region is not supported.                       |

| 0x6000 0000 to 0x8FFF FFFF  | External NVM           | SMIF/Quad SPI, (see the "QSPI interface serial memory interface (SMIF)" on page 30 section). Code can be executed from this region. |

| 0xA000 0000 to 0xDFFF FFFF  | External Device        | Not used                                                                                                                            |

| 0xE000 0000 to 0xE00F FFFF  | Private Peripheral Bus | Provides access to peripheral registers within the CPU core.                                                                        |

| 0xE010 0A000 to 0xFFFF FFFF | Device                 | Device-specific system registers                                                                                                    |

The device memory map is shown in **Table 9**.

Table 9 Internal memory address map

| Address range               | Memory type | Size         |

|-----------------------------|-------------|--------------|

| 0x0000 0000 to 0x0001 0000  | ROM         | 64 KB        |

| 0x2000 0000 to 0x 2004 0000 | SRAM        | Up to 256 KB |

System resources

#### 7 System resources

#### 7.1 **Power system**

The power system provides assurance that voltage levels are as required for each respective mode and will either delay mode entry (on power-on reset (POR), for example) until voltage levels are as required for proper function or generate resets (brown-out detect (BOD)) when the power supply drops below specified levels. The design guarantees safe chip operation between power supply voltage dropping below specified levels (for example, below 1.7 V) and the reset occurring. There are no voltage sequencing requirements.

The V<sub>DDD</sub> supply (1.7 V to 3.6 V) powers an on-chip buck regulator which offers a selectable (1.0 V or 1.16 V) core operating voltage (VCCD). The selection lets users choose between two system power modes:

- System Low Power (LP) operates VCCD at 1.1 V and offers high performance, with no restrictions on device configuration.

- System Ultra Low Power (ULP) operates VCCD at 1.0 V for exceptional low power, but imposes limitations on clock speeds.

The Bluetooth® radio requires 1.1 V for operation. Bluetooth® system may override user core voltage selection when the radio is turned on. System voltage will return to the user selected value automatically once Bluetooth® radio activity is completed. Refer to "Power management unit" on page 38 for more details.

#### 7.1.1 **Power modes**

CYW20829 can operate in four system and three CPU power modes. These modes are intended to minimize the average power consumption in an application. For more details on power modes and other power-saving configuration options, see the relevant application note.

Power modes supported by CYW20829, in the order of decreasing power consumption, are:

- System Low Power (LP) All peripherals and CPU power modes are available at maximum speed

- System Ultra Low Power (ULP) All peripherals and CPU power modes are available, but with limited speed

- CPU Active CPU is executing code in system LP or ULP mode

- CPU Sleep CPU code execution is halted in system LP or ULP mode

- CPU Deep Sleep CPU code execution is halted and system Deep Sleep is requested in system LP or ULP mode

- System Deep Sleep Only low-frequency peripherals are available after both CPUs enter CPU Deep Sleep mode

- System Hibernate Device and I/O states are frozen and the device resets on wakeup

- Deep Sleep RAM only RAM and IO states are retained. All system activity except for select low power peripherals ceases until system exits from this state. The CPU resets upon exit but can skip software initialization since RAM is retained.

CPU Active, Sleep, and Deep Sleep are standard Arm®-defined power modes supported by the Arm® CPU instruction set architecture (ISA). System LP, ULP, Deep Sleep, Deep Sleep RAM and Hibernate modes are additional low-power modes supported by the CYW20829.

System resources

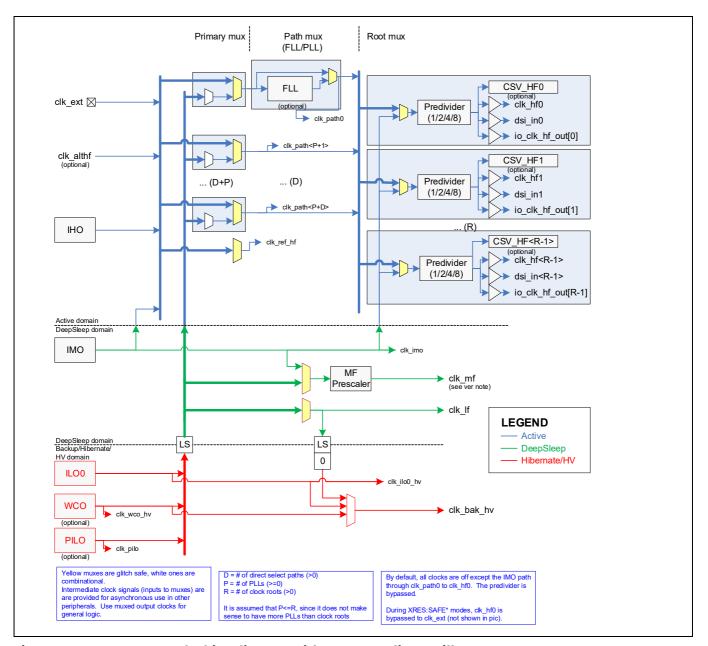

# 7.1.2 CYW20829 clock system

CYW20829 clock system consists of a combination of oscillators, external clock, and frequency-locked loop. Specifically, the following:

- Internal main oscillator (IMO)

- Internal low-speed oscillator (ILO)

- Watch crystal oscillator (WCO)

- System 24-MHz crystal oscillator

- External clock input

- One frequency-locked loop (FLL)

- Internal high-speed oscillator (IHO)

Clocks may be buffered and brought out to a pin on a smart I/O port.

**Table 10** shows the mapping of port and associated clock group mapped to peripherals.

Table 10 Mapping of clock groups to peripherals

| DCLK          | Doot slock             |             | Frequency         |                    |                                                                                                                                                |

|---------------|------------------------|-------------|-------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| PCLK<br>group | Root clock<br>(clk_hf) | Peripherals | LP<br>(1.1 V Typ) | ULP<br>(1.0 V Typ) | Description                                                                                                                                    |

| 0             | clk_hf0                | CPU Trace   | 24 MHz            | 24 MHz             | -                                                                                                                                              |

|               |                        | SCB         |                   |                    |                                                                                                                                                |

|               |                        | TCPWM       |                   |                    | Async peripherals: Strobe signals are                                                                                                          |

| 1             | clk_hf1                | LIN         | 96 MHz            | 48 MHz             | driven through dividers; Interface clock is generated inside the peripheral with the                                                           |

|               |                        | CANFD       |                   |                    | main group clock.                                                                                                                              |

|               |                        | SMARTIO     |                   |                    |                                                                                                                                                |

|               |                        | SMIF        |                   |                    | Direct connection pass through from                                                                                                            |

|               |                        | BTSS        |                   |                    | clk_hf. This clock is not used for interface clock, rather it is used for the MMIO clocks                                                      |

| 2             | clk_hf0                | CRYPTO      | 96 MHz            | 48 MHz             | of SMIF, BTSS and CRYPTO. BTSS uses this clock for Master and Slave AHB/MMIO transactions, and SMIF also uses this clock for FAST/SLOW clocks. |

|               |                        | PDM         |                   |                    | Uses PERI ACLK with default div by 2                                                                                                           |

| 3             | clk_hf1                | TDM         | 96 MHz            | 48 MHz             | option, required interface frequencies are obtained by further division inside the peripheral.                                                 |

| 4             | clk_hf2                | BTSS        | 48 MHz            | 48 MHz             | RPU clock for BTSS                                                                                                                             |

| 5             | clk_hf3                | ADCMIC      | 24 MHz            | 24 MHz             | Direct connection for ADCMIC, main source of clk_hf3 is clk_althf which is the BTSS ECO clock.                                                 |

| 6             | clk_hf1                | SMIF        | 96 MHz            | 48 MHz             | Direct connection for SMIF and SMARTIO peripherals. This clock is an interface clocks for these peripherals.                                   |

System resources

# 7.1.3 Internal main oscillator (IMO)

The IMO is the primary source of internal clocking. It is trimmed during testing to achieve the specified accuracy. The IMO default frequency is 8 MHz and tolerance is  $\pm 2\%$ .

# 7.1.4 Internal low-speed oscillator (ILO)

The ILO is a very low power oscillator, nominally 32 kHz, which operates in all power modes. The ILO can be calibrated against a higher accuracy clock for better accuracy.

Figure 8 CYW20829 clocking diagram with corresponding oscillators

**Note:** Using PILO as the ILO clock source will result in longer boot time.

System resources

# 7.1.5 External crystal oscillators (ECO)

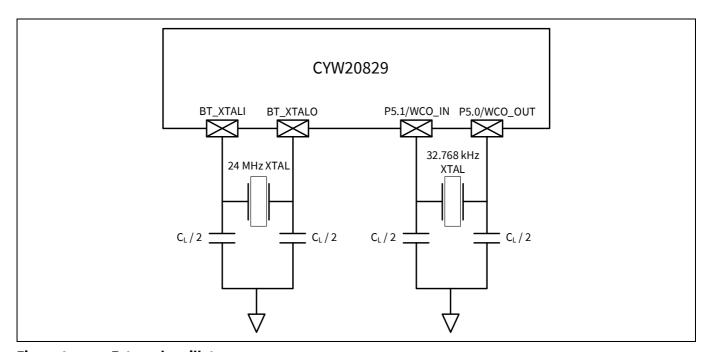

**Figure 9** shows all of the external crystal oscillator circuits for CYW20829. The component values shown are typical; check the ECO specifications for the crystal values, and the crystal datasheet for the load capacitor values. The ECO and WCO require balanced external load capacitors. For more information, see the HW design guidelines. Note that its performance is affected by GPIO switching noise.

Figure 9 External oscillator

# 7.1.6 Watchdog timers (WDT, MCWDT)

CYW20829 has one WDT and two multi-counter WDTs (MCWDTs). The WDT has a 16-bit free-running counter. Each MCWDT has two 16-bit counters and one 32-bit counter, with multiple operating modes. All of the 16-bit counters can generate a watchdog device reset. All of the counters can generate an interrupt on a match event.

The WDT is clocked by the ILO. It can do interrupt/wakeup generation in system LP/ULP, Deep Sleep, and Hibernate power modes. The MCWDTs are clocked by LFCLK (ILO or WCO). It can do periodic interrupt/wakeup generation in system LP/ULP and Deep Sleep power modes.

#### 7.1.7 Clock dividers

Integer and fractional clock dividers are provided for peripheral use and timing purposes. There are one or more:

- 8-bit clock dividers

- 16-bit integer clock dividers

- 16.5-bit fractional clock dividers

- · 24.5-bit fractional clock divider

### 7.1.8 Trigger routing

CYW20829 contains a trigger multiplexer block. This is a collection of digital multiplexers and switches that are used for routing trigger signals between peripheral blocks and between GPIOs and peripheral blocks.

There are two types of trigger routing. Trigger multiplexers have reconfigurability in the source and destination. There are also hardwired switches called "one-to-one triggers", which connect a specific source to a destination. The user can enable or disable the route.

System resources

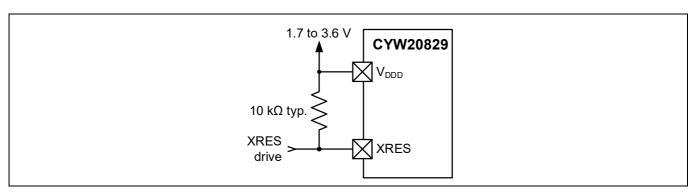

#### 7.1.9 Reset

CYW20829 can be reset from a variety of sources:

- Power-on reset (POR) to hold the device in reset while the power supply ramps up to the level required for the device to function properly. POR activates automatically at power-up.

- Brown-out detect (BOD) reset to monitor the digital voltage supply V<sub>DDD</sub> and generate a reset if V<sub>DDD</sub> falls below the minimum required logic operating voltage.

- External reset dedicated pin (XRES) to reset the device using an external source. The XRES pin is active LOW. It can be connected either to a pull-up resistor to V<sub>DDD</sub>, or to an active drive circuit, as **Figure 10** shows. If a pull-up resistor is used, select its value to minimize current draw when the pin is pulled LOW; 10 kΩ is typical.

Figure 10 XRES connection diagram

- Watchdog Timer (WDT or MCWDT) to reset the device if firmware fails to service it within a specified timeout period.

- Software-initiated reset to reset the device on demand using firmware.

- Logic-protection fault can trigger an interrupt or reset the device if unauthorized operating conditions occur; for example, reaching a debug breakpoint while executing privileged code.

- Hibernate wakeup reset to bring the device out of the system Hibernate low-power mode.

Reset events are asynchronous and guarantee reversion to a known state. Some of the reset sources are recorded in a register, which is retained through reset and allows software to determine the cause of the reset.

System resources

# 7.2 Bluetooth® LE radio and subsystem

CYW20829 incorporates a Bluetooth® 5.4 LE subsystem (BLESS) that contains the physical layer (PHY) and link layer (LL) engines with an embedded security engine. The Bluetooth® LE SS supports all Bluetooth® LE 5.4 features including LE 2 Mbps, LE Long Range, LE Advertising Extensions, LE Isochronous Channels, Periodic Advertising with Responses (PAwR), Encrypted Advertising Data, LE GATT Security Levels Characteristic and Advertising Coding Selection.

The physical layer consists of the digital PHY and the RF transceiver that transmits and receives Gaussian frequency shift keying (GFSK) packets at 1 or 2 Mbps over a 2.4 GHz ISM band, The device also supports Bluetooth® LE long range, both 500 and 125 kbps speeds.

The baseband controller is a composite hardware and firmware implementation that supports both master and slave modes. Key protocol elements, such as HCI and link control, are implemented in firmware. Time-critical functional blocks, such as encryption, CRC, data whitening, and access code correlation, are implemented in hardware (in the LL engine).

The RF transceiver contains an integrated balun, which provides a single-ended RF port pin to drive a 50  $\Omega$  antenna via a matching/filtering network. In the receive direction, this block converts the RF signal from the antenna to a digital bit stream after performing GFSK demodulation. In the transmit direction, this block performs GFSK modulation and then converts a digital baseband signal to a radio frequency before transmitting it through the antenna.

# 7.3 Programmable analog-to-digital converter (ADC)

### 7.3.1 Sigma delta ADC

The ADC block is a single switched-cap  $\Sigma$ - $\Delta$  ADC core for audio and DC measurement. It operates at the 12-MHz clock rate and has 32 DC input channels, including eight GPIO inputs. The internal bandgap reference has  $\pm 5\%$  accuracy without calibration. Different calibration and digital correction schemes can be applied to reduce ADC absolute error and improve measurement accuracy in DC.

One of three internal references may be used for the ADC reference voltage:  $V_{DDA}$ ,  $V_{DDA/2}$ , and an analog reference (AREF). AREF is nominally 1.2 V, trimmed to  $\pm 1\%$ .

# 7.4 Programmable digital

- · System Deep Sleep operation

- Asynchronous or synchronous (clocked) operation

- · Can be synchronous or asynchronous

System resources

# 7.5 Fixed-function digital

# 7.5.1 Timer/counter/pulse-width modulator (TCPWM) block

- The TCPWM supports the following operational modes:

- Timer-counter with compare

- Timer-counter with capture

- Quadrature decoding

- Pulse width modulation (PWM)

- Pseudo-random PWM

- PWM with dead time

- Up, down, and up/down counting modes

- Clock pre-scaling (division by 1, 2, 4, ... 64, 128)

- Double buffering of compare/capture and period values

- Underflow, overflow, and capture/compare output signals

- Supports interrupt on:

- Terminal count Depends on the mode; typically occurs on overflow or underflow

- Capture/compare The count is captured to the capture register or the counter value equals the value in the compare register

- Complementary output for PWMs

- Selectable start, reload, stop, count, and capture event signals for each TCPWM; with rising edge, falling edge, both edges, and level trigger options. The TCPWM has a Kill input to force outputs to a predetermined state.

In this device there are:

- Two 32-bit TCPWMs

- Seven 16-bit TCPWMs

System resources

external memory.

**Datasheet**

#### 7.5.2 Serial communication blocks (SCB)

- This product line has three SCBs:

- First SCB: Configurable as SPI or I<sup>2</sup>C

- Second SCB: Configurable as SPI or UART

- Third SCB: Configurable as I<sup>2</sup>C or UART

- One SCB (SCB #0) can operate in system Deep Sleep mode with an external clock; this SCB can be either SPI slave or I<sup>2</sup>C slave.

- I<sup>2</sup>C mode: The SCB can implement a full multi-master and slave interface (it is capable of multimaster arbitration). This block can operate at speeds of up to 1 Mbps (Fast Mode Plus). It also supports EZI2C, which creates a mailbox address range and effectively reduces I<sup>2</sup>C communication to reading from and writing to an array in the memory. The SCB supports a 256-byte FIFO for receive and transmit. The I<sup>2</sup>C peripheral is compatible with I<sup>2</sup>C standard-mode, Fast Mode, and Fast Mode Plus devices. The I<sup>2</sup>C bus I/O is implemented with GPIO in open-drain modes.

- UART mode: This is a full-feature UART operating at up to 8 Mbps. It supports automotive single-wire interface (LIN), infrared interface (IrDA), and SmartCard (ISO 7816) protocols, all of which are minor variants of the basic UART protocol. In addition, it supports the 9-bit multiprocessor mode that allows the addressing of peripherals connected over common Rx and Tx lines. Common UART functions such as parity error, break detect, and frame error are supported. A 256-byte FIFO allows much greater CPU service latencies to be tolerated.

- SPI mode: The SPI mode supports full SPI, Secure Simple Pairing (SSP) (essentially adds a start pulse that is used to synchronize SPI Codecs), and Microwire (half-duplex form of SPI). The SPI block supports an EZSPI mode in which the data interchange is reduced to reading and writing an array in memory. The SPI interface operates with a 4-MHz clock.

#### 7.5.3 **QSPI** interface serial memory interface (SMIF)

A serial memory interface is provided, running at up to 48 MHz. It supports single, dual and quad SPI configurations, and supports up to four external memory devices. It supports two modes of operation:

- Memory-mapped I/O (MMIO), a command mode interface that provides data access via the SMIF registers and

- Execute-in-Place (XIP), in which AHB reads and writes are directly translated to SPI read and write transfers. In XIP mode, the external memory is mapped into the CYW20829 internal address space, enabling code execution directly from the external memory. To improve performance, a 32 KB cache is included. XIP mode also supports

AES-128 based on-the-fly encryption and decryption, enabling secure storage and access of code and data in the

002-39262 Rev. \*\*

System resources

#### 7.6 **GPIO**

CYW20829 has up to 32 GPIOs, which implement:

- · Eight drive strength modes:

- Analog input mode (input and output buffers disabled) on some IOs

- Input only

- Weak pull-up with strong pull-down

- Strong pull-up with weak pull-down

- Open drain with strong pull-down

- Open drain with strong pull-up

- Strong pull-up with strong pull-down

- Weak pull-up with weak pull-down

- Hold mode for latching previous state (used for retaining the I/O state in system Hibernate and deep sleep mode)

- Selectable slew rates for dV/dt-related noise control to improve EMI

The pins are organized in logical entities called ports, which are up to eight pins in width. Data output and pin state registers store, respectively, the values to be driven on the pins and the input states of the pins.

Every pin can generate an interrupt if enabled; each port has an interrupt request (IRQ) associated with it.

The port 4 pins are capable of overvoltage-tolerant (OVT) operation, where the input voltage may be higher than  $V_{DDD}$ . OVT pins are commonly used with  $I^2C$ , to allow powering the chip OFF while maintaining a physical connection to an operating  $I^2C$  bus without affecting its functionality.

GPIO pins can be ganged to source or sink higher values of current. GPIO pins, including OVT pins, may not be pulled up higher than the absolute maximum; see "Electrical characteristics" on page 39.

During power-on and reset, the pins are forced to the analog input drive mode, with input and output buffers disabled, so as not to crowbar any inputs and/or cause excess turn-on current.

A multiplexing network known as the high-speed I/O matrix (HSIOM) is used to multiplex between various peripheral and analog signals that may connect to an I/O pin.

In order to get the best performance, the following frequency and drive mode constraints may be applied. The DRIVE\_SEL values (refer to **Table 11**) represent drive strengths.

Table 11 DRIVE\_SEL values

| Ports        | Maximum frequency      | Drive strength for V <sub>DDD</sub> 2.7 V | Drive strength for V <sub>DDD</sub> > 2.7 V |

|--------------|------------------------|-------------------------------------------|---------------------------------------------|

| Ports 0, 1   | 8 MHz                  | DRIVE_SEL 2                               | DRIVE_SEL 3                                 |

| Ports 2 to 5 | 16 MHz; 24 MHz for SPI | DRIVE_SEL 2                               | DRIVE_SEL 3                                 |

System resources

# 7.7 Special-function peripherals

# 7.7.1 Audio subsystem

This subsystem consists of the following hardware blocks:

- One inter-IC sound (I<sup>2</sup>S) interface

- Two pulse-density modulation (PDM) to pulse-code modulation (PCM) decoder channels

The I<sup>2</sup>S interface implements two independent hardware FIFO buffers TX and RX, which can operate in master or slave mode. The following features are supported:

- Multiple data formats I<sup>2</sup>S, left-justified, Time Division Multiplexed (TDM) mode A, and TDM mode B

- Programmable channel/word lengths 8/16/18/20/24/32 bits

- Internal/external clock operation. Up to 192 ksps

- Interrupt mask events trigger, not empty, full, overflow, underflow, watchdog

- Configurable FIFO trigger level with datawire support

The I<sup>2</sup>S interface is commonly used to connect with audio codecs, simple DACs, and digital microphones.

The PDM-to-PCM decoder implements a single hardware Rx FIFO that decodes a stereo or mono 1-bit PDM input stream to PCM data output. The following features are supported:

- Programmable data output word length 16/18/20/24 bits

- Configurable PDM clock generation. Range from 384 kHz to 3.072 MHz

- Droop correction and configurable decimation rate for sampling; up to 48 ksps

- Programmable high-pass filter gain

- Interrupt mask events not empty, overflow, trigger, underflow

- Configurable FIFO trigger level with DMA support

The PDM-to-PCM decoder is commonly used to connect to digital PDM microphones. Up to two microphones can be connected to the same PDM data line.

Pinouts

# Each port pin has multiple alternate functions. These are defined in **Table 13**.

| Port/Pin | Analog | ACT #0                           | ACT #1                             | ACT #4             | ACT #5                        | ACT #6                | ACT #7               | ACT #8                   | ACT #9                    | ACT #10                   | ACT #11                        | ACT #12                       | ACT #13                     | ACT #14 | ACT #15                    | DS #2                      | DS #3                | DS #5                            | DS #6                        | DS #7 |

|----------|--------|----------------------------------|------------------------------------|--------------------|-------------------------------|-----------------------|----------------------|--------------------------|---------------------------|---------------------------|--------------------------------|-------------------------------|-----------------------------|---------|----------------------------|----------------------------|----------------------|----------------------------------|------------------------------|-------|

| P0.0     |        | tcpwm[0].<br>line_<br>compl[0]:3 | tcpwm[0].<br>line_<br>compl[262]:0 |                    |                               |                       |                      |                          | pdm.<br>pdm_<br>clk[1]:0  |                           |                                | tdm.tdm_<br>tx_<br>mck[0]:0   | tdm.tdm_<br>rx_<br>mck[0]:0 |         |                            | keyscan.<br>ks_<br>col[2]  |                      |                                  | scb[0].<br>spi_<br>select1:0 |       |

| P0.1     |        | tcpwm[0].<br>line[1]:3           | tcpwm[0].<br>line[256]:1           |                    |                               |                       |                      |                          | pdm.<br>pdm_<br>data[1]:0 |                           |                                | tdm.tdm_<br>tx_sck[0]:0       |                             |         |                            | keyscan.<br>ks_<br>col[3]  |                      |                                  | scb[0].<br>spi_<br>select2:0 |       |

| P0.2     |        | tcpwm[0].<br>line_<br>compl[1]:3 | tcpwm[0].<br>line_<br>compl[256]:1 |                    |                               |                       |                      |                          |                           | peri.tr_io_<br>input[4]:0 |                                | tdm.tdm_<br>tx_<br>fsync[0]:0 |                             |         |                            | keyscan.<br>ks_<br>col[11] | scb[0].<br>i2c_scl:0 |                                  | scb[0].<br>spi_<br>mosi:0    |       |

| P0.3     |        | tcpwm[0].<br>line[0]:4           | tcpwm[0].<br>line[257]:1           |                    |                               |                       |                      | scb[1].spi_<br>select3:0 |                           |                           |                                | tdm.tdm_<br>tx_sd[0]:0        |                             |         |                            | keyscan.<br>ks_<br>col[12] | scb[0].<br>i2c_sda:0 |                                  | scb[0].<br>spi_<br>miso:0    |       |

| P0.4     |        | tcpwm[0].<br>line_<br>compl[0]:4 | tcpwm[0].<br>line_<br>compl[257]:1 | srss.ext_<br>clk:0 | cpuss.<br>trace_<br>data[3]:1 |                       |                      | scb[1].spi_<br>select2:0 |                           | peri.tr_io_<br>input[0]:0 |                                | tdm.tdm_<br>rx_sck[0]:0       |                             |         |                            | keyscan.<br>ks_<br>row[0]  |                      |                                  | scb[0].<br>spi_clk:0         |       |

| P0.5     |        | tcpwm[0].<br>line[1]:4           | tcpwm[0].<br>line[258]:1           |                    | cpuss.<br>trace_<br>data[2]:1 |                       |                      | scb[1].spi_<br>select1:0 |                           | peri.tr_io_<br>input[1]:0 |                                | tdm.tdm_<br>rx_<br>fsync[0]:0 |                             |         | smif.<br>spihb_<br>select1 | keyscan.<br>ks_<br>row[1]  |                      |                                  | scb[0].<br>spi_<br>select0:0 |       |

| P1.0     |        | tcpwm[0].<br>line_<br>compl[1]:4 | tcpwm[0].<br>line_<br>compl[258]:1 |                    | cpuss.<br>trace_<br>data[1]:1 | scb[1].<br>uart_cts:0 |                      | scb[1].spi_<br>select0:0 |                           |                           | peri.tr_<br>io_<br>output[0]:0 | tdm.tdm_<br>rx_sd[0]:0        |                             |         |                            | keyscan.<br>ks_<br>row[2]  |                      | cpuss.<br>swj_<br>swo_<br>tdo    |                              |       |

| P1.1     |        | tcpwm[0].<br>line[0]:5           | tcpwm[0].l<br>ine[259]:1           |                    | cpuss.<br>trace_<br>data[0]:1 | scb[1].<br>uart_rts:0 |                      | scb[1].spi_<br>clk:0     |                           |                           | peri.tr_<br>io_<br>output[1]:0 |                               |                             |         |                            | keyscan.<br>ks_<br>row[3]  |                      | cpuss.<br>swj_<br>swdoe_<br>tdi  |                              |       |

| P1.2     |        | tcpwm[0].<br>line_<br>compl[0]:5 | tcpwm[0].<br>line_<br>compl[259]:1 |                    | cpuss.<br>trace_<br>clock:1   | scb[1].<br>uart_rx:0  | scb[2].i2c_<br>scl:1 | scb[1].spi_<br>mosi:0    |                           | peri.tr_io_<br>input[2]:0 |                                |                               |                             |         |                            | keyscan.<br>ks_<br>row[4]  |                      | cpuss.<br>swj_<br>swdio_<br>tms  |                              |       |

| P1.3     |        | tcpwm[0].<br>line[1]:5           | tcpwm[0].<br>line[260]:1           |                    |                               | scb[1].<br>uart_tx:0  | scb[2].i2c_<br>sda:1 | scb[1].spi_<br>miso:0    |                           | peri.tr_io_<br>input[3]:0 |                                |                               |                             |         |                            | keyscan.<br>ks_<br>row[5]  |                      | cpuss.clk_<br>swj_<br>swclk_tclk |                              |       |

| P1.4     |        | tcpwm[0].<br>line_<br>compl[1]:5 | tcpwm[0].<br>line_<br>compl[260]:1 |                    |                               |                       |                      |                          |                           |                           | lin[0].lin_<br>en[1]:0         |                               |                             |         |                            | keyscan.<br>ks_<br>col[4]  |                      |                                  |                              |       |

| P1.5     |        | tcpwm[0].<br>line[0]:6           | tcpwm[0].<br>line[261]:1           |                    |                               |                       |                      |                          |                           |                           | lin[0].lin_<br>rx[1]:0         |                               |                             |         |                            | keyscan.<br>ks_<br>col[5]  |                      |                                  |                              |       |

| P1.6     |        | tcpwm[0].<br>line_<br>compl[0]:6 | tcpwm[0].<br>line_<br>compl[261]:1 |                    |                               |                       |                      |                          |                           |                           | lin[0].lin_<br>tx[1]:0         |                               |                             |         |                            | keyscan.<br>ks_<br>col[6]  | srss.cal_<br>wave    |                                  |                              |       |