# 21-148603 Microstrip Line Document

FCC ID:UZ7211486030A FCC ID:UZ7211486030B

1. Trace layout and dimensions including rules for:

Trace and parts isolation requirements;

USI: OEM should copy the original design of antenna length and shapes.

Placement of passive parts traces, antenna and connectors;

USI: Please refer to Layout file of EVB, 21-148603 CARRIER M1 V31

Boundary limits of size (thickness, length, width) and shape(s) of the trace must be clearly described for each type antenna;

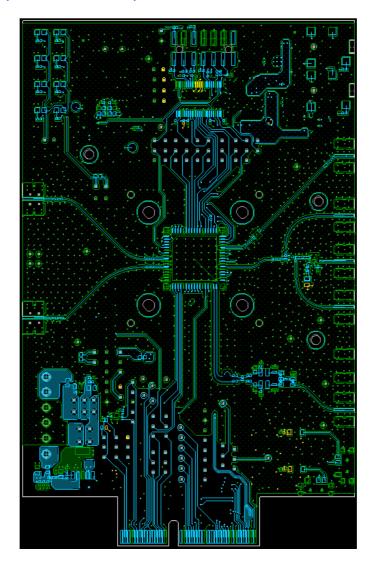

#### PCB Specification of 21-148603 SiP Module Carrier Board

This PCB SPEC is for 21-148603 SiP module carrier board project. This document define the PCB (Printed Circuit Board) manufacturing SPEC. Due to this product are applied in wireless communication field, so all the SPEC defined in this document should be followed strictly in order to control the line impedance and parasitic effects. Any changes or modification must have been rechecked for all test results.

| PCB design requirement                                              |           |                |  |  |

|---------------------------------------------------------------------|-----------|----------------|--|--|

| PCB size: 85mm* 135 mm +/-0.127mm                                   |           |                |  |  |

| Eight Layer PCB, Any Layer Stack:                                   |           |                |  |  |

|                                                                     |           |                |  |  |

| PCB Material: FR4, TG150, Halogen-Free                              |           |                |  |  |

| Solder Resister Color: Green                                        |           |                |  |  |

| The PCB stack is as follows: (unit :mil)                            |           |                |  |  |

| Layer                                                               | Thickness |                |  |  |

| Solder Mask                                                         | 0.8       |                |  |  |

| Add Plating                                                         | 0.9       |                |  |  |

| L1                                                                  | 0.6       | Layer 1: Top   |  |  |

| P.P                                                                 | 9.5       |                |  |  |

| L2                                                                  | 1.2       | Layer 2: GND   |  |  |

| P.P                                                                 | 3.4       |                |  |  |

| L3                                                                  | 1.2       | Layer 3: Inner |  |  |

| P.P                                                                 | 27.95     |                |  |  |

| L4                                                                  | 1.2       | Layer 4: GND   |  |  |

| P.P                                                                 | 3.4       |                |  |  |

| L5                                                                  | 1.2       | Layer 5: Power |  |  |

| P.P                                                                 | 9.5       |                |  |  |

| L6                                                                  | 0.6       | Layer 6: Bot   |  |  |

| Add Plating                                                         | 0.9       |                |  |  |

| Solder mask                                                         | 0.8       |                |  |  |

| Total                                                               | 63.15     |                |  |  |

| Total Thickness: 1.6mm +/- 10%                                      |           |                |  |  |

| Surface finish: Immersion Nickel(118 micro inch)/Gold(2 micro inch) |           |                |  |  |

#### **Boundary limits of the size**

Please refer to the PCB specification stack-up, and all the transmitted transmission lines have the 50ohm.

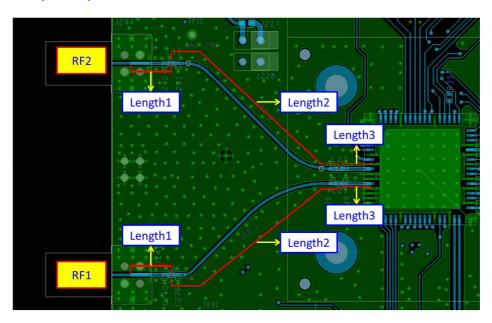

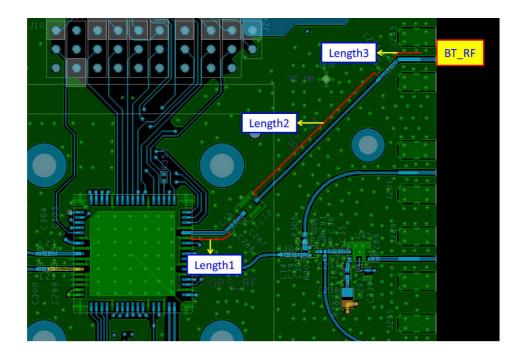

The critical transmitted microstrip lines are the RF2, RF1, BT\_RF.

## Components on the trace of RF2, RF1, BT\_RF

#### **EVB BOM:**

RF2's components: L12, L23. RF1's components: L11, L21.

BT\_RF's components: L15, FLT2, L13.

| Item Description                        | Ref Des                 | Mfr. Name | Mfr. Part Number |

|-----------------------------------------|-------------------------|-----------|------------------|

| CHIP RES 0R MAX0.05R 1/20W 0201 L/F     | L12, L23, L11, L21, L13 | WALSIN    | WR02X000PAL      |

| BPF 2.45G LFB2H2G45CC1D005 SMD4 2.5*2mm | FLT2                    | MURATA    | LFB2H2G45CC1D005 |

## Micro-strip line description and limits for RF2, RF1, BT\_RF

RF2:

Length1: 219 mil, Length2: 1052.78 mil, Length3: 166 mil. (+/- 5%)

Width: 15.5 mil. (+/- 5%)

**RF1:**

Length1: 219.12 mil, Length: 1005.02 mil, Length3: 169.3 mil. (+/- 5%)

Width: 15.5 mil. (+/- 5%)

#### BT\_RF:

Length1: 219 mil, Length2: 1052.78 mil, Length3: 166 mil. (+/- 5%)

Width: 15.5 mil. (+/- 5%)

Different antenna length and shapes affect radiated emissions and each design shall be considered a different type; e.g., antenna length in multiple(s) of frequency wavelength and antenna shape (traces in phase) can affect antenna gain and must be considered;

USI: OEM will verify the radiated emission when modifying antenna length and shapes which base on the original design as benchmark.

If the above data is to be provided by a Gerber file for PC layout, this should be specified in the filing.

USI: Yes. Above data is from Gerber file.

- 2. Test procedures for design verification.

OEM should copy the original design of antenna length and shapes.

- 3. Production test procedures for ensuring compliance. OEM should copy the original design of antenna length and shapes.