FCC ID: UXU1MW

IC: 7316A-1MW

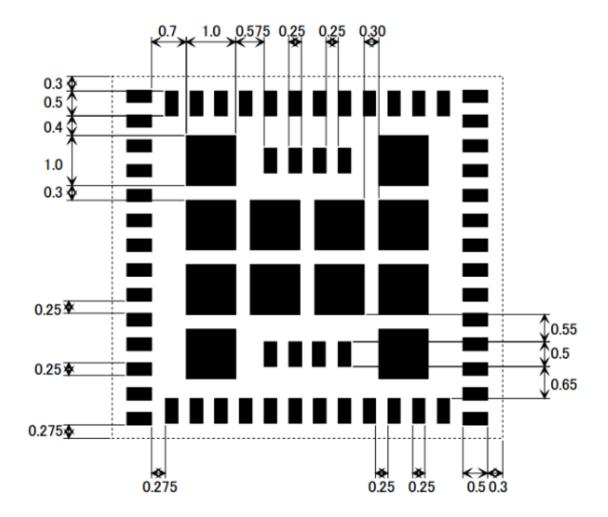

## Land Pattern TOP View

\* To avoid the short-circuit between the side shielding and a solder on the module land after the reflow, please locate the module land at 0.2mm away from module outline as above figure.

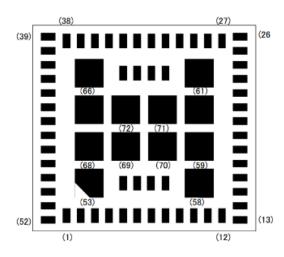

| Pin<br>No. | Description | Pin<br>No. | Description | Pin<br>No. | Description   | Pin<br>No. | Description |

|------------|-------------|------------|-------------|------------|---------------|------------|-------------|

| 1          | GPIO_6      | 19         | GND         | 37         | I2S_CLK       | 55         | GND         |

| 2          | GPIO_0      | 20         | SDIO_CLK    | 38         | I2S_WS        | 56         | GND         |

| 3          | GPIO_3      | 21         | GND         | 39         | GND           | 57         | JTAG_SEL    |

| 4          | GPIO_5      | 22         | VBAT_LDO    | 40         | BT_DEV_WAKE   | 58         | GND         |

| 5          | GPIO_1      | 23         | VBAT_SR     | 41         | BT_HOST_WAKE  | 59         | GND         |

| 6          | GPIO_4      | 24         | SR_PVSS     | 42         | I2S_DI        | 60         | GND         |

| 7          | GPIO_2      | 25         | VIN_LDO     | 43         | NC            | 61         | GND         |

| 8          | BT_REG_ON   | 26         | SR_PVSS     | 44         | GND           | 62         | BT_GPIO_4   |

| 9          | WL_REG_ON   | 27         | SR_PVSS     | 45         | BT_UART_RXD   | 63         | BT_GPIO_3   |

| 10         | GND         | 28         | SR_VLX      | 46         | BT_UART_TXD   | 64         | BT_GPIO_2   |

| 11         | VIO         | 29         | GND         | 47         | BT_UART_RTS_N | 65         | BT_GPIO_5   |

| 12         | GND         | 30         | LPO_IN      | 48         | BT_UART_CTS_N | 66         | GND         |

| 13         | GND         | 31         | GPIO_7      | 49         | GND           | 67         | GND         |

| 14         | SDIO_DATA0  | 32         | BT_PCM_IN   | 50         | ANT           | 68         | GND         |

| 15         | SDIO_CMD    | 33         | BT_PCM_SYNC | 51         | GND           | 69         | GND         |

| 16         | SDIO_DATA1  | 34         | BT_PCM_OUT  | 52         | GND           | 70         | GND         |

| 17         | SDIO_DATA2  | 35         | BT_PCM_CLK  | 53         | GND           | 71         | GND         |

| 18         | SDIO_DATA3  | 36         | I2S_DO      | 54         | NC            | 72         | GND         |

## Supply Voltage

| Para             | Min.            | Тур. | Max. | Unit  |   |

|------------------|-----------------|------|------|-------|---|

| Operating Temper | -30             | 25   | +85  | deg.C |   |

| Supply Voltage   | VBAT            | 3.2  | 3.3  | 4.8   | V |

|                  | VIO*2 1.8V/3.3V | 1.62 | -    | 3.63  | V |

\*1: Surface temperature of the shield case

Functionality is guaranteed but specifications require derating at extreme temperatures

\*2: VIO don't influence the RF characteristic. Tolerance of 1.8V and 3.3V is  $\pm 10\%$ .

## Antenna

■Please perform the antenna design that followed the specifications of the antenna.

■About the signal line between an antenna and a module It is a 50-ohm line design.

Fine tuning of return loss etc. can be performed using a matching network. However, it is required to check "Class1 change" and "Class2 change" which the authorities define then.

The concrete contents of a check are the following three points.

- 1) It is the same type as the antenna type of antenna specifications.

- 2) An antenna gain is lower than a gain given in antenna specifications.

- 3) The emission level is not getting worse.

■50-ohm line(microstrip line length)

Antenna type: monopole pattern antenna

50-ohm feed line length: 0mm