Model:

Vision:

Date:

Page No.:

<u>Z3000B</u>

Version 2.0

#### 2004-04-12

## Tuning Up procedure & Operational Manual

Page 24of 56

| OM6354      |                 |      |          | CONNECTED TO DEVICE SIGNALS |        |          |        |          |  |

|-------------|-----------------|------|----------|-----------------------------|--------|----------|--------|----------|--|

| NAME        | DESCRIPTION     | BALL | PCF50874 |                             |        | PCF50732 |        |          |  |

|             |                 |      | TYPE     | SUPPLY                      | NAME   | TYPE     | SUPPLY | NAME     |  |

| HD0         | memory data bus | H4   | I/O      | VDDE3                       | HD0    |          |        |          |  |

| HD1         |                 | H3   | I/O      | VDDE3                       | HD1    |          |        |          |  |

| HD2         | 1               | H2   | I/O      | VDDE3                       | HD2    |          |        |          |  |

| HD3         | 1               | J3   | I/O      | VDDE3                       | HD3    |          |        |          |  |

| HD4         | 7               | E5   | I/O      | VDDE3                       | HD4    |          |        |          |  |

| HD5         | 7               | H1   | I/O      | VDDE3                       | HD5    |          |        |          |  |

| HD6         | 7               | B1   | I/O      | VDDE3                       | HD6    |          |        |          |  |

| HD7         | 7               | E4   | I/O      | VDDE3                       | HD7    |          |        |          |  |

| HD8         | 1               | F3   | I/O      | VDDE3                       | HD8    |          |        |          |  |

| HD9         | 7               | F2   | I/O      | VDDE3                       | HD9    |          |        |          |  |

| HD10        | 7               | F1   | I/O      | VDDE3                       | HD10   |          |        |          |  |

| HD11        | 7               | E1   | 1/O      | VDDE3                       | HD11   |          |        | 41<br>41 |  |

| HD12        | 1               | D1   | I/O      | VDDE3                       | HD12   |          |        |          |  |

| HD13        | 1               | E3   | I/O      | VDDE3                       | HD13   |          |        |          |  |

| HD14        | 7               | E2   | I/O      | VDDE3                       | HD14   |          |        |          |  |

| HD15        | 7               | B2   | I/O      | VDDE3                       | HD15   |          |        |          |  |

| HWR_N       | memory control  | L5   | 0        | VDDE3                       | HWR_N  |          |        |          |  |

| HRD_N       | signals         | H5   | 0        | VDDE3                       | HRD_N  |          |        |          |  |

| CS_N0       | 1               | N4   | 0        | VDDE3                       | CS0_N  |          |        |          |  |

| CS_N1       |                 | G5   | 0        | VDDE3                       | CS1_N  |          |        |          |  |

| CS_N2       |                 | M5   | 0        | VDDE3                       | CS2_N  |          |        |          |  |

| CS_N3       |                 | G3   | 0        | VDDE3                       | CS3_N  |          |        |          |  |

| Keyboard so | canner          |      |          |                             |        |          |        |          |  |

| KBIO7       | keyboard matrix | L14  | I/O      | VDDE1                       | KBI07  |          |        |          |  |

| KBIO6       |                 | L12  | I/O      | VDDE1                       | KBIO6  |          |        |          |  |

| KBIO5       | 7               | L13  | I/O      | VDDE1                       | KBIO5  |          |        |          |  |

| KBIO4       | 1               | L11  | I/O      | VDDE1                       | KBIO4  |          |        |          |  |

| KBIO3       | 1               | J11  | I/O      | VDDE1                       | KBIO3  |          |        |          |  |

| KBIO2       | 1               | K12  | I/O      | VDDE1                       | KBIO2  |          |        |          |  |

| KBIO1       |                 | J10  | I/O      | VDDE1                       | KBIO1  |          |        |          |  |

| KBIO0       |                 | K10  | 0        | VDDE1                       | KBIO0  |          |        |          |  |

| UART0       | •               |      | •        |                             |        |          |        |          |  |

| CTS0_N      | clear to send   | B5   | I.       | VDDE2                       | CTS0_N |          |        | 9        |  |

| RTS0_N      | request to send | A5   | 0        | VDDE2                       | RTS0_N |          |        | 6<br>1   |  |

| TXD0        | transmit data   | C5   | 0        | VDDE2                       | TXD0   |          |        |          |  |

| RXD0        | receive data    | C4   | 1/O      | VDDE2                       | RXD0   |          |        |          |  |

Z3000B

Model:

Vision:

Date:

Page No.:

Version 2.0

#### 2004-04-12

## Tuning Up procedure & Operational Manual

Page 25of 56

| OM6354                 |                                           |                | CONNECTED TO DEVICE SIGNALS |        |        |            |        |            |

|------------------------|-------------------------------------------|----------------|-----------------------------|--------|--------|------------|--------|------------|

| NAME                   | DESCRIPTION                               | BALL           | PCF50874                    |        |        | PCF50732   |        |            |

|                        |                                           | 1              | TYPE                        | SUPPLY | NAME   | TYPE       | SUPPLY | NAME       |

| UART1                  |                                           |                |                             |        |        |            |        |            |

| TXD1                   | transmit data                             | A4             | 0                           | VDDE2  | TXD1   |            |        | -1<br>51   |

| RXD1                   | receive data                              | D4             | I/O                         | VDDE2  | RXD1   |            |        |            |

| SIM Interface          | 9                                         |                |                             |        |        |            |        |            |

| SIMCLK                 | interface clock                           | M13            | 0                           | VDDE1  | SIMCLK |            |        | ·          |

| SIMIO                  | data transfer                             | M12            | I/O                         | VDDE1  | SIMIO  |            |        |            |

| SIMERR                 | error removal                             | M11            | T                           | VDDE1  | SIMERR |            |        |            |

| General Pur            | pose I/O Port                             |                |                             |        |        |            |        |            |

| GPIO10                 | general purpose                           | K8             | 1/O                         | VDDE2  | GPIO10 |            |        |            |

| GPIO9                  | signal                                    | N8             | I/O                         | VDDE2  | GPIO9  |            |        |            |

| GPIO8                  |                                           | P6             | I/O                         | VDDE2  | GPIO8  |            |        |            |

| GPIO7                  | -                                         | N7             | I/O                         | VDDE2  | GPI07  | -          |        |            |

| GPIO6                  |                                           | L9             | 1/O                         | VDDE2  | GPI06  |            |        |            |

| GPIO5                  |                                           | L7             | 1/O                         | VDDE2  | GPI05  |            | 1      |            |

| GPIO4                  |                                           | P7             | I/O                         | VDDE2  | GPIO4  |            |        |            |

| GPIO3                  | -                                         | N6             | 1/O                         | VDDE2  | GPI03  |            |        |            |

| GPIO2                  |                                           | L8             | 1/O                         | VDDE2  | GPIO2  |            |        |            |

| GPIO1                  |                                           | L6             | 1/O                         | VDDE2  | GPI01  |            |        | 9          |

| GPIO0                  |                                           | P5             | I/O                         | VDDE2  | GPI00  |            |        |            |

| Pulse Width            | Modulator                                 |                |                             |        | 0      |            |        | 8          |

| PWM1                   | pulse width                               | E6             | 0                           | VDDE2  | PWM1   |            |        |            |

| PWM0                   | modulator signal                          | F4             | 0                           | VDDE2  | PWM0   | -          |        |            |

| JTAG and Te            | est Access Port                           | e Sterne       | 199504                      |        |        | -          |        |            |

| тск                    | interface clock                           | A3             | 1                           | VDDE2  | тск    |            |        | 23.<br>    |

| TMS                    | test mode select                          | A2             | T                           | VDDE2  | TMS    |            |        | 6-1<br>675 |

| TDI                    | test data input                           | D2             | 1                           | VDDE2  | TDI    | -          | -      |            |

| TDO                    | test data output                          | D3             | 0                           | VDDE2  | TDO    | - 5.<br>5. |        | 57         |

| TRST N                 | reset                                     | A1             | 1                           | VDDE2  | TRST_N |            |        |            |

| J_SEL                  | controller select<br>BBP DSP or BBP<br>SC | B4             | 1                           | VDDE2  | J_SEL  |            |        |            |

| Power-Dowr             | Control                                   |                |                             |        | •      |            |        |            |

| GPON2                  | general purpose                           | N9             | 0                           | VDDE2  | GPON2  | 8. E       | - 5a   |            |

| GPON1                  | power down signal                         | L10            | 0                           | VDDE2  | GPON1  |            |        |            |

| AUXST                  |                                           | G10            | 0                           | VDDE1  | GPON0  | 1          | VDDD   | AUXST      |

| SAY BUSINESS CHARACTER | ieneral Purpose Outpu                     | 2 3 miles (142 | 1000                        |        |        |            |        |            |

| AMPCTRL                |                                           | H10            | -                           |        |        | 0          | VDDD   | AMPCTE     |

<u>Z3000B</u>

Model:

Vision:

Date:

Page No.:

Version 2.0

### 2004-04-12

## Tuning Up procedure & Operational Manual

Page 260f 56

|              | OM6354                           | CONNECTED TO DEVICE SIGNALS |          |        |      |          |        |         |

|--------------|----------------------------------|-----------------------------|----------|--------|------|----------|--------|---------|

| NAME         | DESCRIPTION                      | BALL                        | PCF50874 |        |      | PCF50732 |        |         |

|              |                                  |                             | TYPE     | SUPPLY | NAME | TYPE     | SUPPLY | NAME    |

| IF Signals   |                                  |                             |          |        |      |          |        |         |

| IP           | baseband                         | J13                         |          |        |      | I/O      | VDDA1  | IP      |

| IN           | differential I signal            | J14                         |          |        |      | I/O      | VDDA1  | IN      |

| QP           | baseband                         | H13                         | 1        |        |      | I/O      | VDDA1  | QP      |

| QN           | differential Q signal            | H14                         |          |        |      | I/O      | VDDA1  | QN      |

| Auxiliary Fu | nctions                          |                             | A.S.     |        |      |          |        |         |

| AUXADC1      | auxiliary ADC input              | F14                         |          |        |      | I        | VDDD   | AUXADC1 |

| AUXADC2      |                                  | G14                         |          |        |      | 1        | VDDD   | AUXADC2 |

| AUXADC3      |                                  | E14                         |          |        |      | L        | VDDD   | AUXADC3 |

| AUXADC4      | 1                                | F13                         |          |        |      | 1        | VDDD   | AUXADC4 |

| AUXDAC1      | auxiliary DAC                    | E12                         |          |        |      | 0        | VDDA1  | AUXDAC1 |

| AUXDAC2      | outputs                          | D13                         |          |        |      | 0        | VDDA1  | AUXDAC2 |

| AUXDAC3      |                                  | D12                         |          |        |      | 0        | VDDA1  | AUXDAC3 |

| Voiceband (  | Codec                            |                             | 34       | 30 X   |      | 22 - 2   | X C    |         |

| MICP         | microphone                       | A13                         |          |        |      | I        | VDDA3  | MICP    |

| MICN         | differential input               | B13                         |          |        |      | 1        | VDDA3  | MICN    |

| AUXMICP      | auxiliary                        | B14                         |          |        |      | 1        | VDDA3  | AUXMICP |

| AUXMICN      | microphone<br>differential input | A14                         |          |        |      | Ĩ        | VDDA3  | AUXMICN |

| EARN         | earphone                         | A11                         |          |        |      | 0        | VDDA4  | EARN    |

| EARP         | differential output              | B10                         |          |        |      | 0        | VDDA4  | EARP    |

| AUXSP        | auxiliary earphone               | A10                         |          |        |      | 0        | VDDA4  | AUXSP   |

| BUZ          | differential output              | B11                         |          |        |      | 0        | VDDA4  | BUZ     |

Notes: TYPE I Input signal

O: Output signal

I/O: Duplexer signal

P: Power

G: Ground

<u>Z3000B</u>

Model:

Vision:

Date:

Version 2.0

## Tuning Up procedure & Operational Manual

2004-04-12

### Page No.: <u>Page 27of 56</u>

### Table 7 Power supply domains for LFBGA180 package

| TYPE                                                                  | NUMBER                                           | DESCRIPTION                                | PIN                                                                                     |

|-----------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------|

| VDDC                                                                  | 4                                                | core power supply pins                     | F5, N13, M8, K6                                                                         |

| VDDE1                                                                 | 4                                                | IO power supply pins                       | C8, H11, N12, P9                                                                        |

| VDDE2                                                                 | 2                                                | IO power supply<br>pins with level shifter | P8, C1                                                                                  |

| VDDE3                                                                 | 4                                                | IO power supply<br>pins with level shifter | G2, L3, P4, M6                                                                          |

| VSS,<br>VSS_VB,<br>VSS_VBOUT,<br>VSS_REF,<br>VSSD,<br>VSS_BB,<br>AVSS | SS_VB,<br>SS_VBOUT,<br>SS_REF,<br>SSD,<br>SS_BB, |                                            | A12, C3, C11, C13, D11, E8, E13, G1, G13, J1, K1,<br>K7, M7, N5, N10, N11, N14, P1, P10 |

| VDD_D                                                                 | 1                                                | Digital Supply of PCF50732                 | C9                                                                                      |

| VDD_VB,<br>VDD_VBOUT,<br>VDD_REF,<br>VDD_BB                           | 4                                                | Analog supplies of PCF50732                | F12, D14, B12, C12                                                                      |

| AVDD                                                                  | 1                                                | PLL supply pin                             | P12                                                                                     |

### 9 Limiting Values

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL                                           | PARAMETER                                                   | MIN.         | MAX.     | UNIT |

|--------------------------------------------------|-------------------------------------------------------------|--------------|----------|------|

| V <sub>DD</sub> C                                | PCF50874 Core supply voltage                                | -0.5         | +3.3     | V    |

| VDDD<br>VDD_BB<br>VDD_VB<br>VDD_VBOUT<br>VDD_REF | PCF50732 Digital and Analog supplies                        | -0.5         | +3.3     | V    |

| VDDE1                                            | PCF50874 IOs supply voltage VDDE1                           | -0.5         | +3.3     | V    |

| VDDE2                                            | PCF50874 IOs supply voltage VDDE2                           | -0.5         | +3.6     | ٧    |

| VDDE3                                            | DE3 PCF50874 IOs supply voltage VDDE3                       |              | +3.6     | V    |

| VI                                               | Input voltage on any pin with respect to ground (VSS)       | -0.5         | VDDx+0.5 | V    |

| IIBBI1                                           | PCF50732 DC current into any pin (except EARP/EARN,AUX,BUZ) | -10          | +10      | mΑ   |

| IIBBI2                                           | PCF50732 DC current into EARP/EARN, AUX, BUZ                | -100         | +100     | mΑ   |

| II, IO                                           | DC current into any input or output                         | -10          | +10      | mΑ   |

| P <sub>tot</sub>                                 | total power dissipation                                     | 9 <u>0</u> 3 | 1.36     | W    |

| T <sub>stg</sub>                                 | storage temperature range                                   | -65          | +150     | °C   |

| T <sub>amb</sub>                                 | operating ambient temperature range                         | -40          | +85      | °C   |

| Ti                                               | operating junction temperature range                        | -            | +125     | °C   |

|              |                                           | Model:    | <u>Z3000B</u> |

|--------------|-------------------------------------------|-----------|---------------|

| Haier        | Qingdao Haier Telecommunication Co., Ltd. | Vision:   | Version 2.0   |

|              |                                           | Date:     | 2004-04-12    |

| Tuning Up pr | ocedure & Operational Manual              | Page No.: | Page 28of 56  |

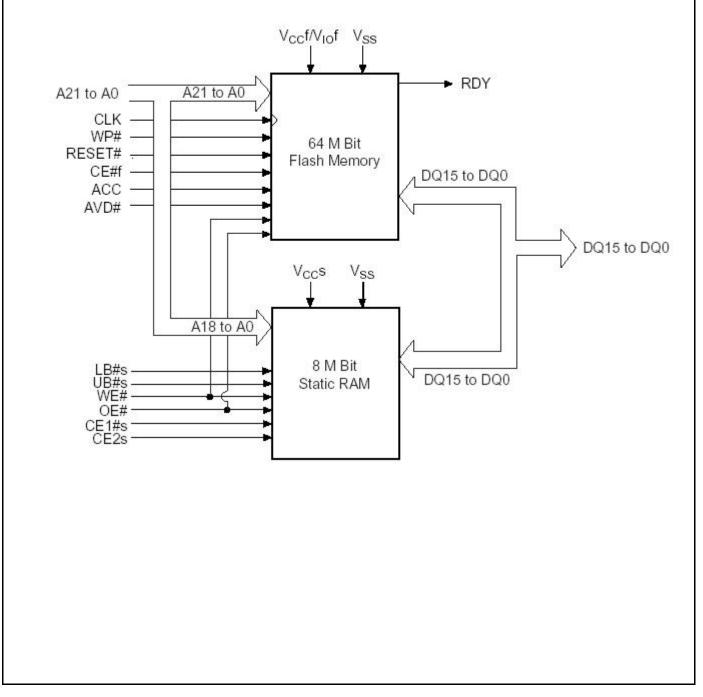

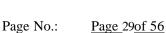

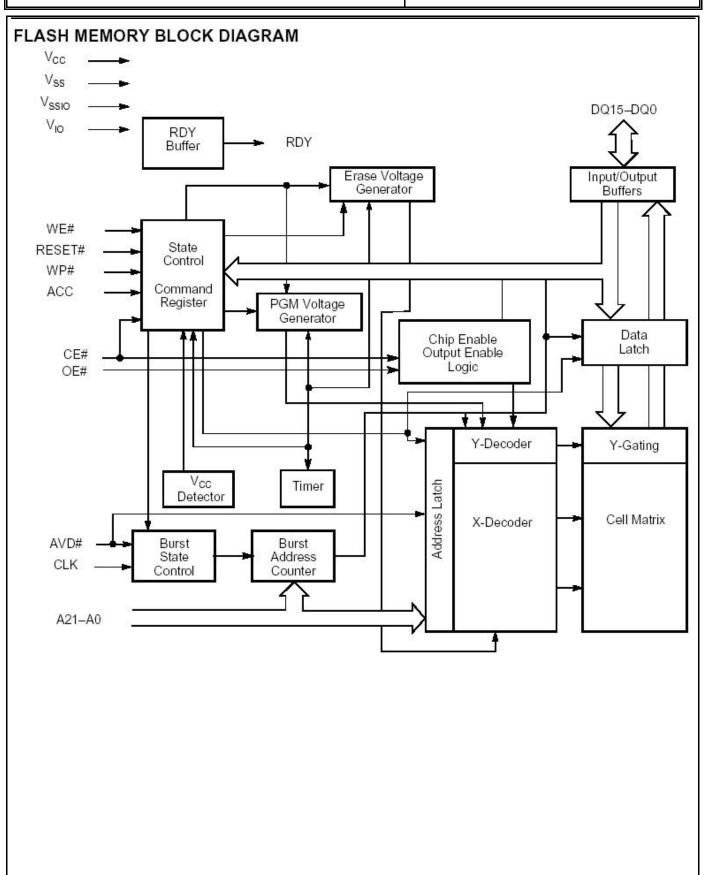

**U500**: Memory chip adopts AM42BDS6408GT89I. It integrates with 64M Bit Flash Memory and 8M Bit SRAM?

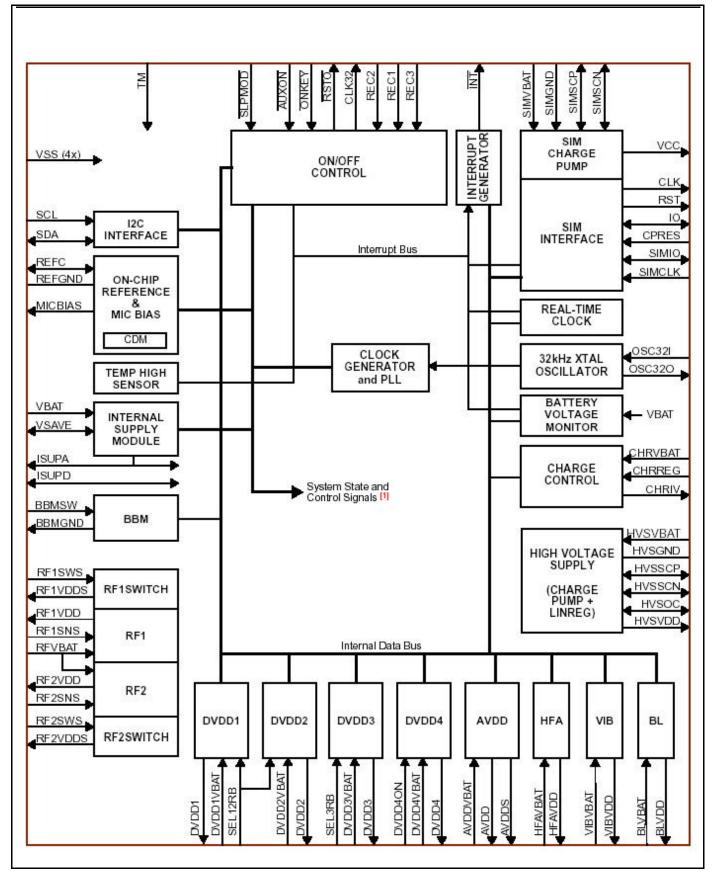

# **BLOCK DIAGRAM**

Model: Z3000B Vision: Version 2.0 2004-04-12

Date:

## **Tuning Up procedure & Operational Manual**

<u>Z3000B</u>

Model:

Vision:

Date:

Page No.:

Version 2.0

### 2004-04-12

### Tuning Up procedure & Operational Manual

Page 31of 56

| Pins desc | cription is as below:                                                                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A18-A0    | 19 Address Inputs (Common)                                                                                                                                        |

| A21-A19   | 3 Address Inputs (Flash)                                                                                                                                          |

| DQ15-DQ0  | 16 Data Inputs/Outputs (Common)                                                                                                                                   |

| CE#f      | Chip Enable (Flash)                                                                                                                                               |

| CE1#s     | Chip Enable 1 (SRAM)                                                                                                                                              |

| CE2s      | Chip Enable 2 (SRAM)                                                                                                                                              |

| OE#       | Output Enable (Common)                                                                                                                                            |

| WE#       | Write Enable (Common)                                                                                                                                             |

| UB#s      | Upper Byte Control (SRAM)                                                                                                                                         |

| LB#s      | Lower Byte Control (SRAM)                                                                                                                                         |

| RESET#    | Hardware Reset Pin, Active Low                                                                                                                                    |

| VCCf      | Flash 1.8 volt-only single power supply (see Product Selector Guide for speed options and voltage supply tolerances)                                              |

| VIOf      | Input & Output Buffer Power Supply must be tied to VCC.                                                                                                           |

| VCCs      | SRAM Power Supply                                                                                                                                                 |

| VSSIOf    | Output Buffer Ground                                                                                                                                              |

| VSS       | Device Ground (Common)                                                                                                                                            |

| NC        | Pin Not Connected Internally                                                                                                                                      |

|           | Ready output; indicates the status of the Burst read.                                                                                                             |

| RDY       | Low = data not valid at expected time.                                                                                                                            |

|           | High = data valid.                                                                                                                                                |

| CLK       | CLK is not required in asynchronous mode. In burst mode, after the initial word is output, subsequent active edges of CLK increment the internal address counter. |

|           | Address Valid input. Indicates to device that the valid address is present on the address inputs (A21–A0).                                                        |

| AVD#      | Low = for asynchronous mode, indicates valid address; for burst mode, causes starting address to be latched.                                                      |

|           | High = device ignores address inputs                                                                                                                              |

| WP#       | Hardware write protect input. At VIL, disables program and erase functions in the two outermost sectors. Should be at VIH for all other conditions.               |

| ACC       | At VID, accelerates programming; automatically places device in unlock bypass mode. At VIL, locks all sectors. Should be at VIH for all other conditions.         |

<u>U401</u>: POWE-SIM-MANAGEMENT adopts PCF50601ET-C2?It mainly provides Baseband power supply, RF power supply, SIM interface and so on. Diagram and pin description are shown below:

Page No.:

Date:

2004-04-12

Page 32of 56

## Tuning Up procedure & Operational Manual

<u>Z3000B</u>

Model:

Vision:

Date:

Page No.:

Version 2.0

### 2004-04-12

## Tuning Up procedure & Operational Manual

Page 33of 56

| Symbol <sup>[1]</sup> | Ball | Supply         | Description/Remarks                                                                        |  |  |  |

|-----------------------|------|----------------|--------------------------------------------------------------------------------------------|--|--|--|

| Linear regulat        | tors |                |                                                                                            |  |  |  |

| RFVBAT                | G8   | 8 <u>7</u>     | Input for RF1 and RF2 linear regulators                                                    |  |  |  |

| RF1SNS                | F8   | 2              | Voltage sense input for RF1; shall be connected to<br>RF1VDD                               |  |  |  |

| RF2SNS                | H8   | 2              | Voltage sense input for RF2; shall be connected to RF2VDD                                  |  |  |  |

| RF1SWS                | E6   | DVDD1          | Output switch enable input for RF1; switches the<br>RF1VDDS on.                            |  |  |  |

| RF2SWS                | F6   | DVDD2          | Output switch enable input for RF2; switches the<br>RF2VDDS on.                            |  |  |  |

| RF1VDD                | F9   | <u>,</u>       | RF1 linear regulator 1 output voltage                                                      |  |  |  |

| RF1VDDS               | E9   | \ <del></del>  | RF1 linear regulator switched output voltage                                               |  |  |  |

| RF2VDD                | G9   | 87             | RF2 linear regulator 2 output voltage                                                      |  |  |  |

| RF2VDDS               | H9   | 17             | RF2 linear regulator switched output voltage                                               |  |  |  |

| SEL12RB               | E7   | DVDD2          | Select register B for DVDD1&2; note that this signal shall<br>be stable at start-up.       |  |  |  |

| DVDD1VBAT             | F2   | 14<br>14       | Input for DVDD1 linear regulator                                                           |  |  |  |

| DVDD1                 | F1   | 22             | DVDD1 linear regulator output voltage                                                      |  |  |  |

| DVVD2VBAT             | G2   | 3 <del>4</del> | Input for DVDD2 linear regulator                                                           |  |  |  |

| DVDD2                 | G1   | . <del>.</del> | DVDD2 linear regulator output voltage                                                      |  |  |  |

| SEL3RB                | E5   | ISUPD          | Select Control Register B for DVDD3; note that this<br>signal shall be stable at start-up. |  |  |  |

| DVDD3VBAT             | H2   | 15             | Input for DVDD3 linear regulator                                                           |  |  |  |

| DVDD3                 | H1   | 1              | DVDD3 linear regulator output voltage                                                      |  |  |  |

| DVDD4VBAT             | В4   | 22             | Input for DVDD4 linear regulator                                                           |  |  |  |

| DVDD4                 | A4   | 3 <del></del>  | DVDD4 linear regulator output voltage                                                      |  |  |  |

| DVDD4ON               | F7   | DVDD2          | Switches DVDD4 linear regulator on; pin has pull-down<br>resistor to VSS.                  |  |  |  |

| AVDDVBAT              | H7   | -              | Input for AVDD linear regulator                                                            |  |  |  |

| AVDD                  | J7   | 17             | AVDD linear regulator output voltage                                                       |  |  |  |

| AVDDS                 | G7   |                | AVDD linear regulator switched output voltage                                              |  |  |  |

| HFAVBAT               | B5   | 22             | Input for hands-free audio linear regulator                                                |  |  |  |

| HFAVDD                | A5   | 82             | Hands-free audio linear regulator output voltage                                           |  |  |  |

| VIBVBAT               | B3   | -              | Input for vibrator linear regulator                                                        |  |  |  |

| VIBVDD                | A3   | 87             | Vibrator linear regulator output voltage                                                   |  |  |  |

<u>Z3000B</u>

Model:

Vision:

Date:

Page No.:

Version 2.0

# Tuning Up procedure & Operational Manual

2004-04-12

Page 34of 56

| BLVBAT       | B6        | -     | Input for backlight linear regulator                                                                                                                                           |

|--------------|-----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLVDD        | A6        | 15    | Backlight linear regulator output voltage                                                                                                                                      |

| BBMGND       | B7        | 17    | Backlight brightness modulator ground                                                                                                                                          |

| BBMSW        | A7        | BLVDD | Backlight brightness modulator switch                                                                                                                                          |

| Control inte | rfaces    |       |                                                                                                                                                                                |

| SLPMOD       | D5        | DVDD1 | Signal switches the system to SLEEP state. At start up<br>this signal is ignored until enabled by the system<br>controller (see OOCC2 register).                               |

| ТМ           | F5        | ISUPD | Test mode selection; shall be connected to ground for<br>normal operation.                                                                                                     |

| RSTO         | D6        | DVDD1 | Active-low reset for logic supplied by DVDD1                                                                                                                                   |

| ONKEY        | F4        | ISUPD | Active Low On-key input with debouncing. Input<br>implemented as Schmitt trigger input with internal pull-up<br>resistor to ISUPD. Edge sensitive input.                       |

| AUXON        | G4        | ISUPD | Active Low Auxiliary On-Key input with 62 msec<br>debouncing. Input implemented as Schmitt trigger input<br>with internal pull-up resistor to ISUPD. Level sensitive<br>input. |

| CLK32        | B8        | DVDD1 | 32.768 kHz digital clock output; note that this output is<br>only available when system is in ACTIVE or SLEEP state<br>and DVDD1 is on.                                        |

| INT          | D7        | DVDD1 | Interrupt to system controller; this active low signal is<br>realized as an open drain output. Requires external<br>pull-up resistor.                                          |

| REC1         | J2        | DVDD2 | Accessory recognition with interrupt; these inputs have                                                                                                                        |

| REC2         | НЗ        | DVDD2 | selectable debounce filters (0, 14 or 62 ms) to prevent                                                                                                                        |

| REC3         | G3        | DVDD2 | <ul> <li>multiple interrupt generation</li> </ul>                                                                                                                              |

| 32.768 kHz o | oscillato | r:    |                                                                                                                                                                                |

| OSC32I       | J8        | ISUPA | 32.768 kHz oscillator input                                                                                                                                                    |

| 0SC32O       | J9        | ISUPA | 32.768 kHz oscillator output                                                                                                                                                   |

| Internal sup | ply       |       |                                                                                                                                                                                |

| ISUPA        | H5        | 22    | Internal supply voltage output                                                                                                                                                 |

| ISUPD        | G5        | -     | Internal supply voltage for digital logic. This pin shall be<br>connected to ISUPA.                                                                                            |

| VSAVE        | J4        | -     | Backup (auxiliary) battery                                                                                                                                                     |

| VBAT         | J3        | -     | Main battery connection for general internal usage                                                                                                                             |