# WE310F5-I/P Module Hardware User Guide

1VV0301662 Rev 9 - 2020-03-12

#### SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE

#### NOTICE

While reasonable efforts have been made to assure the accuracy of this document, Telit assumes no liability resulting from any inaccuracies or omissions in this document, or from use of the information obtained herein. The information in this document has been carefully checked and is believed to be reliable. However, no responsibility is assumed for inaccuracies or omissions. Telit reserves the right to make changes to any products described herein and reserves the right to revise this document and to make changes from time to time in content hereof with no obligation to notify any person of revisions or changes. Telit does not assume any liability arising out of the application or use of any product, software, or circuit described herein; neither does it convey license under its patent rights or the rights of others.

It is possible that this publication may contain references to, or information about Telit products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that Telit intends to announce such Telit products, programming, or services in your country.

#### **COPYRIGHTS**

This instruction manual and the Telit products described in this instruction manual may be, include or describe copyrighted Telit material, such as computer programs stored in semiconductor memories or other media. Laws in the Italy and other countries preserve for Telit and its licensors certain exclusive rights for copyrighted material, including the exclusive right to copy, reproduce in any form, distribute and make derivative works of the copyrighted material. Accordingly, any copyrighted material of Telit and its licensors contained herein or in the Telit products described in this instruction manual may not be copied, reproduced, distributed, merged or modified in any manner without the express written permission of Telit. Furthermore, the purchase of Telit products shall not be deemed to grant either directly or by implication, estoppel, or otherwise, any license under the copyrights, patents or patent applications of Telit, as arises by operation of law in the sale of a product.

#### COMPUTER SOFTWARE COPYRIGHTS

The Telit and 3rd Party supplied Software (SW) products described in this instruction manual may include copyrighted Telit and other 3rd Party supplied computer programs stored in semiconductor memories or other media. Laws in the Italy and other countries preserve for Telit and other 3rd Party supplied SW certain exclusive rights for copyrighted computer programs, including the exclusive right to copy or reproduce in any form the copyrighted computer program. Accordingly, any copyrighted Telit or other 3rd Party supplied SW computer programs contained in the Telit products described in this instruction manual may not be copied (reverse engineered) or reproduced in any manner without the express written permission of Telit or the 3rd Party SW supplier. Furthermore, the purchase of Telit products shall not be deemed to grant either directly or by implication, estoppel, or otherwise, any license under the copyrights, patents or patent applications of Telit or other 3rd Party supplied SW, except for the normal non-exclusive, royalty free license to use that arises by operation of law in the sale of a product.

#### **USAGE AND DISCLOSURE RESTRICTIONS**

#### I. License Agreements

The software described in this document is the property of Telit and its licensors. It is furnished by express license agreement only and may be used only in accordance with the terms of such an agreement.

#### II. Copyrighted Materials

Software and documentation are copyrighted materials. Making unauthorized copies is prohibited by law. No part of the software or documentation may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, without prior written permission of Telit

#### III. High Risk Materials

Components, units, or third-party products used in the product described herein are NOT fault-tolerant and are NOT designed, manufactured, or intended for use as on-line control equipment in the following hazardous environments requiring fail-safe controls: the operation of Nuclear Facilities, Aircraft Navigation or Aircraft Communication Systems, Air Traffic Control, Life Support, or Weapons Systems (High Risk Activities"). Telit and its supplier(s) specifically disclaim any expressed or implied warranty of fitness for such High Risk Activities.

#### IV. Trademarks

TELIT and the Stylized T Logo are registered in Trademark Office. All other product or service names are the property of their respective owners.

#### V. Third Party Rights

The software may include Third Party Right software. In this case you agree to comply with all terms and conditions imposed on you in respect of such separate software. In addition to Third Party Terms, the disclaimer of warranty and limitation of liability provisions in this License shall apply to the Third Party Right software.

TELIT HEREBY DISCLAIMS ANY AND ALL WARRANTIES EXPRESS OR IMPLIED FROM ANY THIRD PARTIES REGARDING ANY SEPARATE FILES, ANY THIRD PARTY MATERIALS INCLUDED IN THE SOFTWARE, ANY THIRD PARTY MATERIALS FROM WHICH THE SOFTWARE IS DERIVED (COLLECTIVELY "OTHER CODE"), AND THE USE OF ANY OR ALL THE OTHER CODE IN CONNECTION WITH THE SOFTWARE, INCLUDING (WITHOUT LIMITATION) ANY WARRANTIES OF SATISFACTORY QUALITY OR FITNESS FOR A PARTICULAR PURPOSE.

NO THIRD PARTY LICENSORS OF OTHER CODE SHALL HAVE ANY LIABILITY FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING WITHOUT LIMITATION LOST PROFITS), HOWEVER CAUSED AND WHETHER MADE UNDER CONTRACT, TORT OR OTHER LEGAL THEORY, ARISING IN ANY WAY OUT OF THE USE OR DISTRIBUTION OF THE OTHER CODE OR THE EXERCISE OF ANY RIGHTS GRANTED UNDER EITHER OR BOTH THIS LICENSE AND THE LEGAL TERMS APPLICABLE TO ANY SEPARATE FILES, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **APPLICABILITY TABLE**

#### **PRODUCTS**

- ■ WE310F5-I

- ■ WE310F5-P

# Contents

| NOTICE                        |                                 |  |  |  |

|-------------------------------|---------------------------------|--|--|--|

| COPYRIGHTS2                   |                                 |  |  |  |

| COMPUTER SOFTWARE COPYRIGHTS2 |                                 |  |  |  |

| USAGE AN                      | ND DISCLOSURE RESTRICTIONS      |  |  |  |

| CONTENT                       | S5                              |  |  |  |

| FIGURE LI                     | ST7                             |  |  |  |

| TABLE LIS                     | 8T8                             |  |  |  |

| 1.                            | INTRODUCTION                    |  |  |  |

| 1.1.                          | Scope                           |  |  |  |

| 1.2.                          | Audience9                       |  |  |  |

| 1.3.                          | Contact Information, Support    |  |  |  |

| 1.4.                          | Text Conventions                |  |  |  |

| 1.5.                          | Related Documents               |  |  |  |

| 2.                            | PRODUCT DESCRIPTION11           |  |  |  |

| 2.1.                          | Overview                        |  |  |  |

| 2.2.                          | Block Diagram                   |  |  |  |

| 3.                            | FEATURES                        |  |  |  |

| 3.1.                          | Main Features                   |  |  |  |

| 3.2.                          | Bootloader                      |  |  |  |

| 3.3.                          | ESD Characteristics             |  |  |  |

| 3.4.                          | SAR ADC Characteristics         |  |  |  |

| 4.                            | PINS ALLOCATION                 |  |  |  |

| 4.1.                          | Pin-out                         |  |  |  |

| 5.                            | POWER SUPPLY                    |  |  |  |

| 5.1.                          | Power Supply Requirements       |  |  |  |

| 5.2.                          | Logic Levels                    |  |  |  |

| 5.3.                          | Power Up and Shutdown Sequences |  |  |  |

| 6.                            | RF SPECIFICATION                |  |  |  |

| 6.1.                          | Wi-Fi Tx Power                  |  |  |  |

| 6.2.   | BLE Tx Power                              | 26 |

|--------|-------------------------------------------|----|

| 6.3.   | Wi-Fi Rx Sensitivity                      | 26 |

| 6.4.   | BLE Rx Sensitivity                        | 27 |

| 6.5.   | General Purpose I/O                       | 28 |

| 6.6.   | Power Consumption                         | 28 |

| 6.6.1. | Power Consumption                         | 28 |

| 6.6.2. | WLAN Continuous Tx Power consumption      | 29 |

| 6.7.   | Pads Layout                               | 30 |

| 7.     | DESIGN GUIDELINES                         | 33 |

| 7.1.   | General Digital Interface Recommendations | 33 |

| 7.2.   | Power supply design guidelines            | 34 |

| 7.3.   | Bypass Capacitors                         | 34 |

| 7.4.   | Antenna Guidelines                        | 35 |

| 7.5.   | Audio considerations                      | 38 |

| 7.6.   | Other General Design Considerations       | 38 |

| 8.     | MECHANICAL DESIGN                         | 41 |

| 8.1.   | WE310F5-I                                 | 41 |

| 8.2.   | WE310F5-P                                 | 43 |

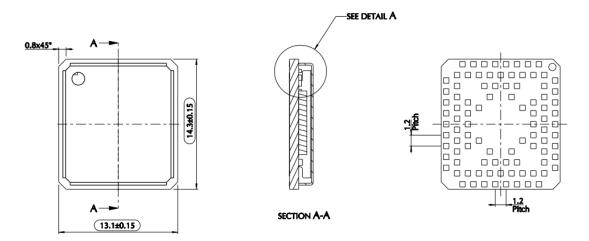

| 8.3.   | PCB Pad Design                            | 44 |

| 8.4.   | PCB Pad Dimensions                        | 45 |

| 8.5.   | Stencil                                   | 45 |

| 8.6.   | Solder Paste                              | 45 |

| 8.7.   | Solder Reflow                             | 46 |

| 9.     | PACKAGING                                 | 48 |

| 9.1.   | Tray                                      | 48 |

| 9.2.   | Moisture Sensitivity                      | 49 |

| 10.    | CONFORMITY ASSESSMENT ISSUES              | 50 |

| 10.1.  | FCC/IC Regulatory Notices                 | 50 |

| 11.    | FCC/IC COMPLIANCE                         | 51 |

| 12.    | SAFETY RECOMMENDATIONS                    | 54 |

| 12.1.  | Read Carefully                            |    |

| 13.    | ACRONYMS                                  | 55 |

| 14.    | DOCUMENT HISTORY                          | 57 |

# FIGURE LIST

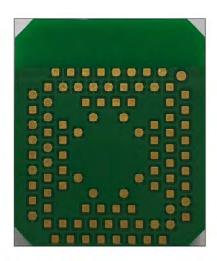

| Figure 1: WE310F5-I 15mm*18mm                                                                         | 11 |

|-------------------------------------------------------------------------------------------------------|----|

| Figure 2: WE310F5-P 13.1mm*14.3mm                                                                     | 11 |

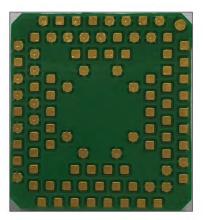

| Figure 3: WE310F5-I/P Block Diagram1                                                                  | 13 |

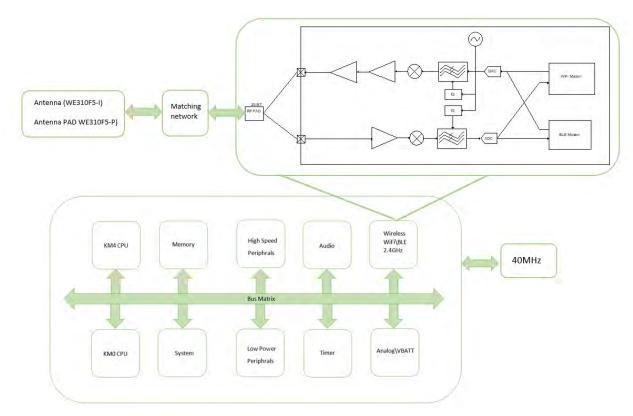

| Figure 4: Power UP Sequence2                                                                          | 24 |

| Figure 5: Shutdown Sequence                                                                           | 24 |

| Figure 6: Pads Layout Top View – WE310F5-I                                                            | 31 |

| Figure 7: Pads Layout Top View – WE310F5-P                                                            | 32 |

| Figure 8: Pinout Legend Color                                                                         | 32 |

| Figure 9: EMI Filter Example                                                                          | 34 |

| Figure 10: WE310F5-I Placement Example                                                                | 35 |

| Figure 11: WE310F5-I Placement Example showing no copper in any layer of the board                    |    |

| Figure 12: WE310F5-P Placement Example                                                                | 36 |

| Figure 13: RF Track Example                                                                           | 37 |

| Figure 14: Coplanar Waveguide Dimensioning Example                                                    | 37 |

| Figure 15: Minimal RF Matching Network Circuitry                                                      | 38 |

| Figure 16: Layout Example for FAST Digital Lines                                                      | 39 |

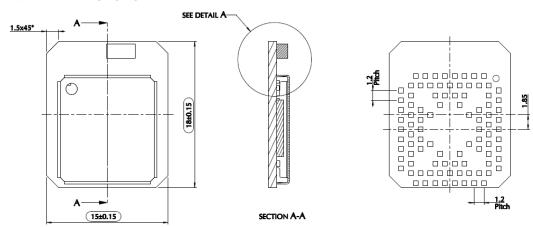

| Figure 17: WE310F5-I mechanical design                                                                | 41 |

| Figure 18: WE310F5-I Side View detail                                                                 | 41 |

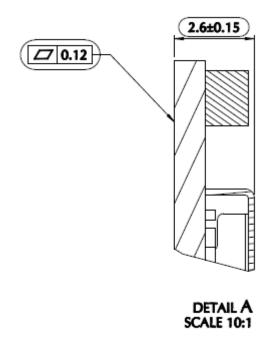

| Figure 19: WE310F5-I Bottom View                                                                      | 12 |

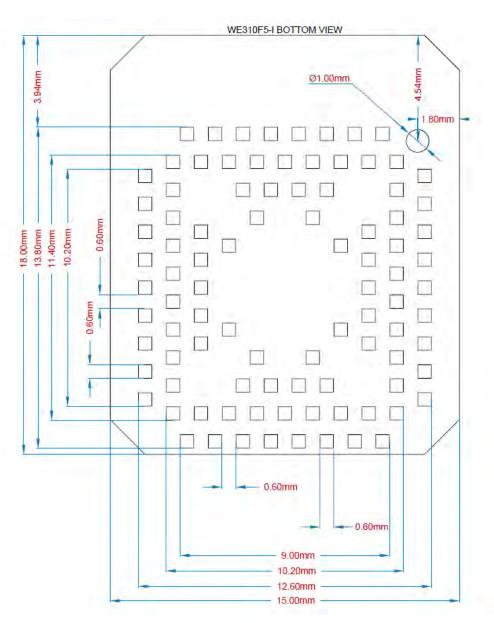

| Figure 20: WE310F5-P mechanical design                                                                | 43 |

| Figure 21: WE310F5-P side view detail                                                                 | 43 |

| Figure 22: WE310F5-P Bottom View                                                                      | 14 |

| Figure 23: SMD and NSMD Pad                                                                           | 14 |

| Figure 24: Inhibit Area for Not Solder Covered Vias                                                   | 45 |

| Figure 25: Solder Reflow Profile                                                                      | 46 |

| Figure 26: WE310F5-I/P Packaging example (to replace with the final one and add the WE310F5-P figure) |    |

# TABLE LIST

| Table 1: Feature Description Table                           | 14 |

|--------------------------------------------------------------|----|

| Table 2: Peripherals Interfaces                              | 15 |

| Table 3: ESD Characteristics of WE310F5-I/P modules          | 16 |

| Table 4: SAR ADC characteristics                             | 16 |

| Table 5: Pinout Table                                        | 22 |

| Table 6: Power Supply requirements                           | 23 |

| Table 7: Input/output Levels                                 | 23 |

| Table 8: Timing Specification of -Power up/shutdown sequence | 24 |

| Table 9: WLAN Tx power                                       | 26 |

| Table 10: BLE Tx Power                                       | 26 |

| Table 11: Wi-Fi Rx Sensitivity                               | 27 |

| Table 12: BLE Rx Sensitivity                                 | 27 |

| Table 13: GPIO Pinmux Table                                  | 28 |

| Table 14: Module power consumption in different states       | 28 |

| Table 15: WLAN Tx Power Consumption                          | 30 |

| Table 16: PCB Finishing Recommendation                       | 45 |

| Table 17: Recommended Solder Paste Type                      | 45 |

| Table 18: Solder Reflow Table                                | 47 |

#### 1. INTRODUCTION

#### 1.1. Scope

The aim of this document is to describe some of the hardware solutions useful for developing a product with the Telit WE310F5-I/P Wi-Fi/BLE module.

#### 1.2. Audience

This document is intended for Telit customers, who are integrators, about to implement their applications using our WE310F5-I/P modules.

## 1.3. Contact Information, Support

For general contact, technical support services, technical questions and report documentation errors contact Telit Technical Support at:

- TS-EMEA@telit.com

- TS-AMERICAS@telit.com

- TS-APAC@telit.com

- TS-SRD@telit.com

Alternatively, use:

#### http://www.telit.com/support

For detailed information about where you can buy the Telit modules or for recommendations on accessories and components visit:

#### http://www.telit.com

Our aim is to make this guide as helpful as possible. Keep us informed of your comments and suggestions for improvements.

Telit appreciates feedback from the users of our information.

#### 1.4. Text Conventions

Danger – This information MUST be followed, or catastrophic equipment failure or bodily injury may occur.

Caution or Warning – Alerts the user to important points about integrating the module, if these points are not followed, the module and end user equipment may fail or malfunction.

Tip or Information – Provides advice and suggestions that may be useful when integrating the module.

All dates are in ISO 8601 format, i.e. 2019-01-08.

#### 1.5. Related Documents

- WE310F5-I/P AT Command Reference Guide

- WE310F5-I/P EVB Hardware User Guide

#### 2. PRODUCT DESCRIPTION

#### 2.1. Overview

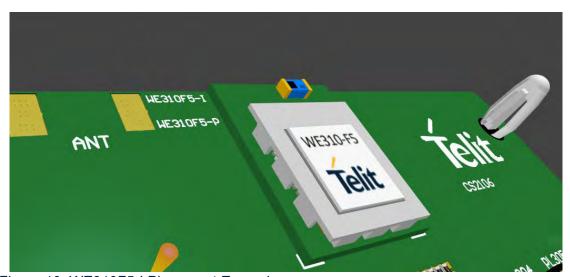

The WE310F5-I/P is a module with single band Wi-Fi/BLE (5.0) 2.4GHz combo module that provides an easy and cost-effective way to the users to add wireless connectivity to their products. This module is available in two different from factors the antenna version named WE310F5-I with 15mmx18mm dimensions and an on-board multilayer antenna and the WE310F5-P with 13.1mmX14.3mm with antenna PAD. The two versions share the same Pinout and are P2P compatible.

The following figure shows the WE310F5-I and WE310F5-P

Figure 1: WE310F5-I 15mm\*18mm

Figure 2: WE310F5-P 13.1mm\*14.3mm

#### NOTE:

- (EN) The integration of the WE310F5-I/P module within user application shall be done according to the design rules described in this manual.

- (IT) L'integrazione del modulo cellulare WE310F5-I/P all'interno dell'applicazione dell'utente dovrà rispettare le indicazioni progettuali descritte in questo manuale.

- (DE) Die Integration des WE310F5-I/P Mobilfunk-Moduls in ein Gerät muß gemäß der in diesem Dokument beschriebenen Kunstruktionsregeln erfolgen.

- (SL) Integracija WE310F5-I/P modula v uporabniški aplikaciji bo morala upoštevati projektna navodila, opisana v tem priročniku.

- (SP) La utilización del modulo WE310F5-I/P debe ser conforme a los usos para los cuales ha sido deseñado descritos en este manual del usuario.

- (FR) L'intégration du module cellulaire WE310F5-I/P dans l'application de l'utilisateur sera faite selon les règles de conception décrites dans ce manuel.

- (HE) האינטגרטור מתבקש ליישם את ההנחיות המפורטות במסמך זה בתהליך האינטגרציה של המודם הסלולרי WE310F5-I/P

# 2.2. Block Diagram

The following figure shows a high-level block diagram of WE310F5-I/P module and its major functional blocks

Figure 3: WE310F5-I/P Block Diagram

#### 3. FEATURES

#### 3.1. Main Features

- 1. Highly integrated single chip with low power single band (2.4GHz) Wireless LAN (WLAN) and Bluetooth Low Energy (BLE5.0) communication controller.

- 2. Dedicated ArmV8-M Cortex-M33 (KM4) processor + low power Armv8-M Cortex-M23 (KM0) WLAN (802.11 b/g/n) MAC, an 1T1R capable WLAN, and Bluetooth.

- 3. FLASH Memory 4Mbytes(32Mbits)

- 4. 456Kb RAM

- 5. Retention SRAM 156Kb

| Item                   | Description                                                                                                           |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|

| WiFi                   | 802.11 b/g/n 1X1 2.4GHz                                                                                               |

|                        | 20MHz/40MHz Channel width                                                                                             |

|                        | Data rates up to MCS7                                                                                                 |

|                        | Low power architecture                                                                                                |

|                        | Low Power Tx/Rx for short range application                                                                           |

|                        | Low Power beacon listen mode                                                                                          |

|                        | Low power Rx mode                                                                                                     |

|                        | Very low power suspend mode (DLPS)                                                                                    |

|                        | Built-in PA                                                                                                           |

|                        | Internal PTA interface for arbitrating data transmission between WiFi and Internal Bluetooth or external 2.4G devices |

| BT BLE                 | BLE 5.0                                                                                                               |

|                        | Both central and peripheral modes                                                                                     |

|                        | High power mode (8dBm, shares the same PA with WiFi)                                                                  |

|                        | Internal Co-existence mechanism between Wi-Fi and BT to share the same antenna                                        |

| Temperature            | Operating: -40°C ~ 85°C                                                                                               |

| Range                  | Junction: -40°C ~ 105°C                                                                                               |

|                        | Storage: -55°C ~ 125°C                                                                                                |

| <br>Table 1: Feature [ | Describetion Tolds                                                                                                    |

Table 1: Feature Description Table

The WE310F5-I/P module supports the following peripherals Interfaces.

| Item             | Peripherals         | Comment                                                      |

|------------------|---------------------|--------------------------------------------------------------|

| UART             | UART0               | Low Power Mode Wakeup                                        |

|                  | AUX_UART            | LOG UART/Low power mode wakeup (no Flow control))            |

| SPI              | SPI0                | Master/Slave Clock up to 50 MHz                              |

| I <sup>2</sup> C | HS_I <sup>2</sup> C | Standard/fast/high speed mode (up to 3.33Mbps)               |

| SDIO             | 1-Bit SDIO mode     | Maximum Clock 50 MHz                                         |

| PWM              | HS_PWM8/            |                                                              |

|                  | LP_PWM2             |                                                              |

| DVI              | I <sup>2</sup> S    | Sampling rates: 8kHz ~ 176.4kHz                              |

|                  |                     | Mono, stereo, and 5.1 channel.                               |

|                  |                     | Sample size for Mono: 16-bit, 32-bit                         |

|                  |                     | Sample size for Stereo & 5.1 channel: 16-bit, 24-bit 32 bit. |

|                  |                     | PCM not supported                                            |

| WAKEUP           |                     | Wake up from deep sleep                                      |

| USB              |                     | USB 2.0 device                                               |

| ADC              | 12-bit SAR ADC      | Single ended input                                           |

|                  |                     | Range: 0~3.3V                                                |

| RTC              |                     | 12- or 24-hour format (seconds, minutes, hours, days)        |

|                  |                     | Daylight saving compensation                                 |

|                  |                     | Register write protection                                    |

|                  |                     |                                                              |

Table 2: Peripherals Interfaces

#### 3.2. Bootloader

The bootloader sits in internal NOR flash. The firmware can be flashed only through AUX\_UART. To program the firmware to module, TX\_AUX (pin Y10) must be LOW before power on or reset.

#### 3.3. ESD Characteristics

The ESD characteristics of the WE310F5-I/P modules are showed in the table 7

| ESD                    | V     |

|------------------------|-------|

| Human Body Model (HBM) | ±2000 |

| Charge Device Model    | ± 500 |

Table 3: ESD Characteristics of WE310F5-I/P modules

#### 3.4. SAR ADC Characteristics

The SAR ADC characteristics of WE310F5-I/P modules are shown in table 8

| Parameter       | Condition                | Minimum | Typical | Maximum | Unit |

|-----------------|--------------------------|---------|---------|---------|------|

| Temperature     |                          | -40     | 25      | 125     | C°   |

| Donald from     | Bypass mode              |         | 12      |         | Bits |

| Resolution      | Resistor driver mode     |         | 12      |         | Bits |

| Clock Source    | From digital             |         |         | 1000    | kHz  |

| DC Offset Error | Cover<br>VBAT=1.62~3.63V |         | 2       |         | LSB  |

Table 4: SAR ADC characteristics

# 4. PINS ALLOCATION

#### 4.1. Pin-out

All IO's are in LVTTL 3.3V logic.

| Pin     | Signal                | I/O    | Function                                        | Comment | Pull-down<br>Restriction |  |

|---------|-----------------------|--------|-------------------------------------------------|---------|--------------------------|--|

| Primar  | y serial port (HW     | / Flow | Control)                                        |         |                          |  |

| Y16     | RXD0                  | I      | Serial data output (RXD) to DTE                 |         | >1K                      |  |

| AA15    | TXD0                  | 0      | Serial data input (TXD) from DTE                |         | >1K                      |  |

| Y18     | CTS0                  | I      | Output for Clear to send signal (CTS) to DTE    |         | >1K                      |  |

| AA17    | RTS0                  | 0      | Input for Request to send signal (RTS) from DTE |         | >1K                      |  |

| USB     |                       |        |                                                 |         |                          |  |

| U19     | USB_D+                | I/O    | USB differential Data (+)                       |         | >1K                      |  |

| V18     | USB_D-                | I/O    | USB differential Data (-)                       |         | >1K                      |  |

| Auxilia | Auxiliary Serial Port |        |                                                 |         |                          |  |

| Y10     | TX_AUX                | 0      | Auxiliary DEBUG UART (TX<br>Data to DTE)        |         | >1K                      |  |

| AA9     | RX_AUX                | I      | Auxiliary DEBUG UART (RX<br>Data to DTE)        |         | >1K                      |  |

| DIGITA  | DIGITAL IO            |        |                                                 |         |                          |  |

| D9      | IO4/SD_CLK         | I/O | Configurable GPIO_04              | I2S_MCLK   |     |

|---------|--------------------|-----|-----------------------------------|------------|-----|

| D11     | IO5/SD_D0          | I/O | Configurable GPIO_05              |            |     |

| D13     | 106                | I/O | Configurable GPIO_06              |            |     |

| SPI     |                    |     |                                   |            |     |

| AA5     | SPI_MOSI           | I/O | MOSI                              |            |     |

| Y6      | SPI_CS             | I/O | Chip Select                       |            | >1K |

| AA7     | SPI_CLK            | I/O | Clock                             |            | >1K |

| Y8      | SPI_MISO           | I/O | MISO                              |            | >1K |

| ADC a   | nd DAC             |     |                                   |            |     |

| B18     | ADC                | 1   | Analog to Digital Converter Input | 0V ~ 3.3V  | >1K |

| R16     | DAC                | 0   | PWM output                        |            |     |

| RF      |                    |     |                                   |            |     |

| A5      | WIFI/BT<br>ANTENNA | I/O | RF pad (50 ohm) on P variant      |            |     |

| Miscell | laneous            |     |                                   |            |     |

| N16     | ON*                | I   | RESET pin                         | Active low |     |

|         |                    |     |                                   |            |     |

| Audio     |           |   |                        |       |

|-----------|-----------|---|------------------------|-------|

| C1        | DVI_WA0   | 0 | I2S Frame Sync         |       |

| D2        | DVI_RX    | 0 | I2S RX                 |       |

| E1        | DVI_TX    | I | I2S TX                 |       |

| F2        | DVI_CLK   | I | I2S CLK                |       |

| Power     | Supply    |   |                        |       |

| W1        | VBATT_3V3 | - | Main power supply 3.3V | Power |

| AA3       | VBATT_3V3 | - | Main power supply 3.3V | Power |

| A3        | GND       | - | RF Ground              | Power |

| <b>A7</b> | GND       | - | RF Ground              | Power |

| A9        | GND       | - | RF Ground              | Power |

| A13       | GND       | - | RF Ground              | Power |

| A17       | GND       | - | RF Ground              | Power |

| B4        | GND       | - | RF Ground              | Power |

| В6        | GND       | - | RF Ground              | Power |

| B10       | GND       | - | RF Ground              | Power |

| B12       | GND       | - | RF Ground              | Power |

| B14       | GND       | - | RF Ground              | Power |

| B16       | GND       | - | RF Ground              | Power |

| C19       | GND       | - | RF Ground              | Power |

| D18 | GND   | _ | RF Ground      | Power |

|-----|-------|---|----------------|-------|

|     | 0.115 |   |                |       |

| F8  | GND   | - | Thermal Ground | Power |

| F12 | GND   | - | Thermal Ground | Power |

| F18 | GND   | - | Thermal Ground | Power |

| G19 | GND   | - | Thermal Ground | Power |

| Н6  | GND   | - | Thermal Ground | Power |

| H14 | GND   | - | Thermal Ground | Power |

| J19 | GND   | - | Thermal Ground | Power |

| K18 | GND   | - | Thermal Ground | Power |

| M18 | GND   | - | Thermal Ground | Power |

| N19 | GND   | - | Thermal Ground | Power |

| P6  | GND   | - | Thermal Ground | Power |

| P14 | GND   | - | Thermal Ground | Power |

| Т8  | GND   | - | Thermal Ground | Power |

| T12 | GND   | - | Thermal Ground | Power |

| U1  | GND   | - | Power Ground   | Power |

| V2  | GND   | - | Power Ground   | Power |

| W19 | GND   | - | Power Ground   | Power |

| Y2  | GND   | - | Power Ground   | Power |

| Y4  | GND   | - | Power Ground   | Power |

|     |       |   |                |       |

| Debug | Debug Port (SWD) |   |          |                                  |  |  |

|-------|------------------|---|----------|----------------------------------|--|--|

| J4    | SWD_CLK          |   | SWD_CLK  |                                  |  |  |

| L4    | SWD_DATA         |   | SWD_DATA | Bootstrap<br>pin. LOW for<br>SWD |  |  |

| RESE  | RVED             |   |          |                                  |  |  |

| A1    | RESERVED         | - | RESERVED |                                  |  |  |

| A11   | RESERVED         | - | RESERVED |                                  |  |  |

| A15   | RESERVED         | - | RESERVED |                                  |  |  |

| B2    | RESERVED         | - | RESERVED |                                  |  |  |

| В8    | RESERVED         | - | RESERVED |                                  |  |  |

| E19   | RESERVED         | - | RESERVED |                                  |  |  |

| G1    | RESERVED         | - | RESERVED |                                  |  |  |

| G4    | RESERVED         | - | RESERVED |                                  |  |  |

| G16   | RESERVED         | - | RESERVED |                                  |  |  |

| H2    | RESERVED         | - | RESERVED |                                  |  |  |

| H18   | RESERVED         | - | RESERVED |                                  |  |  |

| J1    | RESERVED         | - | RESERVED |                                  |  |  |

| J16   | RESERVED         | - | RESERVED |                                  |  |  |

| K2    | RESERVED         | - | RESERVED |                                  |  |  |

| L1    | RESERVED         | - | RESERVED |                                  |  |  |

|       |                  |   |          |                                  |  |  |

| L19         | RESERVED | - | RESERVED |

|-------------|----------|---|----------|

| M2          | RESERVED | - | RESERVED |

| N1          | RESERVED | - | RESERVED |

| N4          | RESERVED | - | RESERVED |

| P2          | RESERVED | - | RESERVED |

| P18         | RESERVED | - | RESERVED |

| R1          | RESERVED | - | RESERVED |

| R4          | RESERVED | - | RESERVED |

| R19         | RESERVED | - | RESERVED |

| Т2          | RESERVED | - | RESERVED |

| T18         | RESERVED | - | RESERVED |

| <b>V</b> 7  | RESERVED | - | RESERVED |

| V9          | RESERVED | - | RESERVED |

| Y12         | RESERVED | - | RESERVED |

| Y14         | RESERVED | - | RESERVED |

| <b>AA11</b> | RESERVED | - | RESERVED |

|             | RESERVED |   | RESERVED |

Table 5: Pinout Table

Note: Reserved Pins must not be connected.

# 5. POWER SUPPLY

#### 5.1. Power Supply Requirements

The WE310F5-I/P can be directly supplied by a 3.3V power supply source capable of at least 500mA or higher.

The voltage supply to all the required parts of the chipset is provided by an embedded switching regulator.

| Power Supply       | Minimum | Typical | Maximum |

|--------------------|---------|---------|---------|

| Main Power ratings | 3.0 V   | 3.3V    | 3.6 V   |

Table 6: Power Supply requirements

# 5.2. Logic Levels

| Levels with VIO = 3.3V                     | Min   | Typical | Max   |

|--------------------------------------------|-------|---------|-------|

| V <sub>IH</sub> Input high level           | 2.0V  | -       | -     |

| V <sub>IL</sub> Input low level            | -     | -       | 0.8V  |

| V <sub>OH</sub> Output high level          | 2.4V  | -       | -     |

| V <sub>OL</sub> Output low level           | -     | -       | 0.4V  |

| I <sub>T+</sub> Schmitt-trigger High Level | 1.78V | 1.87V   | 1.97V |

| I <sub>T-</sub> Schmitt-trigger Low Level  | 1.36V | 1.45V   | 1.56V |

| I <sub>LL</sub> input-Leakage Current      | -10μΑ | +/-1μΑ  | 10μΑ  |

Table 7: Input/output Levels

# 5.3. Power Up and Shutdown Sequences

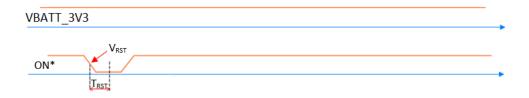

Module power up and shutdown sequences are shown below:

Figure 4: Power UP Sequence

Figure 5: Shutdown Sequence

| Symbol            | Parameter                                               | Minimum | Typical | Maximum       | Unit |

|-------------------|---------------------------------------------------------|---------|---------|---------------|------|

| T <sub>PRDY</sub> | VDD_IO ready time                                       | 0.6     | 0.6     | 1             | ms   |

| Vrst              | Shutdown occurs<br>after ON* lower<br>than this voltage | 0       | 0       | 0.5*VBATT_3V3 | V    |

| T <sub>RST</sub>  | The required time when ON* lower than V <sub>RST</sub>  | 10      | 10      | -             | μS   |

Table 8: Timing Specification of -Power up/shutdown sequence

# 6. RF SPECIFICATION

# 6.1. Wi-Fi Tx Power

Wi-Fi Transmit power at RF pad at 25 °C @3.3V.

| Wi-Fi CH 6<br>WE310F5-I/P* | Modulation | Data Rates | RF Output (dBm) |

|----------------------------|------------|------------|-----------------|

|                            | BPSK       | 1 Mbps     | 18.0            |

|                            | QPSK       |            |                 |

| b                          |            | 2 Mbps     | 18.0            |

|                            | CCK        | 5.5 Mbps   | 18.0            |

|                            | CCK        | 11 Mbps    | 18.0            |

|                            | BPSK       | 6 Mbps     | 18.0            |

|                            | BPSK       | 9 Mbps     | 17.0            |

|                            | QPSK       | 12 Mbps    | 17.0            |

| g                          | QPSK       | 18 Mbps    | 16.5            |

|                            | 16 QAM     | 24 Mbps    | 16.5            |

|                            | 16 QAM     | 36 Mbps    | 16.0            |

|                            | 64 QAM     | 48 Mbps    | 16.0            |

|                            | 64 QAM     | 54 Mbps    | 16.0            |

|                            | BPSK       | MCS0_20    | 17.0            |

|                            | QPSK       | MCS1_20    | 16.0            |

|                            | QPSK       | MCS2_20    | 16.0            |

|                            | 16 QAM     | MCS3_20    | 15.5            |

| n                          | 16 QAM     | MCS4_20    | 15.5            |

|                            | 64 QAM     | MCS5_20    | 15.0            |

|                            | 64 QAM     | MCS6_20    | 15.0            |

|                            | 64 QAM     | MCS7_20    | 15.0            |

|                            | BPSK       | MCS0_40    | 16.0            |

| n                          | QPSK       | MCS1_40    | 15.0            |

| Wi-Fi CH 6   | Modulation | Data Rates | RF Output (dBm) |

|--------------|------------|------------|-----------------|

| WE310F5-I/P* |            |            |                 |

|              | QPSK       | MCS2_40    | 15.0            |

|              | 16 QAM     | MCS3_40    | 14.5            |

|              | 16 QAM     | MCS4_40    | 14.5            |

|              | 64 QAM     | MCS5_40    | 14.0            |

|              | 64 QAM     | MCS6_40    | 14.0            |

|              | 64 QAM     | MCS7_40    | 14.0            |

Table 9: WLAN Tx power

#### 6.2. BLE Tx Power

BLE transmit power with at RF Pad at 25 °C.

| Packet Type | Output Power (dBm) |

|-------------|--------------------|

| LE 1M       | 8                  |

| LE 2M       | 8                  |

Table 10: BLE Tx Power

# 6.3. Wi-Fi Rx Sensitivity

Wi-Fi Rx sensitivity at RF pad @ 25 °C.

| Wi-Fi (CH 6) | Modulation | Data Rates | Sensibility<br>(dBm) |

|--------------|------------|------------|----------------------|

|              | BPSK       | 1 Mbps     | -97                  |

| b            | QPSK       | 2 Mbps     | -93                  |

|              | ССК        | 5.5 Mbps   | -92                  |

|              | CCK        | 11 Mbps    | -89                  |

<sup>\*</sup> For P version remove the antenna and apply a pigtail to the hot pad.

<sup>\*</sup> For P version remove the antenna and apply a pigtail to the hot pad.

| Wi-Fi (CH 6) | Modulation | Data Rates | Sensibility |

|--------------|------------|------------|-------------|

|              |            |            | (dBm)       |

|              | BPSK       | 6 Mbps     | -92         |

|              | BPSK       | 9 Mbps     | -91         |

|              | QPSK       | 12 Mbps    | -90         |

| a a          | QPSK       | 18 Mbps    | -87         |

| g            | 16 QAM     | 24 Mbps    | -84         |

|              | 16 QAM     | 36 Mbps    | -81         |

|              | 64 QAM     | 48 Mbps    | -76         |

|              | 64 QAM     | 54 Mbps    | -75         |

|              | BPSK       | MCS0_20    | -92         |

|              | QPSK       | MCS1_20    | -89         |

|              | QPSK       | MCS2_20    | -87         |

| n            | 16 QAM     | MCS3_20    | -84         |

|              | 16 QAM     | MCS4_20    | -80         |

|              | 64 QAM     | MCS5_20    | -76         |

|              | 64 QAM     | MCS6_20    | -74         |

|              | 64 QAM     | MCS7_20    | -72         |

Table 11: Wi-Fi Rx Sensitivity

# 6.4. BLE Rx Sensitivity

BLE Rx sensitivity tested at RF pad @ 25 °C.

| Packet Type | Rx sensibility (dBm) |

|-------------|----------------------|

| LE 1M       | -97                  |

| LE 2M       | -95                  |

Table 12: BLE Rx Sensitivity

# 6.5. General Purpose I/O

The module has 6 GPIO's which can be configured as Input/output. They also have Alternate Functions.

| GPIO<br>Number | Alternate Function1 | Alternate Function2 - 1bit mode SDIO |

|----------------|---------------------|--------------------------------------|

| IO1            | I2C_SCL (I2C Clock) | SD_CMD (SD Command)                  |

| 102            | I2C_SDA (I2C Data)  | SD_CLK (SD Clock)                    |

| IO3            |                     | SD_D0 (SD Data 0)                    |

| 104            | I2S_MCLK (I2S MCLK) |                                      |

| 105            |                     |                                      |

| 106            |                     |                                      |

Table 13: GPIO Pinmux Table

#### 6.6. Power Consumption

# 6.6.1. Power Consumption

| Power Consumption                         | Typical Average (mA) |

|-------------------------------------------|----------------------|

| Standby                                   | 0,02                 |

| Idle (Radio OFF, UART ON)                 | 14,3                 |

| Deep Sleep (Radio OFF)                    | 1,43                 |

| DTIM=1                                    | 1,15                 |

| DTIM=3                                    | 0,597                |

| DTIM=10                                   | 0,203                |

| BLE RX (peak current, connected to BT NW) | 53                   |

| BLE TX (at 8dBm Tx @1Mbps)                | 109                  |

| Wi-Fi RX (continuous)                     | 58                   |

Table 14: Module power consumption in different states

# 6.6.2. WLAN Continuous Tx Power consumption

| Wi-Fi 2G4 / CH 6 | Modulation | Data Rates | RF Output | Current |

|------------------|------------|------------|-----------|---------|

| Standard 802.11x |            |            | (dBm)     | mA@3.3V |

| b                | BPSK       | 1 Mbps     | 18.0      | 265     |

| b                | QPSK       | 2 Mbps     | 18.0      | 261     |

| b                | CCK        | 5.5 Mbps   | 18.0      | 256     |

| b                | CCK        | 11 Mbps    | 18.0      | 248     |

| g                | BPSK       | 6 Mbps     | 18.0      | 245     |

| g                | BPSK       | 9 Mbps     | 17.0      | 239     |

| g                | QPSK       | 12 Mbps    | 17.0      | 225     |

| g                | QPSK       | 18 Mbps    | 16.5      | 212     |

| g                | 16 QAM     | 24 Mbps    | 16.5      | 205     |

| g                | 16 QAM     | 36 Mbps    | 16.0      | 185     |

| g                | 64 QAM     | 48 Mbps    | 16.0      | 177     |

| g                | 64 QAM     | 54 Mbps    | 16.0      | 173     |

| n                | BPSK       | MCS0_20    | 17.0      | 231     |

| n                | QPSK       | MCS1_20    | 16.0      | 209     |

| n                | QPSK       | MCS2_20    | 17.0      | 201     |

| n                | 16 QAM     | MCS3_20    | 15.5      | 191     |

| n                | 16 QAM     | MCS4_20    | 15.5      | 181     |

| n                | 64 QAM     | MCS5_20    | 15.0      | 169     |

| n                | 64 QAM     | MCS6_20    | 15.0      | 165     |

| n                | 64 QAM     | MCS7_20    | 15.0      | 163     |

| n                | BPSK       | MCS0_40    | 16.0      | 209     |

| n                | QPSK       | MCS1_40    | 15.0      | 188     |

| n                | QPSK       | MCS2_40    | 15.0      | 178     |

| n                | 16QAM      | MCS3_40    | 14.5      | 167     |

| n | 16QAM  | MCS4_40 | 14.5 | 155 |

|---|--------|---------|------|-----|

| n | 64QAM  | MCS5_40 | 14.0 | 146 |

| n | 64QUAM | MCS6_40 | 14.0 | 142 |

| n | 64QAM  | MCS7_40 | 14.0 | 139 |

Table 15: WLAN Tx Power Consumption

#### Caution:

The equipment must be supplied by an external limited power source in compliance with the clause 2.5 of the standard EN 60950-1.

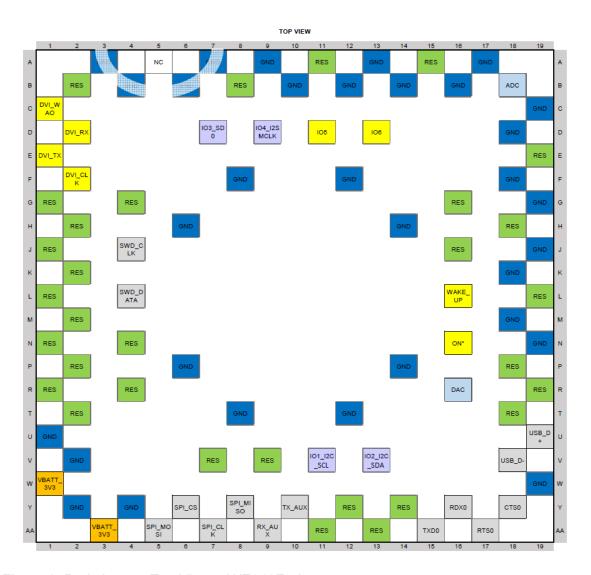

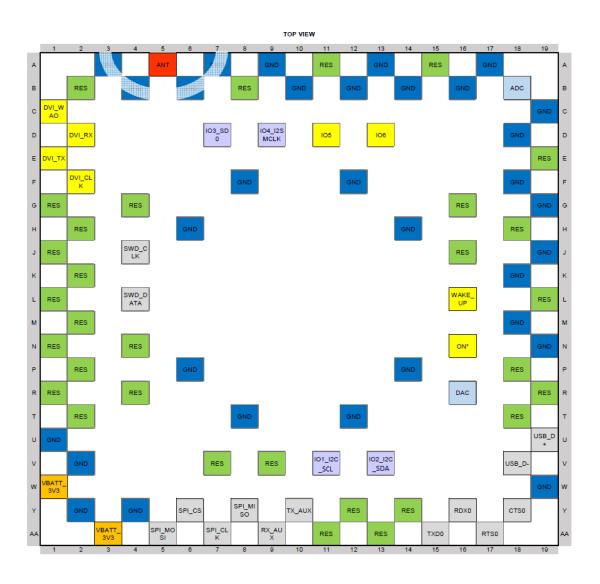

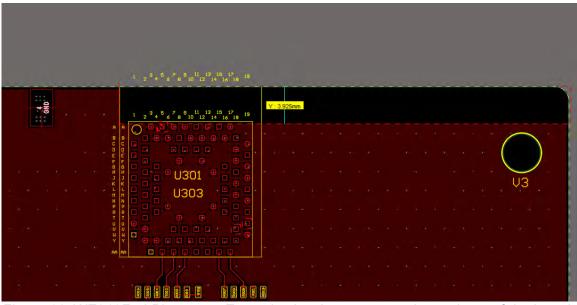

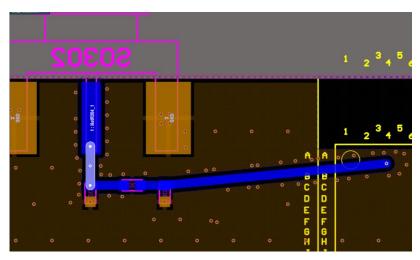

# 6.7. Pads Layout

The Pads layout for both (WE310F5-I and WE310F5-P) the versions of the module is the same, the only difference is the dimension of the RAW PCB due to the on-board antenna on the WE310F5-I version of the module

Following figure shows the pads layout configuration for the module:

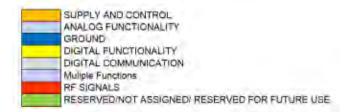

Figure 6: Pads Layout Top View - WE310F5-I

Figure 7: Pads Layout Top View - WE310F5-P

Figure 8: Pinout Legend Color

#### 7. DESIGN GUIDELINES

#### 7.1. General Digital Interface Recommendations

A voltage translator must be used if the components is interfacing with Telit components have digital signals with higher I/O interface voltage than the WE310F5-I/P module.

Using voltage translator components in your design makes the system ready for operation at the full VIO voltage range, 3.3V to system I/O voltage. However, using resistor divider and/or emitter follower circuits, as voltage translators does not protect the module against latch-up. Furthermore, you cannot guarantee a constant voltage on the divider net.

The use of open collector buffers or bi-directional voltage level translators with unidirectional signals is correct, but they suffer of some RF noise and they are dependent on Pull-Up/Downs in the two sides of the voltage translator.

Some translators operate with different power ranges in the two sides: pay attention to the direction in this case.

In general, we recommend unidirectional level shifters but if bi-directional buffers are preferred, please considering those that requires external PU/PD instead having embedded PU/PD circuitry. Some brands that we recommend:

Texas Instruments TXS series

NXS NVT200x series

If the system includes cellular module, consider adding some bypass capacitors to the supply lines of the voltage level translators to provide a protection from RF signal. For bypass use 33pF for 0402 package or 56pF when are you going to use 0201. For example, SN74AVC2T245, SN74AVC4T774 or SN74LVC2T45, for 5V signals.

Moreover, while using level shifters for better testability, it is recommended to use those having OE pins. Test pulling the "EN" lines of the level shifts with the addition of a 10K resistor to GND or VCC, depending on level shifter used. This will create access points that would put shifts in tri-state and can be conveniently used for testing and firmware updates originating from external serial ports such as a PC.

It is recommended to connect the WE310F5-I/P ON\* (N16 pin) to control the Enable pin of the level shifter, in this way a tri-state will be guarantee during BOOT.

#### 7.2. Power supply design guidelines

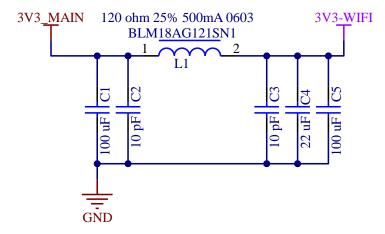

We recommend adding and external EMI filter to improve the quality of the power supply especially when the module will be embedded with other technologies, (i.e. Cellular). The pi-greca filter composed by ferrite bead and 10pF capacitors (C2,C3) is used to provide an high impedance value for high frequency signals, while the 100uF and 22uF capacitors (C1,C5 and C4) are used to bypass low frequencies from switching regulator circuit and to provide a supply tank for high current absorption.

Figure 9: EMI Filter Example

Figure above shows an example circuit with the minimum allowable capacitor values.

#### **WARNING:**

Abrupt Power Cut may corrupt modem's memory.

Use it only when no other option, like RESET or Power Shutdown, is not available.

#### 7.3. Bypass Capacitors

To improve the harmonic filtering, we recommend adding bypass capacitors, close to:

- Power Sources and signals on input-output connectors

- At power supply output PADs

- At component's power supply input PADs (even if shielded)

- Diodes in forward conduction, like LEDs, on anode and/or cathodes if not directly tied to a power net

- Transistor bases, mainly for bipolar ones, phototransistors and opto-isolator

- Analog microphone pads

- Operational Amplifiers Inputs and supplies.

The bypass capacitors should have a self-resonant frequency close to the frequency generated on your board or on transmitted from the boards that will operate in the same environment in which your board operates.

For example, to effectively filter the Wi-Fi RF bands, these small signal capacitors must have a self-resonant (SRF) at about 2.4GHz. Example capacitor values, depending on manufacture and its mechanical dimensions should be around 10pF, in general by reducing the packaging size you will need to increase the capacitance value. Please check carefully the datasheet to find the proper component suitable for this purpose.

Another example is for GSM, in general you can use 33pF 0402 or 56pF 0201

#### 7.4. Antenna Guidelines

The WE310F5-I has an embedded ceramic antenna on board. To preserve the bandwidth, keep attention to not place any copper or mechanic component in front or close to ceramic antenna.

We recommend module placement as shown in the figure below:

Figure 10: WE310F5-I Placement Example

For WE310F5-I version the antenna is placed directly on the board, so you will need to leave a copper keep-out area as shown in below:

Figure 11: WE310F5-I Placement Example showing no copper in any layer of the board.

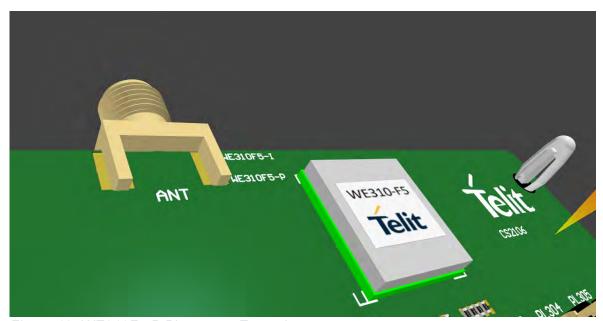

For WE310F5-P you will need to use an external antenna connected to the antenna pad of the module, such as SMA connector as shown in figure below.

Figure 12: WE310F5-P Placement Example

In this case considering the position of the external antenna with respect to other boards is very important. the conductive planes close to the antenna can modify the impedance seen by the antenna or detune it.

- The WE310F5-P module provides a  $50\Omega$  antenna pad, which needs to be routed to the antenna connector (or the integrated antenna) with a transmission line

- Please keep as close as possible to  $50\Omega$  impedance in the RF track, including the RF Pad

- To avoid step impedance, try to track RF trace as much equal as possible to the pad with of the matching components

Figure 13: RF Track Example

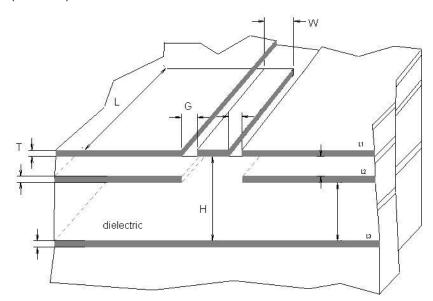

• To have a good impedance control consider using a Grounded coplanar waveguide structure (G-CPW) line.

Figure 14: Coplanar Waveguide Dimensioning Example

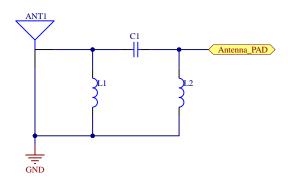

The final dimensions depend on the use of stack-up. While the WE310F5-I is already tuned to the embedded antenna, the WE310F5-P version needs to be tuned in relationship to the stack-up used.

Figure 15: Minimal RF Matching Network Circuitry

A possible network topology is seen in the above figure and it consist of three passive components.

To reuse Telit's FCC certification for our module, the antenna on the application board shall have a gain equal or lower to the one recommended by Telit, the separation distance between the user and/or bystander and the device's radiating element must be greater than 20cm and no other radiating element must be present inside the application closer than 20cm to our antennas. However, a separate test for any other radiating element could be necessary.

For external antenna, it is recommended to use xxx antenna from xxx which is a WLAN, complete with antenna characteristics.

#### 7.5. Audio considerations

The digital audio data interface supports I2S. Since, many external processors and applications have fast transient signals, it is recommended to add an RC filter on all DVI lines (R~22Ohm and C~10nF). If the DVI lines, I2S, are run on external layers it is possible that RF will disturb the lines, to resolve this, add in parallel, to 10nF, another capacitor of about 10pF to 33pF.

## 7.6. Other General Design Considerations

Since, components and PCBs are getting smaller while component's density increases, another problem that becomes important is the heat dissipation.

For that reason, pay special attention to the PCB stack up and component placement. The following PCB design rules will help RF immunity and improve heat dissipation.

- 1. Use at least a six layers PCB technology.

- 2. Layer2 and Layer4 should be mainly ground.

- 3. On top of Layer1 and at the bottom of Layer6, place mainly ground plane interrupted just by component pads and RF antenna tracks.

- 4. Minimum tracks connecting Layer3 to Layer5. This is done to avoid ground interruption and its heat dissipation.

- 5. Use Layer3 and Layer5 only for signals, where power lines are wider tracks and surrounded by ground to reduce the risk of crosstalk with other signals.

- 6. Use one layer for horizontal lines only, and the another one for vertical lines. Fill the remaining empty space with ground.

- 7. Use several vias to connect all ground planes and areas in all layers with possible through hole drills.

- 8. Place warmer components on the PCB side facing up and do not place anything near them, leaving space for air.

- 9. If it is a closed application, consider opening holes on top and bottom of the cover for ventilation.

It is recommended to use 4 layers only, if the number of interconnection gives you the possibility to route them on layer2 and layer3 in a way that power lines and signals lines do not intersect, and the module is operating continuously so the heat dissipation is not a must. All the rest suggestion described above must be fulfilling.

The audio, USB, and ADC lines must be routed avoiding intersection with any other signal.

Top and Bottom layers should be mainly a ground plane interrupted just by component's pads, vias and RF tracks. Connect all ground areas avoiding isolated island with several vias. In this way, the signal tracks are more protected from picking up RF due to the Faraday-Cage effect. Long exposed tracks can easily pick-up RF power and especially in your case with many RF power sources you can generate high frequency intermodulation harmonics that the same exposed tracks can then irradiate very efficiently.

The PCB outline should be surrounded by GND vias interconnected from TOP to Bottom. We also recommend filling the free space in inner layers with ground.

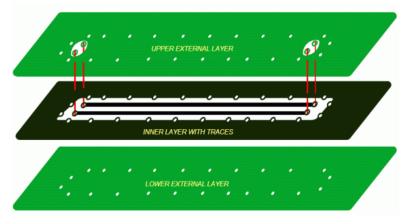

Pay attention to interconnect all the ground areas or planes to guarantee a strong equipotential node. Remove dead copper areas and net antennas tracks or vias. It is recommended to bury in inner layers:

- 1) analog or digital audio lines,

- 2) memory address and data bus, f

- 3) fast digital signals like SPI or SDIO, clocks, quartz,

- 4) USB and long serial.

The following figure shows an example of fast signals track routing. In this example the tracks are routed in an inner layer and surrounded by GND and GND vias to be shielded. If possible, try to shield with GND areas the above and below areas.

Figure 16: Layout Example for FAST Digital Lines

Lines to resolve this, add in parallel, to 10nF, another capacitor of about 10pF to 33pF.

# 8. MECHANICAL DESIGN

## 8.1. WE310F5-I

Figure 17: WE310F5-I mechanical design

Figure 18: WE310F5-I Side View detail

Figure 19: WE310F5-I Bottom View

## 8.2. WE310F5-P

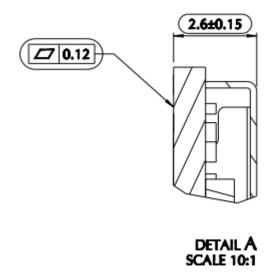

Figure 20: WE310F5-P mechanical design

Figure 21: WE310F5-P side view detail

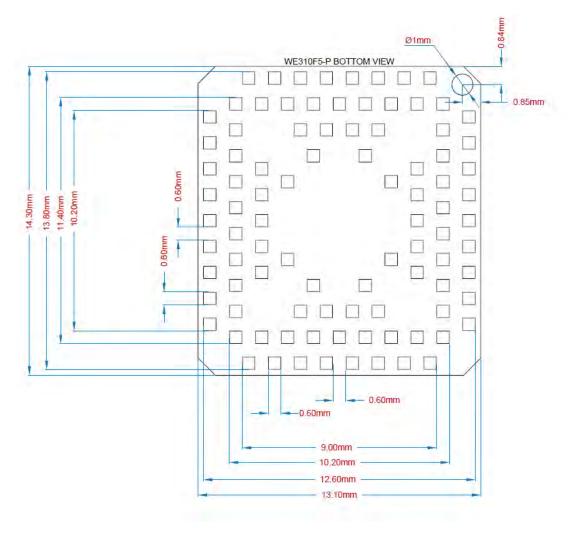

Figure 22: WE310F5-P Bottom View

# 8.3. PCB Pad Design

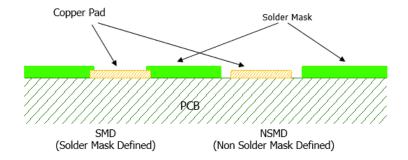

For the solder pads, it is recommended to use Non-Solder Mask Defined pad (NSMD) on the PCB.

Figure 23: SMD and NSMD Pad

#### 8.4. PCB Pad Dimensions

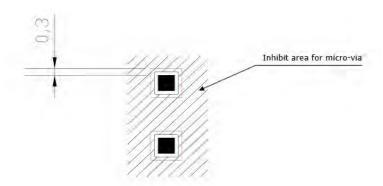

It is not recommended to place via or micro-via not covered by solder resist in an area of 0.3 mm around the pads unless it carries the same signal of the pad itself as shown below.

Figure 24: Inhibit Area for Not Solder Covered Vias

The holes in pad are allowed only for blind holes and not for through holes. Table 16: shows the recommended PCB pad surfaces

| Finish                         | Layer thickness [µm] | Properties              |               |

|--------------------------------|----------------------|-------------------------|---------------|

| Electro-less Ni / Immersion Au | 3 –7 / 0.03 – 0.15   | Good protection,        | solderability |

|                                |                      | high shear force values |               |

Table 16: PCB Finishing Recommendation

The PCB must be able to resist the higher temperatures which can occurs during the lead-free process. This issue should be discussed with the PCB-supplier. Generally, the wettability of tin-lead solder paste on the described surface plating is better compared to lead-free solder paste.

It is not necessary to panel the application PCB. However, it is recommended to use milled contours and predrilled board breakouts; scoring or v-cut solutions are NOT recommended.

#### 8.5. Stencil

Stencil's apertures layout can be the same as the recommended footprint (1:1). It is recommended to use a stencil foil with thickness  $\geq$  120  $\mu$ m.

#### 8.6. Solder Paste

|              | Lead free |

|--------------|-----------|

| Solder paste | Sn/Ag/Cu  |

Table 17: Recommended Solder Paste Type

To avoid or minimize the cleaning efforts after assembly, it is recommended to use a "no clean" solder paste.

# 8.7. Solder Reflow

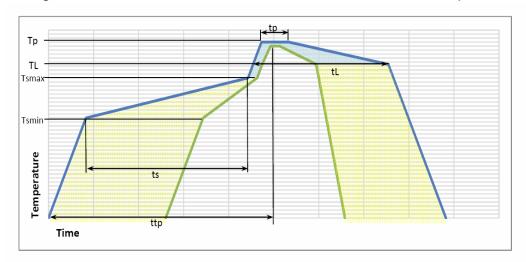

Figure 25: and Table 18: shows the recommended solder reflow profile.

Figure 25: Solder Reflow Profile

| Profile Feature                                                                                                                                 | Pb-Free Assembly                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Average ramp-up rate (T <sub>L</sub> to T <sub>p</sub> )                                                                                        | 3 °C/second max.                   |

| Preheat                                                                                                                                         |                                    |

| <ul> <li>Temperature Min. (T<sub>smin</sub>)</li> <li>Temperature Max. (T<sub>smax</sub>)</li> <li>Time (min to max) (t<sub>s</sub>)</li> </ul> | 150 °C<br>200 °C<br>60-180 seconds |

| T <sub>smax</sub> to T <sub>L</sub> • Ramp-up rate                                                                                              | 3 °C/second max                    |

| Time maintained above:  Temperature (T <sub>L</sub> )  Time (t <sub>L</sub> )                                                                   | 217 ℃<br>60-150 seconds            |

| Peak temperature (T <sub>p</sub> )                                                                                                              | 245 +0/-5 °C                       |

| Time within 5 °C of actual peak temperature (t <sub>p</sub> )                                                                                   | 10-30 seconds                      |

| Ramp-down rate                                                                                                                                  | 6 °C/second max.                   |

| Profile Feature                | Pb-Free Assembly |

|--------------------------------|------------------|

| Time 25 °C to peak temperature | 8 minutes max.   |

Table 18: Solder Reflow Table

All temperatures refer to topside of the package, measured on the package body surface.

#### **WARNING:**

The WE310F5-I/P module withstands only one reflow process.

The above solder reflow profile represents the typical SAC reflow limits and does not guarantee adequate adherence of the module to the customer application throughout the temperature range. Customer must optimize the reflow profile depending on the overall system considering such factors as thermal mass and warpage.

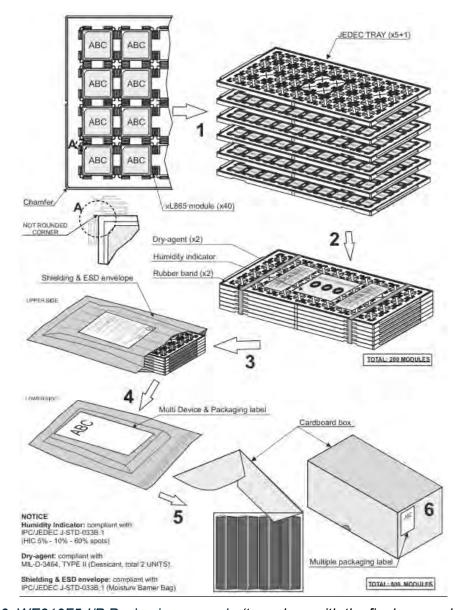

## 9. PACKAGING

## 9.1. Tray

The WE310F5-I/P modules are packaged on trays of 50 pieces each when small quantities are required (i.e. for test and evaluation purposes).

These trays are not designed for use in SMT processes for pick and place handling.

Figure 26: WE310F5-I/P Packaging example (to replace with the final one and add the WE310F5-P figure)

#### **WARNING:**

The maximum temperature for these trays shall not exceed 65°C.

## 9.2. Moisture Sensitivity

The WE310F5-I/P module is classified as a LEVEL 3 moisture sensitive device in accordance with IPC/JEDEC J-STD-020.

Moreover, the customer must take care of the following conditions:

- a) The shelf life of the product inside the dry bag is 12 months starting from the bag seal date, when stored in a non-condensing atmospheric environment of  $< 40^{\circ}$ C and < 90% relative humidity (RH).

- b) Environmental condition during the production:  $\leq$  30°C / 60% RH according to IPC/JEDEC J-STD-033B.

- c) The maximum time between the opening of the sealed bag and the reflow process must be 168 hours, if condition b) "IPC/JEDEC J-STD-033B paragraph §5.2" is respected.

- d) Baking is required if conditions b) or c) are not respected

- e) Baking is required if the humidity indicator inside the bag indicates 10% RH or more.

# 10. CONFORMITY ASSESSMENT ISSUES

# 10.1. FCC/IC Regulatory Notices

Hereby, Telit Communications S.p.A declares that the WE310 F5-I/P Module is following Directive 2014/53/EU.

The full text of the EU declaration of conformity is available at the following internet address: http://www.telit.com/red

## 11. FCC/IC COMPLIANCE

#### **Modification statement**

Telit has not approved any changes or modifications to this device by the user. Any changes or modifications could void the user's authority to operate the equipment.

Telit n'approuve aucune modification apportée à l'appareil par l'utilisateur, quelle qu'en soit la nature. Tout changement ou modification peuvent annuler le droit d'utilisation de l'appareil par l'utilisateur.

#### Interference statement

This device complies with Part 15 of the FCC Rules and Industry Canada licence-exempt RSS standard(s). Operation is subject to the following two conditions:

- (1) this device may not cause interference, and

- (2) this device must accept any interference, including interference that may cause undesired operation of the device.

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes :

- (1) l'appareil ne doit pas produire de brouillage, et

- (2) l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

#### Wireless notice

This device complies with FCC/ISED radiation exposure limits set forth for an uncontrolled environment and meets the FCC radio frequency (RF) Exposure Guidelines and RSS-102 of the ISED radio frequency (RF) Exposure rules. This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter. The antenna should be installed and operated with minimum distance of 20 cm between the radiator and your body.

Le présent appareil est conforme à l'exposition aux radiations FCC / ISED définies pour un environnement non contrôlé et répond aux directives d'exposition de la fréquence de la FCC radiofréquence (RF) et RSS-102 de la fréquence radio (RF) ISED règles d'exposition. L'émetteur ne doit pas être colocalisé ni fonctionner conjointement avec à autre antenne ou autre émetteur. L'antenne doit être installée de façon à garder une distance minimale de 20 centimètres entre la source de rayonnements et votre corps.

## FCC Class B digital device notice

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation.

This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to

radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

## **CAN ICES-3 (B) / NMB-3 (B)**

This Class B digital apparatus complies with Canadian ICES-003.

Cet appareil numérique de classe B est conforme à la norme canadienne ICES-003.

#### List of applicable FCC rules

Parts 15C, 2.1091

#### Limited module procedures

N/A

#### Trace antenna designs

See 7.4 Antenna design

## Antennas

This radio transmitter has been approved by FCC and ISED to operate with the antenna types listed below with the maximum permissible gain indicated. Antenna types not included in this list, having a gain greater than the maximum gain indicated for that type, are strictly prohibited for use with this device.

Type Max Gain

Omnidirectional 2.3dBi@2.4GHz band

Le présent émetteur radio a été approuvé par ISDE pour fonctionner avec les types d'antenne énumérés ci-dessous et ayant un gain admissible maximal. Les types d'antenne non inclus dans cette liste, et dont le gain est supérieur au gain maximal indiqué, sont strictement interdits pour l'exploitation de l'émetteur.

Type Gain maximal

Omnidirectional 2.3dBi@2.4GHz band

#### Label and compliance information

The product has FCC ID and ISED label on the device itself. Also, the OEM host end product manufacturer will be informed to display a label referring to the enclosed module. The exterior label will read as follows:

Contains TX FCC ID: RI7WE310F5

Contains IC: 5131A-WE310F5

#### Information on test modes and additional testing requirements

The module has been evaluated in mobile stand-alone conditions. For different operational conditions from a stand-alone modular transmitter in a host (multiple, simultaneously transmitting modules or other transmitters in a host), additional testing may be required (collocation, retesting...).

If this module is intended for use in a portable device, you are responsible for separate approval to satisfy the SAR requirements of FCC Part 2.1093 and IC RSS-102.

#### Additional testing, Part 15 Subpart B disclaimer

The modular transmitter is only FCC authorized for the specific rule parts (i.e., FCC transmitter rules) listed on the grant, and that the host product manufacturer is responsible for compliance to any other FCC rules that apply to the host not covered by the modular transmitter grant of certification. If the grantee markets their product as being Part 15 Subpart B compliant (when it also contains unintentional-radiator digital circuity), then the grantee shall provide a notice stating that the final host product still requires Part 15 Subpart B compliance testing with the modular transmitter installed. The end product with an embedded module may also need to pass the FCC Part 15 unintentional emission testing requirements and be properly authorized per FCC Part 15.

## 12. SAFETY RECOMMENDATIONS

## 12.1. Read Carefully

Be sure the use of this product is allowed in the country and in the environment required. The use of this product may be dangerous and must be avoided in the following areas:

- Where it can interfere with other electronic devices in environments such as hospitals, airports, aircrafts, etc.

- Where there is risk of explosion such as gasoline stations, oil refineries, etc. It is

the responsibility of the user to enforce the country regulation and the specific

environment regulation.

Do not disassemble the product; any mark of tampering will compromise the warranty validity. We recommend following the instructions of the hardware user guides for correct wiring of the product. The product must be supplied with a stabilized voltage source and the wiring must be conformed to the security and fire prevention regulations. The product must be handled with care, avoiding any contact with the pins because electrostatic discharges may damage the product itself. Same cautions must be taken for the SIM, checking carefully the instruction for its use. Do not insert or remove the SIM when the product is in power saving mode.

The system integrator is responsible for the functioning of the final product; therefore, care must be taken to the external components of the module, as well as any project or installation issue, because the risk of disturbing the GSM network or external devices or having impact on the security. Should there be any doubt, please refer to the technical documentation and the regulations in force. Every module must be equipped with a proper antenna with specific characteristics. The antenna must be installed with care to avoid any interference with other electronic devices and must guarantee a minimum distance from the body (20 cm). In case this requirement cannot be satisfied, the system integrator must assess the final product against the SAR regulation.

The European Community provides some Directives for the electronic equipment introduced on the market. All the relevant information is available on the European Community website:

http://ec.europa.eu/enterprise/sectors/rtte/documents/

The text of the Directive 99/05 regarding telecommunication equipment is available,

while the applicable Directives (Low Voltage and EMC) are available at:

http://ec.europa.eu/enterprise/sectors/electrical/

# 13. ACRONYMS

| TTSC | Telit Technical Support Centre              |

|------|---------------------------------------------|

| USB  | Universal Serial Bus                        |

| HS   | High Speed                                  |

| UART | Universal Asynchronous Receiver Transmitter |

| BLE  | Bluetooth low energy                        |

| WLAN | Wireless LAN                                |

| SPI  | Serial Peripheral Interface                 |

| ADC  | Analog – Digital Converter                  |

| DAC  | Digital – Analog Converter                  |

| PWM  | Pulse Width Modulation                      |

| I/O  | Input Output                                |

| GPIO | General Purpose Input Output                |

| CMOS | Complementary Metal – Oxide Semiconductor   |

| MOSI | Master Output – Slave Input                 |

| MISO | Master Input – Slave Output                 |

| CLK  | Clock                                       |

| RTC  | Real Time Clock                             |

| PCB | Printed Circuit Board        |

|-----|------------------------------|

| ESR | Equivalent Series Resistance |

\

# 14. DOCUMENT HISTORY

| Revision | Date       | Changes                                                                                                                                       |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | 2020-05-27 | First issue.                                                                                                                                  |

| 1        | 2020-06-29 | Update of SD card, Clock and Memory specification.                                                                                            |

| 3        | 2020-09-04 | Pinout and some figures.                                                                                                                      |

| 4        | 2020-09-04 | Pinout table fixed on debug port.                                                                                                             |

| 5        | 2020-09-14 | Pinout Figure 6 and Figure 7 updated.                                                                                                         |

| 6        | 2020-09-30 | Pinout Figure 6 and Figure 7 updated (removed R-KEY)                                                                                          |

| 7        | 2020-10-09 | Updated Figures 20 and 23, added ESD and SAR ADC characteristics, some general improvements, removed Preliminary Watermark.                   |

| 8        | 2020-13-11 | Updated WiFi Transmit Power table (Table n°9), and WLAN Continuous TX power Consumption table (Table n°15) after some software optimizations. |

| 9        | 2020-03-12 | Updated Power consumption Table 14.                                                                                                           |

# SUPPORT INQUIRIES

Link to www.telit.com and contact our technical support team for any questions related to technical issues.

# www.telit.com

Telit Communications S.p.A. Via Stazione di Prosecco, 5/B I-34010 Sgonico (Trieste), Italy

Telit IoT Platforms LLC 5300 Broken Sound Blvd, Suite 150 Boca Raton, FL 33487, USA Telit Wireless Solutions Inc. 3131 RDU Center Drive, Suite 135 Morrisville, NC 27560, USA

Telit Wireless Solutions Co., Ltd. 8th Fl., Shinyoung Securities Bld. 6, Gukjegeumyung-ro8-gil, Yeongdeungpo-gu Seoul, 150-884, Korea Telit Wireless Solutions Ltd. 10 Habarzel St. Tel Aviv 69710, Israel

Telit Wireless Solutions Technologia e Servicos Ltda Avenida Paulista, 1776, Room 10.C 01310-921 São Paulo, Brazil

Telit reserves all rights to this document and the information contained herein. Products, names, logos and designs described herein may in whole or in part be subject to intellectual property rights. The information contained herein is provided "as is". No warranty of any kind, either express or implied, is made in relation to the accuracy, reliability, fitness for a particular purpose or content of this document. This document may be revised by Telit at any time. For most recent documents, please visit www.telit.com