# ATOP3.5G Product Description (OM12030)

80447ST10636A rev.10 - 2015-03-03

## APPLICABILITY TABLE

| PRODUCT     | REGIONS     |           |            |  |  |

|-------------|-------------|-----------|------------|--|--|

|             | W<br>(orld) | U<br>(SA) | A<br>(PAC) |  |  |

| ATOP 3.5G   | ٧           | v         | ٧          |  |  |

| + SMX       | ٧           | ٧         | ٧          |  |  |

| + SMX + NFC | ٧           | ٧         | ٧          |  |  |

80447ST10636A rev.10 - 2015-03-03

#### SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE

#### **Notice**

While reasonable efforts have been made to assure the accuracy of this document, Telit assumes no liability resulting from any inaccuracies or omissions in this document, or from use of the information obtained herein. The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies or omissions. Telit reserves the right to make changes to any products described herein and reserves the right to revise this document and to make changes from time to time in content hereof with no obligation to notify any person of revisions or changes. Telit does not assume any liability arising out of the application or use of any product, software, or circuit described herein; neither does it convey license under its patent rights or the rights of others.

It is possible that this publication may contain references to, or information about Telit products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that Telit intends to announce such Telit products, programming, or services in your country.

#### Copyrights

This instruction manual and the Telit products described in this instruction manual may be, include or describe copyrighted Telit material, such as computer programs stored in semiconductor memories or other media. Laws in the Italy and other countries preserve for Telit and its licensors certain exclusive rights for copyrighted material, including the exclusive right to copy, reproduce in any form, distribute and make derivative works of the copyrighted material. Accordingly, any copyrighted material of Telit and its licensors contained herein or in the Telit products described in this instruction manual may not be copied, reproduced, distributed, merged or modified in any manner without the express written permission of Telit. Furthermore, the purchase of Telit products shall not be deemed to grant either directly or by implication, estoppel, or otherwise, any license under the copyrights, patents or patent applications of Telit, as arises by operation of law in the sale of a product.

#### **Computer Software Copyrights**

The Telit and 3<sup>rd</sup> Party supplied Software (SW) products described in this instruction manual may include copyrighted Telit and other 3<sup>rd</sup> Party supplied computer programs stored in semiconductor memories or other media. Laws in the Italy and other countries preserve for Telit and other 3<sup>rd</sup> Party supplied SW certain exclusive rights for copyrighted computer programs, including the exclusive right to copy or reproduce in any form the copyrighted computer program. Accordingly, any copyrighted Telit or other 3<sup>rd</sup> Party supplied SW computer programs contained in the Telit products described in this instruction manual may not be copied (reverse engineered) or reproduced in any manner without the express written permission of Telit or the 3<sup>rd</sup> Party SW supplier. Furthermore, the purchase of Telit products shall not be deemed to grant either directly or by implication, estoppel or otherwise, any license under the copyrights, patents or patent applications of Telit or other 3<sup>rd</sup> Party supplied SW, except for the normal non-exclusive, royalty free license to use that arises by operation of law in the sale of a product.

80447ST10636A rev.10 - 2015-03-03

#### **Usage and Disclosure Restrictions**

#### **License Agreements**

The software described in this document is the property of Telit and its licensors. It is furnished by express license agreement only and may be used only in accordance with the terms of such an agreement.

#### **Copyrighted Materials**

Software and documentation are copyrighted materials. Making unauthorized copies is prohibited by law. No part of the software or documentation may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, without prior written permission of Telit.

#### **High Risk Materials**

Components, units, or third-party products used in the product described herein are NOT fault-tolerant and are NOT designed, manufactured, or intended for use as on-line control equipment in the following hazardous environments requiring fail-safe controls: the operation of Nuclear Facilities, Aircraft Navigation or Aircraft Communication Systems, Air Traffic Control, Life Support, or Weapons Systems ("High Risk Activities"). Telit and its supplier(s) specifically disclaim any expressed or implied warranty of fitness for such High Risk Activities.

#### **Trademarks**

TELIT and the Stylized T Logo are registered in Trademark Office. All other product or service names are the property of their respective owners.

Copyright © Telit Communications S.p.A.

80447ST10636A rev.10 - 2015-03-03

# ATOP 3.5G (OM12030)

Automotive telematics on-board unit platform 3.5G

## 1 Introduction

ATOP 3.5G (OM12030) is Telit's platform for automotive telematics on-board units (OBU's) for applications such as road pricing and eCall, based on the following technologies:

- 3G cellular for voice and data communication

- GPS/GLONASS for positioning service

- NFC for short range communication, e.g. configuration and law enforcement

- SmartMX smartcard with Java card JCOP OS for security

- J9 Virtual Machine for application portability and easy creation

- Dedicated processor for Real-Time and connection to system via ADC, CAN, UART, Ethernet, USB

- Backward hardware compatibility with ATOP 2.5G EVO (OM12001)

- Designed for automotive markets<sup>1</sup>

Thanks to on-board ATOP 3.5G security resources, product developers and manufacturers can offer products which guarantee fraud prevention and tamper evidence without extra effort for additional security precautions. These products can be used in end-to-end transaction systems requiring Common Criteria level 5+.

ATOP 3.5G can be used by itself as a complete solution for GNSS-3G based road pricing and eCall applications. In this case, ATOP 3.5G just needs to be complemented with a power supply, speaker, microphone, some knobs and an optional display. ATOP 3.5G provides the processing power and software application environment resources on board to complement road pricing and eCall with some other added value telematics services.

ATOP 3.5G can also be applied as a front end for more elaborate telematics products, by making its resources, i.e. GNSS, mobile communication, security (ID authentication) available for use by other resources in the OBU.

Three different 3G band configuration variants are defined for OM12030:

- World market configuration

- American market configuration

- Pacific market configuration

For applications where security is not paramount, such as eCall, variants without NFC short range communication and/or the SmartMX security processor are available.

<sup>&</sup>lt;sup>1</sup> In accordance with Telit's Robustness Validation, using AEC-Q100-defined qualification tests.

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved.

Page 5 of 66

80447ST10636A rev.10 - 2015-03-03

## 2 General description

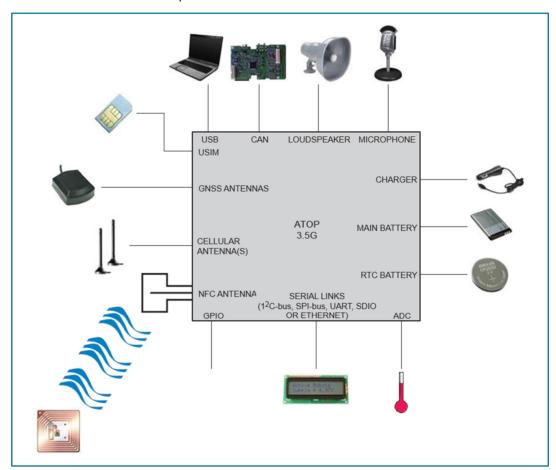

Figure 1 represents ATOP 3.5G connections in a typical application, with its connection to batteries, antennas and USIM. For communication with the external world, serial link, GPIOs, and ADCs will connect to screen, keys, and sensors. UART, CAN, SDIO, Ethernet or USB can be used to connect to an on-board computer.

Figure 1 ATOP 3.5G module connections

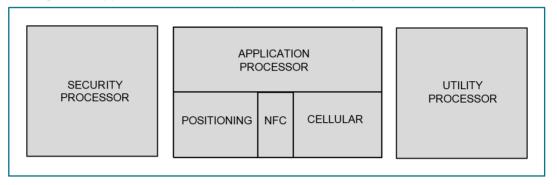

Figure 2 represents a more conceptual view of ATOP from a system point of view, showing three main components:

- Application processor: This processor will run code specific to the application (road tolling, insurance ...) which is portable from one platform to another one in order to avoid recertification. The application drives the three following conceptual co-processors:

- A Positioning processor provides accurate location information to the application;

- An NFC processor<sup>2</sup> provides connection to an external bignette, card reader, or other NFC enabled device to increase application security;

- A Communication processor allows the application to connect to servers and receive update and notifications, receive or generate voice call or SMS.

<sup>&</sup>lt;sup>2</sup> Only for OM12030/1X0, with X as defined in Section 5.

**ATOP3.5G Product Description** 80447ST10636A rev.10 - 2015-03-03

- Security processor<sup>3</sup>: This processor provides a root of trust for signing messages to servers; authenticates the presence of an external vignette; and/or runs multiple security applications.

- Utility processor: This processor takes care of all housekeeping tasks such as

connecting to external interfaces, displays, etc. but also handles power management,

waking-up and booting-up the system, i.e. all support tasks which are not part of the

high-level applications but are required to make the system work.

Figure 2 ATOP conceptual view

## 3 Features and benefits

- Utility processor for interfacing with external world and house-keeping

- ARM Cortex M3 microcontroller with Ethernet, CAN, USB Host, Device and OTG, UART, SPI-bus, I<sup>2</sup>C-bus, ADCs, DAC, GPIOs, and PWMs

- o Internal temperature sensor

- Application processor to run customer application code

- Virtual Machine for customer application

- Communication coprocessor with Quad-band 3.5G/EDGE/GPRS/GSM terminal

- o GPS/GLONASS receiver

- Near Field Communication (NFC) coprocessor to connect to external vignette, smart card, mobile phone<sup>2</sup>

- Security processor for providing a source of trust<sup>3</sup>

- o SmartMX smartcard running JCOP 2.4.2

- Mandatory and voluntary certification

- R&TTE and FCC passed for safety, EMC, and RF

- Certification for GCF, including field test

- o Certification for PTCRB

- Certification for AT&T

- Designed and qualified for use in automotive applications<sup>1</sup>

- -40 °C to +85 °C / limited operating range as defined in Table 11

<sup>&</sup>lt;sup>3</sup> Only for OM12030/1X0 and OM12030/2X0, with X as defined in Section 5.

80447ST10636A rev.10 - 2015-03-03

## 4 Applications

ATOP 3.5G can be used for telematics applications where tamper-resistance, confidentiality, integrity and authenticity of end-user information are required, e.g.:

- Road pricing

- Pay as you drive insurance

- Stolen vehicles tracking

- Emergency call

- Internet connectivity

## 5 Ordering information

ATOP 3.5G is defined in multiple variants:

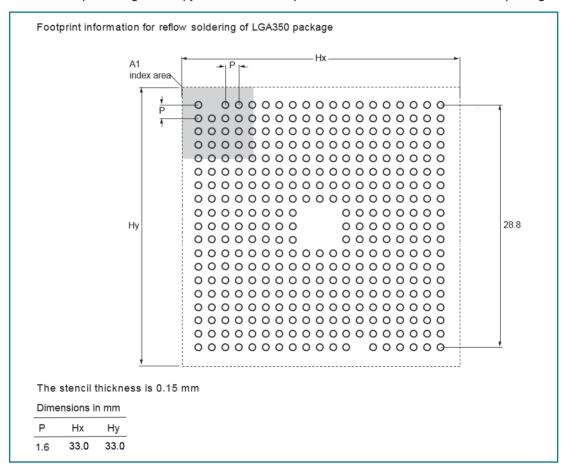

Table 1 Type names

| Type number                | Package<br>Name | Description                                                                                             |

|----------------------------|-----------------|---------------------------------------------------------------------------------------------------------|

| OM12030/X00 [1]            | LGA350          | Worldwide Quad-band UMTS 2100 (I), 1900 (II), 850 (V) including 800 (VI), 900 (VIII)                    |

| OM12030/X10 <sup>[1]</sup> |                 | North American Quad-band UMTS 2100 (I), 1900 (II), 1700 (IV), 850 (V) including 800 (VI)                |

| OM12030/X20 <sup>[1]</sup> |                 | Pacific Quad-band UMTS 2100 (I), 1800 (III) including 1700 (IX), 850 (V) including 800 (VI), 900 (VIII) |

- [1] X = 1 Includes NFC short range communication and the SmartMX security element. Feature combination nicknamed "Full".

- X = 0 Omits NFC short range communication and the SmartMX security element. Feature combination nicknamed "Minus".

- X = 2 Omits NFC short range communication but retains the SmartMX security element.Feature combination nicknamed "Auth".

All variants support 2G bands 850, 900, 1800, and 1900.

80447ST10636A rev.10 - 2015-03-03

## 6 Block diagram

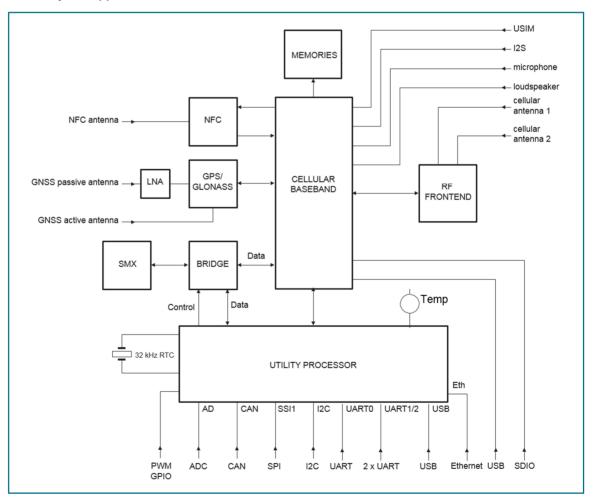

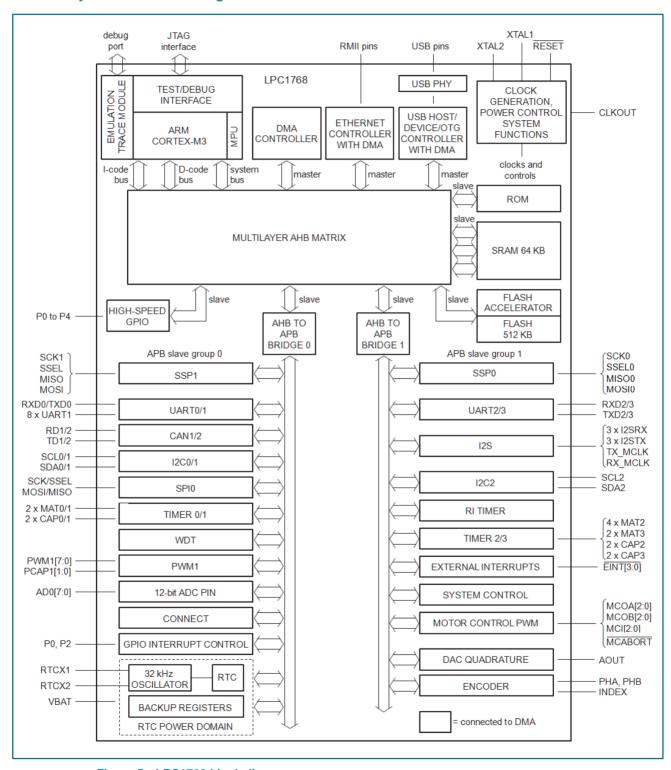

Figure 3 represents the data connections within the ATOP 3.5G module.

Two main groups of components can be distinguished:

- The first group includes the cellular baseband, GPS/GLONASS and secure element (SMX). They offer to the application running on a Virtual Machine all services required for telematics applications.

- The second group includes the microcontroller which takes care of interfacing with the

external world via its interfaces: Ethernet, USB, CAN, UARTs, SPIs, GPIOs, PWMs, and

ADCs.

Depending on which ATOP software features are used in the customer application, some of its interfaces that are exported due to multiplexing may be used internally and thus may not be usable by the application.

Figure 3 ATOP 3.5G internal connections

80447ST10636A rev.10 - 2015-03-03

## 7 Pinning information

## 7.1 Pinning

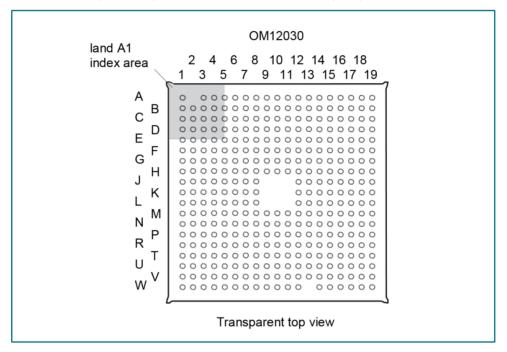

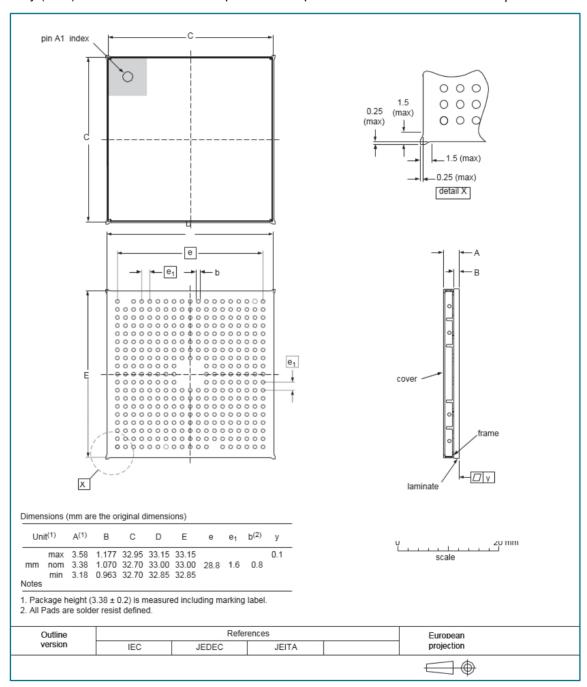

Figure 4 shows a transparent top view of ATOP 3.5G to identify all pins.

Figure 4 ATOP 3.5G pin configuration

## 7.2 Pin description

#### 7.2.1 Module pinning list

Table 2 ATOP 3.5G pinning list

| Symbol <sup>[1]</sup>   | Pin | Level | Description <sup>[2]</sup>          |

|-------------------------|-----|-------|-------------------------------------|

| Utility processor       |     |       |                                     |

| UART0                   |     |       |                                     |

| MC_P002_TXD0_AD07       | M15 | 3.0   | transmitter output for UART0 [3]    |

| MC_P003_RXD0_AD06       | M19 | 3.0   | receiver input for UART0 [3]        |

| UART1                   |     |       |                                     |

| MC_P015_TXD1_SCK0_SCK   | V15 | 3.0   | transmitter output for UART1 [4][5] |

| MC_P016_RXD1_SSEL0_SSEL | T7  | 3.0   | receiver input for UART1 [4][5]     |

| MC_P022_RTS1_TD1        | Т9  | 3.0   | ready to send [5]                   |

| MC_P017_CTS1_MISO0_MISO | V13 | 3.0   | clear to send [4][5]                |

| MC_P021_RI1_RD1         | R10 | 3.0   | ring indicator [5]                  |

| MC_P018_DCD1_MOSI0_MOSI | R11 | 3.0   | data carrier detect [4][5]          |

| UART2                   |     |       |                                     |

| MC_P010_TXD2_SDA2_MAT30 | R13 | 3.0   | transmitter output for UART2 [5]    |

| MC P011 RXD2 SCL2 MAT31 | U10 | 3.0   | receiver input for UART2 [5]        |

# **ATOP3.5G Product Description** 80447ST10636A rev.10 - 2015-03-03

| Symbol <sup>[1]</sup>        | Pin | Level | Description <sup>[2]</sup>                  |

|------------------------------|-----|-------|---------------------------------------------|

| UART3                        |     |       |                                             |

| MC_P428_RXMCLK_MAT20_TXD3    | V14 | 3.0   | transmitter output for UART3 [5][6]         |

| MC_P429_TXMCLK_MAT21_RXD3    | N11 | 3.0   | receiver input for UART3 [5][6]             |

| I <sup>2</sup> C-bus 0       |     |       |                                             |

| MC_P028_SCL0_USBSCL          | T12 | 3.0   | I <sup>2</sup> C-bus clock input/output [7] |

| MC_P027_SDA0_USBSDA          | T11 | 3.0   | I <sup>2</sup> C-bus data input/output [7]  |

| SSI                          |     |       |                                             |

| MC_P007_I2STXCLK_SCK1_MAT21  | T18 | 3.0   | serial clock [5]                            |

| MC_P009_I2STXSDA_MOSI1_MAT23 | V18 | 3.0   | master out/slave in [5]                     |

| MC_P008_I2STXWS_MISO1_MAT22  | V17 | 3.0   | master in/slave out [5]                     |

| MC_P006_I2SRXSDA_SSEL1_MAT20 | R18 | 3.0   | slave select [5]                            |

| I <sup>2</sup> S-bus         |     |       |                                             |

| MC_P023_AD00_I2SRXCLK_CAP30  | P16 | 3.0   | receive serial clock [3]                    |

| MC_P024_AD01_I2SRXWS_CAP31   | M16 | 3.0   | receive word select [3]                     |

| MC_P025_AD02_I2SRXSDA_TXD3   | N16 | 3.0   | receive data [3]                            |

| MC_P211_EINT1_I2STXCLK       | T13 | 3.0   | transmit serial clock [8]                   |

| MC_P212_EINT2_I2STXWS        | R9  | 3.0   | transmit word select [8]                    |

| MC_P213_EINT3_I2STXSDA       | T10 | 3.0   | transmit data [8]                           |

| CAN1                         |     |       |                                             |

| MC_P000_RD1_TXD3_SDA1        | T14 | 3.0   | receive data [5]                            |

| MC_P001_TD1_RXD3_SCL1        | R12 | 3.0   | transmit data [5]                           |

| CAN2                         |     |       |                                             |

| MC_P004_I2SRXCLK_RD2_CAP20   | P19 | 3.0   | receive data [5]                            |

| MC_P005_I2SRXWS_TD2_CAP21    | P15 | 3.0   | transmit data [5]                           |

| Universal Serial Bus (USB)   |     |       |                                             |

| MC_P029_USBDP                | N12 |       | USB data P [9]                              |

| MC_P030_USBDN                | L13 |       | USB data N [9]                              |

| MC_P130_VBUS_AD04            | L12 |       | USB V <sub>bus</sub> detect [3]             |

| MC_P209_USBCNT_RXD2          | R14 |       | USB device connect [5]                      |

| Ethernet                     |     |       |                                             |

| MC_P115_ENETREFCLK           | T19 | 3.0   | [5]                                         |

| MC_P116_ENETMDC              | U18 | 3.0   | [5]                                         |

| MC_P100_ENETTXD0             | R16 | 3.0   | [5]                                         |

| MC_P101_ENETTXD1             | R15 | 3.0   | [5]                                         |

| MC_P104_ENETTXEN             | V19 | 3.0   | [5]                                         |

| MC_P109_ENETRXD0             | T15 | 3.0   | [5]                                         |

| MC_P110_ENETRXD1             | T16 | 3.0   | [5]                                         |

| MC_P114_ENETRXER             | T8  | 3.0   | [5]                                         |

| MC_P108_ENETCRS              | P14 | 3.0   | [5]                                         |

|                              |     |       |                                             |

# **ATOP3.5G Product Description** 80447ST10636A rev.10 - 2015-03-03

| Symbol <sup>[1]</sup>       | Pin | Level | Description <sup>[2]</sup>                                                       |

|-----------------------------|-----|-------|----------------------------------------------------------------------------------|

| MC_P117_ENETMDIO            | V16 | 3.0   | [5]                                                                              |

| Control                     |     |       |                                                                                  |

| Analog IOs                  |     |       |                                                                                  |

| MC_P026_AD03_AOUT_RXD3      | N18 | 3.0   | digital analog converter output [10                                              |

| GPIO/PWM                    |     |       |                                                                                  |

| MC_P210_EINT0_NMI           | W14 | 3.0   | external interrupt; pull up in ATOP<br>2.5G EVO (OM120001) not in<br>LPC1768 [8] |

| MC_P119_MCOA0_CAP11         | N13 | 3.0   | PWM, event capture input, [5]                                                    |

| MC_P118_USBLD_PWM11_CAP10   | N15 | 3.0   |                                                                                  |

| MC_P122_MCOB0_USBPWRD_MAT10 | M10 | 3.0   |                                                                                  |

| MC_P129_MCOB2_PCAP11_MAT01  | M11 | 3.0   |                                                                                  |

| Debug Interfaces            |     |       |                                                                                  |

| Microcontroller JTAG        |     |       |                                                                                  |

| MC_JTAG_TCK_SWDCLK          | K16 | 3.0   | [11]                                                                             |

| MC_JTAG_TDO_SWO             | K19 | 3.0   | [5]                                                                              |

| MC_JTAG_TDI                 | L16 | 3.0   | [12]                                                                             |

| MC_JTAG_TMS_SWDIO           | L18 | 3.0   | [12]                                                                             |

| MC_JTAG_RTCK                | M18 | 3.0   | [11]                                                                             |

| MC_JTAG_TRST                | K18 | 3.0   | [12]                                                                             |

| Microcontroller PC trace    |     | 3.0   |                                                                                  |

| MC_P206_TRCLK_PCAP10_RI1    | N10 | 3.0   | [5]                                                                              |

| MC_P205_TRDATA0_PWM16_DTR1  | N9  | 3.0   | [5]                                                                              |

| MC_P204_TRDATA1_PWM15_DSR1  | P18 | 3.0   | [5]                                                                              |

| MC_P203_TRDATA2_PWM14_DCD1  | M12 | 3.0   | [5]                                                                              |

| MC_P202_TRDATA3_PWM13_CTS1  | N8  | 3.0   | [5]                                                                              |

| Audio interfaces            |     |       |                                                                                  |

| Analog in                   |     |       |                                                                                  |

| BB_AUDIO_IN1_N              | G12 |       | microphone 1 (optionally digital)                                                |

| BB_AUDIO_IN1_P              | H13 |       |                                                                                  |

| BB_AUDIO_IN1_BIAS           | G13 |       |                                                                                  |

| BB_AUDIO_IN2_N              | G16 |       | microphone 2                                                                     |

| BB_AUDIO_IN2_P              | F16 |       |                                                                                  |

| BB_AUDIO_IN2_BIAS           | G15 |       |                                                                                  |

| BB_AUDIO_IN_L               | H14 |       | line in left                                                                     |

| BB_AUDIO_IN_R               | J14 |       | line in right                                                                    |

| Analog out                  |     |       |                                                                                  |

| BB_AUDIO_OUT1_LP            | J15 |       | positive left out                                                                |

| BB_AUDIO_OUT1_LN            | H15 |       | negative left out                                                                |

| BB_AUDIO_OUT1_2_RP          | K13 |       | positive right out                                                               |

| Symbol <sup>[1]</sup>        | Pin        | Level | Description <sup>[2]</sup>                                                         |

|------------------------------|------------|-------|------------------------------------------------------------------------------------|

| BB_AUDIO_OUT1_2_RN           | K15        |       | negative right out                                                                 |

| BB_AUDIO_SPKL_P              | D17        |       | positive speaker left out                                                          |

| BB_AUDIO_SPKL_N              | E17        |       | negative speaker left out                                                          |

| BB_AUDIO_SPKR_P              | F17        |       | positive speaker right out                                                         |

| BB_AUDIO_SPKR_N              | G17        |       | negative speaker right out                                                         |

| Digital                      |            |       |                                                                                    |

| BB_I2S_SCLK_PCM_CLK          | E14        | 1.8   |                                                                                    |

| BB_I2S_WS_PCM_SYNC           | D15        | 1.8   |                                                                                    |

| BB_I2S_DOUT_PCM_DATA_IN      | E12        | 1.8   |                                                                                    |

| BB_I2S_MCLK_PCM_DATA_OUT     | E13        | 1.8   |                                                                                    |

| BB_I2S_DIN                   | G14        | 1.8   |                                                                                    |

| System interfaces            |            |       |                                                                                    |

| USB interface                |            |       |                                                                                    |

| BB_USBDN                     | U12        |       | USB data N                                                                         |

| BB_USBDP                     | U11        |       | USB data P                                                                         |

| BB_USBID                     | U13        |       | USB device connect                                                                 |

| BB_USBVBUS                   | U14        |       | USB V <sub>bus</sub> detect                                                        |

| SDIO interface               |            |       |                                                                                    |

| BB_SDIOCMD                   | P7         | 2.85  |                                                                                    |

| BB_SDIOCLK                   | P8         | 2.85  |                                                                                    |

| BB_SDIO_PWR_EN_N             | P9         | 2.85  |                                                                                    |

| BB_SDIO_DET                  | P11        | 1.8   | active low, no pull up needed                                                      |

| BB_SDIOD0                    | U6         | 2.85  |                                                                                    |

| BB_SDIOD1                    | U7         | 2.85  |                                                                                    |

| BB_SDIOD2                    | U8         | 2.85  |                                                                                    |

| BB_SDIOD3                    | U9         | 2.85  |                                                                                    |

| USIM interface               |            |       | ISO7316-3 class B/C I/O levels                                                     |

| BB_SIM_DATA                  | E16        |       |                                                                                    |

| BB_SIM_CLK                   | D14        |       |                                                                                    |

| BB_SIM_RST                   | D13        |       |                                                                                    |

| BB_USIM_DETEC_N              | L14        |       | active low, no pull up needed                                                      |

| Battery and power management |            |       |                                                                                    |

| VBAT_RTC_SNK                 | J18        |       | power supply for microcontroller RTC battery                                       |

| VBAT_SNK                     | J2; J4     |       | power supply for whole system except RF power amplifier and utility processor [13] |

| VBAT_PA_SNK                  | J1; K1; K2 |       | power supply for RF power amplifier [13]                                           |

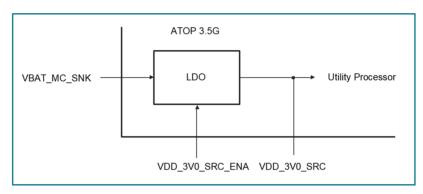

| VBAT_MC_SNK                  | K4         |       | main power supply for utility processor                                            |

|                              |            |       |                                                                                    |

| Symbol <sup>[1]</sup> | Pin      | Level | Description <sup>[2]</sup>                                                                      |

|-----------------------|----------|-------|-------------------------------------------------------------------------------------------------|

| VDD_SPKR              | H17      |       | power supply for class D amplifier                                                              |

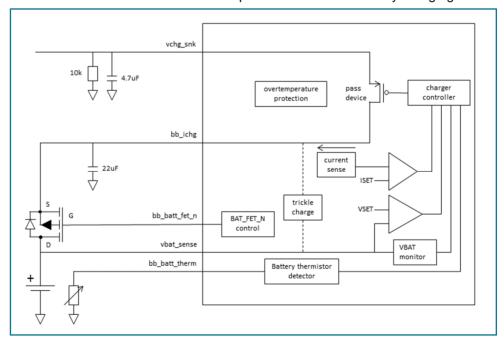

| VCHG_SNK              | G10; H10 |       | charger supply connection                                                                       |

| VBAT_SENSE            | E10      |       | battery voltage sense                                                                           |

| BB_ICHG               | H11      |       | charger output                                                                                  |

| BB_BATT_FET_N         | E11      |       | external charge FET control                                                                     |

| BB_BATT_THERM         | H18      |       | battery thermistor                                                                              |

| VIO_REF               | P5       |       | voltage (1.8 V) reference for baseband digital interface                                        |

| VADC_REF              | W16      |       | voltage reference for MC_ADC                                                                    |

| VADC_GND              | W17      |       | ground reference for MC_ADC                                                                     |

| VUSIM_SRC             | J13      |       | USIM power supply                                                                               |

| VDD_3V0_SRC           | N19      |       | microcontroller current source and voltage reference                                            |

| VDD_3V0_SRC_ENA       | W18      |       | enables VDD_3V0_SRC (active HIGH, internal pull up)                                             |

| Clock generation      |          |       |                                                                                                 |

| BB_EXT_CLK            | D10      | 2.6   | clock source                                                                                    |

| MC_XTAL1              | M13      |       | optional quartz for microcontroller                                                             |

| MC_XTAL2              | N7       |       |                                                                                                 |

| GPS_1PPS              | R4       | 1.8   | one pulse per second (output)                                                                   |

| System reset          |          |       |                                                                                                 |

| MC_RESET              | L15      | 3.0   | reset ATOP module [14]                                                                          |

| Antennas              |          |       |                                                                                                 |

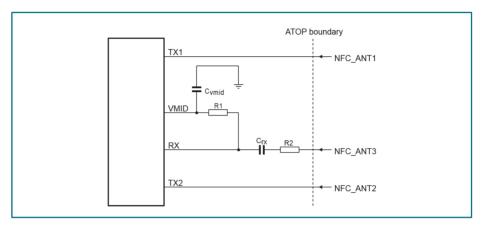

| NFC antenna           |          |       |                                                                                                 |

| NFC_ANT1              | W10      |       | TX1                                                                                             |

| NFC_ANT2              | W11      |       | TX2                                                                                             |

| NFC_ANT3              | V12      |       | RX                                                                                              |

| Cellular antenna      |          |       |                                                                                                 |

| CELL_ANT1             | C1       |       | [15]                                                                                            |

| CELL_ANT2             | A3       |       | [15]                                                                                            |

| GPS antenna           |          |       |                                                                                                 |

| GPS_PAS_ANT           | V1       |       | passive GPS antenna input                                                                       |

| GPS_ACT_ANT           | W3       |       | active antenna input                                                                            |

| GPS_ACT_ANT_BIAS      | T4       |       | active antenna bias (1 V PIN diode drop inside ATOP 3.5G) [16]                                  |

| GPS_PAS_ANT_DIS       | T2       |       | passive antenna disable:<br>3-state: internal LNA enabled;<br>active LOW: internal LNA disabled |

| Industrial test       |          |       |                                                                                                 |

| Baseband JTAG         |          |       |                                                                                                 |

| BB_JTAG_NTRST         | E9       | 1.8   |                                                                                                 |

| Symbol <sup>[1]</sup>                | Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Level | Description <sup>[2]</sup>                               |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------|

| BB_JTAG_TCK                          | G7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.8   |                                                          |

| BB_JTAG_TDI                          | G8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.8   |                                                          |

| BB_JTAG_RTCK                         | G9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.8   |                                                          |

| BB_JTAG_TDO                          | H7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.8   |                                                          |

| BB_JTAG_TMS                          | J7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.8   |                                                          |

| Other baseband debug                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |                                                          |

| BB_BOOTMODE                          | J8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.8   | internal pull up; high = normal boot<br>low = flash mode |

| BB_BOOT_SCUR                         | P12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.8   | used for debug of Secure Boot                            |

| BB_PS_HOLD                           | H8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | used for JTAG debug of application                       |

| BB_PON_RESETN                        | D12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | processor                                                |

| Reserved for future use - Do not con | nect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |                                                          |

|                                      | F15; H9; H12; H16; J16;<br>J17; K12; L17; M2; M4; M5<br>M14; M17; N2; N4; N17;<br>P2; P4; P13; P17; R5; R7;<br>R8; R17; T17; U4; U5; U15<br>U16; V5; V7; V8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ,     |                                                          |

| Ground                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |                                                          |

| GND                                  | A1; A4; A5; A6; A7; A8; A9; A10; A11; A12; A13; A14; A15; A16; A17; A18; A19; B1; B2; B3; B4; B5; B6; B7; B8; B9; B10; B11; B12; B13; B14; B15; B16; B17; B18; B19; C2; C3; C4; C5; C6; C7; C8; C9; C10; C11; C12; C13; C14; C15; C16; C17; C18; C19; D1; D2; D3; D4; D5; D6; D7; D8; D9; D11; D16; D18; D19; E1; E2; E3; E4; E5; E6; E7; E8; E15; E18; E19; F1; F2; F3; F4; F5; F6; F7; F8; F9; F10; F11; F12; F13; F14; F18; F19; G1; G2; G3; G4; G5; G6; G11; G18; G19; H1; H2; H3; H4; H5; H6; H19; J3; J5; J6; J12; J19; K3; K5; K6; K7; K8; K14; K17; L1; L2; L3; L4; L5; L6; L7; L8; L19; M1; M3; M6; M7; M8; M9; N1; N3; N5; N6; N14; P1; P3; P6; P10; R1; R2; R3; R6; R19; T1; T3; T5; T6; U1; U2; U3; U17; U19; V2; V3; V4; V6; V9; V10; V11; W1; W2; W4; W5; W6; W7; W8; W9 |       |                                                          |

80447ST10636A rev.10 - 2015-03-03

| Symbol <sup>[1]</sup> | Pin     | Level Description <sup>[2]</sup> |

|-----------------------|---------|----------------------------------|

| Unused                |         |                                  |

|                       | A2; W13 |                                  |

[1] Pin names aree encoded as follows: MC\_Pxyy\_iii\_jjj\_kkk indicates a microcontroller pin. Each pin can be configured between several functions (typically 4), all mentioned in the pin name:

Pxyy: GPIO yy of GPIO port x;

AD0x: ADC input x;

EINTx: external interrupt x;

MATxy: match output for timer x, channel y; PCAPxy: capture input for PWM x, channel y;

PWMxy: PWM x, channel y;

RDx/TDx: CAN port x; SDx/SCLx: I<sup>2</sup>C-bus x; TXx/RXy: UART x;

BB\_xxx indicates a pin connected respectively to baseband; GPS\_xxx indicates a pin connected respectively to GPS/GLONASS;

NFC\_xxx: indicates a pin connected respectively to NFC;

Vxxx\_REF indicates a voltage reference – no current should be drawn from this pin;

Vxxx\_SNK indicates a voltage sink – current is drawn by this pin;

Vxxx\_SRC indicates a current source – current can be drawn from this pin.

- [2] Only the main function is described for microcontroller pins, but all functions available for a given pin can be found in its name.

- [3] 5 V tolerant pad providing digital I/O functions (with TTL levels and hysteresis) and analog input. When configured as an ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant.

- [4] SSP0 is used internally and therefore is not available for customer application.

- [5]  $\,$  5 V tolerant pad providing digital I/O functions with TTL levels and hysteresis.

- [6] V14 and N11 optionally connected to BB\_UART\_RX/BB\_UART\_TX for debugging.

- [7] Open-drain 5 V tolerant digital I/O pad, compatible with I<sup>2</sup>C-bus 400 kHz specification. This pad requires an external pull up to provide output functionality. When power is switched off, this pin is connected to the I<sup>2</sup>C-bus and does not disturb the I<sup>2</sup>C-bus lines. Open-drain configuration applies to all functions on this pin.

- [8] 5 V tolerant pad with 5 ns glitch filter providing digital I/O functions with TTL levels and hysteresis.

- [9] Pad provides digital I/O and USB functions. It is designed in accordance with the USB specification, revision 2.0 (Full-speed and Low-speed mode only). This pad is not 5 V tolerant.

- [10] 5 V tolerant pad providing digital I/O with TTL levels and hysteresis and analog output function. When configured as the DAC output, digital section of the pad is disabled.

- [11] 5 V tolerant pad providing digital I/O functions with TTL levels and hysteresis. Internal pull up and pull down resistors disabled.

- [12] 5 V tolerant pad providing digital I/O functions with TTL levels and hysteresis and internal pull up resistor.

- [13] The VBAT\_SNK and VBAT\_PA\_SNK pins should be supplied only whenever VBAT\_MC\_SNK is supplied.

- [14] 5 V tolerant pad with 20 ns glitch filter providing digital I/O function with TTL levels and hysteresis.

- [15] Cellular antennas switchable under control of the utility processor.

- [16] A minimum current of 1 mA is required to minimize insertion loss. Maximum rating pin diode 100 mA.

80447ST10636A rev.10 - 2015-03-03

## 7.2.2 Internal pins list

Table 3 lists a number of internal pins controlled by the Utility Processor that are of interest to ATOP 3.5G application programmers. Most of these pins are controlled by low-level software drivers provided by TELIT and so should not be controlled directly. They are there described only for reference.

Table 3 Internal microcontroller pins, controlled by TELIT-provided libraries

All these pins are controlled via TELIT-provided libraries and should not be used/controlled directly in any way.

| Pin name    | <b>GPIO</b> number | Description                                                                                                                                                                                                                                                            |  |  |  |

|-------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BB_RESETN   | P1.25              | 0 = reset application processor, otherwise should be left floating                                                                                                                                                                                                     |  |  |  |

| BB_POK      | P1.28              | 0 = enable application processor                                                                                                                                                                                                                                       |  |  |  |

| BB_SSI[3:0] | P1.20              | serial communication channel                                                                                                                                                                                                                                           |  |  |  |

|             | P1.21              |                                                                                                                                                                                                                                                                        |  |  |  |

|             | P1.23              |                                                                                                                                                                                                                                                                        |  |  |  |

|             | P1.24              |                                                                                                                                                                                                                                                                        |  |  |  |

| BB_SDB[4:0] | P2.0               | internal communication channel                                                                                                                                                                                                                                         |  |  |  |

|             | P2.1               |                                                                                                                                                                                                                                                                        |  |  |  |

|             | P2.7               |                                                                                                                                                                                                                                                                        |  |  |  |

|             | P2.8               |                                                                                                                                                                                                                                                                        |  |  |  |

|             | P3.26              |                                                                                                                                                                                                                                                                        |  |  |  |

| ANT_SW      | P3.25              | antenna switch                                                                                                                                                                                                                                                         |  |  |  |

| BB_UART_RX  | P4.28              | BB UART internally connected to MC UART3 by means of level                                                                                                                                                                                                             |  |  |  |

| BB_UART_TX  | P4.29              | shifter                                                                                                                                                                                                                                                                |  |  |  |

| INT_TEMP    | P1.31              | ADC input to internal temperature sensor. A TELIT-provided function call converts value to °C. For more information see section 12.1.                                                                                                                                  |  |  |  |

| I2C_SDA     | P0.19 [1]          | I <sup>2</sup> C bus to SmartMX security processor bridge                                                                                                                                                                                                              |  |  |  |

| I2C_SCL     | P0.20 [1]          |                                                                                                                                                                                                                                                                        |  |  |  |

| I2C_GATE    | P2.1 [1]           | SmartMX security processor bridge control line. This is used to switch the SmartMX data communication channel between the base band and the Utility Processor (see Figure 3). This is shared with one of the BB_SDB pins. For detailed usage instructions, see Ref 12. |  |  |  |

| SMX_NRESET  | P1.26 [1]          | SmartMX security processor reset line                                                                                                                                                                                                                                  |  |  |  |

| RFU         | P1.27              | 32KHz tree distribution                                                                                                                                                                                                                                                |  |  |  |

<sup>[1]</sup> Only for OM1230/1X0 and OM12030/2X0, with X as defined in Section 5. On all other ATOP 3.5G variants this pin is RFU.

80447ST10636A rev.10 - 2015-03-03

## 8 Functional description

## 8.1 Utility Processor

The LPC1768 Utility Processor is responsible for tasks such as:

- booting the system

- · handling RTC and regular wake-up

- interfacing with external sensors, display, buttons via I<sup>2</sup>C-bus, SPI-bus, UART, ...

- communicating with others car's units via CAN, UART, Ethernet, ...

- controlling operator access for firmware upgrade, data retrieval via USB, UART, ...

- managing eCall access through the lower layers of the application processor. Due to license restrictions, only service calls are allowed from the J9 VM, no eCalls.

- · monitoring internal thermal sensor

Except for a few services provided by TELIT to handle communication between the applications running on the Virtual Machine and virtualized external devices, the Utility Processor is completely available to the application developer.

## 8.1.1 General features

- ARM Cortex-M3 microcontroller, running up to 100 MHz

- 512 KB on-chip Flash Program Memory with In-System Programming (ISP) and In-Application Programming (IAP) capabilities. Single Flash sector or full-chip erase in 100 ms and 256 bytes programming in 1 ms. Flash program memory is on the ARM local bus for high performance CPU access

- o 10000 erase cycles<sup>4</sup>

- o 10 years retention powered on; 20 years powered off

- o First 16 erase block are 4 KB large, others are 32 KB large

- 64 KB RAM memory:

- 32 KB Static RAM with local code/data bus for high-performance CPU access

- 2 \* 16 KB Static RAM blocks with separate access paths for higher throughput, for Ethernet, USB, DMA memory as well as for CPU code and data

- These SRAM blocks may be used for Ethernet, USB, and DMA memory, as well as for general-purpose CPU instruction and data storage for general-purpose SRAM

- Multilayer AHB matrix interconnect with separate bus for each AHB master, providing simultaneous DMA and program execution from on-chip flash with no contention between these functions

- Nested Vectored Interrupt Controller (NVIC), supporting up to 33 vectored interrupts

- 8 channel General Purpose DMA controller (GPDMA) on the AHB multilayer matrix that can be used with the SSP, serial interfaces, the I2S-bus port, as well as for memory-tomemory transfers

<sup>&</sup>lt;sup>4</sup> If data needs to be saved regularly by utility processor, it is advised to use an external EEPROM connected to I<sup>2</sup>C-bus or SPI-bus.

- Serial interfaces available externally:

- 3 UARTs with fractional baud rate generation, one with modem control I/O, one with IrDA support, all with FIFO. These reside on the APB-bus

- 1 SSP controller with FIFO and multi-protocol capabilities, as well as a SPI port, sharing its interrupt. The SSP controller can be used with the GPDMA controller and reside on the APB-bus

- 2 I<sup>2</sup>C-bus interfaces reside on the APB-bus. The I<sup>2</sup>C-bus interfaces are expansion I<sup>2</sup>C-bus interfaces with standard port pins

- I<sup>2</sup>S-bus (Inter-IC Sound) interface for digital audio input or output, residing on the APB bus. The I<sup>2</sup>S-bus interface can be used with the GPDMA

- o 2 channels with Acceptance Filter/FullCAN mode residing on the APB-bus

- High-speed serial interfaces

- USB 2.0 Full-speed Device/Host/OTG controller with on-chip PHY and associated DMA controller

- Ethernet MAC with RMII interface and dedicated DMA controller

- o 2 CAN channels

- Other APB peripherals

- o 12-bit A/D converter with input multiplexing among 7 external pins

- o 10-bit D/A converter with DMA support

- 4 general-purpose timers with a total of 8 capture inputs and ten compare output pins each. Each timer block has an external count input

- 1 PWM/Timer block with support for three-phase motor control

- Real-Time Clock (RTC) with separate power pin; clock source can be the RTC oscillator or the APB clock oscillator

- Watchdog Timer: the watchdog timer can be clocked from the internal RC oscillator, the RTC oscillator or the APB clock

- Standard ARM Test/Debug interface for compatibility with existing tools

- 4 reduced power modes: Sleep mode, Deep-sleep mode, Power-down mode and Deep Power-down mode

- 4 external interrupt inputs. In addition every PORT0/2 pin can be configured as an edge sensing interrupt

- Processor wake-up from Power-down mode via any interrupt able to operate during Power-down mode (includes external interrupts, RTC interrupt)

- Brownout detection with separate thresholds for interrupt and forced reset

- On-chip Power-On Reset

- On-chip crystal oscillator with an operating range of 1 MHz to 25 MHz

- For CAN and USB, a clock generated internally to ATOP 3.5G is provided or an external crystal can be used

- On-chip PLL allows CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. May be run from the main oscillator, the internal RC oscillator or the RTC oscillator

- Versatile pin function selections allow more possibilities for using on-chip peripheral functions

80447ST10636A rev.10 - 2015-03-03

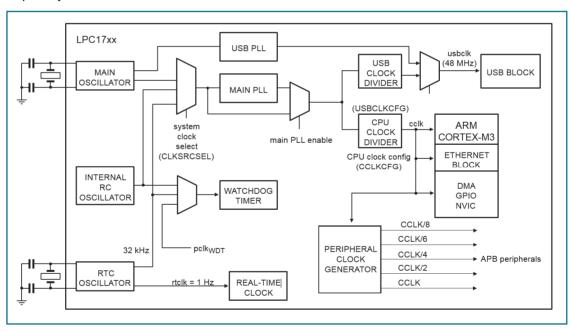

#### 8.1.2 Utility Processor block diagram

Figure 5 LPC1768 block diagram

**Remark:** Some interfaces, such as 1 UART, 1 I<sup>2</sup>C-bus, 1 SSP are not available externally, as they are used within ATOP 3.5G. For more details, refer to Section 7.2.2.

80447ST10636A rev.10 - 2015-03-03

#### 8.1.3 Ethernet

The Ethernet block supports bus clock rates of up to 100 MHz. It contains a full featured 10 Mbit/s or 100 Mbit/s Ethernet MAC designed to provide optimized performance by using DMA hardware acceleration. Features include a generous suite of control registers, half or full-duplex operation, flow control, control frames, hardware acceleration for transmit retry, receive packet filtering and wake-up on LAN activity. Automatic frame transmission and reception with scatter-gather DMA off-loads many operations from the CPU.

The Ethernet block and the CPU share the ARM Cortex M3 D-CODE and system bus through the AHB-multilayer matrix to access the various on-chip SRAM blocks for Ethernet data, control and status information.

The Ethernet block interfaces between an off-chip Ethernet PHY using the Reduced MII (RMII) protocol and the on-chip Media Independent Interface Management (MIIM) serial bus.

#### 8.1.4 USB

Device and host controller with on-chip PHY.

#### 8.1.4.1 USB device controller

This controller enables Full-speed (12 Mbit/s) data exchange with a USB Host controller. It consists of a register interface, serial interface engine, endpoint buffer memory and a DMA controller. The serial interface engine decodes the USB data stream and writes data to the appropriate endpoint buffer. The status of a completed USB transfer or error condition is indicated via status registers. If enabled, an interrupt is also generated. When enabled, the DMA controller transfers data between the endpoint buffer and the on-chip SRAM.

#### 8.1.4.2 USB host controller

This controller enables full- and low-speed data exchange with USB devices attached to the bus. It consists of a register interface, a serial interface engine and a DMA controller. The register interface complies with the OHCI specification.

#### 8.1.5 CAN

#### 8.1.5.1 Description

The Controller Area Network (CAN) is a serial communications protocol which efficiently supports distributed real-time control with a very high level of security. Its application domain ranges from high-speed networks to low-cost multiplex wiring. The CAN block is intended to support multiple CAN buses simultaneously, allowing the device to be used as a gateway, switch or router among a number of CAN buses in industrial or automotive applications.

### **8.1.5.2** Features

- 2 CAN controllers and buses

- Data rates to 1 Mbit/s on each bus

- 32-bit register and RAM access

- Compatible with CAN specification 2.0B, ISO 11898-1

- Global Acceptance Filter recognizes 11- and 29-bit receive identifiers for all CAN buses

- Acceptance Filter can provide FullCAN-style automatic reception for selected Standard Identifiers

- FullCAN messages can generate interrupts

80447ST10636A rev.10 - 2015-03-03

#### 8.1.6 Power-saving modes

#### 8.1.6.1 Peripheral and clock control

As shown in Figure 6, the CPU clock rate can also be controlled as needed by changing clock sources, reconfiguring PLL values and/or altering the CPU clock divider value. This allows a trade-off of power versus processing speed based on application requirements. In addition, Peripheral Power Control allows shutting down the clocks to individual on-chip peripherals, allowing fine-tuning of power consumption by eliminating all dynamic power use in any peripherals that are not required for the application.

The LPC1768 includes three independent oscillators. These are the main oscillator, the IRC oscillator and the RTC oscillator. Each oscillator can be used for more than one purpose as required in a particular application. Any of the 3-clock sources can be chosen by software to drive the main PLL and ultimately the CPU.

Following reset, the LPC1768 operates from the Internal RC oscillator until switched by software. This allows systems to operate without any external crystal and the boot loader code to operate at a known frequency. Main oscillator is driven by an optional external crystal on customer board. Its presence might be required if an accurate clock is necessary, for instance for USB or HS CAN compliancy.

Figure 6 LPC1768 clock generation

## 8.1.6.2 Power modes

The LPC1768 supports various power control features. There are 4 special modes of processor power reduction:

- Sleep mode

- Deep sleep mode

- Power-down mode

- Deep power-down mode

**ATOP3.5G Product Description** 80447ST10636A rev.10 - 2015-03-03

The CPU clock rate may also be controlled as needed by changing clock sources, reconfiguring PLL values and/or altering the CPU clock divider value. This allows a trade-off of power versus processing speed based on application requirements. In addition, Peripheral Power Control allows shutting down the clocks to individual on-chip peripherals, allowing fine-tuning of power consumption by eliminating all dynamic power use in any peripherals that are not required for the application. Each of the peripherals has its own clock divider which provides even better power control.

An integrated PMU (Power Management Unit) automatically adjusts internal regulators to minimize power consumption during Sleep mode, Deep sleep mode, Power-down mode and Deep power-down mode.

The LPC1768 also implements a separate power domain to allow turning off power to the bulk of the device while maintaining operation of the RTC and a small set of registers for storing data during any of the Power-down modes.

**Sleep mode:** When Sleep mode is entered, the clock to the core is stopped. Resumption from the Sleep mode does not need any special sequence but re-enabling the clock to the ARM core.

In Sleep mode, execution of instructions is suspended until either a Reset or interrupt occurs. Peripheral functions continue operation during Sleep mode and may generate interrupts to cause the processor to resume execution. Sleep mode eliminates dynamic power used by the processor itself, memory systems and related controllers and internal buses.

**Deep sleep mode:** In Deep sleep mode, the oscillator is shut down and the chip receives no internal clocks. The processor state and registers, peripheral registers and internal SRAM values are preserved throughout Deep sleep mode and the logic levels of chip pins remain static. The output of the IRC is disabled but the IRC is not powered down for a fast wake-up later.

The RTC oscillator is not stopped because the RTC interrupts may be used as the wake-up source. The PLL is automatically turned off and disconnected.

The Deep sleep mode can be terminated and normal operation resumed by either a reset or certain specific interrupts that are able to function without clocks. Since all dynamic operation of the chip is suspended, this mode reduces chip power consumption to a very low value. Power to the flash memory is left on in Deep sleep mode, allowing a very quick wake-up.

**Power-down mode:** Power-down mode does everything that Deep sleep mode does, but also turns off the power to the IRC oscillator and flash memory. This saves more power but requires waiting for resumption of flash operation before code execution or data access can resume.

**Deep power-down mode:** The Deep power-down mode can only be entered from the RTC block. In Deep power-down mode, power is shut off to the entire chip except for the RTC module and the RESET pin. The LPC1768 can wake up from Deep power-down mode via the RESET pin or an alarm time match event of the RTC.

**Wake-up interrupt controller:** The wake-up Interrupt Controller (WIC) allows the CPU to wake up automatically from any enabled priority interrupt that can occur while the clocks are stopped in Deep sleep mode, Power-down mode and Deep power-down mode.

The WIC works with the Nested Vectored Interrupt Controller (NVIC). When the CPU enters Deep sleep mode, Power-down mode or Deep power-down mode, the NVIC sends a mask of the current interrupt situation to the WIC. This mask includes all of the interrupts that are both enabled and of sufficient priority to be serviced immediately. With this information, the WIC notices when one of the interrupts has occurred and then it wakes up the CPU. The WIC eliminates the need to periodically wake up the CPU and poll the interrupts.

80447ST10636A rev.10 - 2015-03-03

#### 8.1.7 RTC

The RTC is designed to have low-power consumption: less than 1  $\mu$ A. The RTC typically runs from the main chip power supply, conserving battery power while the rest of the device is powered up. When operating from a battery, the RTC is operational down to 2.1 V. Battery power can be provided from a standard 3 V Lithium button cell.

An ultra-low power 32 kHz oscillator provides a 1 Hz clock to the time counting portion of the RTC, moving most of the power consumption out of the time counting function.

The RTC contains a small set of backup registers (20 bytes) for holding data while the main part of the LPC1768 is powered off.

The RTC includes an alarm function that can wake up the LPC1768 from all reduced power modes with a time resolution of 1 s.

## 8.2 Application processor

The application processor is running a Virtual Machine (VM) able to interpret Java applications. It is running on the main CPU of the UMTS/EDGE/GPRS/GSM baseband and offers:

- portability to numerous platforms

- maintainability via secure download and update mechanisms

- large virtualized feature set, such as:

- secure network access (https)

- cryptography

- Near Field Communication (NFC)<sup>2</sup>

- Java VM with the following features:

- o High performance J2ME Virtual Machine

- based on IBM J9

- Connected Device Configuration 1.1.2

- CDC Foundation Profile 1.1.2, extended with the following Telit API's

- o Wireless Messaging

- o Location

- Audio playback

- Telephony

- o Contactless communication including secure element access

- o Power management

- Service calls

- Firmware Update over The Air

- Connection to microcontroller via message passing

As for memory, the application processor features:

- 256 MB of NAND flash memory available to store application data and code

- 128 MB of volatile memory for application data (LPDDR)

80447ST10636A rev.10 - 2015-03-03

## 8.3 Position processing

#### 8.3.1 Key features

ATOP 3.5 G features GNSS reception used for positioning services. This support is provided in software integrated on the application processor with the following key features:

- Supports both GPS and GLONASS

- "All in view" tracking capability

- Dual antenna support with internal switching:

- o passive antenna input with internal separate LNA

- o active antenna input with internal LNA bypass

- Supports following Satellite Based Augmentation Systems: WAAS, EGNOS, MSAS

- Receiver Autonomous Integrity Monitoring (RAIM) & Fault Detection and Exclusion (FDE) support

- Support of assistance data (Ephemerides, location, time...) provided by customer application to ensure faster Time To First Fix (TTFF)

- 1 Pulse Per Second (1PPS) output for synchronization with GPS system clock

- Software upgradable

- CEP50 < 2 m</li>

#### 8.3.2 Sensitivity

Table 4 shows acquisition and tracking sensitivity measurements for a passive antenna.

Table 4 Sensitivity

| Symbol                | Parameter                               | Conditions                            | Min | Тур  | Max | Unit |

|-----------------------|-----------------------------------------|---------------------------------------|-----|------|-----|------|

| t <sub>TTFF</sub>     | time to first fix time                  | open sky, hot start, -130 dBm signal  | -   | 1.5  | -   | S    |

|                       |                                         | open sky,warm start, -130 dBm signal  | -   | < 27 | -   | S    |

|                       |                                         | open sky, cold start, -130 dBm signal | -   | < 36 | -   | S    |

| $P_{i(acq)}$          | ni(acq) minimum acquisition             | ephemeris decode, cold start          | -   | -145 | -   | dBm  |

|                       | input power                             | hot start                             | -   | -152 | -   | dBm  |