**TRF7970A**

SLOS743K - AUGUST 2011 - REVISED APRIL 2014

# TRF7970A Multiprotocol Fully Integrated 13.56-MHz RFID and Near Field Communication (NFC) Transceiver IC

#### 1 Device Overview

#### 1.1 Features

- Supports Near Field Communication (NFC) Standards NFCIP-1 (ISO/IEC 18092) and NFCIP-2 (ISO/IEC 21481)

- Completely Integrated Protocol Handling for ISO15693, ISO18000-3, ISO14443A/B, and FeliCa™

- Integrated Encoders, Decoders, and Data Framing for NFC Initiator, Active and Passive Target Operation for All Three Bit Rates (106 kbps, 212 kbps, 424 kbps) and Card Emulation

- RF Field Detector With Programmable Wake-Up Levels for NFC Passive Transponder Emulation Operation

- RF Field Detector for NFC Physical Collision Avoidance.

- Integrated State Machine for ISO14443A Anticollision (Broken Bytes) Operation (Transponder Emulation or NFC Passive Target)

- Input Voltage Range: 2.7 VDC to 5.5 VDC

#### 1.2 Applications

- Mobile Devices (Tablets, Handsets)

- Secure Pairing ( Bluetooth<sup>®</sup>, Wi-Fi<sup>®</sup>, Other Paired Wireless Networks)

- Public Transport or Event Ticketing

- · Passport or Payment (POS) Reader Systems

- Programmable Output Power: +20 dBm (100 mW), +23 dBm (200 mW)

- Programmable I/O Voltage Levels From 1.8 VDC to 5.5 VDC

- Programmable System Clock Frequency Output (RF, RF/2, RF/4) from 13.56-MHz or 27.12-MHz Crystal or Oscillator

- Integrated Voltage Regulator Output for Other System Components (MCU, Peripherals, Indicators), 20 mA (Max)

- · Programmable Modulation Depth

- Dual Receiver Architecture With RSSI for Elimination of "Read Holes" and Adjacent Reader System or Ambient In-Band Noise Detection

- Programmable Power Modes for Ultra Low-Power System Design (Power Down <1 μA)</li>

- Parallel or SPI Interface (With 127-Byte FIFO)

- Temperature Range: –40°C to 110°C

- 32-Pin QFN Package (5 mm x 5 mm)

- Short-Range Wireless Communication Tasks (Firmware Updates)

- Product Identification or Authentication

- Medical Equipment or Consumables

- · Access Control, Digital Door Locks

- · Sharing of Electronic Business Cards

## 1.3 Description

The TRF7970A device is an integrated analog front end and data-framing device for a 13.56-MHz RFID and Near Field Communication (NFC) system. Built-in programming options make the device suitable for a wide range of applications for proximity and vicinity identification systems.

The device can perform in one of three modes: RFID and NFC reader, NFC peer, or in card emulation mode. Built-in user-configurable programming options make the device suitable for a wide range of applications. The TRF7970A device is configured by selecting the desired protocol in the control registers. Direct access to all control registers allows fine tuning of various reader parameters as needed.

Documentation, reference designs, EVM, and source code TI MSP430 $^{\text{TM}}$  MCUs or ARM $^{\text{®}}$  MCUs are available.

#### **Device Information**

| PART NUMBER | PACKAGE   | BODY SIZE   |

|-------------|-----------|-------------|

| TRF7970ARHB | VQFN (32) | 5 mm x 5 mm |

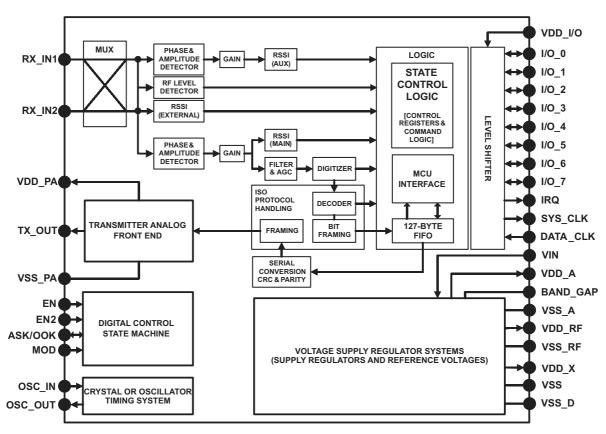

## 1.4 Functional Block Diagram

Figure 1-1 shows the block diagram.

Figure 1-1. Block Diagram

# **Table of Contents**

| 1 | Devi | ce Overview                       | <u>1</u>      |   | 6.8  | Transmitter – Digital Section                    | 28        |

|---|------|-----------------------------------|---------------|---|------|--------------------------------------------------|-----------|

|   | 1.1  | Features                          | 1             |   | 6.9  | Transmitter – External Power Amplifier and       |           |

|   | 1.2  | Applications                      | 1             |   |      | Subcarrier Detector                              | 29        |

|   | 1.3  | Description                       | 1             |   | 6.10 | TRF7970A IC Communication Interface              | 30        |

|   | 1.4  | Functional Block Diagram          | 2             |   | 6.11 | Special Direct Mode for Improved MIFARE™         |           |

| 2 | Revi | sion History                      | _             |   |      | Compatibility                                    | _         |

| 3 |      | ce Characteristics                |               |   | 6.12 | NFC Modes                                        |           |

| 4 |      | ninal Configuration and Functions | _             |   | 6.13 | Direct Commands from MCU to Reader               |           |

| • | 4.1  | Pin Assignments                   |               |   | 6.14 | Register Description                             | <u>55</u> |

|   | 4.2  | Terminal Functions                | _             | 7 |      | ication Schematic and Layout                     |           |

| _ |      |                                   | _             |   | Cons | siderations                                      | <u>75</u> |

| 5 | •    | cifications                       | _             |   | 7.1  | TRF7970A Reader System Using Parallel            |           |

|   | 5.1  | Absolute Maximum Ratings          | _             |   |      | Microcontroller Interface                        | <u>75</u> |

|   | 5.2  | Recommended Operating Conditions  | 9             |   | 7.2  | TRF7970A Reader System Using SPI With SS         | 70        |

|   | 5.3  | Electrical Characteristics        | 10            |   |      | Mode                                             | _         |

|   | 5.4  | Handling Ratings                  | <u>11</u>     |   | 7.3  | Layout Considerations                            |           |

|   | 5.5  | Thermal Characteristics           | 11            |   | 7.4  | Impedance Matching TX_Out (Pin 5) to 50 $\Omega$ |           |

|   | 5.6  | Switching Characteristics         | 11            |   | 7.5  | Reader Antenna Design Guidelines                 |           |

| 6 | Deta | iled Description                  | <u></u><br>12 | 8 | Devi | ce and Documentation Support                     | 80        |

|   | 6.1  | Overview                          |               |   | 8.1  | Documentation Support                            | 80        |

|   | 6.2  | System Block Diagram              | _             |   | 8.2  | Community Resources                              | 80        |

|   | 6.3  | Power Supplies                    |               |   | 8.3  | Trademarks                                       | 80        |

|   | 6.4  | Receiver – Analog Section         |               |   | 8.4  | Electrostatic Discharge Caution                  | 80        |

|   | 6.5  | Receiver – Digital Section        |               |   | 8.5  | Glossary                                         |           |

|   |      | 9                                 | _             | 9 | Mecl | nanical Packaging and Orderable                  |           |

|   | 6.6  | Oscillator Section                |               | - |      | mation                                           | 80        |

|   | 6.7  | Transmitter – Analog Section      | 28            |   | 9.1  | Packaging Information                            |           |

|   |      |                                   |               |   |      |                                                  |           |

# 2 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Ch | nanges from Revision J (February 2014) to Revision K                                                            | Page |

|----|-----------------------------------------------------------------------------------------------------------------|------|

|    | Changed Figure 1-1 to show 127-byte FIFO                                                                        | 2    |

|    | Moved Section 3                                                                                                 |      |

|    | Changed title of Section 4                                                                                      |      |

|    | Changed title of Section 5                                                                                      | ç    |

|    | - Added ASK/OOK and MOD to $V_{\text{IL}}$ and $V_{\text{IH}}$                                                  | 9    |

|    | Moved Section 5.3                                                                                               | 10   |

|    | Changed V <sub>DD A</sub> TYP value from 3.5 V to 3.4 V                                                         | 10   |

|    | Moved Section 5.4                                                                                               |      |

|    | Added V <sub>(ESD)</sub> MIN values, test specifications, and notes                                             |      |

|    | Changed title of Section 5.5 from Dissipation Ratings to Thermal Characteristics                                |      |

|    | Moved Section 5.6                                                                                               |      |

|    | Changed title of Section 6                                                                                      |      |

|    | Moved previous Section 3, Device Overview, to Section 6.1                                                       |      |

|    | • Changed from "By default, the AGC is frozen after" to "By default, the AGC window comparator is set after" .  |      |

|    | Changed from "TX Pulse Length Control register (0x05)" to "TX Pulse Length Control register (0x06)"             |      |

|    | • Changed from "18.8 s" to "18.8 $\mu$ s" in the sentence that starts with "If the register contains all zeros" |      |

|    | Changed Table 6-18 to match Table 6-43                                                                          |      |

|    | Changed command 0x18 to "Test internal RF"                                                                      |      |

|    | Changed command 0x19 to "Test external RF"                                                                      |      |

|    | Moved Section 6.14                                                                                              | 55   |

|    | Changed the sentence that starts "The AGC action is fast" from "finishes after four subcarrier pulses" to       |      |

|    | "finishes within eight subcarrier pulses"                                                                       |      |

|    | Moved Section 7                                                                                                 | _    |

|    | • Deleted previous Section 10, System Design, and moved contents to Section 7.3 through Section 7.5             |      |

|    | Removed references to figure numbers in Figure 7-3                                                              | 78   |

|    |                                                                                                                 |      |

# 3 Device Characteristics

Table 3-1 shows the supported modes of operation for the TRF7970A device.

**Table 3-1. Supported Modes of Operation**

| P2P Initiator or Read      | der/Writer                           | Card En    | nulation | P2P Target |                    |  |

|----------------------------|--------------------------------------|------------|----------|------------|--------------------|--|

| Technology Bit rate (kbps) |                                      | Lechnology |          | Technology | Bit rate<br>(kbps) |  |

| NFC-A/B (ISO14443A/B)      | 106, 212, 424,<br>848 <sup>(1)</sup> | NFC-A/B    | 106      | NFC-A      | 106                |  |

| NFC-F (JIS: X6319-4)       | 212, 424                             | N/A        | N/A      | NFC-F      | 212, 424           |  |

| NFC-V (ISO15693)           | 6.7, 26.7                            | N/A        | N/A      | N/A        | N/A                |  |

<sup>(1) 848</sup> kbps only applies to reader/writer mode.

# 4 Terminal Configuration and Functions

# 4.1 Pin Assignments

Figure 4-1 shows the pin assignments for the 32-pin RHB package.

Figure 4-1. 32-Pin RHB Package (Top View)

# 4.2 Terminal Functions

Table 4-1 describes the signals.

**Table 4-1. Terminal Functions**

| TERMINAL            | TERMINAL |          |                                                                                                                                                                                                                                                                                                                                        |  |  |

|---------------------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                | NO.      | TYPE (1) | DESCRIPTION                                                                                                                                                                                                                                                                                                                            |  |  |

| V <sub>DD_A</sub>   | 1        | OUT      | Internal regulated supply (2.7 V to 3.4 V) for analog circuitry                                                                                                                                                                                                                                                                        |  |  |

| V <sub>IN</sub>     | 2        | SUP      | External supply input to chip (2.7 V to 5.5 V)                                                                                                                                                                                                                                                                                         |  |  |

| V <sub>DD_RF</sub>  | 3        | OUT      | Internal regulated supply (2.7 V to 5 V), normally connected to V <sub>DD PA</sub> (pin 4)                                                                                                                                                                                                                                             |  |  |

| V <sub>DD_PA</sub>  | 4        | INP      | Supply for PA; normally connected externally to V <sub>DD RF</sub> (pin 3)                                                                                                                                                                                                                                                             |  |  |

| TX_OUT              | 5        | OUT      | RF output (selectable output power, 100 mW or 200 mW, with V <sub>DD</sub> = 5 V)                                                                                                                                                                                                                                                      |  |  |

| V <sub>SS_PA</sub>  | 6        | SUP      | Negative supply for PA; normally connected to circuit ground                                                                                                                                                                                                                                                                           |  |  |

| V <sub>SS_RX</sub>  | 7        | SUP      | Negative supply for RX inputs; normally connected to circuit ground                                                                                                                                                                                                                                                                    |  |  |

| RX_IN1              | 8        | INP      | Main RX input                                                                                                                                                                                                                                                                                                                          |  |  |

| RX_IN2              | 9        | INP      | Auxiliary RX input                                                                                                                                                                                                                                                                                                                     |  |  |

| V <sub>SS</sub>     | 10       | SUP      | Chip substrate ground                                                                                                                                                                                                                                                                                                                  |  |  |

| BAND_GAP            | 11       | OUT      | Bandgap voltage (V <sub>BG</sub> = 1.6 V); internal analog voltage reference                                                                                                                                                                                                                                                           |  |  |

|                     |          |          | Selection between ASK and OOK modulation (0 = ASK, 1 = OOK) for Direct Mode 0 or 1.                                                                                                                                                                                                                                                    |  |  |

| ASK/OOK             | 12       | BID      | Can be configured as an output to provide the received analog signal output.                                                                                                                                                                                                                                                           |  |  |

| IRQ                 | 13       | OUT      | Interrupt request                                                                                                                                                                                                                                                                                                                      |  |  |

|                     |          | INP      | External data modulation input for Direct Mode 0 or 1                                                                                                                                                                                                                                                                                  |  |  |

| MOD                 | 14       | OUT      | Subcarrier digital data output (see registers 0x1A and 0x1B)                                                                                                                                                                                                                                                                           |  |  |

| V <sub>SS_A</sub>   | 15       | SUP      | Negative supply for internal analog circuits; connected to GND                                                                                                                                                                                                                                                                         |  |  |

| V <sub>DD_I/O</sub> | 16       | INP      | Supply for I/O communications (1.8 V to V <sub>IN</sub> ) level shifter. V <sub>IN</sub> should be never exceeded.                                                                                                                                                                                                                     |  |  |

| I/O_0               | 17       | BID      | I/O pin for parallel communication                                                                                                                                                                                                                                                                                                     |  |  |

| I/O_1               | 18       | BID      | I/O pin for parallel communication                                                                                                                                                                                                                                                                                                     |  |  |

|                     |          |          | I/O pin for parallel communication                                                                                                                                                                                                                                                                                                     |  |  |

| I/O_2 19            |          | BID      | TX Enable (in Special Direct Mode)                                                                                                                                                                                                                                                                                                     |  |  |

|                     |          |          | I/O pin for parallel communication                                                                                                                                                                                                                                                                                                     |  |  |

| I/O_3               | 20       | BID      | TX Data (in Special Direct Mode)                                                                                                                                                                                                                                                                                                       |  |  |

|                     |          |          | I/O pin for parallel communication                                                                                                                                                                                                                                                                                                     |  |  |

| I/O_4               | 21       | BID      | Slave Select signal in SPI mode                                                                                                                                                                                                                                                                                                        |  |  |

|                     |          |          | I/O pin for parallel communication                                                                                                                                                                                                                                                                                                     |  |  |

| I/O_5               | 22       | BID      | Data clock output in Direct Mode 1 and Special Direct Mode                                                                                                                                                                                                                                                                             |  |  |

|                     |          |          | I/O pin for parallel communication                                                                                                                                                                                                                                                                                                     |  |  |

| I/O_6               | 23       | BID      | MISO for serial communication (SPI)                                                                                                                                                                                                                                                                                                    |  |  |

|                     |          |          | Serial bit data output in Direct Mode 1 or subcarrier signal in Direct Mode 0                                                                                                                                                                                                                                                          |  |  |

|                     |          |          | I/O pin for parallel communication.                                                                                                                                                                                                                                                                                                    |  |  |

| I/O_7               | 24       | BID      | MOSI for serial communication (SPI)                                                                                                                                                                                                                                                                                                    |  |  |

|                     | 0.5      | IN ID    | Selection of power down mode. If EN2 is connected to $V_{IN}$ , then $V_{DD\ X}$ is active during power                                                                                                                                                                                                                                |  |  |

| EN2                 | 25       | INP      | down mode 2 (for example, to supply the MCU).                                                                                                                                                                                                                                                                                          |  |  |

| DATA_CLK            | 26       | INP      | Data Clock input for MCU communication (parallel and serial)                                                                                                                                                                                                                                                                           |  |  |

| SYS_CLK             | 27       | OUT      | If EN = 1 (EN2 = don't care) the system clock for MCU is configured. Depending on the crystal that is used, options are as follows (see register 0x09):  13.56-MHz crystal: Off, 3.39 MHz, 6.78 MHz, or 13.56 MHz 27.12-MHz crystal: Off, 6.78 MHz, 13.56 MHz, or 27.12 MHz  If EN = 0 and EN2 = 1, then system clock is set to 60 kHz |  |  |

| EN                  | 28       | INP      | Chip enable input (If EN = 0, then chip is in sleep or power-down mode).                                                                                                                                                                                                                                                               |  |  |

|                     | 29       | SUP      | Negative supply for internal digital circuits                                                                                                                                                                                                                                                                                          |  |  |

| V <sub>SS_D</sub>   | 23       | 001      | 110gative supply for internal digital circuits                                                                                                                                                                                                                                                                                         |  |  |

<sup>(1)</sup> SUP = Supply, INP = Input, BID = Bidirectional, OUT = Output

# **Table 4-1. Terminal Functions (continued)**

| TERMINAL          |     | TYPE (1)   | DESCRIPTION                                                                                              |    |    |     |                             |

|-------------------|-----|------------|----------------------------------------------------------------------------------------------------------|----|----|-----|-----------------------------|

| NAME              | NO. | I I PE \ / | DESCRIPTION                                                                                              |    |    |     |                             |

| OSC_OUT           | 30  | OUT        | Crystal or oscillator output                                                                             |    |    |     |                             |

| OSC IN            | 31  | 31         | 31                                                                                                       | 31 | 31 | INP | Crystal or oscillator input |

| OSC_IN            |     |            |                                                                                                          |    |    | 31  | 31                          |

| V <sub>DD_X</sub> | 32  | OUT        | Internally regulated supply (2.7 V to 3.4 V) for digital circuit and external devices (for example, MCU) |    |    |     |                             |

| Thermal Pad       | PAD | SUP        | Chip substrate ground                                                                                    |    |    |     |                             |

# 5 Specifications

# 5.1 Absolute Maximum Ratings (1) (2)

over operating free-air temperature range (unless otherwise noted)

| $V_{\text{IN}}$ | Input voltage range                               | -0.3 V to 6 V                                   |       |

|-----------------|---------------------------------------------------|-------------------------------------------------|-------|

| I <sub>IN</sub> | Maximum current V <sub>IN</sub>                   | 150 mA                                          |       |

| _               | Marian and a second and a second and a second and | Any condition                                   | 140°C |

| IJ              | Maximum operating virtual junction temperature    | Continuous operation, long-term reliability (3) | 125°C |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Operating Conditions are not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to substrate ground terminal V<sub>SS</sub>.

## 5.2 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                        |                                                             | MIN                          | TYP | MAX                          | UNIT |

|-----------------|----------------------------------------|-------------------------------------------------------------|------------------------------|-----|------------------------------|------|

| $V_{IN}$        | Operating input voltage                |                                                             | 2.7                          | 5   | 5.5                          | V    |

| T <sub>A</sub>  | Operating ambient temperature          |                                                             | -40                          | 25  | 110                          | °C   |

| $T_J$           | Operating virtual junction temperature |                                                             | -40                          | 25  | 125                          | °C   |

| V <sub>IL</sub> | Input voltage - logic low              | I/O lines, IRQ, SYS_CLK, DATA_CLK,<br>EN, EN2, ASK/OOK, MOD |                              |     | 0.2 x<br>V <sub>DD_I/O</sub> | V    |

| V <sub>IH</sub> | Input voltage threshold, logic high    | I/O lines, IRQ, SYS_CLK, DATA_CLK,<br>EN, EN2, ASK/OOK, MOD | 0.8 x<br>V <sub>DD_I/O</sub> | ·   |                              | V    |

<sup>(3)</sup> The maximum junction temperature for continuous operation is limited by package constraints. Operation above this temperature may result in reduced reliability or lifetime of the device.

#### **Electrical Characteristics**

TYP operating conditions are T<sub>A</sub> = 25°C, VIN = 5 V, full-power mode (unless otherwise noted) MIN and MAX operating conditions are over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                       | PARAMETER                                             | TEST CONDITIONS                                                                                                                          | MIN | TYP   | MAX | UNIT      |

|-----------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|-----------|

| I <sub>PD1</sub>      | Supply current in Power Down Mode 1                   | All building blocks disabled, including supply-<br>voltage regulators; measured after 500-ms<br>settling time (EN = 0, EN2 = 0)          |     | 0.5   | 5   | μA        |

| I <sub>PD2</sub>      | Supply current in Power Down Mode 2 (Sleep Mode)      | The SYS_CLK generator and $V_{DD\_X}$ remain active to support external circuitry; measured after 100-ms settling time (EN = 0, EN2 = 1) |     | 120   | 200 | μΑ        |

| I <sub>STBY</sub>     | Supply current in stand-by mode                       | Oscillator running, supply-voltage regulators in low-consumption mode (EN = 1, EN2 = x)                                                  |     | 1.9   | 3.5 | mA        |

| I <sub>ON1</sub>      | Supply current without antenna driver current         | Oscillator, regulators, RX and AGC active, TX is off                                                                                     |     | 10.5  | 14  | mA        |

| I <sub>ON2</sub>      | Supply current – TX (half power)                      | Oscillator, regulators, RX and AGC and TX active, P <sub>OUT</sub> = 100 mW                                                              |     | 70    | 78  | mA        |

| I <sub>ON3</sub>      | Supply current – TX (full power)                      | Oscillator, regulators, RX and AGC and TX active, P <sub>OUT</sub> = 200 mW                                                              |     | 130   | 150 | mA        |

| $V_{POR}$             | Power-on reset voltage                                | Input voltage at V <sub>IN</sub>                                                                                                         | 1.4 | 2     | 2.6 | V         |

| $V_{BG}$              | Bandgap voltage (pin 11)                              | Internal analog reference voltage                                                                                                        | 1.5 | 1.6   | 1.7 | V         |

| V <sub>DD_A</sub>     | Regulated output voltage for analog circuitry (pin 1) | V <sub>IN</sub> = 5 V                                                                                                                    | 3.1 | 3.4   | 3.8 | V         |

| V <sub>DD_X</sub>     | Regulated supply for external circuitry               | Output voltage pin 32, V <sub>IN</sub> = 5 V                                                                                             | 3.1 | 3.4   | 3.8 | V         |

| I <sub>VDD_Xmax</sub> | Maximum output current of V <sub>DD_X</sub>           | Output current pin 32, V <sub>IN</sub> = 5 V                                                                                             |     |       | 20  | mA        |

|                       | Antenna driver output resistance (1)                  | Half-power mode, V <sub>IN</sub> = 2.7 V to 5.5 V                                                                                        |     | 8     | 12  | _         |

| R <sub>RFOUT</sub>    |                                                       | Full-power mode, V <sub>IN</sub> = 2.7 V to 5.5 V                                                                                        |     | 4     | 6   | Ω         |

| R <sub>RFIN</sub>     | RX_IN1 and RX_IN2 input resistance                    |                                                                                                                                          | 4   | 10    | 20  | kΩ        |

| V <sub>RF_INmax</sub> | Maximum RF input voltage at RX_IN1 and RX_IN2         | V <sub>RF_INmax</sub> should not exceed V <sub>IN</sub>                                                                                  |     | 3.5   |     | $V_{pp}$  |

|                       | Minimum RF input voltage_at RX_IN1 and                | f <sub>SUBCARRIER</sub> = 424 kHz                                                                                                        |     | 1.4   | 2.5 |           |

| $V_{RF\_INmin}$       | RX_IN2 (input sensitivity) (2)                        | f <sub>SUBCARRIER</sub> = 848 kHz                                                                                                        |     | 2.1   | 3   | $mV_{pp}$ |

| f <sub>SYS_CLK</sub>  | SYS_CLK frequency                                     | In power mode 2, EN = 0, EN2 = 1                                                                                                         | 25  | 60    | 120 | kHz       |

| f <sub>C</sub>        | Carrier frequency                                     | Defined by external crystal                                                                                                              |     | 13.56 |     | MHz       |

| t <sub>CRYSTAL</sub>  | Crystal run-in time                                   | Time until oscillator stable bit is set (register 0x0F) <sup>(3)</sup>                                                                   |     | 3     |     | ms        |

| f <sub>D_CLKmax</sub> | Maximum DATA_CLK frequency <sup>(4)</sup>             | Depends on capacitive load on the I/O lines, recommendation is 2 MHz <sup>(4)</sup>                                                      | 2   | 8     | 10  | MHz       |

| R <sub>OUT</sub>      | Output resistance I/O_0 to I/O_7                      |                                                                                                                                          |     | 500   | 800 | Ω         |

| R <sub>SYS_CLK</sub>  | Output resistance R <sub>SYS CLK</sub>                |                                                                                                                                          |     | 200   | 400 | Ω         |

<sup>(1)</sup> Antenna driver output resistance

Measured with subcarrier signal at RX\_IN1 or RX\_IN2 and measured the digital output at MOD pin with register 0x1A bit 6 = 1.

<sup>(3)</sup> Depends on the crystal parameters and components

Recommended DATA\_CLK speed is 2 MHz. Higher data clock depends on the capacitive load. Maximum SPI clock speed should not exceed 10 MHz. This clock speed is acceptable only when external capacitive load is less than 30 pF. MISO driver has a typical output resistance of 400  $\Omega$  (12-ns time constant when 30-pF load used).

## 5.4 Handling Ratings

|                  |                          |                                                                               | MIN  | MAX | UNIT |

|------------------|--------------------------|-------------------------------------------------------------------------------|------|-----|------|

| T <sub>STG</sub> | Storage temperature rang | ne e                                                                          | -55  | 150 | °C   |

| $V_{(ESD)}$      | Electrostatic discharge  | Human-Body Model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)              | -2   | 2   | kV   |

|                  |                          | Charged-Device Model (CDM), per JEDEC specification JESD22-C101, all pins (2) | -500 | 500 | V    |

|                  |                          | Machine Model (MM)                                                            | -200 | 200 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as 2 kV may actually have higher performance.

#### 5.5 Thermal Characteristics

| DACKACE      | 0               | Δ (1)    | POWER RATING <sup>(2)</sup> |                       |  |  |

|--------------|-----------------|----------|-----------------------------|-----------------------|--|--|

| PACKAGE      | A <sup>1C</sup> | θJA'''   | T <sub>A</sub> ≤ 25°C       | T <sub>A</sub> ≤ 85°C |  |  |

| RHB (32 pin) | 31°C/W          | 36.4°C/W | 2.7 W                       | 1.1 W                 |  |  |

<sup>(1)</sup> This data was taken using the JEDEC standard high-K test PCB.

## 5.6 Switching Characteristics

TYP operating conditions are  $T_A = 25^{\circ}C$ , VIN = 5 V, full-power mode (unless otherwise noted) MIN and MAX operating conditions are over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                       | PARAMETER                                                                             | TEST CONDITIONS                                            | MIN | TYP  | MAX | UNIT |

|-----------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------|-----|------|-----|------|

| t <sub>LO/HI</sub>    | DATA_CLK time high or low, one half of DATA_CLK at 50% duty cycle                     | Depends on capacitive load on the I/O lines <sup>(1)</sup> | 250 | 62.5 | 50  | ns   |

| t <sub>STE,LEAD</sub> | Slave select lead time, slave select low to clock                                     |                                                            |     | 200  |     | ns   |

| t <sub>STE,LAG</sub>  | Slave select lag time, last clock to slave select high                                |                                                            |     | 200  |     | ns   |

| t <sub>STE,DIS</sub>  | Slave select disable time, slave select rising edge to next slave select falling edge |                                                            | 300 |      |     | ns   |

| t <sub>SU,SI</sub>    | MOSI input data setup time                                                            |                                                            | 15  |      |     | ns   |

| t <sub>HD,SI</sub>    | MOSI input data hold time                                                             |                                                            | 15  |      |     | ns   |

| t <sub>SU,SO</sub>    | MISO input data setup time                                                            |                                                            | 15  |      |     | ns   |

| t <sub>HD,SO</sub>    | MISO input data hold time                                                             |                                                            | 15  |      |     | ns   |

| t <sub>VALID,SO</sub> | MISO output data valid time                                                           | DATA_CLK edge to MISO valid, C <sub>L</sub> ≤ 30 pF        | 30  | 50   | 75  | ns   |

<sup>(1)</sup> Recommended DATA\_CLK speed is 2 MHz. Higher data clock depends on the capacitive load. Maximum SPI clock speed should not exceed 10 MHz. This clock speed is acceptable only when external capacitive load is less than 30 pF. MISO driver has a typical output resistance of 400 Ω (12-ns time constant when 30-pF load used).

<sup>(2)</sup> JEĎEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as 500 V may actually have higher performance.

<sup>(2)</sup> Power rating is determined with a junction temperature of 125°C. This is the point where distortion starts to increase substantially. Thermal management of the final PCB should strive to keep the junction temperature at or below 125°C for best performance and long-term reliability.

## **Federal Communication Commission Interference Statement**

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

#### **FCC Caution:**

- Any changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate this equipment.

- This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter.

## **Radiation Exposure Statement:**

The product is a low power device and its output power is lower than FCC/IC SAR exemption level. This module can be used with **Tablet: ZX70**.

#### This device is intended only for OEM integrators under the following conditions:

- 1) The transmitter module may not be co-located with any other transmitter or antenna. The co-transmitting with other radio will need a separate evaluation.

- 2) Module approval valid only when this module is installed in the tested host "**Tablet: ZX70**".

As long as 2 conditions above are met, further transmitter test will not be required. However, the OEM integrator is still responsible for testing their end-product for any additional compliance requirements required with this module installed

**IMPORTANT NOTE:** In the event that these conditions <u>cannot be met</u> (for example certain laptop configurations or co-location with another transmitter), then the FCC/IC authorization is no longer considered valid and the FCC ID/IC <u>cannot</u> be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining a separate FCC/IC authorization.

## **End Product Labeling**

The final end product must be labeled in a visible area with the following: "Contains FCC ID: QYLZX70N and IC: 10301A-ZX70N". The grantee's FCC ID/IC can be used only when all FCC/IC compliance requirements are met.

#### **Manual Information to the End User**

The OEM integrator has to be aware not to provide information to the end user regarding how to install or remove this RF module in the user's manual of the end product which integrates this module.

The end user manual shall include all required regulatory information/warning as show in this manual.

## **Industry Canada statement**

- This device complies with Industry Canada license-exempt RSS standard(s).

Operation is subject to the following two conditions:

- 1) this device may not cause interference, and

- this device must accept any interference, including interference that may cause undesired operation of the device.

- Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes:

- 1) l'appareil ne doit pas produire de brouillage, et

- l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

- This Class B digital apparatus complies with Canadian ICES-003.

- Cet appareil numérique de la classe B est conforme à la norme NMB-003 du Canada.

- This device and its antenna(s) must not be co-located or operating in conjunction with any other antenna or transmitter, except tested built-in radios.

- Cet appareil et son antenne ne doivent pas être situés ou fonctionner en conjonction avec une autre antenne ou un autre émetteur, exception faites des radios intégrées qui ont été testées.

- The County Code Selection feature is disabled for products marketed in the US/ Canada.

- La fonction de sélection de l'indicatif du pays est désactivée pour les produits commercialisés aux États-Unis et au Canada.