# **Macaron N Series** SM-MSBTF-C01

# NFC Controller Module with Integrated Antenna

Approach Your

**Datasheet Version 1.2**

Smart

3F.-5, No. 1, Taiyuan 2nd St., Zhubei City, Hsinchu County 30288, Taiwan (R.O.C.) TEL: 886-3-5601363 Fax: 886-3-5601361 http://www.smart-approach.com.tw

Smart Approach Co., Ltd ("S.A.") retains the right to make changes to its products or specifications to improve performance, reliability or manufacturability. All information in this document, including descriptions of features, functions, performance, technical specifications and availability, is subject to change without notice at any time. While the information furnished herein is held to be accurate and reliable, no responsibility will be assumed by Smart Approach for its use. Furthermore, the information contained herein does not convey to the purchaser of microelectronic devices any license under license under the patent right of any manufacturer.

Smart Approach Co., Ltd is a registered trademark. All other products or service names used in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other trademarks or registered trademarks mentioned herein are the property of their respective holders.

Feedback on the use of any of the document is welcomed and encouraged by Smart Approach.

- Please contact <u>service@smart-approach.com.tw</u> for your feedback or any ordering inquiry.

- Please contact <a href="mailto:support@smart-approach.com.tw">support@smart-approach.com.tw</a> for any technical question.

# **Revision History**

This section describes the changes that were implemented in this document. The changes are listed by revision, starting with the most current publication.

#### **Revision 1.0**

Revision 1.0 of this datasheet was published in Jun. 2023. This was the first publication of the document.

#### **Revision 1.1**

Revision 1.1 of this datasheet was published in Sep. 2023. Update card instructions and main board design reference. Add download mode concept.

#### **Revision 1.2**

Revision 1.2 of this datasheet was published in Mar. 2024. Update NFC MODULE OUTLINE on page 18.

# Contents

| RE  | VISIO | N HISTORY                                                     | 2 -   |

|-----|-------|---------------------------------------------------------------|-------|

| CO  | NTEN  | VTS                                                           | 3 -   |

| FIG | URE   | CONTENTS                                                      | 4 -   |

| TAI | BLE C | CONTENTS                                                      | 4 -   |

| 1   | PRO   | DUCT OVERVIEW                                                 | 5 -   |

|     | 1.1   | Features                                                      |       |

|     | 1.2   | APPLICATION                                                   | - 6 - |

| 2   | FUN   | CTIONAL DESCRIPTIONS                                          | 8 -   |

|     | 2.1   | COMMUNICATION OVERVIEW FOR ISO/IEC 14443A / MIFARE CONTROLLER | 9 -   |

| 3   | ELE   | CTRICAL SPECIFICATIONS                                        | 10 -  |

|     | 3.1   | PIN DESCRIPTION                                               | 10 -  |

|     | 3.2   | I <sup>2</sup> C Address                                      | 10 -  |

|     | 3.3   | TEMPERATURE MAXIMUM RATINGS                                   | 11 -  |

|     | 3.4   | DC ELECTRICAL PARAMETERS                                      |       |

|     | 3.5   | ANTENNA SPECIFICATIONS                                        | 12 -  |

|     | 3.6   | Power Consumption                                             |       |

|     | 3.7   | THERMAL PROTECTION                                            | 12 -  |

|     | 3.8   | System power modes                                            |       |

|     | 3.9   | RESET CONCEPT                                                 | 14 -  |

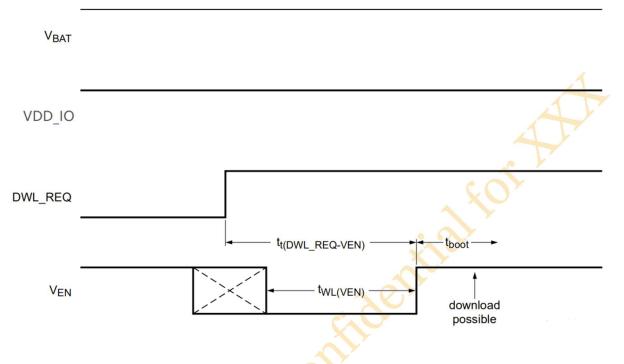

|     | 3.10  | DOWNLOAD MODE CONCEPT                                         | 15 -  |

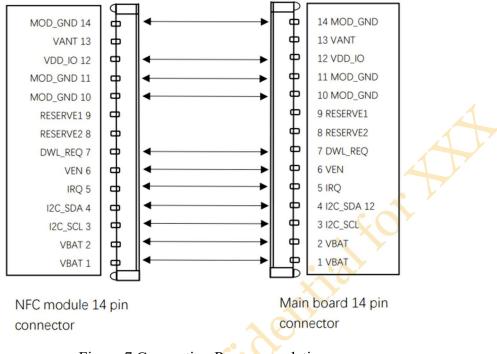

|     | 3.11  | NFC CONNECTION RECOMMENDATION                                 | 16 -  |

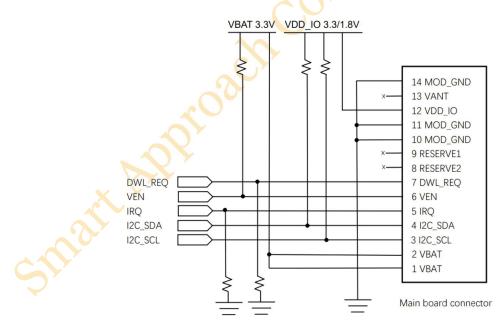

|     | 3.12  | MAIN BOARD DESIGN REFERENCE                                   | 16 -  |

| 4   | ORD   | DERING INFORMATION                                            | 17 -  |

| 5   | NFC   | MODULE OUTLINE                                                | 18 -  |

|     |       |                                                               |       |

# **Figure Contents**

| Figure 1 Typical Application                               | 5 -  |

|------------------------------------------------------------|------|

| Figure 2 Typical Application II                            | 7 -  |

| Figure 3 Module Block Diagram                              | 8 -  |

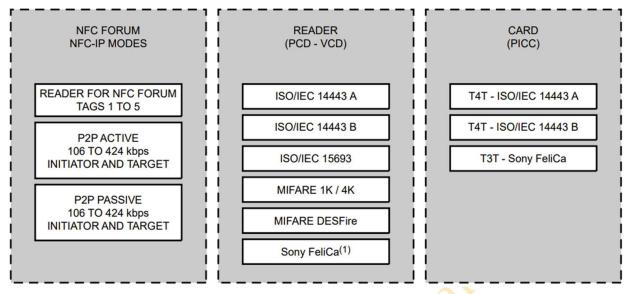

| Figure 4 Transmission Modes                                | 9 -  |

| Figure 5 Reset via V <sub>EN</sub> Pin                     | 14 - |

| Figure 6 Download Mode Sequence                            | 15 - |

| Figure 7 Connection Recommendation                         | 16 - |

| Figure 8 Main Board Design W/O UICC Reference              | 16 - |

| Figure 9 Antenna Module Drawing                            |      |

| Figure 10 Module FPC Connection Footprint (Button Contact) | 19 - |

| Figure 11 FPC Wire Dimension                               | 19 - |

|                                                            |      |

# Table Contents

| Table 1 Module Pin Description          | 10 - |

|-----------------------------------------|------|

| Table 2 I <sup>2</sup> C Address        | 10 - |

| Table 3 Temperature Maximum Ratings     | 11 - |

| Table 4 DC Electrical Specification     | 11 - |

| Table 5 Antenna Specifications          | 12 - |

| Table 6 Current Consumption             | 12 - |

| Table 7 Thermal Protection              | 12 - |

| Table 8 System Power Mode Configuration | 13 - |

| Table 9 System Power States             | 14 - |

| Table 10 Reset Timing.                  | 14 - |

| Table 11 Download Mode Timing           | 15 - |

| Table 12 Ordering Information Table     | 17 - |

# **1 Product Overview**

SM-MSBTF-C01 is full featured NFC controllers designed for integration in portable equipment. It is optimized for low power consumption with fully host controllable power states and for small footprint for portable equipment applications.

The module's compact, flexible design with and exposed pad is optimal for size-sensitive applications, assures robust performance.

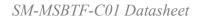

The following illustration shows a high-level, generic view of a SM-MSBTF-C01 application.

Figure 1 Typical Application

#### 1.1 Features

- Highly integrated demodulator and decoder

- Buffered output drivers to connect an antenna with minimum number of external components

- Integrated RF level detector

- Integrated Polling Loop for automatic device discovery

- RF protocols supported

- ISO/IEC 14443A, ISO/IEC 14443B PICC mode

- ISO/IEC 14443A, ISO/IEC 14443B PCD mode designed according to NFC Forum digital protocol T4T platform and ISO-DEP

- FeliCa PCD mode

- -MIFARE PCD encryption mechanism (MIFARE 1K/4K)

- NFC Forum tags T1T, T2T, T3T, T4T and T5T

- NFCIP-1, NFCIP-2 protocol

- NFC Forum certification for P2P, reader and card mode

- FeliCa PICC mode

- ISO/IEC 15693/ICODE VCD mode

- NFC Forum-compliant embedded T4T for NDEF short record

- Supported host interfaces

- NCI protocol interface according to NFC Forum standardization

- I2C-bus High-speed mode

- Flexible clock supply concept to facilitate PN7160 integration

- Internal oscillator for 27.12 MHz crystal connection

- Integrated PLL unit to make use of device reference clock and facilitate PN7160 integration

- Integrated power management unit

- Direct connection to a battery (2.3 V to 5.5 V voltage supply range)

- Support different low-power states configuration: Hard Power-Down state and Standby states activated by firmware

- Autonomous mode when host is shut down

- Automatic wake-up via RF field, internal timer and I2C-bus interface

- Integrated non-volatile memory to store data and executable code for customization

Anti tearing support to recover from tearing events

- Standards compliance

- NFC Forum Device Requirements

- $-NCI \ 2.0$

\*All card types and it's protocol shall follow NXP's and NFC forum recommendation.

Cards that comply with the protocol are subject to testing with the host.

#### 1.2 Application

Suggested applications for the SM-MSBTF-C01 module include:

- Mobile devices

- Portable equipment (personal digital assistants, tablet, notebook, wearable)

- Consumer devices

- Smart home gateways

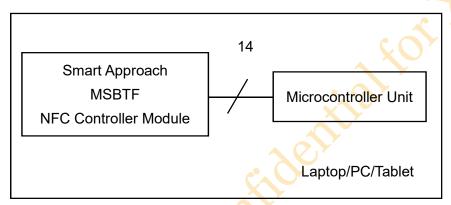

Figure 2 Typical Application II

SM-MSBTF-C01 can be connected on a host controller through I<sup>2</sup>C-bus interfaces. The logical interface towards the host base band is NCI-compliant with additional command set for SA specific product features.

Moreover, SM-MSBTF-C01 provides flexible and integrated power management unit in order to preserve energy supporting Powered by the Field and Power Off mode.

### 2 Functional Descriptions

This section provides detailed information about how SM-MSBTF-C01 module works, what configurations and operational features are available.

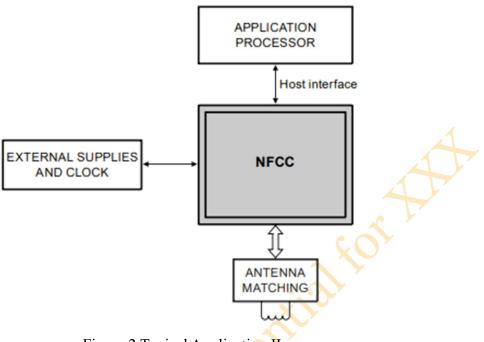

The following illustration shows the primary functional blocks of SM-MSBTF-C01 module.

Figure 3 Module Block Diagram

Loop Antenna is Smart Approach customize solution, Antenna size of SM-MSBTF-C01 is 45mm x 35 mm. Antenna matching is also a customize solution. NFC controller includes NXP PN7160 chipset, and has an I<sup>2</sup>C control interface through the connector to mother board.

- 1. According to ISO/IEC 18092(Ecma 340)standard.

- 2. PICC only for android HCE.

#### Figure 4 Transmission Modes

For contactless card functionality, SM-MSBTF-C01 can act autonomously if previously configured by the host in such a manner.

#### 2.1 Communication overview for ISO/IEC 14443A / MIFARE Controller

The contactless coprocessor and the on-chip CPU of SM-MSBTF-C01 handle the complete ISO/IEC 14443A/MIFARE RF-protocol, nevertheless a dedicated external host has to handle the application layer communication.

# **3** Electrical Specifications

This section provides the DC characteristics, AC characteristics, recommended operating conditions. It includes information on the various timing functions of the module.

#### 3.1 Pin Description

The following Table shows the pin description for SM-MSBTF-C01 module.

The connection ground is internally connected and should be connected to GND on the main board as well.

| PIN<br>No. | Name                 | Description                                                                                                                  | Power<br>Reference        | P/I/O |

|------------|----------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------|

| 1          | V <sub>BAT</sub>     | Battery Supply Voltage                                                                                                       | 3.3V                      | Р     |

| 2          | V <sub>BAT</sub>     | Battery Supply Voltage                                                                                                       | 3.3V                      | Р     |

| 3          | I <sup>2</sup> C_SCL | I <sup>2</sup> C-bus Clock Line                                                                                              | VDD_IO                    | Ι     |

| 4          | I <sup>2</sup> C_SDA | I <sup>2</sup> C-bus Data Line                                                                                               | VDD_IO                    | I/O   |

| 5          | IRQ                  | Interrupt request from module to platform,<br>Normal : Low; Interrupt : High                                                 | VDD_IO                    | Ο     |

| 6          | $V_{\text{EN}}$      | Reset pin input from the host to wake up the device from<br>standby and also to reset the device, Normal : High; Reset : Low | $\mathbf{V}_{\text{BAT}}$ | Ι     |

| 7          | DWL_REQ              | Firmware download control: Normal : Low; Active : High                                                                       | VDD_IO                    | Ι     |

| 8          | Reserve2             | N.C.                                                                                                                         | -                         | -     |

| 9          | Reserve1             | N.C.                                                                                                                         | -                         | -     |

| 10         | MOD_GND              | Module Ground                                                                                                                | GND                       | Р     |

| 11         | MOD_GND              | Module Ground                                                                                                                | GND                       | Р     |

| 12         | VDD_IO               | Pad Supply Voltage                                                                                                           | 1.8V/3.3V                 | Р     |

| 13         | VANT                 | N.C.                                                                                                                         | -                         | -     |

| 14         | MOD_GND              | Module Ground                                                                                                                | GND                       | Р     |

Table 1 Module Pin Description

### 3.2 I<sup>2</sup>C Address

SM-MSBTF-C01 I<sup>2</sup>C 7bit address is defined to 0x28. To write data, this module is addressed using 0x50, to read data, this module is addressed using 0x51.

#### Table 2 I<sup>2</sup>C Address

| I2C address (R/W=0, write) | I2C address (R/W=1, read) |

|----------------------------|---------------------------|

| 0x50                       | 0x51                      |

#### 3.3 Temperature Maximum Ratings

Thermal specifications for this module have been modeled using a two-layer test board.

| Symbol | Definition               | Va  | llue | Lin:4a              |

|--------|--------------------------|-----|------|---------------------|

| Symbol | Definition               | Min | Max  | - Units<br>°C<br>°C |

| Т      | Operating<br>Temperature | -25 | 85   | °C                  |

| Ts     | Storage<br>Temperature   | -40 | 100  | °C                  |

Table 3 Temperature Maximum Ratings

#### **3.4 DC Electrical Parameters**

DC Electrical specifications for this module have been modeled using a two-layer test board.

Table 4 DC Electrical Specification

| Symbol            | Definition   |     | Value |     | Units | Note     |

|-------------------|--------------|-----|-------|-----|-------|----------|

| Symbol            | Definition   | Min | Тур   | Max |       | Note (1) |

| V <sub>BAT</sub>  | Power Supply | 3.1 | 3.3   | 5.5 | Volts |          |

| I <sub>VBAT</sub> | DC Current   |     |       | 290 | mA    | (1)      |

#### Note:

1. continuous total current consumption in PCD mode at VBAT = 3.6 V

#### 3.5 Antenna Specifications

Antenna specifications for this module have been modeled using a two-layer test board.

| Itom                                   |       | Value             |       | J                  | Nata                  |

|----------------------------------------|-------|-------------------|-------|--------------------|-----------------------|

| Item                                   | Min   | Тур               | Max   | Unit               | Note                  |

| DC                                     | 0.5   | 1                 | 2     | Ω                  | A                     |

| Resistance                             | 0.5   | 1                 | 2     | 52                 |                       |

| AC<br>Impedance                        |       | 50                |       | Ω                  |                       |

| Frequency                              | 13.06 | 13.56             | 14.06 | MHz                |                       |

| Q factor                               | 25    | 30                | 35    |                    |                       |

| Antenna<br>Type                        |       | FR4 Loop Coil     |       | $\mathbf{\lambda}$ | Add the Ferrite sheet |

| Size                                   | (4    | 5 ±0.3) X (35±0.3 | 3)    | mm                 |                       |

| <b>3.6 Power Con</b> Table 6 Current 0 | •     |                   | e der |                    |                       |

#### Table 5 Antenna Specifications

#### 3.6 Power Consumption

| Symbol            | Parameter                  | Conditions                     | Min | Тур  | Max | Unit |

|-------------------|----------------------------|--------------------------------|-----|------|-----|------|

| I <sub>HPD</sub>  | Hard power down current    | $V_{BAT}=3.6V,$<br>$V_{EN}=0V$ | -   | 10   | 24  | μΑ   |

| I <sub>STBY</sub> | Standby state current      | V <sub>BAT</sub> =3.6V         | -   | 20   | 35  | μΑ   |

| I <sub>ACT</sub>  | Active state current       | $V_{BAT}=3.6V$                 | -   | 4.55 | -   | mA   |

| I <sub>tvdd</sub> | Transmitter supply current | V <sub>BAT</sub> =3.6V         | -   | 240  | -   | mA   |

\*Active state : Idle and Listenser modes.

#### 3.7 Thermal Protection

Table 7 Thermal Protection

| Symbol    | Parameter          | Conditions | Min       | Тур | Max            | Unit |

|-----------|--------------------|------------|-----------|-----|----------------|------|

| Tovertemp | Temperature        |            | - 125 125 | 125 | <sup>0</sup> C |      |

|           | protection trigger |            | -         | 123 | 123            | C    |

#### 3.8 System power modes

| VBAT | VDD_IO | $\mathbf{V}_{\mathbf{EN}}$ | Power mode      |

|------|--------|----------------------------|-----------------|

| Off  | Х      | Х                          | Power Off       |

| On   | Х      | Off                        | Hard Power Down |

| On   | Off    | On                         | Standby         |

| On   | On     | On                         | Active          |

Table 8 System Power Mode Configuration

Note: X: Don't care

Table 9 System Power States

| Power State name | Description                                                                               |

|------------------|-------------------------------------------------------------------------------------------|

|                  | The MSBTF is supplied by $V_{\text{BAT}}$ within its operating range and MSBTF is kept in |

| Hard Power Down  | Hard Power Down ( $V_{EN}$ voltage is kept low by host or SW programming) to have         |

|                  | the minimum power consumption. The system mode is in Power Off.                           |

|                  | The MSBTF is supplied by $V_{BAT}$ within its operating range, $V_{EN}$ voltage is high   |

|                  | (by host or SW programming) and minimum part of MSBTF is kept supplied to                 |

| Standby          | enable configured wake-up sources which allow to switch to Active state; RF               |

|                  | field, Host interface (if VDD_IO is high). The system mode is Low-power mode              |

|                  | or Full power mode.                                                                       |

|                  | The MSBTF is supplied by $V_{BAT}$ within its operating range, $V_{EN}$ voltage is high   |

| . <i></i>        | (by host or SW programming), VDD_IO is high and the MSBTF internal blocks                 |

| Active           | are supplied. 3 sub-modes are defined: Idle, Listener and Poller. The system mode         |

|                  | is Full power mode.                                                                       |

|                  |                                                                                           |

#### 3.9 Reset concept

To enter reset, the  $V_{EN}$  voltage shall be set to low (this is also the Hard Power Down state): Reset means resetting the embedded FW execution and the registers values to their default values. Parts of these default values are defined from EEPROM data loaded values, others are hardware defined. To get out of reset:

$\bullet$  Pulling  $V_{\text{EN}}$  voltage high with  $V_{\text{BAT}}$  within its operating range

Figure 5 Reset via V<sub>EN</sub> pin

| Table | 10 | Reset | Timing |

|-------|----|-------|--------|

|-------|----|-------|--------|

| Symbol               | Parameter   | Condition | Min | Тур | Max | Unit |

|----------------------|-------------|-----------|-----|-----|-----|------|

| t <sub>WL(VEN)</sub> | pulse width | to reset  | 10  | -   | -   |      |

|                      | VEN LOW     | to reset  |     |     |     | μs   |

| t <sub>boot</sub>    | boot time   |           | -   | -   | 2.5 | ms   |

|                      |             |           |     |     |     |      |

#### 3.10 Download mode concept

To enter this mode, the pin DWL\_REQ shall be pulled to VDD\_IO before reset via VEN pin is done.

Figure 6 Download mode sequence

| Symbol                | Parameter                | Condition       | Min | Тур | Max | Unit         |

|-----------------------|--------------------------|-----------------|-----|-----|-----|--------------|

| 4                     | transition time from pin | DWL_REQ, VEN    | 0   | 0.5 |     | <b>100</b> G |

| $t_{t(DWL\_REQ-VEN)}$ | DWL_REQ to pin VEN       | voltages = HIGH | 0   | 0.5 | -   | ms           |

|                       |                          |                 |     |     |     |              |

#### 3.11 NFC Connection Recommendation

Figure 7 Connection Recommendation

#### 3.12 Main Board Design Reference

I2C\_SDA, I2C\_SCL, VEN, DWL\_REQ, IRQ have pull-up or pull-down resistors inside the module, the main board is recommended to reserve the pull-up or pull-down resistors position (not SMD components).

#### Figure 8 Main Board Design W/O UICC Reference

#### **Ordering Information** 4

| Order Number | Descriptions                                            |

|--------------|---------------------------------------------------------|

| SM-MSBTF-C01 | NFC Macaron Module (NXP PN7160) with Integrated Antenna |

| Dimension    | Module: 71.62 x 35 x 2.1 mm                             |

|              | oproach confidential for A                              |

# 5 NFC Module Outline

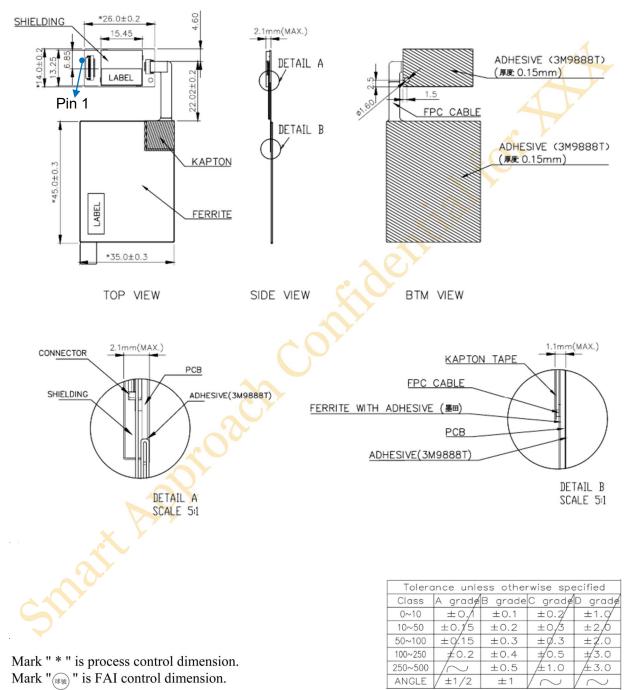

The following illustration shows the package drawing for SM-MSBTF-C01 module. The drawing contains the detail views, dimensions, tolerances and notes.

Figure 9 Antenna Module Drawing

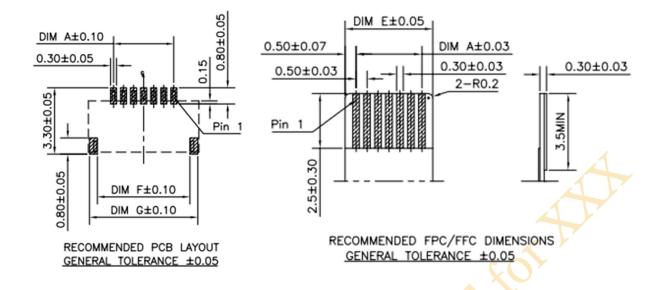

Figure 10 Module FPC Connection Footprint (Button Contact)

| CKT | DIM A | DIM B | DIM C | DIM D | DIM E | DIM F | DIM G | DIM H | DIM J | DIM K |

|-----|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 04  | 1.50  | 4.0   | 2.57  | 3.33  | 2.50  | 3.10  | 3.90  |       |       |       |

| 05  | 2.00  | 4.5   | 3.07  | 3.83  | 3.00  | 3.60  | 4.40  |       |       |       |

| 06  | 2.50  | 5.0   | 3.57  | 4.33  | 3.50  | 4.10  | 4.90  |       |       |       |

| 07  | 3.00  | 5.5   | 4.07  | 4.83  | 4.00  | 4.60  | 5.40  |       |       |       |

| 08  | 3.50  | 6.0   | 4.57  | 5.33  | 4.50  | 5.10  | 5.90  |       | 3.0   |       |

| 09  | 4.00  | 6.5   | 5.07  | 5.83  | 5.00  | 5.60  | 6.40  |       |       |       |

| 10  | 4.50  | 7.0   | 5.57  | 6.33  | 5.50  | 6.10  | 6.90  |       |       |       |

| 11  | 5.00  | 7.5   | 6.07  | 6.83  | 6.00  | 6.60  | 7.40  |       |       |       |

| 12  | 5.50  | 8.0 🧹 | 6.57  | 7.33  | 6.50  | 7.10  | 7.90  |       |       |       |

| 13  | 6.00  | 8.5   | 7.07  | 7.83  | 7.00  | 7.60  | 8.40  |       |       |       |

| 14  | 6.50  | 9.0   | 7.57  | 8.33  | 7.50  | 8.10  | 8.90  | 3.0   |       | 2.5   |

| 15  | 7.00  | 9.5   | 8.07  | 8.83  | 8.00  | 8.60  | 9.40  | 5.0   |       |       |

| 16  | 7.50  | 10.0  | 8.57  | 9.33  | 8.50  | 9.10  | 9.90  |       |       |       |

| 17  | 8.00  | 10.5  | 9.07  | 9.83  | 9.00  | 9.60  | 10.40 |       |       |       |

| 18  | 8.50  | 11.0  | 9.57  | 10.33 | 9.50  | 10.10 | 10.90 |       | 6.0   |       |

| 19  | 9.00  | 11.5  | 10.07 | 10.83 | 10.00 | 10.60 | 11.40 |       | 0.0   |       |

| 20  | 9.50  | 12.0  | 10.57 | 11.33 | 10.50 | 11.10 | 11.90 |       |       |       |

Figure 11 FPC Wire Dimension