## Rayson

# MICROCHIP

1F No.9 R&D Rd.II ,Science-Based Industrial Park,Hsin-Chu 300 Taiwan,R.O.C. No.1,Tongfu  $1_{\rm ST}$  Road ,The  $2_{\rm nd}$  Industrial Zone, Loucun, Gongming, Guangming New District, Shenzhen, China. Tel: 886-3-5633666 Fax: 886-3-5633688

Email: <a href="mailto:sales@rayson.com">sales@rayson.com</a>

| <b>Annra</b>                                  | Date :                      |          |  |

|-----------------------------------------------|-----------------------------|----------|--|

| Appro                                         | 20-March-2023               |          |  |

| Customer                                      |                             |          |  |

| Customer Part Number                          |                             |          |  |

| Description                                   | Bluetooth Stereo M          | odule    |  |

| Customer's Project                            |                             |          |  |

| Firmware Version                              |                             |          |  |

| Manufacturer                                  | Rayson Technology (         | Co., Ltd |  |

| Model Name BTM983H                            |                             |          |  |

| Supplier Level : ■ New Source □ Second Source |                             |          |  |

| Contact Person :                              | Tel : <u>+886-3-5633666</u> | _        |  |

| Approval status :                             |                             |          |  |

| E.E. engineer :                               |                             |          |  |

| M.E. engineer : □ Approval □ Reject           |                             |          |  |

| P.E. engineer : □ Approval □ Reject           |                             |          |  |

| Approval :                                    |                             |          |  |

## Revision History

| Revision | Date       | Description                |

|----------|------------|----------------------------|

| No.      |            |                            |

| V00      | 2019/05/07 | Draft version.             |

| V01      | 2020/07/07 | Initial version.           |

| V02      | 2023/03/20 | Update FCC ID \ IC \ HVIN. |

|          |            |                            |

|          |            |                            |

|          |            |                            |

|          |            |                            |

|          |            |                            |

|          |            |                            |

|          |            |                            |

|          |            |                            |

|          |            |                            |

|          |            |                            |

|          |            |                            |

.

## BTM983H Bluetooth® Stereo Audio Module Data Sheet

## Introduction

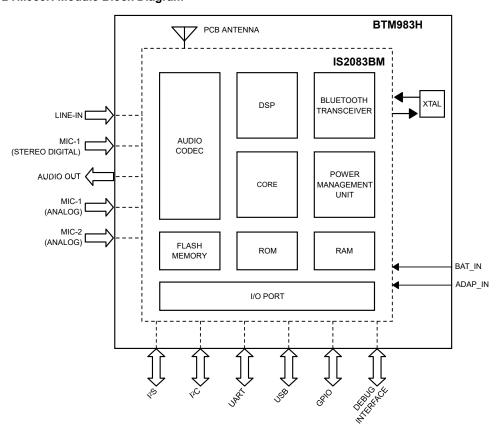

The BTM983H, based on Microchip's dual-mode IS2083 system-on-chip (SoC) device, is an RF-certified, fully integrated module with high-performing voice and audio post-processing capability for Bluetooth audio applications. Tuning for Noise Reduction, Acoustic Echo Cancellation (AEC), and EQ filtering can be customized with an easy-to-use GUI Configuration Tool. This flexible platform provides multiple digital and analog audio interfaces including stereo microphones, I²S, Line-In and a stereo audio DAC. It supports easy firmware upgrades via UART, USB and Over-the- Air (OTA).

This turn-key solution module is pre-programmed with firmware that enables Bluetooth audio playback for a plug-and-play solution, and an audio transceiver solution for A2DP source/sink. Control settings for LED drivers and other peripherals can be set via the Configuration Tool. Advanced developers can use the Software Development Kit (SDK) to implement their applications.

Note: Contact your local sales representative for more information about the Software Development Kit (SDK).

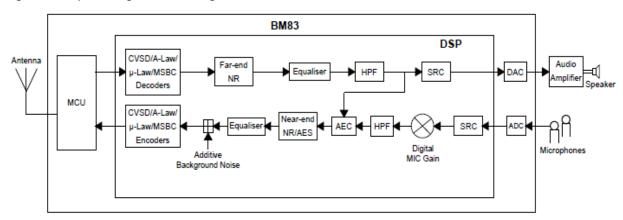

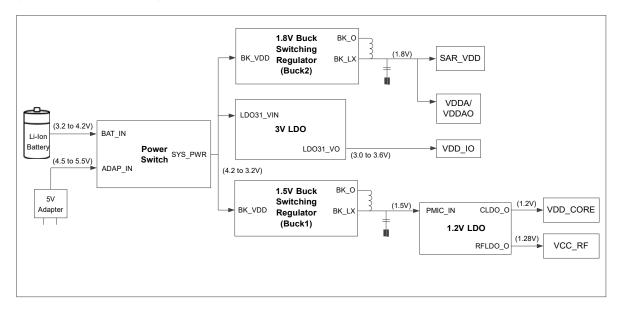

Figure 1. BTM983H Module Block Diagram

The BTM983H module supports the following Bluetooth profiles and codecs:

- · Profiles:

- Hands-free Profile (HFP) 1.7, Headset Profile (HSP) 1.2, Advanced Audio Distribution Profile (A2DP) 1.3,

Serial Port Profile (SPP) 1.2, Audio/Video Remote Control Profile (AVRCP) 1.6, and Phone Book Access Profile (PBAP) 1.2

- · Codecs:

- Advanced Audio Codec (AAC) and Sub-band Coding (SBC)

## **Features**

- Qualified for Bluetooth v5.0 Specification:

- HFP 1.7, HSP 1.2, A2DP 1.3, SPP 1.2, AVRCP 1.6, and PBAP 1.2

- Bluetooth classic (BR/EDR) and Bluetooth Low Energy

- General Attribute Profile (GATT) and General Access Profile (GAP)

- Bluetooth Low Energy Data Length Extension (DLE) and secure connection

- · SDK:

- 8051 MCU debugging

- 24-bit program counter and data pointer modes

- Multi-Link:

- A2DP (maximum 3 devices)

- HFP (maximum 3 devices)

- · Multi-Speaker (MSPK) Solution:

- Microchip's proprietary solution to connect a master speaker to one or more slave speakers

- With MSPK firmware, the BTM983H can provide Concert mode and Stereo mode

- Audio Transceiver (AT) Solution:

- With AT firmware, the BTM983H can work as either an A2DP source (where BTM983H is the transmitter) or A2DP/HFP sink (where BTM983H is a receiver)

- Audio Interfaces:

- Stereo line input

- Two analog microphones

- One stereo digital microphone

- Stereo audio Digital-to-Analog converter (DAC)

- Inter-IC (I<sup>2</sup>S) Sound input/output

- I<sup>2</sup>S Master Clock (MCLK)/reference clock

- USB, UART, and Over-the-Air (OTA) Firmware Upgrade

- Built-In Lithium-Ion and Lithium Polymer Battery Charger (Up To 350 mA Charging Current)

- · Compact Surface Mount Module:

- 32 mm x 15 mm x 2.5 mm

- Castellated surface mount pads

- Module shield

- Integrated 3V and 1.8V Configurable Switching Regulator and Low-Dropout (LDO)

#### RF/Analog

- · Frequency Spectrum: 2.402 GHz to 2.480 GHz

- Receive Sensitivity: -90 dBm (2 Mbps EDR, at 0.01% BER)

- · Programmable Transmit Output Power:

- Up to +10.4 dBm (typical) for Basic Data Rate (BDR)

- Up to +9.2 dBm (typical) for Enhanced Data Rate (EDR)

#### **DSP Voice and Audio Processing**

- 16/32-bit DSP Core with Enhanced 32-Bit Precision, Single Cycle Multiplier

- 64 Kbps A-Law, μ-Law Pulse Code Modulation (PCM), or Continuous Variable Slope Delta (CVSD) Modulation for Synchronous Connection-Oriented (SCO) Channel Operation

- 8/16 kHz Noise Reduction (NR)

- 8/16 kHz Acoustic Echo Cancellation (AEC)

- Modified Sub-Band Coding (mSBC) Decoder for Wideband Speech

- · Packet Loss Concealment (PLC) for SBC and AAC Codecs Only

#### **Audio Codec**

- · SBC and AAC

- · 20-bit Audio Stereo DAC with Signal-to-Noise Ratio (SNR) 95 dB

- 16-bit Audio Stereo Analog-to-Digital Converter (ADC) with SNR 90 dB

- 16-bit/24-bit I<sup>2</sup>S Digital Audio:

- 8 kHz, 16 kHz, 44.1 kHz, and 48 kHz sampling frequency for SBC and AAC

#### **Peripherals**

- Successive Approximation Register Analog-to-Digital Converter (SAR ADC) with Dedicated Channels:

- Battery voltage detection and adapter voltage detection

- Charger thermal protection and ambient temperature detection

- UART (With Hardware Flow Control)

- USB (Full-Speed USB 1.1 Interface)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>) Master

- One Pulse Width Modulation (PWM) Channel

- · Two LED Drivers

- Up to 18 General Purpose Inputs/Outputs (GPIOs)

- 2-wire 8051 MCU Joint Test Action Group (JTAG) Debug

#### **Operating Conditions**

- · Operating Voltage: 3.2V to 4.2V

- Operating Temperature: -40°C to +85°C

#### Compliance

- Bluetooth Special Interest Group (SIG) QDID: 134083 (Class1) and 134099 (Class2)

- Certified to the United States (FCC), Canada (ISED), Europe (CE), Korea (KCC), Taiwan (NCC), and Japan (MIC) Radio Regulations

- RoHS Compliant

#### **Applications**

- · Portable Speaker

- · Multiple Speakers

- · Headphones

## 2. Device Overview

The BTM983H stereo audio module is built around the IS2083BM SoC, which integrates the dual-mode baseband, modem, radio transceiver, PMU, MCU, crystal, and a DSP dedicated for audio and voice applications. Users can configure the BTM983H module by using the SDK or the IS208x\_Config\_GUI\_Tool (Config Tool).

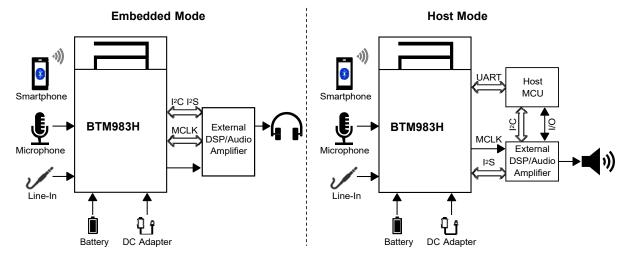

There are two modes of operation:

- · Host mode:

- Interfaces with an external MCU over UART for application specific system control

- The MSPK solution and AT solution can reside on the external MCU

- · Embedded mode:

- No external MCU involved

- BTM983H acts as an MCU to control all peripherals to provide various speaker features

- Integrates the MSPK and AT solution on the module

Simple system control can be implemented using the SDK. DSP parameters such as equalizer settings can be set using the Config Tool.

Note: The SDK and Config Tool are available for download at: www.microchip.com/BM83.

The following figure illustrates the Embedded mode and Host mode of the BTM983H module.

Figure 2-1. BTM983H Module Application Modes

The following table provides the features of the BTM983H module.

Table 2-1. BTM983H Module Features

| Features                                                              | ВТМ983Н                              |

|-----------------------------------------------------------------------|--------------------------------------|

| SoC                                                                   | IS2083BM                             |

| Pin Count                                                             | 50                                   |

| Dimension                                                             | 32 mm x 15 mm                        |

| RF                                                                    |                                      |

| PCB Antenna                                                           | Yes                                  |

| TX Power (typical)                                                    | +11 dBm (Class1) and +1 dBm (Class2) |

| RX Sensitivity                                                        | -90 dBm (2 Mbps EDR)                 |

| Bluetooth Power Class                                                 | Class 1 and Class 2                  |

| RF Shield                                                             | Yes                                  |

| Audio                                                                 |                                      |

| Audio DAC Output                                                      | 2-channel                            |

| DAC (Single-ended) SNR                                                | -95 dB                               |

| DAC (Capless) SNR                                                     | -95 dB                               |

| ADC SNR                                                               | -90 dB                               |

| I <sup>2</sup> S Audio (Input/Output) with Master Clock (MCLK) Output | Yes                                  |

| Analog Auxiliary In                                                   | Yes                                  |

| Analog Microphone                                                     | 2                                    |

| Stereo Digital Microphone                                             | 1                                    |

| External Audio Amp Interface                                          | Yes                                  |

| Power                                                                 |                                      |

| Battery Input (BAT_IN)                                                | 3.8V (typ.)                          |

| DC Adapter Input (ADAP_IN)                                            | 5.0V (typ.)                          |

| Integrated BUCK Regulator                                             | Yes                                  |

| Battery Charger (350 mA charging current max)                         | Yes                                  |

| Peripherals                                                           |                                      |

| UART (with HW flow control)                                           | Yes                                  |

| I <sup>2</sup> C Master                                               | Yes                                  |

| USB (full speed USB v1.1 interface)                                   | Yes                                  |

| SAR ADC                                                               | 2                                    |

| PWM                                                                   | 1                                    |

| LED Driver                                                            | 2                                    |

| GPIOs                                                                 | 18                                   |

| JTAG Debug Port (8051 MCU)                                            | 2-wire                               |

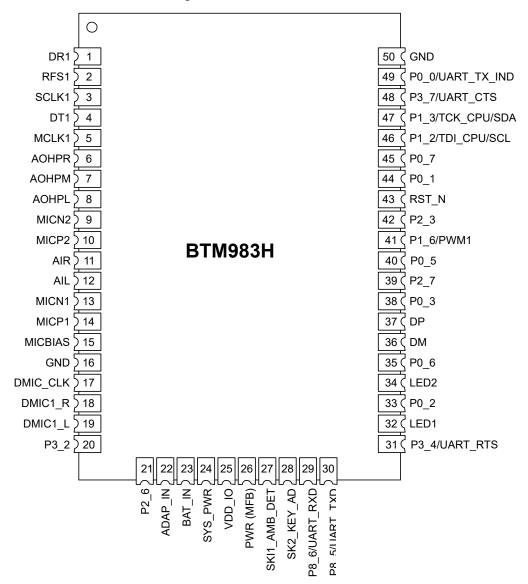

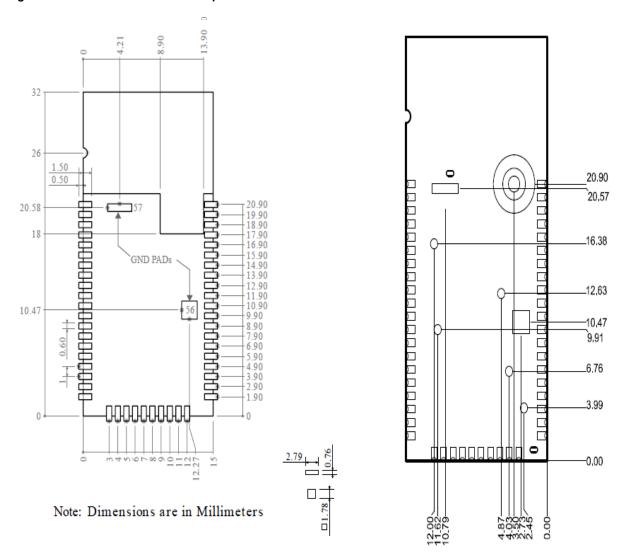

## 2.1 BTM983H Module Pin Diagram

The following figure illustrates the pin diagram of the BTM983H module.

Figure 2-2. BTM983H Module Pin Diagram

## 2.2 BTM983H Module Pin Description

The following table describes the pin description of the BTM983H module.

Table 2-2. BTM983H Module Pin Description

| Pin<br>Number | Pin Name | Pin<br>Type | Description                                                                                                                                                                                                               |

|---------------|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | DR1      | I           | I <sup>2</sup> S interface: digital left/right data                                                                                                                                                                       |

| 2             | RFS1     | I/O         | I <sup>2</sup> S interface: digital left/right clock                                                                                                                                                                      |

| 3             | SCLK1    | I/O         | I <sup>2</sup> S interface: bit clock                                                                                                                                                                                     |

| 4             | DT1      | 0           | I <sup>2</sup> S interface: digital left/right data                                                                                                                                                                       |

| 5             | MCLK1    | 0           | I <sup>2</sup> S interface: master clock                                                                                                                                                                                  |

| 6             | AOHPR    | 0           | R-channel analog headphone output                                                                                                                                                                                         |

| 7             | AOHPM    | 0           | Headphone common mode output/sense input                                                                                                                                                                                  |

| 8             | AOHPL    | 0           | L-channel analog headphone output                                                                                                                                                                                         |

| 9             | MICN2    | I           | MIC 2 mono differential analog negative input                                                                                                                                                                             |

| 10            | MICP2    | 1           | MIC 2 mono differential analog positive input                                                                                                                                                                             |

| 11            | AIR      | I           | R-channel single-ended analog input                                                                                                                                                                                       |

| 12            | AIL      | I           | L-channel single-ended analog input                                                                                                                                                                                       |

| 13            | MICN1    | I           | MIC 1 mono differential analog negative input                                                                                                                                                                             |

| 14            | MICP1    | 1           | MIC 1 mono differential analog positive input                                                                                                                                                                             |

| 15            | MICBIAS  | Р           | Electric microphone biasing voltage                                                                                                                                                                                       |

| 16            | GND      | Р           | Ground reference                                                                                                                                                                                                          |

| 17            | DMIC_CLK | 0           | Digital MIC clock output                                                                                                                                                                                                  |

| 18            | DMIC1_R  | I           | Digital MIC right input                                                                                                                                                                                                   |

| 19            | DMIC1_L  | I           | Digital MIC left input                                                                                                                                                                                                    |

| 20            | P3_2     | I/O         | <ul> <li>General purpose I/O port P3_2</li> <li>By default, this is configured as AUX_IN DETECT</li> </ul>                                                                                                                |

| 21            | P2_6     | I/O         | General purpose I/O port P2_6                                                                                                                                                                                             |

| 22            | ADAP_IN  | Р           | <ul> <li>5V power adapter input</li> <li>To charge the battery in the Li-ion battery powered applications</li> <li>To be used for USB Device Firmware Upgrade (DFU)</li> <li>Otherwise it can be left floating</li> </ul> |

| 23            | BAT_IN   | Р           | <ul> <li>Power supply input; voltage range: 3.2V to 4.2V</li> <li>Source can either be a Li-ion battery or any other power rail on the host board</li> </ul>                                                              |

## BTM983H

## **Device Overview**

| continued    |                 |           |                                                                                                                                                                  |

|--------------|-----------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin          | Pin Name        | Pin       | Description                                                                                                                                                      |

| Number<br>24 | SYS_PWR         | Type<br>P | System power output derived from the ADAP_IN or BAT_IN input Only for internal use Do not connect to any other devices LED1 and LED2 can be connected to SYS_PWR |

| 25           | VDD_IO          | Р         | I/O power supply, do not connect, for internal use only (connected to LDO31_VO)                                                                                  |

| 26           | PWR (MFB)       | I         | Multi-function push button and Power On key                                                                                                                      |

| 27           | SK1_AMB_DET     | I         | Temperature sense channel 1                                                                                                                                      |

| 28           | SK2_KEY_AD      | I         | Temperature sense channel 2                                                                                                                                      |

| 29           | P8_6 / UART_RXD | I/O       | General purpose I/O port P8_6 UART RX data                                                                                                                       |

| 30           | P8_5 / UART_TXD | I/O       | <ul><li>General purpose I/O port P8_5</li><li>UART TX data</li></ul>                                                                                             |

| 31           | P3_4 / UART_RTS | I/O       | <ul> <li>General purpose I/O port P3_4</li> <li>System configuration pin (Application mode or Test mode)</li> <li>UART RTS</li> </ul>                            |

| 32           | LED1            | I         | LED driver 1                                                                                                                                                     |

| 33           | P0_2            | I/O       | General purpose I/O port P0_2     By default, this is configured as play/pause button (user configurable button)                                                 |

| 34           | LED2            | I         | LED driver 2                                                                                                                                                     |

| 35           | P0_6            | I/O       | General purpose I/O port P0_6                                                                                                                                    |

| 36           | DM              | I/O       | USB data minus data line                                                                                                                                         |

| 37           | DP              | I/O       | USB data positive data line                                                                                                                                      |

| 38           | P0_3            | I/O       | <ul> <li>General purpose I/O port P0_3</li> <li>By default, this is configured as reverse button (user configurable button)</li> </ul>                           |

| 39           | P2_7            | I/O       | <ul> <li>General purpose I/O port P2_7</li> <li>By default, this is configured as volume up button (user configurable button)</li> </ul>                         |

| 40           | P0_5            | I/O       | <ul> <li>General purpose I/O port P0_5</li> <li>By default, this is configured as volume down button (user configurable button)</li> </ul>                       |

| 41           | P1_6 / PWM1     | I/O       | <ul><li>General purpose I/O port P1_6</li><li>PWM1 output</li></ul>                                                                                              |

| 42           | P2_3            | I/O       | General purpose I/O port P2_3                                                                                                                                    |

| 43           | RST_N           | I         | System Reset pin (active-low)                                                                                                                                    |

# BTM983H Device Overview

| cont          | continued               |             |                                                                                                                                                                                                                  |  |

|---------------|-------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin<br>Number | Pin Name                | Pin<br>Type | Description                                                                                                                                                                                                      |  |

| 44            | P0_1                    | I/O         | <ul> <li>General purpose I/O port P0_1</li> <li>By default, this is configured as forward button (user configurable button)</li> </ul>                                                                           |  |

| 45            | P0_7                    | I/O         | General purpose I/O port P0_7                                                                                                                                                                                    |  |

| 46            | P1_2 / TDI_CPU / SCL    | I/O         | <ul> <li>General purpose I/O port P1_2</li> <li>CPU 2-wire debug data</li> <li>I<sup>2</sup>C SCL</li> </ul>                                                                                                     |  |

| 47            | P1_3 / TCK_CPU /<br>SDA | I/O         | <ul> <li>General purpose I/O port P1_3</li> <li>CPU 2-wire debug clock</li> <li>I<sup>2</sup>C SDA</li> </ul>                                                                                                    |  |

| 48            | P3_7 / UART_CTS         | I/O         | <ul><li>General purpose I/O port P3_7</li><li>UART CTS</li></ul>                                                                                                                                                 |  |

| 49            | P0_0 / UART_TX_IND      | I/O         | <ul> <li>General purpose I/O port P0_0</li> <li>By default, this is configured as an external codec reset (Embedded mode)</li> <li>UART_TX_IND (active-high) used to wake-up the host MCU (Host mode)</li> </ul> |  |

| 50            | GND                     | Р           | Ground reference                                                                                                                                                                                                 |  |

**Note:** The BTM983H module is pre-configured with Embedded mode (see, 6.4 General Purpose I/O Pins). The GPIOs mentioned in the preceding table can be configured using the Config Tool or the SDK.

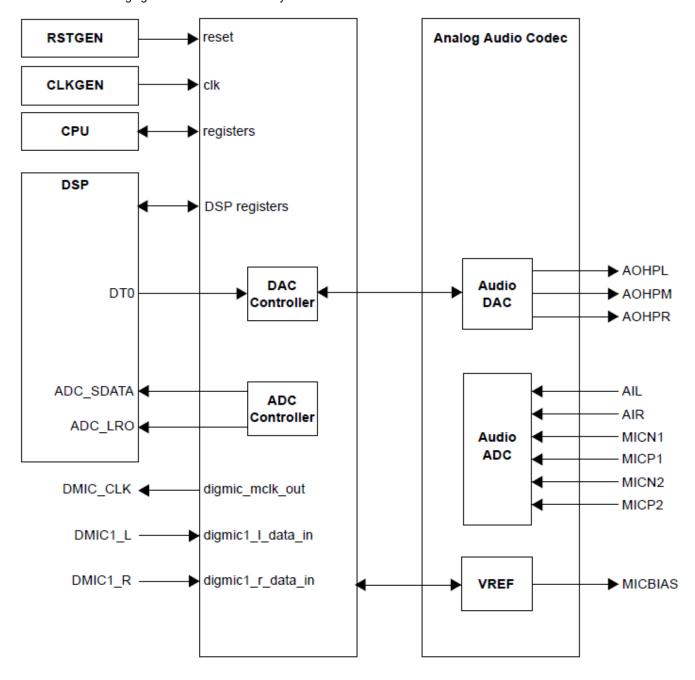

**Audio Subsystem**

## 3. Audio Subsystem

The input and output audios have different stages and each stage can be programmed to vary the gain response characteristics. For microphone, both single-ended inputs and differential inputs are supported. To maintain a high quality signal, a stable bias voltage source to the condenser microphone's Field-Effect Transistor (FET) is provided. The DC blocking capacitors can be used at both positive and negative sides of an input. Internally, this analog signal is converted to 16-bit, 8 kHz/16 kHz/44.1 kHz/48 kHz linear PCM data.

The following figure shows the audio subsystem.

## 3.1 Digital Signal Processor

The BTM983H module integrates a high-performance DSP to provide excellent voice and audio user experience. The advanced speech features, such as AEC and NR are inbuilt. To reduce nonlinear distortion and echo cancellation, an

outgoing signal level to the speaker is monitored and adjusted to avoid saturation of speaker output or microphone input. Adaptive filtering is also applied to track the echo path impulse in response, to provide an echo free and full-duplex user experience.

The embedded noise reduction algorithm helps to extract clean speech signals from the noisy inputs captured by the microphones and improves communication.

In addition to NR/AEC function, audio effect functions such as Multiband Dynamic Range Compression (MB-DRC), virtual bass enhancement (VB), and audio widening (AW)), for A2DP audio streaming are also available to enhance the audio quality for various applications. For mono speaker/speakerphone and stereo headset applications, MB-DRC and VB can be enabled to have better audio clarity. For stereo speaker/speakerphone applications, in addition to MB-DRC and VB. AW can be enabled to provide better live audio effect for the users.

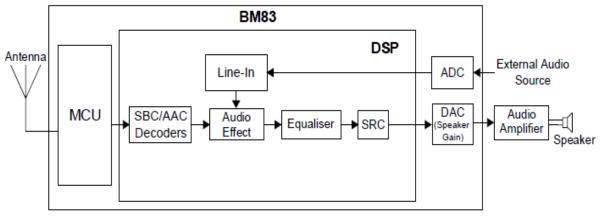

The following figures illustrate the signal processing flow of speakerphone applications for speech and audio signal processing.

Figure 3-2. Speech Signal Processing

Figure 3-3. Audio Signal Processing

#### Note:

1. The DSP parameters can be configured using the Config Tool.

## 3.2 Codec

The built-in codec has a high SNR performance and it consists of an ADC, a DAC and an additional analog circuitry. The internal codec supports 20-bit resolution for DAC and 16-bit resolution for ADC.

- Interfaces

- Two mono differential or single-ended MIC inputs

- One stereo single-ended line input

- One stereo single-ended line output

- One stereo single-ended headphone output (capacitor-less connection)

- · Built-in circuit

- MIC bias

- Reference and biasing circuitry

- · Optional digital High Pass Filter (HPF) on ADC path

- · Silence detection

- To turn off the DSP and audio codec subsystem, if there is no Line-In data after UI configured time stamp.

- Anti-pop function (pop reduction system to reduce audible glitches)

- Sampling rates:

- ADC/DAC/I<sup>2</sup>S: 8 kHz, 16 kHz, 44.1 kHz, and 48 kHz

Note: The sampling rates can be selected in the CODEC Setup tab of Config Tool.

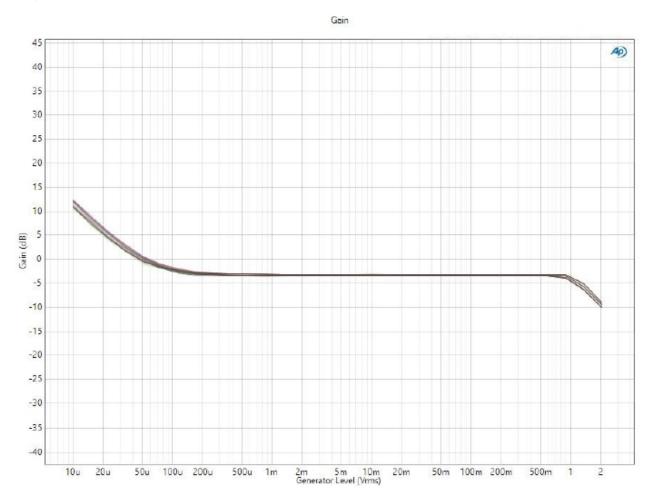

#### 3.2.1 DAC Performance

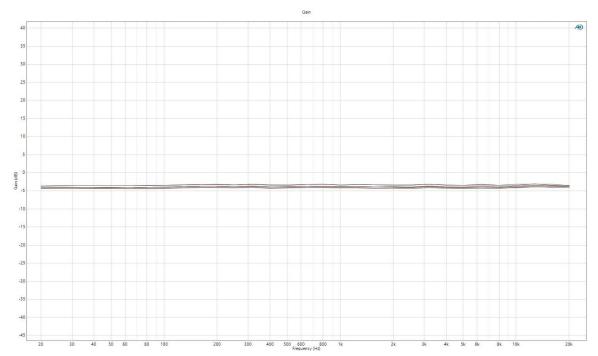

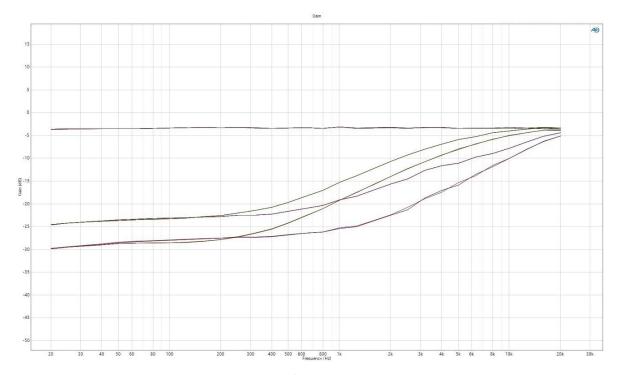

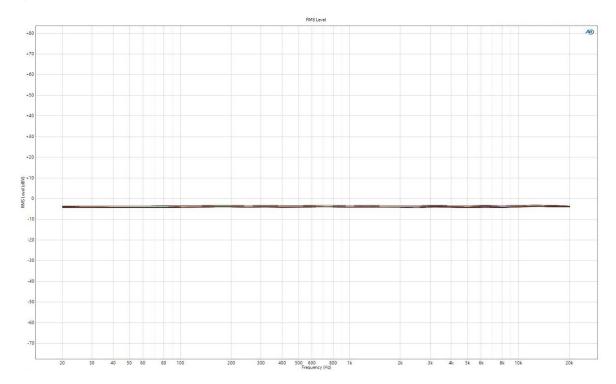

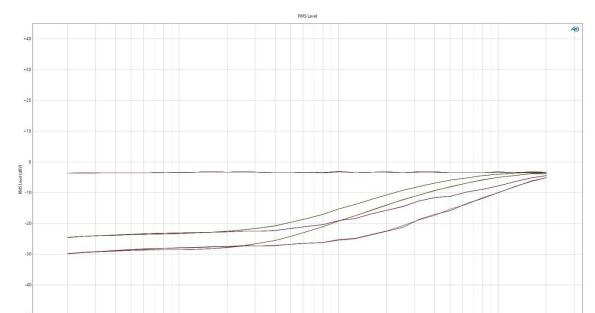

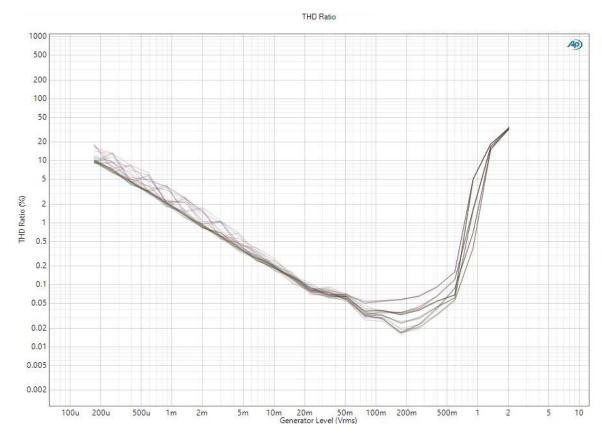

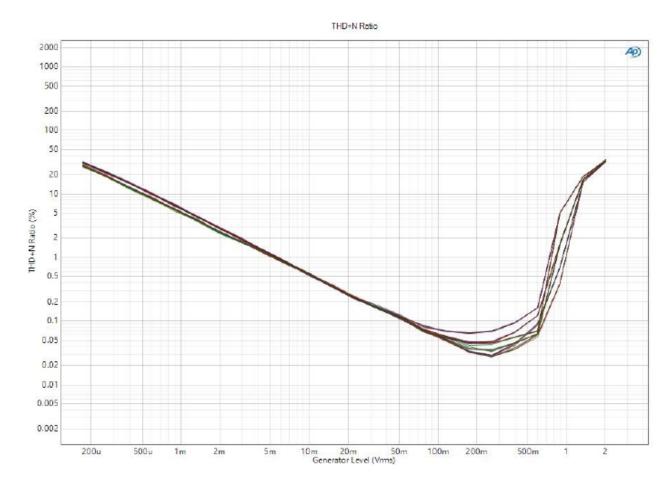

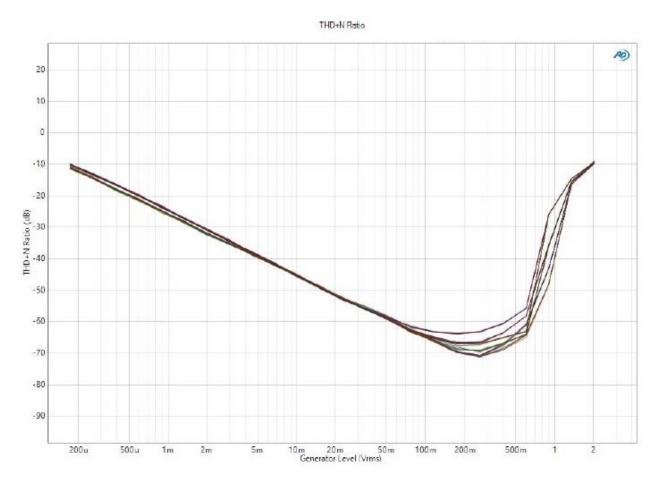

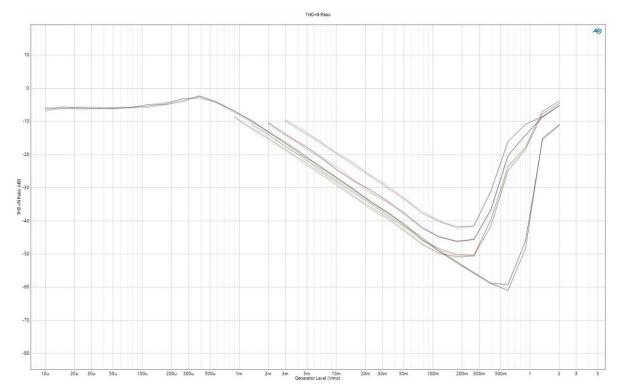

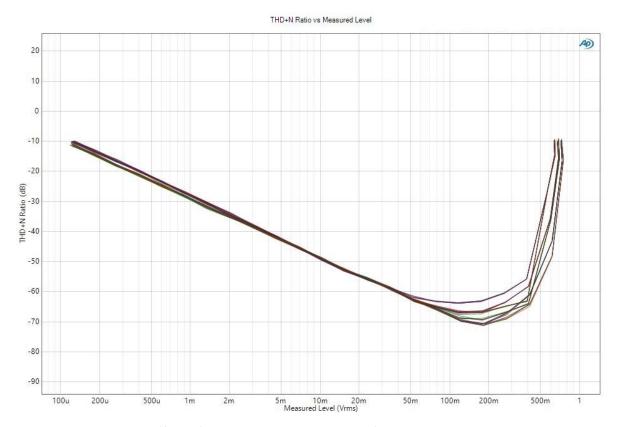

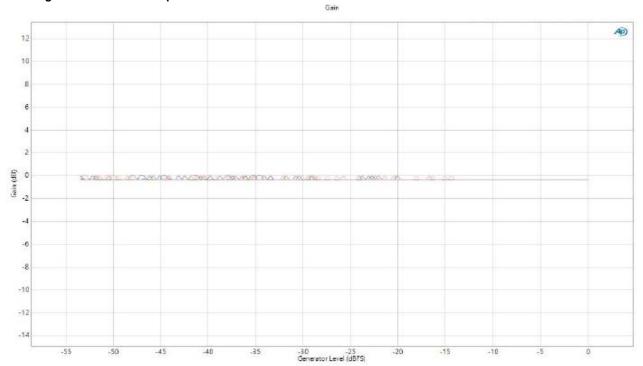

The audio graphs in this section are produced in the following conditions:

- · At room temperature

- Using BTM983H EVB platform with BTM983H module mounted on BTM983H Carrier Board

- Input signal = 1 kHz sine tone, level sweep across -100 dBv to 6 dBv, frequency sweep across 20 Hz to 20 kHz at 1 Fs input level

- Various termination loads ( $16\Omega$ ,  $32\Omega$ ,  $100 \text{ k}\Omega$ )

- Analog gain = -3 dB; digital gain = 0 dB

- · A-weighting applied, 22K bandwidth.

The following figures illustrate the DAC performance.

Figure 3-4. Gain Vs. Input Level at Various Loads (Capless Mode)

Figure 3-5. Gain Vs. Input Level at Various Loads (Single-ended Mode)

Figure 3-6. Gain Vs. Frequency at Various Loads (Capless Mode)

Figure 3-7. Gain Vs. Frequency at Various Loads (Single-ended Mode)

Figure 3-8. Level Vs. Frequency at Various Loads (Capless Mode)

Figure 3-9. Level Vs. Frequency at Various Loads (Single-ended Mode)

Figure 3-10. THD Ratio (%) Vs. Input Level at Various Loads (Capless Mode)

THD Ratio

10

10

-10

-20

-50

-60

-70

-80

10m 20m 50m Generator Level (Vrms)

100m

200m

500m

Figure 3-11. THD Ratio (dB) Vs. Input Level at Various Loads (Capless Mode)

-90

100u

200u

500u

1 m

2m

5m

Figure 3-12. THD Ratio (%) Vs. Input Level at Various Loads (Capless Mode)

Figure 3-13. THD Ratio (dB) Vs. Input Level at Various Loads (Capless Mode)

Figure 3-14. THD+N Ratio (%) Vs. Input Level at Various Loads (Single-ended mode)

Figure 3-15. THD+N Ratio (dB) Vs. Input Level at Various Loads (Single-ended mode)

.

Figure 3-16. THD+N Ratio (%) Vs. output Level at Various Loads (Capless Mode)

0.002

200u

500u

1m

2m

THD+N Ratio vs Measured Level AD) 1000 500 200 100 50 20 10 THD →N Ratio (%) 2 0.5 0.2 0.1 0.05 0.02 0.01 0.005

> 5m 10m 20m Measured Level (Vrms)

100m

200m

500m

Figure 3-17. THD+N Ratio (dB) Vs. Output Level at Various Loads (Capless Mode)

Figure 3-18. THD+N Ratio (%) Vs. Output Level at Various Loads (Single-ended mode)

Figure 3-19. THD+N Ratio (dB) Vs. Output Level at Various Loads (Single-ended mode)

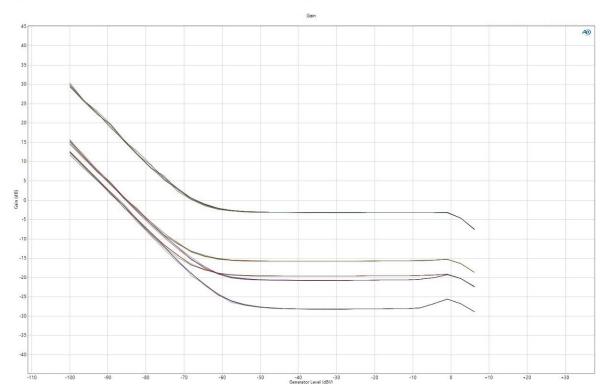

## 3.2.2 ADC Performance

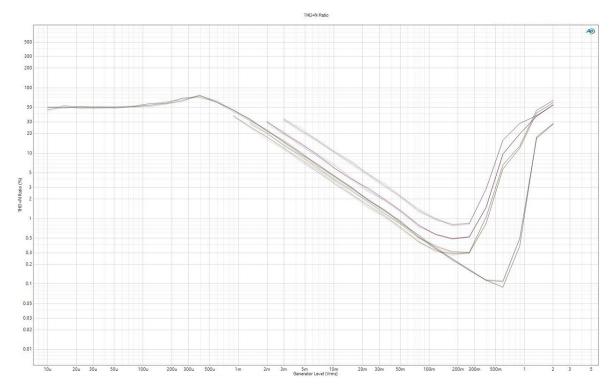

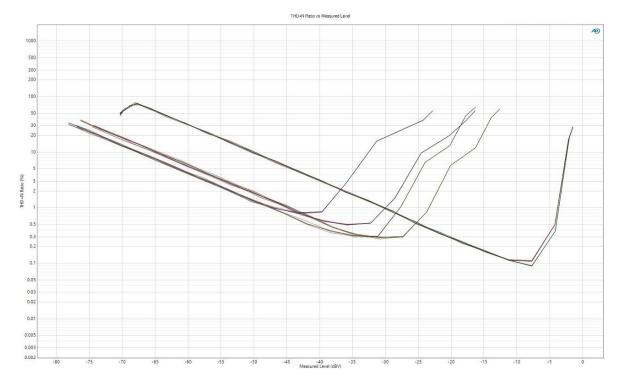

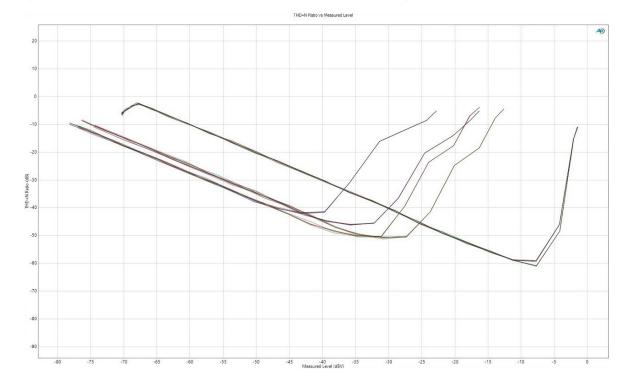

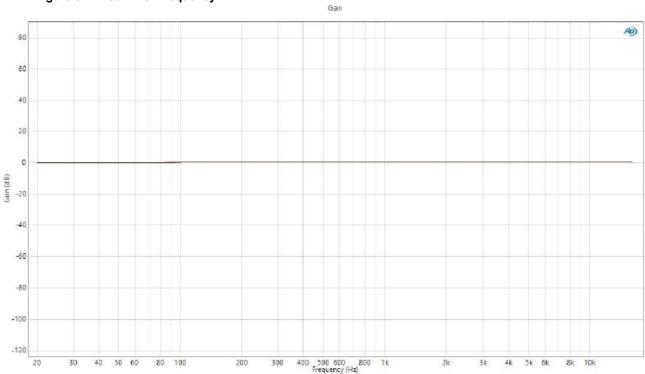

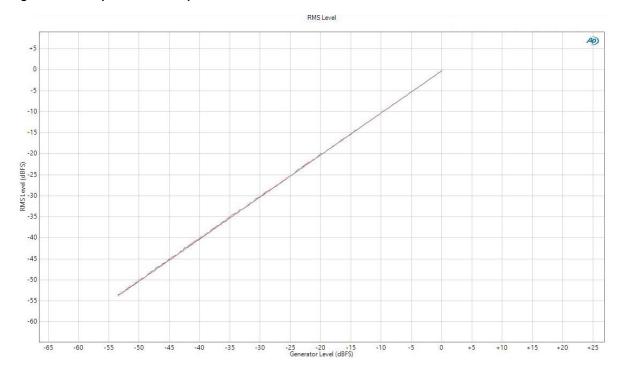

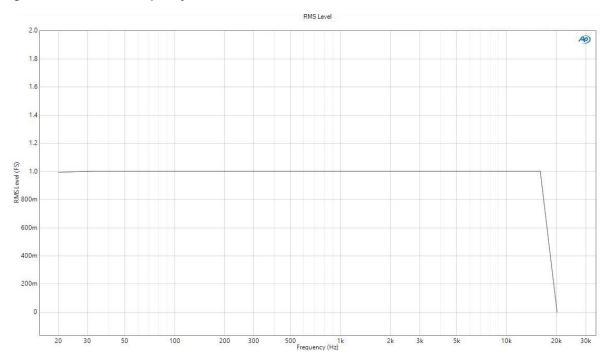

The audio graphs in this section were produced in the following conditions:

- · At room temperature

- Using BTM983H EVB platform with BTM983H module mounted on BTM983H Carrier Board

- Input signal = 1 kHz sine tone, level sweep across -100 dBv to 6 dBv, frequency sweep across 20 Hz to 20 kHz at 1 Fs input level

- Analog gain = -3 dB; digital gain = 0 dB

- · A-weighting applied, 22K bandwidth

The following figures illustrate the ADC performance

Figure 3-20. Gain Vs. Input Level

Figure 3-21. Gain Vs. Frequency

Figure 3-22. Output Level Vs. Input Level

Figure 3-23. Level Vs. Frequency

+10

+15

THO-N Ratio

-30 -25 -20 Generator Level (dBFS) -10

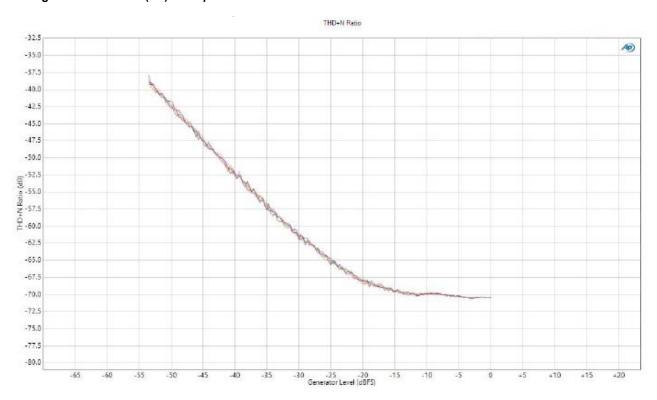

Figure 3-24. THD+N Ration(%) Vs. Input Level

Figure 3-25. THD+N (dB) Vs. Input Level

-55

-50

-45

-40

-35

-60

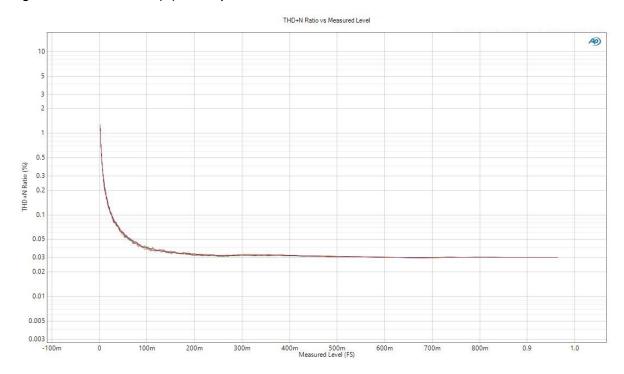

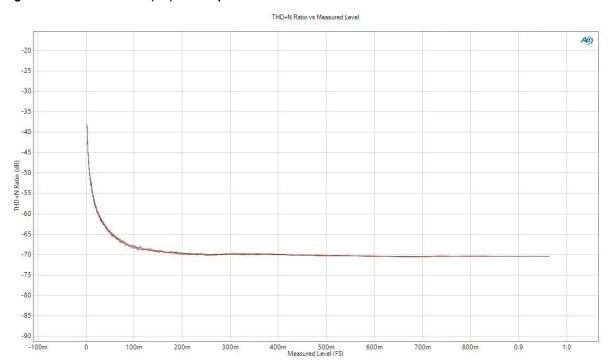

Figure 3-26. THD+N Ratio (%) Vs. Output Level

Figure 3-27. THD+N Ratio (dB) Vs. Output Level

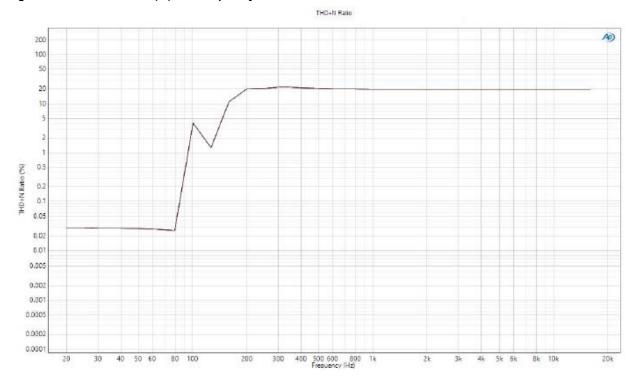

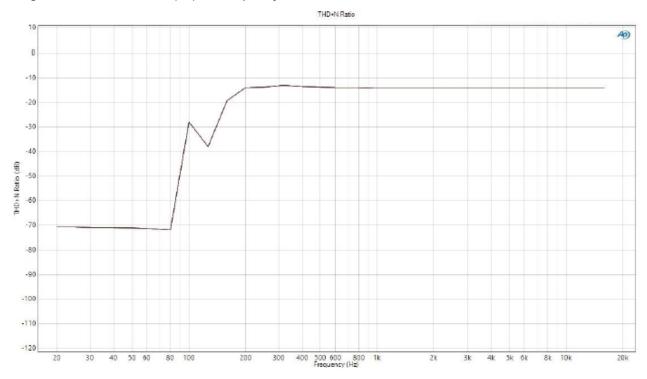

Figure 3-28. THD+N Ratio (%) Vs. Frequency

Figure 3-29. THD+N Ration (dB) Vs. Frequency

## 3.3 Auxiliary Port

The BTM983H module supports one analog (Line-In, also called as Aux-In) signal from the external audio source. The analog (Line-In) signal can be processed by the DSP to generate different sound effects (MB-DRC and AW), which can be configured by using the Config Tool.

## 3.4 Analog Speaker Output

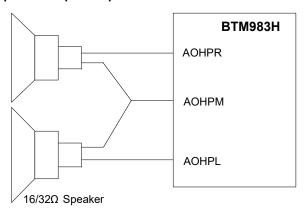

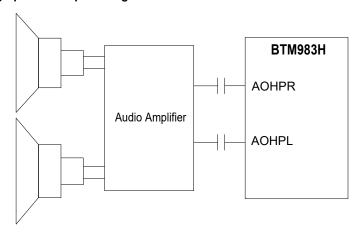

The BTM983H module supports the following analog speaker output modes:

Capless mode – recommended for headphone applications in which capless output connection helps to save

the Bill of Materials (BOM) cost by avoiding a large DC blocking capacitor. The following figure illustrates the

analog speaker output in Capless mode.

Figure 3-30. Analog Speaker Output - Capless Mode

• Single-Ended mode – used for driving an external audio amplifier where a DC blocking capacitor is required. The following figure illustrates the analog speaker output in Single-Ended mode.

Figure 3-31. Analog Speaker Output - Single-Ended Mode

## 3.5 Microphone Inputs

The BTM983H module supports up to two analog microphone channels and one stereo digital microphone. The digital microphone interface should only be used for Pulse Density Modulation (PDM) digital microphones (typically, MEMS microphones) up to about 4 MHz of clock frequency.

$\textbf{Note:} \ \ \, \text{An I$^2$S$ based digital microphone should use the external I$^2$S port.}$

**Note:** To avoid saturation in the PDM digital microphone path, Microchip recommends limiting the PDM maximum input level to -6 dBFS.

## 4. Bluetooth Transceiver

The BTM983H module is designed and optimized for the Bluetooth 2.4 GHz system. It contains a complete RF Transmitter (TX)/Receiver (RX) section. An internal synthesizer generates a stable clock for synchronizing with another device.

#### 4.1 Transmitter

The IS2083BM device has an internal Medium Power Amplifier (MPA) and a Low Power Amplifier (LPA). The MPA supports up to +11 dBm output power for Bluetooth Class1 applications, and the LPA supports +1 dBm output power for the Class 2 applications. The transmitter performs the I/Q conversion to minimize the frequency drift.

#### 4.2 Receiver

- The Low-Noise Amplifier (LNA) operates with TR-Combined mode with LPA for single port application. It removes the need for an external TX/RX switch.

- The ADC is used to sample the input analog signal and convert it into a digital signal for demodulator analysis. A channel filter has been integrated into the receiver channel before the ADC, which is used to reduce the external component count and increase the anti-interference capability.

- The image rejection filter is used to reject the image frequency for low-Intermediate Frequency (IF) architecture and to reduce external Band Pass Filter (BPF) component for a super heterodyne architecture.

- Received Signal Strength Indicator (RSSI) signal feedback to the processor is used to control the RF output power to make a good trade-off for effective distance and current consumption.

## 4.3 Synthesizer

A synthesizer generates a clock for radio transceiver operation. There is a Voltage-Controlled Oscillator (VCO) inside with a tunable internal LC tank that can reduce variation for components. A crystal oscillator with an internal digital trimming circuit provides a stable clock for the synthesizer.

#### 4.4 Modulator-Demodulator

- For Bluetooth 1.2 specification and below, 1 Mbps is the standard data rate based on the Gaussian Frequency Shift Keying (GFSK) modulation scheme. This BR modem meets BDR requirements of Bluetooth 2.0 with EDR specifications.

- For Bluetooth 2.0 and above specifications, EDR is introduced to provide the data rates of 1/2/3 Mbps.

- For baseband, both BDR and EDR utilize the same 1 MHz symbol rate and 1.6 kHz slot rate.

- For BDR, symbol 1 represents 1-bit. However, each symbol in the payload part of EDR packet represents 2/3 bits. This is achieved by using two different modulations π/4 Differential Quadrature Phase Shift Keying (DQPSK) and 8-Differential Phase Shift Keying (DPSK).

## 4.5 Adaptive Frequency Hopping

The BTM983H module has an AFH function to avoid RF interference. It has an algorithm to check the nearby interference and to choose clear channel for transceiver Bluetooth signal.

## 5. Power Management Unit

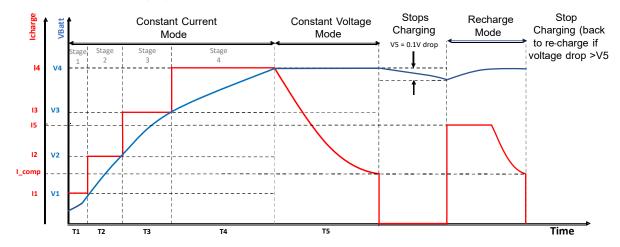

The on-chip PMU integrates the battery (lithium-ion and lithium-polymer) charger, and voltage regulator. A power switch is used to switch over the power source between the battery (BAT\_IN) and an adapter (ADAP\_IN). The PMU provides current to drive two LEDs.

The battery charger supports various modes with features listed below:

- · Charging control using current sensor

- User-programmable current regulation

- · High accuracy voltage regulation

- · Constant current and constant voltage modes

- Stop charging and re-charging modes

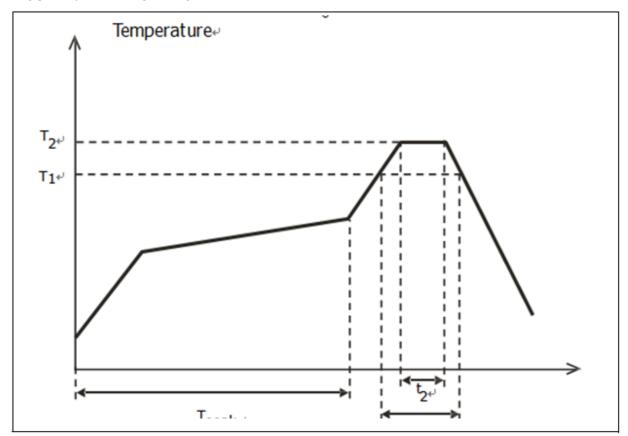

The following figure illustrates the charging curve of a battery.

Figure 5-1. Battery Charging Curve

**Note:** For more details on battery charger configuration, refer to the *IS2083/BTM983H Battery Charger Application Note(AN3490)*.

## 5.1 Power Supply

The BTM983H module is powered through the BAT\_IN input pin. The following figure illustrates the connection from the BAT\_IN pin to various other voltage supply pins of the IS2083BM SoC on the BTM983H module. The external 5V power adapter can be connected to ADAP\_IN in order to charge the battery in battery powered applications or in USB applications. Otherwise the ADAP\_IN pin can be left floating if there is no battery utilized at BAT\_IN pin.

Figure 5-2. Power Tree Diagram

## 5.2 SAR ADC

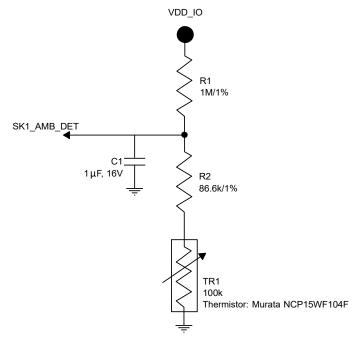

The BTM983H module has a 10-bit Successive Approximation Register (SAR) ADC with ENOB (Effective Number of Bits) of 8-bits; used for battery voltage detection, adapter voltage detection, charger thermal protection, and ambient temperature detection. The input power of the SAR ADC is supplied by the 1.8V output of Buck2. The warning level can be programmed by using the Config Tool or the SDK.

The SK1 and SK2 are the ADC channel pins. The SK1 is used for charger thermal protection. The following figure illustrates the suggested circuit and thermistor, Murata NCP15WF104F. The charger thermal protection can avoid battery charge in a restricted temperature range. The upper and lower limits for temperature values can be configured by using the Config Tool.

Figure 5-3. Ambient Detection Circuit

**Note:** The thermistor must be placed close to the battery in the user application for accurate temperature measurements and to enable the thermal shutdown feature.

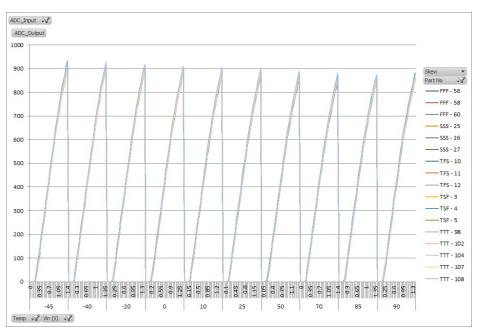

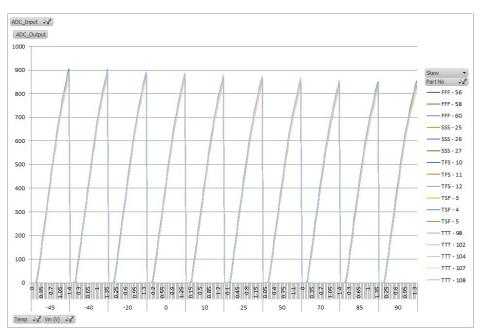

The following figures show SK1 and SK2 channel behavior.

Figure 5-4. SK1 Channel

Figure 5-5. SK2 Channel

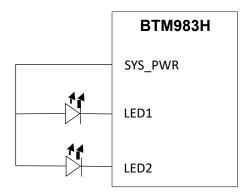

## 5.3 LED Drivers

The BTM983H module has two LED drivers to control external LEDs. The LED drivers provide enough sink current (16- step control and 0.35 mA for each step) and the LED can be connected directly to the BTM983H module. The LED settings can be configured by using the Config Tool.

The following figure illustrates the LED drivers in the BTM983H module.

Figure 5-6. LED Drivers

## 6. Application Information

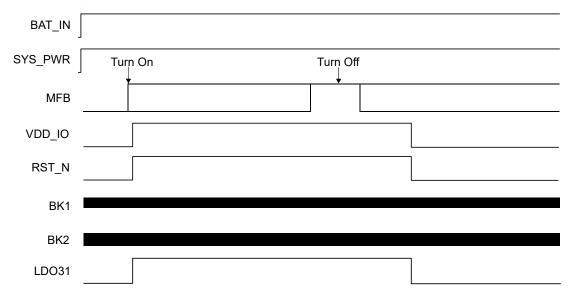

## 6.1 Power On/Off Sequence

In Embedded mode, the MFB button is used to turn on and turn off the system. For Host mode, refer to 6.6 Host MCU Interface Over UART. The following figure illustrates the system behavior (Embedded mode) upon a MFB press event to turn on and turn off the system.

Figure 6-1. Timing Sequence of Power On/Off in Embedded Mode

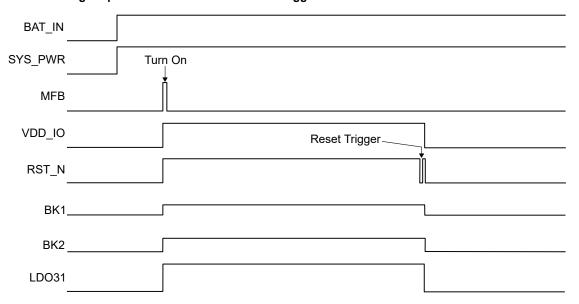

The following figure illustrates the system behavior (Embedded mode) upon a MFB press event to turn on the system and then trigger a Reset event.

Figure 6-2. Timing Sequence of Power On and Reset Trigger in Embedded Mode

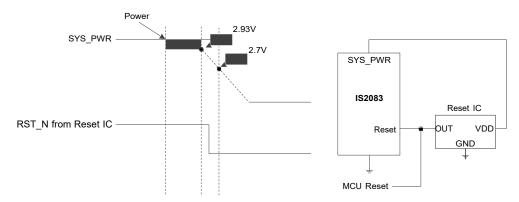

#### 6.2 Reset

The Reset logic generates proper sequence to the device during Reset events. The Reset sources include external Reset, power-up Reset, and Watchdog Timer (WDT). The IS2083 SoC provides a WDT to Reset the chip. In addition, it has an integrated Power-on Reset (POR) circuit that resets all circuits to a known Power On state. This action can also be driven by an external Reset signal, which is used to control the device externally by forcing it into a POR state. The following figure illustrates the system behavior upon a RST N event.

**Note:** The Reset (RST\_N) is an active-low signal and can be utilized based on the application needs, otherwise, it can be left floating.

Figure 6-3. Timing Sequence of Reset Trigger

**Note:** RST\_N pin has an internal pull-up, thus, RST\_N signal will transition to high again upon releasing the RST\_N button. This is an expected behavior of RST\_N signal.

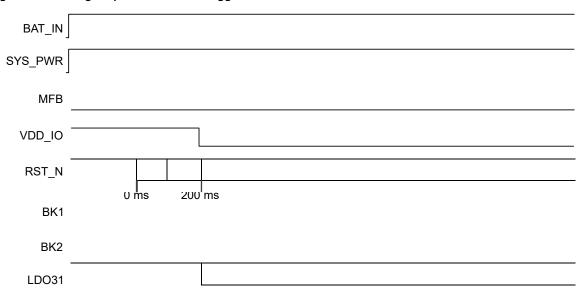

Figure 6-4. Timing Sequence of Power Drop Protection

Timing sequence of power drop protection:

- It is recommended to use the battery to provide the power supply at BAT\_IN.

- If an external power source or a power adapter is utilized to provide power to BAT\_IN, it is recommended to use a voltage supervisor Integrated Circuit (IC).

- The Reset IC output pin, RST\_N, must be open drain type and threshold voltage as 2.93V.

- The RST\_N signal must be fully pulled low before SYS\_PWR power drop to 2.7V.

## 6.3 Configuring and Programming

#### 6.3.1 Test Mode

The BTM983H module can be configured by using the Config Tool and the firmware is programmed by using the isUpdate tool. The following table provides the settings for configuring the BTM983H module for Test mode or Application mode.

Table 6-1. BTM983H Module - Test Mode Configuration Settings

| Pins | Status   | Mode             |

|------|----------|------------------|

| P3_4 | Low      | Test mode        |

|      | Floating | Application mode |

**Note:** The BTM983H module provides Test mode, which allows customers to use existing module manufacturing and testing equipment and flow to test the BTM983H modules without reinvesting in new test equipment. New customers are encouraged to use the new RF test modes defined for this device.

Test mode allows an external UART host to communicate with the BTM983H using Bluetooth vendor commands over the UART interface. The host can interface with the driver firmware on the BTM983H module to perform TX/RX operations and to collect/report Bit Error Rate (BER) and other RF performance parameters. These values can then be used to accept/reject the device and/or calibrate the module.

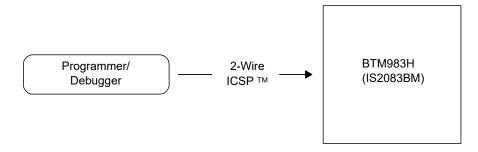

## 6.3.2 2-wire JTAG Program and Debug

The BTM983H (IS2083BM) provides physical interface for connecting and programming the memory contents, see the following figure. For all the programming interfaces, the target device (IS2083BM) must be powered, and all required signals must be connected. In addition, the interface must be enabled through a special initialization sequence.

**Note:** For more details on 2-wire prog/debug, refer to the IS2083 SDK User's Guide and IS2083 SDK Debugger User's Guide.

Figure 6-5. 2-wire In-Circuit Serial Programming (ICSP) Interface

The 2-wire ICSP port can be used to program the memory content. This interface uses the following two communication lines to transfer data to and from the BTM983H (IS2083BM) device being programmed:

- · Serial Program Clock (TCK CPU)

- Serial Program Data (TDI\_CPU)

These signals are described in the following sections. The following table describes the signals required for the 2-wire ICSP interface.

Table 6-2. 2-wire Interface Pin Description

| Pin Name                | Pin Type | Description       |

|-------------------------|----------|-------------------|

| RST_N                   | I        | Reset pin         |

| VDD_IO, ADAP_IN, BAT_IN | Р        | Power supply pins |

| continued |          |                                            |  |  |  |

|-----------|----------|--------------------------------------------|--|--|--|

| Pin Name  | Pin Type | Description                                |  |  |  |

| GND       | Р        | Ground pin                                 |  |  |  |

| TCK_CPU   | I        | Primary programming pin pair: Serial Clock |  |  |  |

| TDI_CPU   | I/O      | Primary programming pin pair: Serial Data  |  |  |  |

#### 6.3.2.1 Serial Program Clock (TCK\_CPU)

TCK\_CPU is the clock that controls the TAP controller update and the shifting of data through the instruction or selected data registers. TCK\_CPU is independent of the processor clock, with respect to both frequency and phase.

#### 6.3.2.2 Serial Program Data (TDI\_CPU)

TDI\_CPU is the data input/output to the instruction or selected data registers and the control signal for the TAP controller. This signal is sampled on the falling edge of TDI\_CPU for some TAP controller states.

## 6.4 General Purpose I/O Pins

The BTM983H module provides up to 18 GPIOs that can be configured by using the Config Tool. The following table provides the default I/O functions of the BTM983H module.

Note: The MFB pin must be configured as the power On/Off key and the remaining pins are user configurable pins.

Table 6-3. GPIO Assigned Pins Function<sup>(1)</sup>

| Pin Name | Function Assigned                                        |

|----------|----------------------------------------------------------|

| P0_0     | External codec reset                                     |

| P0_1     | Forward (FWD) button                                     |

| P0_2     | Play or Pause (PLAY/PAUSE) button                        |

| P0_3     | Reverse (REV) button                                     |

| P0_5     | Volume decrease (VOL_DN) button                          |

| P0_6     | Available for user configuration                         |

| P0_7     | Available for user configuration                         |

| P1_2     | I <sup>2</sup> C SCL (muxed with 2-wire CPU debug data)  |

| P1_3     | I <sup>2</sup> C SDA (muxed with 2-wire CPU debug clock) |

| P1_6     | PWM                                                      |

| P2_3     | Available for user configuration                         |

| P2_6     | Available for user configuration                         |

| P2_7     | Volume increase (VOL_UP) button                          |

| P3_2     | Line-In detect                                           |

| P3_4     | SYS_CFG (muxed with UART_RTS) <sup>(2)</sup>             |

| P3_7     | UART_CTS                                                 |

| P8_5     | UART_TXD <sup>(3)(4)</sup>                               |

| P8_6     | UART_RXD <sup>(3)(4)</sup>                               |

| MFB      | MFB                                                      |

#### Notes:

- 1. This table reflects the default IO assignment for the turn-key solution. The GPIOs are user configurable.

- 2. GPIO P3\_4 is used to enter Test mode during reset. If the user wants to use this pin to control external peripherals, care must be taken to ensure this pin is not pulled LOW and accidentally enters Test mode.

- 3. Microchip recommends to reserve UART port (P8\_5 and P8\_6) for Flash download in Test mode during production.

- 4. Currently, GPIOs ports P8 5 and P8 6 APIs (button detect driver) are not implemented.

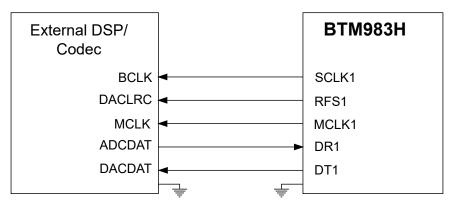

#### 6.5 I<sup>2</sup>S Interface

The BTM983H module provides an I<sup>2</sup>S digital audio input, output or input/output interface to connect with the external codec or DSP. It provides 8, 16, 44.1, 48, 88.2, and 96 kHz sampling rates for 16-bit and 24-bit data formats. The following are the BTM983H module interface signals:

- MCLK1 Master Clock (BTM983H output)

- SCLK1- Serial/Bit Clock (BTM983H input/output)

- DR1 Receive Data (BTM983H input)

- RFS1 Receive Frame Sync (BTM983H input/output)

- DT1 Transmit Data (BTM983H output)

**Note:** The I<sup>2</sup>S parameters can be configured by using the Config Tool.

I<sup>2</sup>S supports the following modes:

- · Master mode

- The BTM983H serves as a master to provide clock and frame synchronous signals for the master/slave data synchronizations, as illustrated in the following figures. The MCLK is optional and is not required if the external I<sup>2</sup>S device can drive its system clock on its own.

Figure 6-6. BTM983H Module in I<sup>2</sup>S Master Mode

- · Slave mode

- The BTM983H serves as a slave to receive clock and frame synchronous signals from the external codec or DSP devices, as illustrated in the following figure.

External DSP/

Codec

BCLK

DACLRC

ADCDAT

DACDAT

DACDAT

DACDAT

DACDAT

DACDAT

DT1

Figure 6-7. BTM983H Module in I<sup>2</sup>S Slave Mode

Note: Use the Config Tool to configure the BTM983H module as a master/slave.

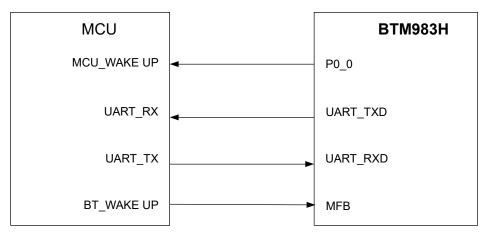

#### 6.6 Host MCU Interface Over UART

The BTM983H module supports UART commands, which enable an external MCU to control the BTM983H module. The following figure illustrates the UART interface between the BTM983H module and an external MCU. An external MCU can control the BTM983H module over the UART interface and wake up the module with the MFB and P0\_0 pins.

Refer to *SPKcommandset tool* to get a list of functions supported by the BTM983H module and how to use the Config Tool for configuring UART and UART command set tool.

Figure 6-8. Host MCU Interface Over UART

Note: For the latest SPKcommandset tool, refer to www.microchip.com/BM83.

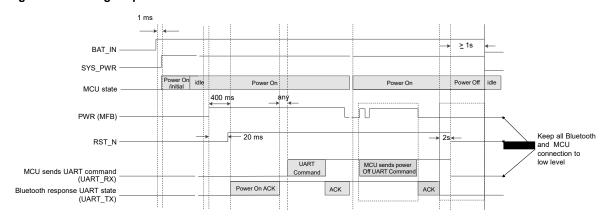

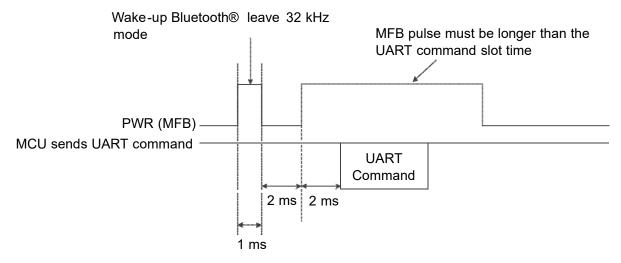

The following figures illustrate the timing sequences of various UART control signals.

Figure 6-9. Timing Sequence of Power On/Off

Figure 6-10. Timing Sequence of RX Indication After Power On State

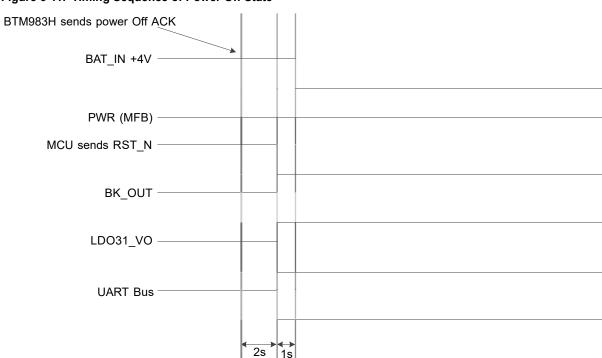

Figure 6-11. Timing Sequence of Power Off State

Timing sequence of power Off state:

- For a byte write: 0.01 ms x 32 clock x 2 = 640 μs.

- It is recommended to have ramp-down time more than 640 µs during the power Off sequence to ensure safe operation of the device.

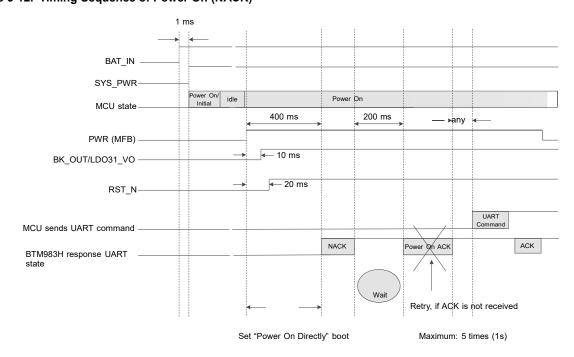

Figure 6-12. Timing Sequence of Power On (NACK)

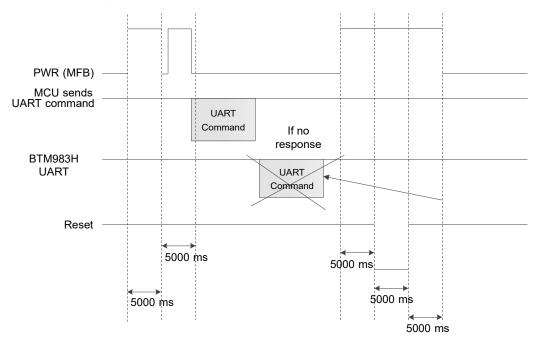

Figure 6-13. Reset Timing Sequence in No Response From Module to Host MCU

If the BTM983H module does not respond to the host MCU's UART command, the MCU re-sends the UART command. If the BTM983H module does not respond within 5 secs, the MCU forces the system to reset.

## 7. PCB Antenna Information

The BTM983H module is integrated with a PCB antenna. This chapter provides the radiation pattern, its orientation, and characteristics.

## 7.1 Antenna Radiation Pattern

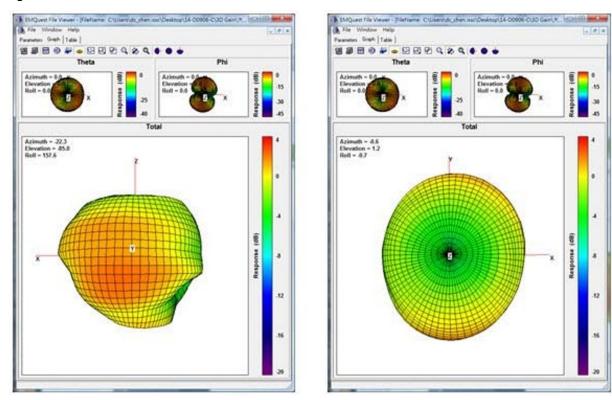

The following figure illustrates the 3D radiation pattern of the PCB antenna at 2438 MHz.

Figure 7-1. PCB Antenna 3D Radiation Pattern At 2438 MHz<sup>(1)</sup>

1. The preceding figure illustrates the typical radiation pattern with BTM983H module on the 45 mm x 45 mm BTM983H Carrier Board.

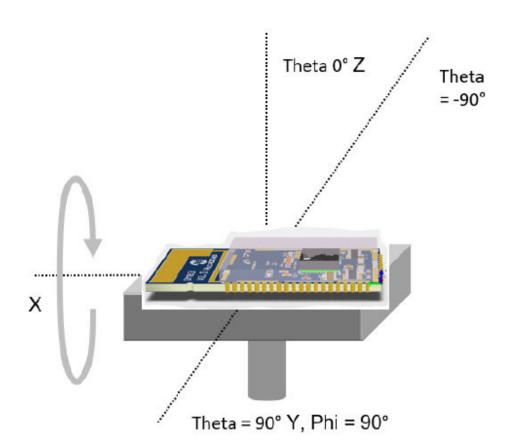

The following figure illustrates the module orientation for antenna radiation pattern Figure 7-2. Module Orientation for Radiation Pattern

# Elevation Cut (Phi Axis = 90°)

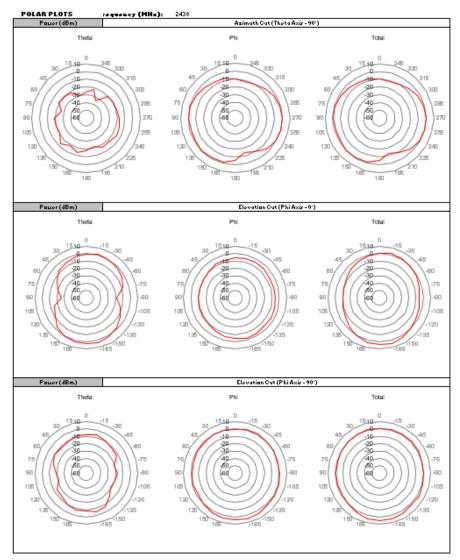

Figure 7-3. Polar Plots<sup>(1)</sup>

1. The preceding figure illustrates the typical radiation pattern with BTM983H module on the  $45 \text{ mm} \times 45 \text{ mm}$  BTM983H Carrier Board.

The following table provides the characteristics of PCB antenna with BTM983H Module mounted on BTM983H Carrier Board, plugged into BTM983H EVB.

Table 7-1. BTM983H PCB Antenna Characteristics

| Parameter  | Value                |

|------------|----------------------|

| Frequency  | 2400 MHz to 2480 MHz |

| Peak Gain  | 3.5 dBi              |

| Efficiency | 80%                  |

#### 7.2 Module Placement Guidelines

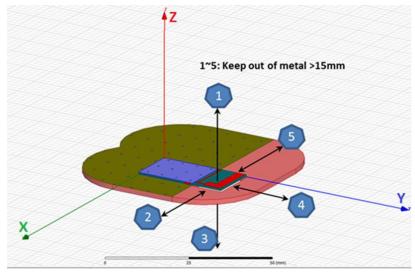

For a Bluetooth-enabled product, the antenna placement affects the overall performance of the system. The antenna requires free space to radiate RF signals and it must not be surrounded by the ground plane. It is recommended that the areas underneath the antenna on the host PCB must not contain copper on the top, inner, or bottom layers, as illustrated in the following figure.

Figure 7-4. Recommended Keep-out Area for PCB Antenna

A low-impedance ground plane ensures the best radio performance (best range, lowest noise). The ground plane can be extended beyond the minimum recommendation as required for the main Printed Circuit Board (PCB) Electromagnetic Compatibility (EMC) noise reduction. For the best range performance, keep all external metal at least 15 mm away from the on-board PCB trace antenna.

The following figure illustrates the example of recommended placement of the BTM983H module on a host board for the best RF performance.

Figure 7-5. Recommended Module Placement

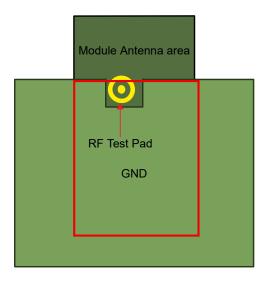

The application board provides a continuous ground plane equal to or greater than the module dimension below the module PCB. Trace routing is not recommended on the application board top layer underneath the module. Bigger ground plane is recommended for better antenna range performance. The reference radiation pattern data provided above uses a BTM983H Carrier Board with a dimension of 45 mm x 45 mm. The following figure illustrates the ground plane placement of BTM983H module on the host board. The BTM983H FCC/ISED certification requires the host board to provide a continuous ground plane with minimum size equal to the BTM983H module dimension directly beneath the

## **BTM983H**

## **PCB Antenna Information**

module (16mmx19mm). Provide ground plane with distributed via stitching. Avoid trace routing directly under the module. A small cut out can be provided on the host PCB below the module RF test point in order to solder pig tail SMA cable and perform conducted RF measurements.

Figure 7-6. Ground Plane on Host Application Board

No PCB area

**Top View**

No copper, No component, and Keep-out area

## 8. Physical Dimensions

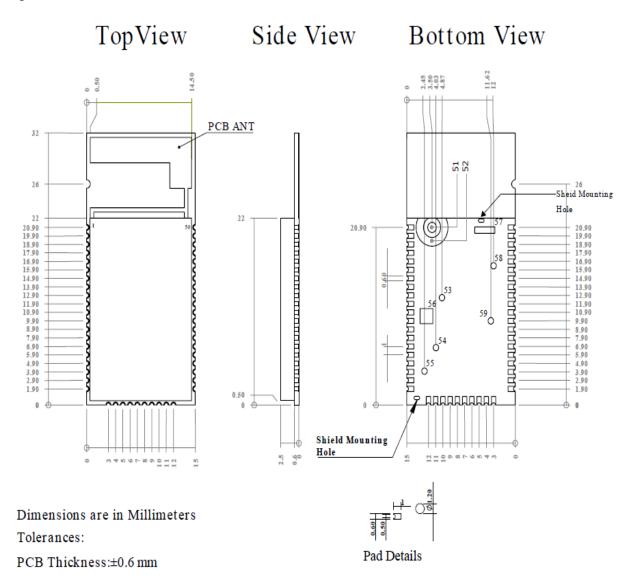

The following figures illustrate the PCB dimension and the recommended PCB footprint of the BTM983H module.

Figure 8-1. BTM983H Module PCB Dimension

Note: PCB dimensions: X: 15.0 mm, Y: 32.0 mm and tolerances: 0.25 mm.

Pins 51-59 (except 56 and 57) are used only for testing purpose.

Pins 56-57 are GND pads. It is recommended to have these pads included in

the module footprint on the host board.

Figure 8-2. Recommended PCB Footprint

## 9. Electrical Specifications

This section provides an overview of the BTM983H stereo audio module electrical characteristics. The following table provides the absolute maximum ratings for the BTM983H module.

Table 9-1. Absolute Maximum Ratings

| Parameter                                     | Min. | Тур. | Max. | Unit |

|-----------------------------------------------|------|------|------|------|

| Ambient temperature under bias                | -40  | _    | +85  | °C   |

| Storage temperature                           | -40  | _    | +150 | °C   |

| Battery input voltage (BAT_IN)                | _    | _    | +4.3 | V    |

| Adapter input voltage (ADAP_IN)               | _    | _    | +7   | V    |

| Maximum output current sink by any I/O pin    | _    | _    | 12   | mA   |

| Maximum output current sourced by any I/O pin | _    | _    | 12   | mA   |

Stresses listed in the preceding table cause permanent damage to the device. This is a stress rating only. The functional operation of the device at those or any other conditions and those indicated in the operation listings of this specification are not implied. Exposure to maximum rating conditions for extended periods affects device reliability.

The following tables provide the recommended operating conditions and the electrical specifications of the BTM983H module.

Table 9-2. Recommended Operating Conditions (1)

| Parameter                                       | Min. | Тур. | Max. | Unit |

|-------------------------------------------------|------|------|------|------|

| Battery input voltage (BAT_IN)                  | 3.2  | 3.8  | 4.2  | V    |

| Adapter input voltage (ADAP_IN)(2)              | 4.5  | 5    | 5.5  | V    |

| Operation temperature (T <sub>OPERATION</sub> ) | -40  | +25  | +85  | °C   |

- 1. The recommended operating condition tables reflect a typical voltage usage for the device.

- 2. ADAP\_IN is recommended to be used to charge the battery in battery powered applications, and/or applications with USB functionality, otherwise ADAP\_IN can be left floating.

Table 9-3. I/O and Reset Level (1)

| Parameter                               |                                   | Min. | Тур. | Max. | Unit |

|-----------------------------------------|-----------------------------------|------|------|------|------|

| I/O supply voltage (VDD_IO)             |                                   | 3.0  | 3.3  | 3.6  | V    |

| I/O voltage levels                      |                                   |      |      |      |      |

| VIL input logic levels low              |                                   | 0    | _    | 0.8  | V    |

| VIH input logic levels high             |                                   | 2.0  | _    | 3.6  | V    |

| VOL output logic levels low             |                                   | _    | _    | 0.4  | V    |

| VOH output logic levels high            |                                   | 2.4  | _    | _    | V    |

| RST_N Input low to high threshold point |                                   | _    | _    | 1.87 | V    |

|                                         | Input high to low threshold point | 1.25 | _    | _    | V    |

|    | continued       |      |      |      |      |

|----|-----------------|------|------|------|------|

| Pa | rameter         | Min. | Тур. | Max. | Unit |

| Th | reshold voltage | _    | 1.6  | _    | V    |

1. These parameters are characterized, but not tested on production device.

Table 9-4. Battery Charger (1)

| Parameter                                                     |                                                  | Min.               | Тур.               | Max. | Unit |

|---------------------------------------------------------------|--------------------------------------------------|--------------------|--------------------|------|------|

| Adapter input voltage (ADAP_IN)                               |                                                  | 4.6 <sup>(2)</sup> | 5.0                | 5.5  | V    |

| Supply current to charger only                                |                                                  | _                  | 3                  | 4.5  | mA   |

| Maximum battery fast charge current                           | Headroom <sup>(3)</sup> > 0.7V<br>(ADAP_IN = 5V) | _                  | 350                | _    | mA   |

|                                                               | Headroom = 0.3V to 0.7V<br>(ADAP_IN = 4.5V)      | _                  | 175 <sup>(4)</sup> | _    | mA   |

| Trickle charge voltage threshold                              |                                                  | _                  | 3                  | _    | V    |

| Battery charge termination current (% of fast charge current) |                                                  | _                  | 10                 | _    | %    |

- 1. These parameters are characterized, but not tested on production devices.

- 2. More time is required to get the battery fully charged when ADAP\_IN = 4.5V.

- 3. Headroom = VADAP\_IN VBAT\_IN.

- 4. When VADAP\_IN VBAT\_IN > 2V, the maximum fast charge current is 175 mA for thermal protection.

Table 9-5. SAR ADC Operating Conditions

| Parameter                                        | Condition                       | Min. | Тур. | Max. | Unit |

|--------------------------------------------------|---------------------------------|------|------|------|------|

| Shutdown current (I <sub>OFF</sub> )             | PDI_ADC = 1                     | _    | _    | 1    | μA   |

| Resolution                                       | _                               | _    | 10   | _    | bits |

| Effective Number of Bits (ENOB)                  | _                               | 7    | 8    | _    | bits |

| SAR core clock (F <sub>CLOCK</sub> )             | _                               | _    | 0.5  | 1    | MHz  |

| Conversion time per channel (T <sub>CONV</sub> ) | 10 F <sub>CLOCK</sub> cycles    | 10   | 20   | _    | μs   |

| Offset error (E <sub>OFFSET</sub> )              | _                               | -5   | _    | +5   | %    |

| Gain error (E <sub>GAIN</sub> )                  | _                               | _    | _    | +1   | %    |

| ADC SAR core power-up (t <sub>PU</sub> )         | PDI_ADC transitions from 1 to 0 | _    | _    | 500  | ns   |

| Input voltage range (V <sub>IN</sub> )           | Channel 8 (SK2 Pin)             | 0.25 | _    | 1.4  | V    |

|                                                  | Channel 9 (SK1 Pin)             | 0.25 | _    | 1.4  | V    |

|                                                  | Channel 10 (OTP)                | 0.25 | _    | 1.4  | V    |

|                                                  | Channel 11 (ADAP_IN Pin)        | 2.25 | _    | 12.6 | V    |

|                                                  | Channel 12 (BAT_IN Pin)         | 1.0  | _    | 5.6  | V    |

Table 9-6. LED Driver (1)

| Parameter                     | Min. | Тур. | Max. | Unit |

|-------------------------------|------|------|------|------|

| Open-drain voltage            | _    | _    | 3.6  | V    |

| Programmable current range    | 0    | _    | 5.25 | mA   |

| Intensity control             | _    | 16   | _    | step |

| Current step                  | _    | 0.35 | _    | mA   |

| Power-down open-drain current | _    | _    | 1    | μΑ   |

| Shutdown current              | _    | _    | 1    | μA   |

1. These parameters are characterized, but not tested on production devices.

Table 9-7. Audio Codec Analog-to-Digital Converter (1,4)

| Parameter (Condition)                           | Min. | Тур.   | Max. | Unit   |

|-------------------------------------------------|------|--------|------|--------|

| Resolution                                      | _    | _      | 16   | Bit    |

| Output sample rate                              | 8    | _      | 48   | kHz    |

| SNR ratio <sup>(2)</sup> (at MIC or Line-In)    | _    | 91     | _    | dB     |

| Digital gain                                    | -54  | _      | 4.85 | dB     |

| Digital gain resolution                         | _    | 2 to 6 | _    | dB     |

| MIC boost gain                                  | _    | 20     | _    | dB     |

| Analog gain                                     | _    | _      | 60   | dB     |

| Analog gain resolution                          | _    | 2.0    | _    | dB     |

| Input full-scale at maximum gain (differential) | _    | 4      | _    | mV/rms |

| Input full-scale at minimum gain (differential) | _    | 800    | _    | mV/rms |

| 3 dB bandwidth                                  | _    | 20     | _    | kHz    |

| Microphone mode (input impedance)               | _    | 24     | _    | kΩ     |

| THD+N ratio <sup>(3)</sup>                      | _    | 0.04   | _    | %      |

| THD+N ratio <sup>(3)</sup>                      | _    | -68    | _    | dB     |

- 1. These parameters are characterized, but not tested on production devices.

- 2. T = 25°C, VDD = 1.8V, 1 kHz sine wave input, bandwidth = 20 Hz to 20 kHz.

- 3. f<sub>in</sub> = 1kHz sine tone, analog gain = -3 dB, digital gain = 0 dB, bandwidth = 22K, A-weighted, sweep across -100 dBv to 6 dBv.

- 4. Measurements performed on the BTM983H EVB platform.

Table 9-8. Audio Codec Digital-to-Analog Converter(1,5)

| Parameter (Condition)                                 | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------|------|------|------|------|

| Over-sampling rate                                    | _    | 128  | _    | fs   |

| Resolution                                            | 16   | _    | 20   | Bit  |

| Output sample rate                                    | 8    | _    | 48   | kHz  |

| SNR ratio <sup>(2)</sup> (at Capless mode) for 48 kHz | _    | 95   | _    | dB   |

| SNR <sup>(2)</sup> (at Single-ended mode) for 48 kHz  | _    | 95   | _    | dB   |

| continued                          |             |      |        |      |        |  |

|------------------------------------|-------------|------|--------|------|--------|--|

| Parameter (Condition)              | Min.        | Тур. | Max.   | Unit |        |  |

| Digital gain                       |             | -54  | _      | 4.85 | dB     |  |

| Digital gain resolution            |             | _    | 2 to 6 | _    | dB     |  |

| Analog gain                        |             | -28  | _      | 3    | dB     |  |

| Analog gain resolution             |             | _    | 1      | _    | dB     |  |

| Output voltage full-scale swing (A | VDD = 1.8V) | 495  | 742.5  | _    | mV/rms |  |

| Maximum output power (16Ω loa      | d)          | _    | 34.5   | _    | mW     |  |

| Maximum output power (32Ω loa      | d)          | _    | 17.2   | _    | mW     |  |

| Allowed load                       | Resistive   | 16   | _      | _    | Ω      |  |

|                                    | Capacitive  | _    | _      | 500  | pF     |  |

| THD Ratio (3)                      |             | 0.15 | 0.02   | 0.05 | %      |  |

| THD Ratio (3)                      |             | -75  | -70    | -65  | dB     |  |

| THD+N Ratio <sup>(3)</sup>         |             | 0.03 | 0.04   | 0.05 | %      |  |

| THD+N Ratio (3)                    |             | -72  | -70    | -65  | dB     |  |

| SNR ratio (at 16Ω load) (4)        |             | _    | 95     | _    | dB     |  |

- 1. These parameters are characterized, but not tested on production devices.

- 2. T = 25°C, VDD = 1.8V, 1 kHz sine wave input, bandwidth = 20 Hz to 20 kHz.

- 3.  $f_{in}$ =1 kHz sine tone, analog gain = -3dB, digital gain = 0dB, bandwidth = 22K, A-weighting applied, sweep across -100 dBv to 6 dBv level, with various loads (16 $\Omega$ , 32 $\Omega$ , 100 k $\Omega$ )

- 4.  $f_{in} = 1$  kHz, bandwidth = 20 Hz to 20 kHz, A-weighted, -1 dBFS signal, load =16 $\Omega$ .

- 5. Measurements performed on the BTM983H EVB platform.

Table 9-9. Transmitter Section Class 1 (MPA Configuration) for BDR and EDR<sup>(1,4)</sup>

| Parameter <sup>(2,3)</sup> | Bluetooth Specification | Min. | Тур. | Max. | Unit |

|----------------------------|-------------------------|------|------|------|------|

| Transmit power BDR         | 0 to 20                 | _    | 10.4 | _    | dBm  |

| Transmit power EDR 2M      | 0 to 20                 | _    | 9.2  | _    | dBm  |

| Transmit power EDR 3M      | 0 to 20                 | _    | 9.2  | _    | dBm  |

- 1. These parameters are characterized, but not tested on production devices.

- 2. The RF transmit power is the average power measured for the mid-channel (Channel 39).

- 3. The RF transmit power is calibrated during production using the MP tool and MT8852 Bluetooth test equipment.

- 4. Test condition: VCC\_RF = 1.28V, temperature +25°C.

Table 9-10. Transmitter Section Class 2 (LPA Configuration) for BDR and EDR (1,4)

| Parameter <sup>(2,3)</sup> | Bluetooth Specification | Min. | Тур. | Max. | Unit |

|----------------------------|-------------------------|------|------|------|------|

| Transmit power BDR         | -6 to 4                 | _    | 2    | _    | dBm  |

| Transmit power EDR 2M      | -6 to 4                 | _    | 0.5  | _    | dBm  |

| Transmit power EDR 3M      | -6 to 4                 | _    | 0.5  | _    | dBm  |

- 1. These parameters are characterized, but not tested on production devices.

- 2. The RF transmit power is the average power measured for the mid-channel (Channel 39).

- 3. The RF transmit power is calibrated during production using the MP tool and MT8852 Bluetooth test equipment.

- 4. Test condition: VCC\_RF = 1.28V, temperature +25°C.

Table 9-11. Receiver Section for BDR/EDR/Bluetooth Low Energy<sup>(1,2)</sup>

| Parameter               | Bluetooth<br>Specification | Modulation              | Min. | Тур. | Max. | Unit |

|-------------------------|----------------------------|-------------------------|------|------|------|------|

| Sensitivity at 0.1% BER | ≤-70                       | GFSK                    | _    | -88  | _    | dBm  |

| Sensitivity at 0.01%    | ≤-70                       | π/4 DQPSK               | _    | -90  | _    | dBm  |

| RFK                     | ≤-70                       | 8 DPSK                  | _    | -84  | _    | dBm  |

| Sensitivity at 0.1% BER | ≤-70                       | Bluetooth Low<br>Energy | _    | -92  | _    | dBm  |

- 1. These parameters are characterized, but not tested on production devices.

- 2. Test condition: VCC\_RF = 1.28V with temperature +25°C.

Table 9-12. BTM983H System Current Consumption<sup>(1,2,3,6,7,8)</sup>

| Modes                     | Condition                         | Role   | Packet Type | Current (Typ.) | Unit |

|---------------------------|-----------------------------------|--------|-------------|----------------|------|

| A2DP mode                 | Internal codec, iOS Master        | Slave  | 2DH5/3DH5   | 12.05          | mA   |

|                           | Internal codec, Android™<br>Slave | Master | 3DH5        | 12.32          | mA   |

| Sniff mode <sup>(4)</sup> | Internal codec, Bluetooth         | Slave  | DM1         | 548            | μΑ   |

|                           | Low Energy disabled               | Master | 2DH1/3DH1   | 555            | μΑ   |

|                           | Internal codec, Bluetooth         | Slave  | DM1         | 832            | μΑ   |

|                           | Low ⊨nergy enabled                | Master | 2DH1/3DH1   | 863            | μΑ   |

| SCO/eSCO                  | D/eSCO Mute at both far end and   | Slave  | 2EV3        | 14.1           | mA   |

| connection                | near end                          | Master | 2EV3        | 13.94          | mA   |

| Inquiry Scan              | Bluetooth Low Energy disabled     | _      | _           | 1.35           | mA   |

|                           | Bluetooth Low Energy enabled      | _      | _           | 1.70           | mA   |

| Standby                   | System off                        | Slave  | _           | 2.81           | μА   |

| mode                      |                                   | Master | _           | 2.85           | μΑ   |

| continu                 | continued          |                        |             |                |      |  |  |  |  |

|-------------------------|--------------------|------------------------|-------------|----------------|------|--|--|--|--|

| Modes                   | Condition          | Role                   | Packet Type | Current (Typ.) | Unit |  |  |  |  |

| RF modes <sup>(5)</sup> | Continuous TX mode | Modulation<br>OFF, PL0 | _           | 59             | mA   |  |  |  |  |

|                         |                    | Modulation<br>ON, PL0  | _           | 30             | mA   |  |  |  |  |

|                         |                    | Modulation<br>OFF, PL2 | _           | 35.5           | mA   |  |  |  |  |

|                         |                    | Modulation<br>ON, PL2  | _           | 22             | mA   |  |  |  |  |

|                         | Continuous RX mode | Packet count disable   | _           | 49             | mA   |  |  |  |  |

|                         |                    | Packet count enable    | _           | 38.5           | mA   |  |  |  |  |

- 1. VBAT IN = 3.8V; current measured across BAT IN.

- 2. BTM983H module (mounted on BTM983H Carrier Board) configured in standalone mode (internal codec) with SBC, used for measurements; no LEDs, no speaker load.

- 3. iPhone<sup>®</sup>6 (iOS v12.2) and OnePlus6 (Android Oxygen version 9.0.3) used for measurements.

- 4. Auto-unsniff mode is disabled. Sniff interval is 500 ms by default; observed time to enter sniff mode is approximately 20 secs.

- 5. RF TX power is set to 10 dBm.

- 6. Current measurements average over a period of 120 secs.

- 7. Distance between DUT (BTM983H) and Bluetooth source (smartphone) is 30 cms.

- 8. All measurements are taken inside a shield room.

## 9.1 Timing Specifications

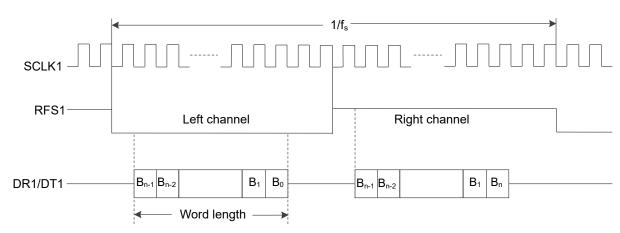

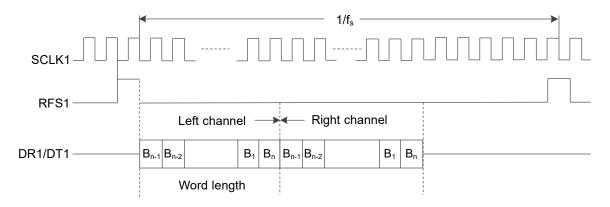

The following figures illustrate the timing diagram of the IS2083BM/BTM983H in  $I^2S$  and PCM modes.

Figure 9-1. Timing Diagram for I<sup>2</sup>S Modes (Master/Slave)

Figure 9-2. Timing Diagram for PCM Modes (Master/Slave)

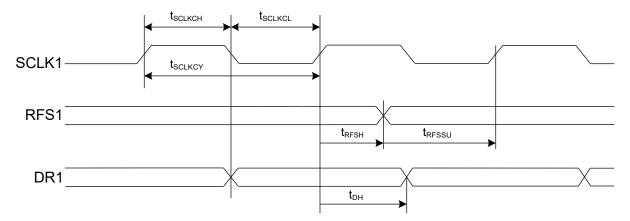

The following figure illustrates the timing diagram of the audio interface.

Figure 9-3. Audio Interface Timing Diagram

The following table provides the timing specifications of the audio interface.

Table 9-13. Audio Interface Timing Specifications (1)

| Parameter                             | Symbol              | Min. | Тур. | Max. | Unit |

|---------------------------------------|---------------------|------|------|------|------|

| SCLK1 duty ratio                      | d <sub>SCLK</sub>   | _    | 50   | _    | %    |

| SCLK1 cycle time                      | t <sub>SCLKCY</sub> | 50   | _    | _    | ns   |

| SCLK1 pulse width high                | t <sub>SCLKCH</sub> | 20   | _    | _    | ns   |

| SCLK1 pulse width low                 | t <sub>SCLKCL</sub> | 20   | _    | _    | ns   |

| RFS1 setup time to SCLK1 rising edge  | t <sub>RFSSU</sub>  | 10   | _    | _    | ns   |

| RFS1 hold time from SCLK1 rising edge | t <sub>RFSH</sub>   | 10   | _    | _    | ns   |

| DR1 hold time from SCLK1 rising edge  | t <sub>DH</sub>     | 10   | -    | _    | ns   |

1. Test Conditions: Slave mode, fs = 48 kHz, 24-bit data, and SCLK1 period = 256 fs.

# 10. Soldering Recommendations

| Reflow profile requirements                     |                   |                                 |  |  |  |  |

|-------------------------------------------------|-------------------|---------------------------------|--|--|--|--|

| Parameter Specification Reference Specification |                   |                                 |  |  |  |  |

| Average temperature gradient in                 |                   | 1~2.5°C/s to 175°C equilibrium. |  |  |  |  |

| Soak time                                       | T <sub>soak</sub> | 120~180 seconds                 |  |  |  |  |