Revision PA7

# **CM52 Integrator's Manual**

Revision PA7

# **Table of Contents**

| 1 | Introduction to the Integrator's Manual                      | 5        |

|---|--------------------------------------------------------------|----------|

|   | 1.1 OVERVIEW                                                 | 5        |

|   | 1.2 HOW TO READ THE MANUAL                                   | 5        |

|   | 1.3 SERVICE AND SUPPORT  1.3.1 WEB PAGES                     | 5<br>5   |

|   | 1.4 RELATED DOCUMENTS                                        | 6        |

|   | 1.5 ABBREVIATIONS                                            | 6        |

| 2 |                                                              | 7        |

| 2 | Integrating the CM52 Module 2.1 OVERVIEW                     | 7        |

|   | 2.2 MECHANICAL DESCRIPTION                                   | 7        |

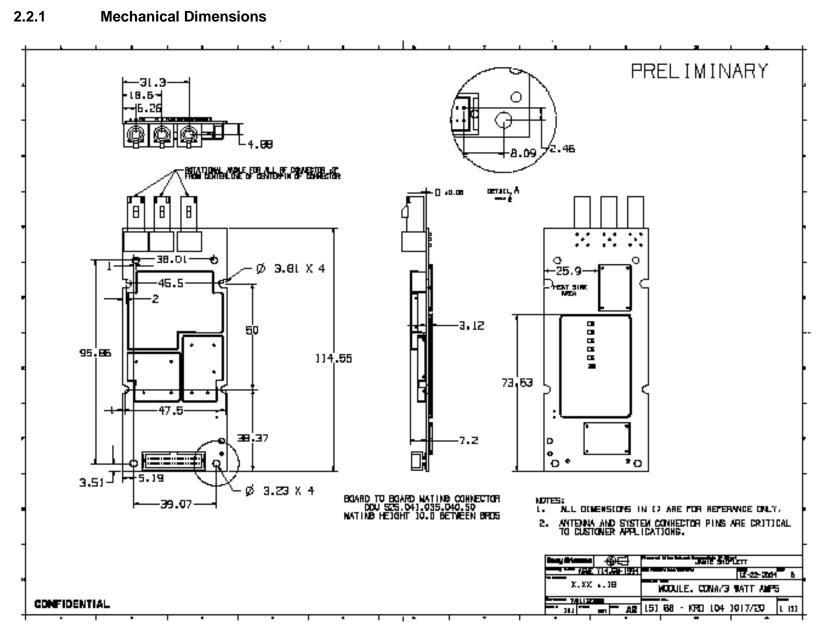

|   | 2.2.1 MECHANICAL DIMENSIONS                                  | 8        |

|   | 2.2.2 HEAT-SINK REQUIREMENTS                                 | 10       |

|   | 2.2.3 MOUNTING HOLES                                         | 10       |

|   | 2.3 SYSTEM CONNECTOR INTERFACE                               | 11       |

|   | 2.3.1 MECHANICAL OVERVIEW                                    | 11       |

|   | 2.3.2 PINOUT                                                 | 12       |

|   | 2.3.3 LOGIC LEVELS 2.4 POWER SUPPLY                          | 13<br>13 |

|   | 2.4.1 POWER SUPPLY AND GROUND SIGNALS                        | 13       |

|   | 2.4.1.1 POWER SUPPLY SIGNAL PINS                             | 13       |

|   | 2.4.1.2 GROUND SIGNAL PINS                                   | 14       |

|   | 2.4.2 POWER CONSUMPTION                                      | 14       |

|   | 2.4.2.1 WAKEUP-INRUSH CURRENT 2.4.2.2 CONTACT-INRUSH CURRENT | 17<br>17 |

|   | 2.4.2.3 POWER DOWN MODE (MINIMUM DC POWER CONSUMPTION)       | 17       |

|   | 2.4.3 VREF REQUIREMENTS                                      | 17       |

|   | 2.4.4 REAL TIME CLOCK (RTC) CIRCUIT                          | 18       |

|   | 2.5 AUDIO INTERFACE                                          | 18       |

|   | 2.5.1 DIGITAL AUDIO                                          | 19       |

|   | 2.5.1.1 DATA FORMAT                                          | 19       |

|   | 2.5.1.2 TIMING<br>2.5.2 ANALOG AUDIO                         | 19<br>21 |

|   | 2.6 SERIAL DATA INTERFACE                                    | 24       |

|   | 2.7 ANTENNA INTERFACE                                        | 25       |

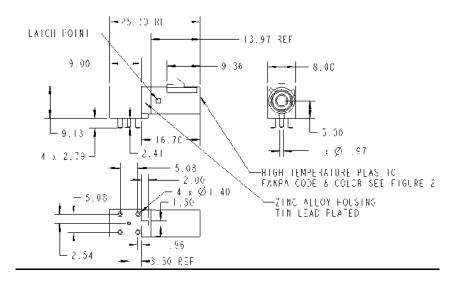

|   | 2.7.1 ANTENNA CONNECTOR                                      | 25       |

|   | 2.7.2 RF OUTPUT POWER                                        | 27       |

|   | 2.7.3 CARRIER APPROVAL                                       | 27       |

|   | 2.7.4 ANTENNA DIAGNOSTICS                                    | 27       |

| 3 | · · · · · · · · · · · · · · · · · · ·                        | 29       |

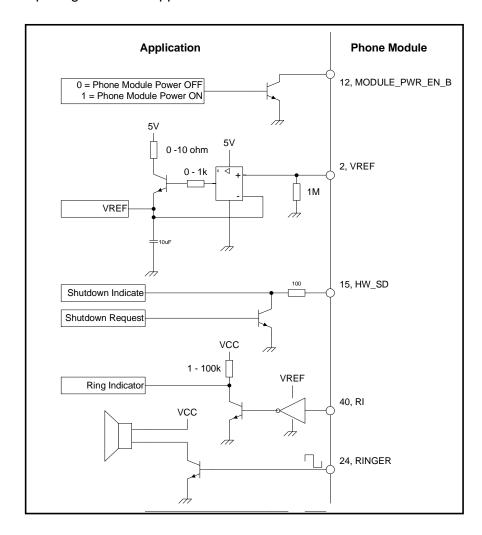

|   | 3.1 STATUS GROUP RECOMMENDED CIRCUITRY                       | 29       |

|   | 3.1.1 MODULE_PWR_EN_B                                        | 30       |

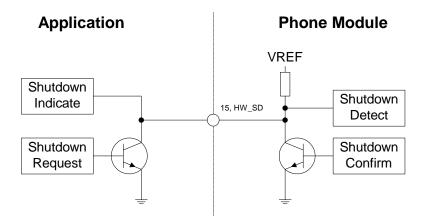

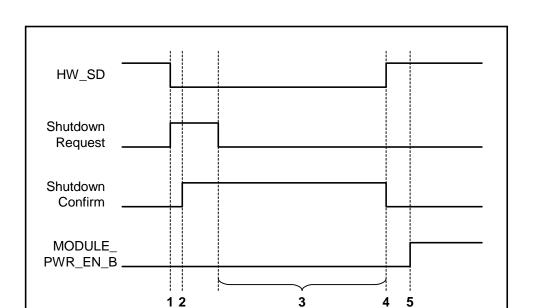

|   | 3.1.2 VREF<br>3.1.3 HW SD                                    | 30<br>30 |

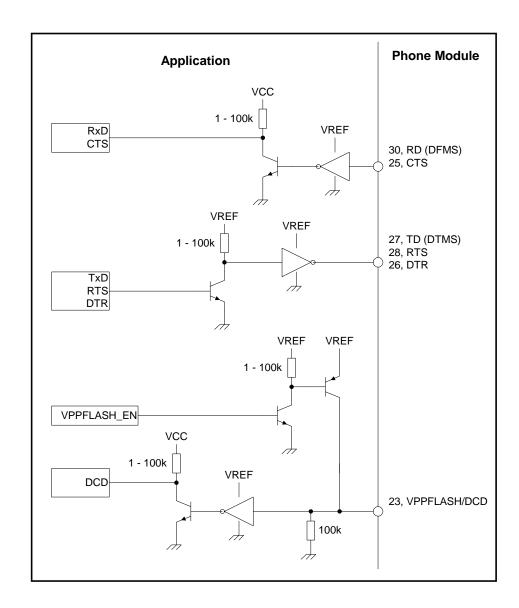

|   | 3.2 DATA GROUP RECOMMENDED CIRCUITRY                         | 31       |

|   | 3.2.1 VPPFLASH/DCD                                           | 32       |

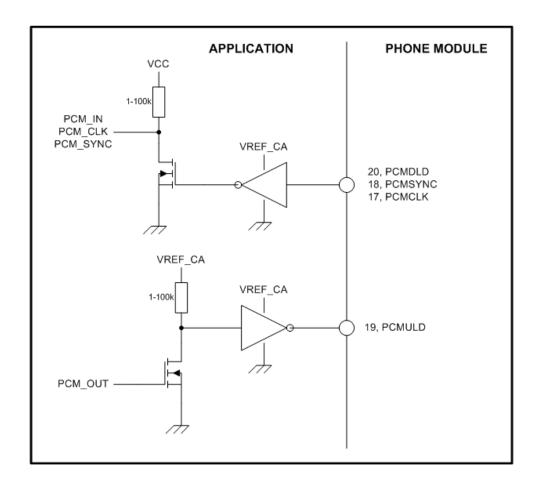

|   | 3.3 PCM GROUP RECOMMENDED CIRCUITRY                          | 33       |

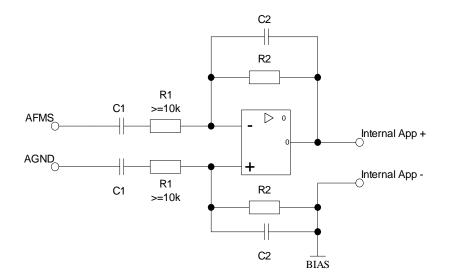

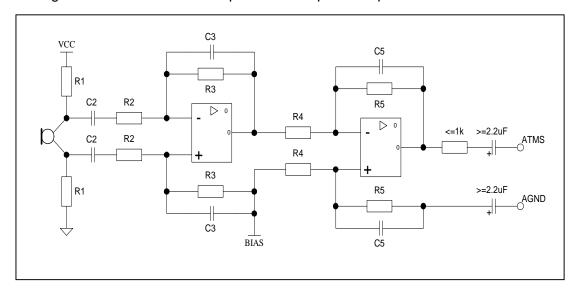

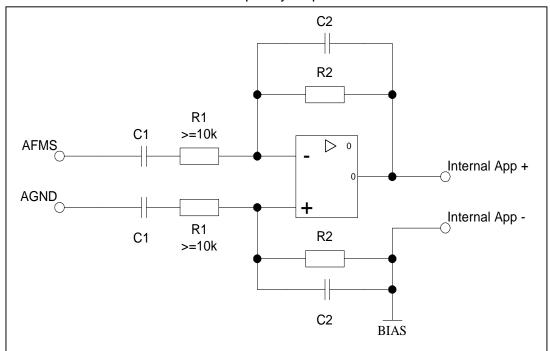

|   | 3.4 ANALOG AUDIO GROUP RECOMMENDED CIRCUITRY                 | 34       |

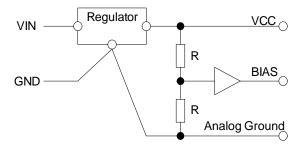

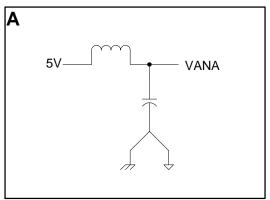

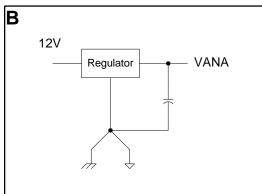

|   | 3.4.1 CREATING AN ANALOG GROUND                              | 34       |

|   | 3.4.2 CREATING AN ANALOG REFERENCE VOLTAGE (BIAS)            | 34       |

|   | 3.4.3 ANALOG GROUND VS. AGND                                 | 35       |

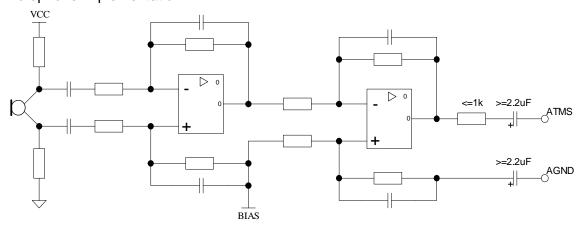

|   | 3.4.4 MICROPHONE PATH 3.4.5 LOUDSPEAKER PATH                 | 35<br>36 |

|   | 3.5 SYSTEM CONNECTOR IO FUNCTIONALITY                        | 37       |

|   | 5.5. 5. 5. 5. 5. 5. 5. 5. 5. 5. 5. 5. 5.                     | ٠,       |

Confidential USERS MANUAL

Document number 4/198 17-LXE 108 566 Uen

Revision PA7

| 4 Functional Description                | 40 |

|-----------------------------------------|----|

| 5 Hints for Integrating the Module      | 40 |

| 5.1 PRECAUTIONS                         | 40 |

| 5.2 WHERE TO INSTALL THE MODULE         | 40 |

| 5.3 SAFETY STANDARDS                    | 40 |

| 5.4 ANTENNA                             | 41 |

| 5.4.1 ANTENNA TYPE                      | 41 |

| 5.4.2 ANTENNA PLACEMENT                 | 41 |

| 5.5 POSSIBLE COMMUNICATION DISTURBANCES | 41 |

| 6 Technical Data                        | 42 |

PA7

## **Tables**

| TABLE 2: PIN-OUT OF THE SYSTEM CONNECTOR HEADER       12         TABLE 3: CMOS OUTPUT / INPUT ELECTRICAL CHARACTERISTICS       13         TABLE 4: CM52 POWER SUPPLY REQUIREMENTS.       13         TABLE 5: CM52 POWER SUPPLY SIGNALS.       14         TABLE 6: CM52 GROUND SIGNALS.       14         TABLE 7: VCC_AUX SUPPLY POWER CONSUMPTION       15         TABLE 8: VCC_MAIN SUPPLY POWER CONSUMPTION       16         TABLE 9: VREF SUPPLY DETAILS       17         TABLE 10: CM52 AUDIO SIGNALS.       18         TABLE 11: CM52 DIGITAL AUDIO SIGNALS.       19         TABLE 12: PCM TIMING PARAMETERS.       20         TABLE 13: CM52 ANALOG AUDIO SIGNALS.       21         TABLE 14: AUDIO CHARACTERISTICS       21         TABLE 15: SERIAL DATA CHANNELS.       24         TABLE 15: MOBILE STATION NOMINAL ANALOG POWER LEVELS       24         TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER       27         TABLE 18: PIN DIRECTION FOR GENERAL PURPOSE SIGNALS.       39         Figure 2: CM52 SECONDARY SIDE       7         FIGURE 3: MCCHANICAL DIMENSIONS DRAWING.       8         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING.       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING.       11 | TABLE 1: SYSTEM CONNECTOR AND MATING PART NUMBERS       | 11 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----|

| TABLE 4: CM52 POWER SUPPLY REQUIREMENTS.       13         TABLE 5: CM52 POWER SUPPLY SIGNALS       14         TABLE 6: CM52 GROUND SIGNALS       14         TABLE 7: VCC_AUX SUPPLY POWER CONSUMPTION       15         TABLE 8: VCC_MAIN SUPPLY POWER CONSUMPTION       16         TABLE 9: VREF SUPPLY DETAILS.       17         TABLE 10: CM52 AUDIO SIGNALS.       18         TABLE 11: CM52 DIGITAL AUDIO SIGNALS.       19         TABLE 12: PCM TIMING PARAMETERS.       20         TABLE 13: CM52 ANALOG AUDIO SIGNALS.       21         TABLE 14: AUDIO CHARACTERISTICS       21         TABLE 15: SERIAL DATA CHANNELS       24         TABLE 16: MOBILE STATION NOMINAL ANALOG POWER LEVELS       24         TABLE 17: MOBILE STATION OFM MAXIMUM OUTPUT POWER       27         TABLE 18: PIN DIRECTION FOR GENERAL PURPOSE SIGNALS       39         FIGURE 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                               | TABLE 2: PIN-OUT OF THE SYSTEM CONNECTOR HEADER         | 12 |

| TABLE 5: CM52 POWER SUPPLY SIGNALS       14         TABLE 6: CM52 GROUND SIGNALS       14         TABLE 7: VCC_AUX SUPPLY POWER CONSUMPTION       15         TABLE 8: VCC_MAIN SUPPLY POWER CONSUMPTION       16         TABLE 9: VREF SUPPLY DETAILS.       17         TABLE 10: CM52 AUDIO SIGNALS.       18         TABLE 11: CM52 DIGITAL AUDIO SIGNALS.       19         TABLE 12: PCM TIMING PARAMETERS.       20         TABLE 13: CM52 ANALOG AUDIO SIGNALS.       21         TABLE 14: AUDIO CHARACTERISTICS       21         TABLE 15: SERIAL DATA CHANNELS       24         TABLE 16: MOBILE STATION NOMINAL ANALOG POWER LEVELS       27         TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER       27         TABLE 18: PIN DIRECTION FOR GENERAL PURPOSE SIGNALS       39         Figures         Figure 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                           | TABLE 3: CMOS OUTPUT / INPUT ELECTRICAL CHARACTERISTICS | 13 |

| TABLE 6: CM52 GROUND SIGNALS       14         TABLE 7: VCC_AUX SUPPLY POWER CONSUMPTION       15         TABLE 8: VCC_MAIN SUPPLY POWER CONSUMPTION       16         TABLE 9: VREF SUPPLY DETAILS       17         TABLE 10: CM52 AUDIO SIGNALS       18         TABLE 11: CM52 DIGITAL AUDIO SIGNALS       18         TABLE 12: PCM TIMING PARAMETERS       20         TABLE 13: CM52 ANALOG AUDIO SIGNALS       21         TABLE 14: AUDIO CHARACTERISTICS       21         TABLE 15: SERIAL DATA CHANNELS       24         TABLE 15: SERIAL DATA CHANNELS       24         TABLE 17: MOBILE STATION NOMINAL ANALOG POWER LEVELS       27         TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER       27         TABLE 18: PIN DIRECTION FOR GENERAL PURPOSE SIGNALS       39         Figures         Figure 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                 | TABLE 4: CM52 POWER SUPPLY REQUIREMENTS                 | 13 |

| TABLE 7: VCC_AUX SUPPLY POWER CONSUMPTION       15         TABLE 8: VCC_MAIN SUPPLY POWER CONSUMPTION       16         TABLE 9: VREF SUPPLY DETAILS       17         TABLE 10: CM52 AUDIO SIGNALS       18         TABLE 11: CM52 DIGITAL AUDIO SIGNALS       19         TABLE 12: PCM TIMING PARAMETERS       20         TABLE 13: CM52 ANALOG AUDIO SIGNALS       21         TABLE 13: SERIAL DATA CHANNELS       21         TABLE 15: SERIAL DATA CHANNELS       24         TABLE 16: MOBILE STATION NOMINAL ANALOG POWER LEVELS       27         TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER       27         TABLE 18: PIN DIRECTION FOR GENERAL PURPOSE SIGNALS       39         Figures         Figure 2: CM52 SECONDARY SIDE       7         FIGURE 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                  | TABLE 5: CM52 POWER SUPPLY SIGNALS                      | 14 |

| TABLE 8: VCC_MAIN SUPPLY POWER CONSUMPTION.       16         TABLE 9: VREF SUPPLY DETAILS.       17         TABLE 10: CM52 AUDIO SIGNALS.       18         TABLE 11: CM52 DIGITAL AUDIO SIGNALS.       19         TABLE 12: PCM TIMING PARAMETERS.       20         TABLE 13: CM52 ANALOG AUDIO SIGNALS.       21         TABLE 14: AUDIO CHARACTERISTICS       21         TABLE 15: SERIAL DATA CHANNELS.       24         TABLE 17: MOBILE STATION NOMINAL ANALOG POWER LEVELS.       27         TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER       27         TABLE 18: PIN DIRECTION FOR GENERAL PURPOSE SIGNALS.       39         FIGURE 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING.       8         FIGURE 4: KEEP-OUT DRAWING OF CM52.       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR.       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                            | TABLE 6: CM52 GROUND SIGNALS                            | 14 |

| TABLE 8: VCC_MAIN SUPPLY POWER CONSUMPTION.       16         TABLE 9: VREF SUPPLY DETAILS.       17         TABLE 10: CM52 AUDIO SIGNALS.       18         TABLE 11: CM52 DIGITAL AUDIO SIGNALS.       19         TABLE 12: PCM TIMING PARAMETERS.       20         TABLE 13: CM52 ANALOG AUDIO SIGNALS.       21         TABLE 14: AUDIO CHARACTERISTICS       21         TABLE 15: SERIAL DATA CHANNELS.       24         TABLE 17: MOBILE STATION NOMINAL ANALOG POWER LEVELS.       27         TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER       27         TABLE 18: PIN DIRECTION FOR GENERAL PURPOSE SIGNALS.       39         FIGURE 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING.       8         FIGURE 4: KEEP-OUT DRAWING OF CM52.       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR.       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                            |                                                         |    |

| TABLE 9: VREF SUPPLY DETAILS       17         TABLE 10: CM52 AUDIO SIGNALS       18         TABLE 11: CM52 DIGITAL AUDIO SIGNALS       19         TABLE 12: PCM TIMING PARAMETERS       20         TABLE 13: CM52 ANALOG AUDIO SIGNALS       21         TABLE 14: AUDIO CHARACTERISTICS       21         TABLE 15: SERIAL DATA CHANNELS       24         TABLE 16: MOBILE STATION NOMINAL ANALOG POWER LEVELS       27         TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER       27         TABLE 18: PIN DIRECTION FOR GENERAL PURPOSE SIGNALS       39         FIGURE 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 8: PCM TIMING DIAGRAM       20         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                                        | TABLE 8: VCC MAIN SUPPLY POWER CONSUMPTION              | 16 |

| TABLE 10: CM52 AUDIO SIGNALS.       18         TABLE 11: CM52 DIGITAL AUDIO SIGNALS.       19         TABLE 12: PCM TIMING PARAMETERS       20         TABLE 13: CM52 ANALOG AUDIO SIGNALS.       21         TABLE 14: AUDIO CHARACTERISTICS       21         TABLE 15: SERIAL DATA CHANNELS       24         TABLE 16: MOBILE STATION NOMINAL ANALOG POWER LEVELS.       27         TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER       27         TABLE 18: PIN DIRECTION FOR GENERAL PURPOSE SIGNALS.       39         Figures         Figure 1: CM52 PRIMARY SIDE       7         FIGURE 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 8: PCM TIMING DIAGRAM       18         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                     | TABLE 9: VREF SUPPLY DETAILS                            | 17 |

| TABLE 12: PCM TIMING PARAMETERS       20         TABLE 13: CM52 ANALOG AUDIO SIGNALS       21         TABLE 14: AUDIO CHARACTERISTICS       21         TABLE 15: SERIAL DATA CHANNELS       24         TABLE 16: MOBILE STATION NOMINAL ANALOG POWER LEVELS       27         TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER       27         TABLE 18: PIN DIRECTION FOR GENERAL PURPOSE SIGNALS       39         Figures         Figure 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 8: PCM TIMING DIAGRAM       20         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                                                                                                                                                                          |                                                         |    |

| TABLE 12: PCM TIMING PARAMETERS       20         TABLE 13: CM52 ANALOG AUDIO SIGNALS       21         TABLE 14: AUDIO CHARACTERISTICS       21         TABLE 15: SERIAL DATA CHANNELS       24         TABLE 16: MOBILE STATION NOMINAL ANALOG POWER LEVELS       27         TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER       27         TABLE 18: PIN DIRECTION FOR GENERAL PURPOSE SIGNALS       39         Figures         Figure 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 8: PCM TIMING DIAGRAM       20         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                                                                                                                                                                          | TABLE 11: CM52 DIGITAL AUDIO SIGNALS                    | 19 |

| TABLE 13: CM52 ANALOG AUDIO SIGNALS       21         TABLE 14: AUDIO CHARACTERISTICS       21         TABLE 15: SERIAL DATA CHANNELS       24         TABLE 16: MOBILE STATION NOMINAL ANALOG POWER LEVELS       27         TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER       27         TABLE 18: PIN DIRECTION FOR GENERAL PURPOSE SIGNALS       39         FIGURE 2: CM52 PRIMARY SIDE       7         FIGURE 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 8: PCM TIMING DIAGRAM       18         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |    |

| TABLE 14: AUDIO CHARACTERISTICS       21         TABLE 15: SERIAL DATA CHANNELS       24         TABLE 16: MOBILE STATION NOMINAL ANALOG POWER LEVELS       27         TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER       27         TABLE 18: PIN DIRECTION FOR GENERAL PURPOSE SIGNALS       39         FIGURE 1: CM52 PRIMARY SIDE       7         FIGURE 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 8: PCM TIMING DIAGRAM       18         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                         |    |

| TABLE 15: SERIAL DATA CHANNELS       24         TABLE 16: MOBILE STATION NOMINAL ANALOG POWER LEVELS       27         TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER       27         TABLE 18: PIN DIRECTION FOR GENERAL PURPOSE SIGNALS       39         FIGURE 1: CM52 PRIMARY SIDE       7         FIGURE 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 8: PCM TIMING DIAGRAM       20         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                         |    |

| TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                         |    |

| TABLE 17: MOBILE STATION CDMA MAXIMUM OUTPUT POWER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TABLE 16: MOBILE STATION NOMINAL ANALOG POWER LEVELS    | 27 |

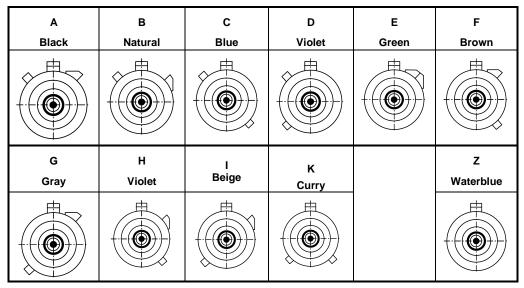

| FIGURE 1: CM52 PRIMARY SIDE  FIGURE 2: CM52 SECONDARY SIDE  FIGURE 3: MECHANICAL DIMENSIONS DRAWING  FIGURE 4: KEEP-OUT DRAWING OF CM52  FIGURE 5: 40-PIN SYSTEM CONNECTOR  FIGURE 6: 40-PIN SYSTEM CONNECTOR  FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM  FIGURE 8: PCM TIMING DIAGRAM  FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS  23  24  25  25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                         |    |

| FIGURE 1: CM52 PRIMARY SIDE       7         FIGURE 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 8: PCM TIMING DIAGRAM       20         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                         |    |

| FIGURE 1: CM52 PRIMARY SIDE       7         FIGURE 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 8: PCM TIMING DIAGRAM       20         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                         |    |

| FIGURE 1: CM52 PRIMARY SIDE       7         FIGURE 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 8: PCM TIMING DIAGRAM       20         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figures                                                 |    |

| FIGURE 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 8: PCM TIMING DIAGRAM       20         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | i igaroo                                                |    |

| FIGURE 2: CM52 SECONDARY SIDE       7         FIGURE 3: MECHANICAL DIMENSIONS DRAWING       8         FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 8: PCM TIMING DIAGRAM       20         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FIGURE 1: CM52 PRIMARY SIDE                             | 7  |

| FIGURE 3: MECHANICAL DIMENSIONS DRAWING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                         |    |

| FIGURE 4: KEEP-OUT DRAWING OF CM52       9         FIGURE 5: 40-PIN SYSTEM CONNECTOR       11         FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING       11         FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM       18         FIGURE 8: PCM TIMING DIAGRAM       20         FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                         |    |

| FIGURE 5: 40-PIN SYSTEM CONNECTOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |    |

| FIGURE 6: 40-PIN SYSTEM CONNECTOR PIN NUMBERING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                         |    |

| FIGURE 7: RTC FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         |    |

| FIGURE 8: PCM TIMING DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                         |    |

| FIGURE 9: COLOR AND KEYING FOR VARIOUS FAKRA CONNECTORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                         |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                         |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                         |    |

# **Revision History**

| Release | Date       | Summary of Changes                                               |

|---------|------------|------------------------------------------------------------------|

| PA1     | 05/07/2004 | Initial Draft                                                    |

| PA2     | 09/01/2004 | Formatting                                                       |

| PA3     | 11/17/2004 | Updated Chapters 1 & 2                                           |

| PA4     | 11/29/2004 | Updated with review feedback                                     |

| PA5     | 12/1/2004  | Updated the List of Tables and Figures                           |

| PA6     | 06/16/2005 | Current Consumption Table, RTC Block Diagram, Mechanical Drawing |

Revision PA7

## 1 Introduction to the Integrator's Manual

### 1.1 Overview

This manual is for use as a guide to the setup, installation, and use of the CM52 module into your application. The module may be tested using the developer's board, which is supplied together with all the necessary tools in the Developer's Kit.

#### 1.2 How to read the manual

This manual is divided into six chapters:

**Chapter 1** gives a general view of the integrator's manual. A list of related documents as well as a list of abbreviations, used throughout the manual, is also included. Information concerning service and support is also presented.

**Chapter 2** focuses on helping the hardware developer to integrate the CM52 hardware into their application. An overview of the mechanical and electrical information is provided. Also, interface specifications, RF output power, and power supply issues are included in this chapter.

**Chapter 3** contains information on recommended circuitry needed to ensure proper performance from the CM52 module.

Chapter 4 describes several of the common cellular functions available with the CM52.

**Chapter 5** provides some hints for integrating the module.

Chapter 6 provides a summary of the technical data for the CM52 module.

### 1.3 Service and Support

### 1.3.1 Web Pages

Please look at our web page for more information about where you can buy our modules or for recommendations of accessories and components. The address is:

http://www.sonyericsson.com/m2m

To register for product news and announcements or for product questions, contact the Sony Ericsson modules technical support group:

• **Telephone**: 919-472-1122

• Email: M2Msupport.Americas@sonyericsson.com

PA7

4/190 17-LXL 100

### 1.4 Related Documents

CM52 AT Command Manual – Details the AT command interface for the CM52

The CM52 is based upon the following mobile standards:

- IS-2000 Release 0 (1XRTT), MOB\_P\_REV CDMA protocol

- TIA/EIA/IS-91 Mobile Station Base Station Compatibility Standard for 800 MHz Analog Cellular

- TIA/EIA-98-D Recommended Minimum Performance Standards for Dual-Mode Spread Spectrum Mobile Stations

### 1.5 Abbreviations

| Abbicviations        |                                  |  |

|----------------------|----------------------------------|--|

| AGND                 | Analog Reference                 |  |

| AMPS                 | Advanced Mobile Phone System     |  |

| AT Attention Command |                                  |  |

| CDMA                 | Code Division Multiple Access    |  |

| CTS                  | Clear to Send                    |  |

| DCD                  | Data Carrier Detect              |  |

| DFMS                 | Data from Mobile Station         |  |

| DTMS                 | Data to Mobile Station           |  |

| DTR                  | Data Terminal Ready              |  |

| EMI                  | Electromagnetic Interference     |  |

| ESD                  | Electrostatic Discharge          |  |

| GND                  | Chassis GrouND                   |  |

| IRA                  | International Reference Alphabet |  |

| LSB                  | Least Significant Bit            |  |

| ME                   | Mobile Equipment                 |  |

| MO                   | Mobile Originated                |  |

| MS                   | Mobile Station                   |  |

| MT                   | Mobile Terminated                |  |

| OEM                  | Original Equipment Manufacturer  |  |

| PCB                  | Printed Circuit Board            |  |

| PCM                  | Pulse Code Modulation            |  |

| PIN                  | Personal Identification Number   |  |

| RD                   | Receive Data, also known as DFMS |  |

| RF                   | Radio Frequency                  |  |

| RTS                  | Request to Send                  |  |

| SMS                  | Short Message Service            |  |

| TD                   | Transmit Data, also know as DTMS |  |

|                      |                                  |  |

## 2 Integrating the CM52 Module

### 2.1 Overview

The CM52 is a dual band, dual mode CDMA transceiver module. It operates in the 800 MHz band for CDMA and AMPS and in the 1900 MHz band for CDMA. It is designed for consumer and OEM industrial voice and data applications.

The CM52 module is intended for mounting into an application developer's chassis to provide wireless communication capability for the product. The target chassis could be in a wide variety of forms such as a residential electric meter, a point of sale terminal, an alarm panel, or an automobile console. All initial configuration, mode control, and operational commands are issued to the module over an RS-232 serial port using a flexible AT command format. The module circuitry has been designed to meet the environmental requirements of a large range of commercial and industrial users.

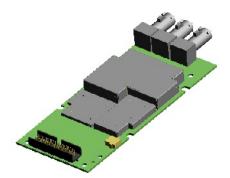

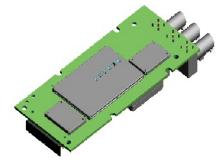

## 2.2 Mechanical Description

The CM52 has no mechanical elements other than the main PCB assembly. All critical electronic components are shielded using six cans to prevent internal and external electromagnetic interference from degrading the module's performance and to prevent the module from interfering with other nearby devices. The module is plugged into the fixed mating connector and secured with four screws.

The antenna interface is provided via a board mounted RF connector at the opposite end of the board from the system connector. See Section 2.8 for more information on antenna connector options.

The module has no keypad, display, microphone, speaker, or battery. The following figures show a mechanical drawing and physical dimensions of the module.

**Note!** All the measurements are in millimeters.

Figure 1: CM52 Primary Side

Figure 2: CM52 Secondary Side

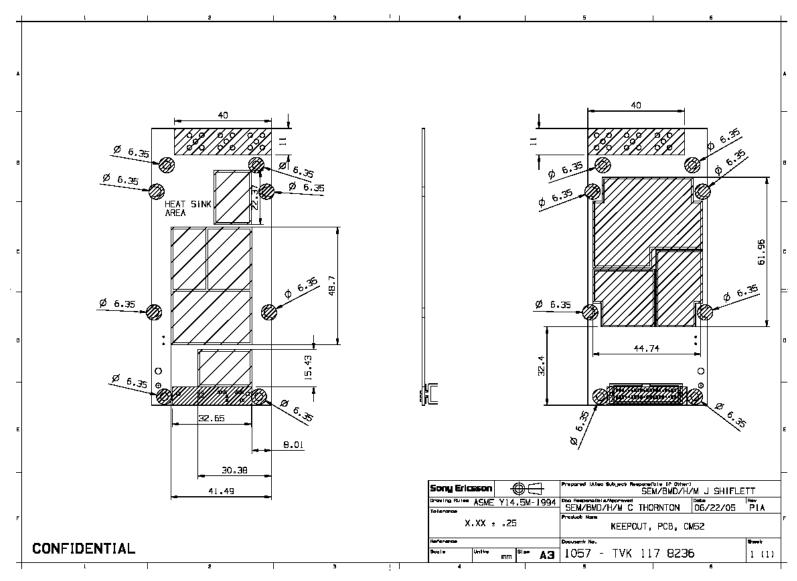

**Figure 3: Mechanical Dimensions Drawing**

Revision PA7

Figure 4: Keep-out Drawing of CM52

Revision PA7

## 2.2.2 Heat-Sink Requirements

The application is required to provide a heat-sink for the 3W AMPS capabilities of the CM52.

The application should be designed to provide a heat sink with a thermal resistance of 4.0 °C/W.

For applications that disable the 3W mode (Class I) and only operate in 0.6W mode (Class III) a heat-sink is not required.

### 2.2.3 Mounting Holes

Mounting holes and tabs are provided for proper mechanical support of the CM52 module in the customer's application. OEM application must provide sufficient mechanical retention using the mounting holes and/or tabs or some other means. The system connector and RF connector connections should not be used as a means of mechanical support. Also, please note that the mounting holes may not substitute for the actual grounding pins provided via the system connector.

PA7

### 2.3 System Connector Interface

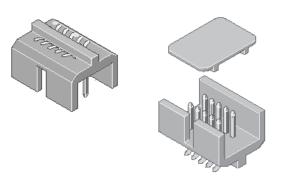

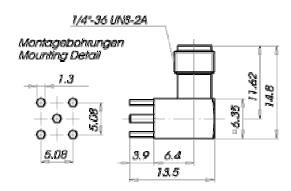

#### 2.3.1 Mechanical Overview

External interfaces to the module are made primarily through a 40 pin, standard 0.050-inch pitch, ODU header show below.

#### **Features**

- Vacuum adapter plate

- SMT version

- pin cross-section 0.38 x 0.38 mm

- 10-20-30-40-50 positions available

- · without guide pins

Figure 5: 40-Pin System Connector

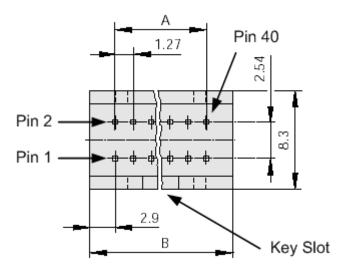

Figure 6: 40-Pin System Connector Pin Numbering

| Description             | ODU Part Number     | Dimension A | Dimension B |

|-------------------------|---------------------|-------------|-------------|

| System Connector        | 515.569.035.140.xxx | 24.13 mm    | 22.86 mm    |

| Mating Ribbon Connector | 525.060.035.040.xxx |             |             |

| SMT Mating Header       | 525.041.035.040.xxx |             |             |

| Ribbon cable, AWG 30    | 921.659.031.040.000 |             |             |

**Table 1: System Connector and Mating Part Numbers**

Please consult the ODU site for more information on mating options: <a href="http://www.odu.de">http://www.odu.de</a>

4/198 17-LXE 108 566 Uen

PA7

#### 2.3.2 **Pinout**

| PIHOU |                    |                                                                 |  |

|-------|--------------------|-----------------------------------------------------------------|--|

| _ Pin | Signal             | Description                                                     |  |

| 1     | I/O_1 / Timemark   | Reserved                                                        |  |

|       |                    | 1 PPS output from GPS chip <sup>1</sup>                         |  |

| 2     | VREF               | Logic Voltage Reference                                         |  |

| 3     | I/O_3 / GPS_FIX    | Reserved                                                        |  |

|       |                    | Logic HIGH signal to indicate active GPS Fix 1                  |  |

| 4     | I/O_4 / VRTC       | Reserved                                                        |  |

|       |                    | Supply pin for RTC <sup>2</sup> and GPS regulators <sup>1</sup> |  |

| 5     | GND                | Chassis Ground                                                  |  |

| 6     | GND                | Chassis Ground                                                  |  |

| 7     | AFMS               | Analog Audio from module                                        |  |

| 8     | GND                | Chassis Ground                                                  |  |

| 9     | AGND               | Analog Reference                                                |  |

| 10    | ATMS               | Analog Audio to module                                          |  |

| 11    | INPUT1 / UART3_RX  | Reserved                                                        |  |

|       |                    | Receive Data for UART3 <sup>1</sup>                             |  |

| 12    | MODULE_PWR_EN_B    | Switches the module on/off (hardware-wise), active low          |  |

| 13    | OUTPUT1 / UART3 TX | Reserved                                                        |  |

| 10    |                    | Transmit Data for UART3 <sup>1</sup>                            |  |

| 14    | OUTPUT2            | Reserved                                                        |  |

| 15    | HW_SD              | Hardware shutdown                                               |  |

|       |                    |                                                                 |  |

| 16    | INPUT2             | Reserved                                                        |  |

| 17    | PCMCLK             | PCM Clock output from Module to Application                     |  |

| 18    | PCMSYNC            | PCM Frame sync from Module to Application                       |  |

| 19    | PCMULD             | PCM Voice input to Module from Application                      |  |

| 20    | PCMDLD             | PCM Voice output from Module to Application                     |  |

| 21    | GND                | Chassis Ground                                                  |  |

| 22    | GND                | Chassis Ground                                                  |  |

| 23    | DCD / VPPFLASH     | Data Carrier Detect & Flash programming voltage input           |  |

| 24    | RINGER             | Ringer output                                                   |  |

| 25    | CTS                | Clear to send                                                   |  |

| 26    | DTR                | Data Terminal Ready                                             |  |

| 27    | TD                 | Transmit data, also known as DTMS                               |  |

| 28    | RTS                | Request to Send                                                 |  |

| 29    | VCC_AUX            | 13.8 VDC supply input                                           |  |

| 30    | RD                 | Receive data, also known as DFMS                                |  |

| 31    | VCC_AUX            | 13.8 VDC supply input                                           |  |

| 32    | VCC_AUX            | 13.8 VDC supply input                                           |  |

| 33    | VCC_MAIN           | 5 VDC regulated supply input                                    |  |

| 34    | VCC_MAIN           | 5 VDC regulated supply input                                    |  |

| 35    | SDA_SPI_IN         | Reserved                                                        |  |

| 36    | SCL_SPI_CLK        | Reserved                                                        |  |

| 37    | SYS_DTM_2          | Transmit Data for UART2                                         |  |

| 5,    | 0.0_D.m_2          | Transmit Data for GPS 1                                         |  |

| 38    | SPI_OUT            | Reserved                                                        |  |

|       |                    | Receive Data for UART2                                          |  |

|       |                    | Receive Data for GPS <sup>1</sup>                               |  |

| 40    | DI                 |                                                                 |  |

| 40    | RI                 | Ring Indicator                                                  |  |

Table 2: Pin-out of the System Connector Header

<sup>&</sup>lt;sup>1</sup> Default function if GPS option on board. <sup>2</sup> Default function if RTC option on board

### 2.3.3 Logic Levels

Many of the signals present in the interface are CMOS signals where the following levels apply. The nominal voltage level for the CMOS signals is 2.9 V.

| Doromotoro                                          | Test            | Limits |      | llu:to |

|-----------------------------------------------------|-----------------|--------|------|--------|

| Parameters                                          | Conditions      | Min    | Max  | Units  |

| High level output voltage ( $I_{OH} = 800 \mu A$ )  | V <sub>OH</sub> | 2.45   | 3.1  | Volts  |

| Low level output voltage ( $I_{OL} = 800 \mu A$ )   | V <sub>OL</sub> | 0      | 0.45 | Volts  |

| High level input voltage (V <sub>IH</sub> = 800 μA) | V <sub>IH</sub> | 1.9    | 3.1  | Volts  |

| Low level input voltage (V <sub>IL</sub> = 800 μA)  | $V_{IL}$        | 0      | 0.9  | Volts  |

**Table 3: CMOS Output / Input Electrical Characteristics**

### 2.4 Power Supply

The CM52 requires a dual DC power supply implementation in the application. VCC\_MAIN provides power to the entire radio while VCC\_AUX provides power for the 3-Watt functionality and biasing for the RF switches. VCC\_AUX must be present if the 3W option is provided even if it is not used. If the 3W circuitry is not populated then VCC\_AUX is not required.

The following table summarizes the power supply requirements from the application.

| Input Supply   | Voltage    | Max. Current (Amps) | Max. Ripple (mVpp) |             |  |

|----------------|------------|---------------------|--------------------|-------------|--|

|                | (Volts DC) | Operation           | 0- 4KHz            | 4 KHz-10MHz |  |

| VCC_MAIN       | 5.00 ± 10% | 1.0                 | 100mVpp            | 50mVpp      |  |

| VCC_AUX        | 13.8 ± 20% | 1.3                 | 600mVpp            | 240mVpp     |  |

| VRTC(no GPS)   | 1.8 to 3.9 | 1.2 µ               |                    |             |  |

| VRTC(with GPS) | 3.4 to 3.9 | 500 μ               |                    |             |  |

**Table 4: CM52 Power Supply Requirements**

### 2.4.1 Power Supply and Ground Signals

### 2.4.1.1 Power Supply Signal Pins

Following is a list of the power supply pins:

| Pin                               | Signal            | Description                                  |

|-----------------------------------|-------------------|----------------------------------------------|

| 4                                 | VRTC <sup>3</sup> | 1.8 V to 3.9V ( 3.4V to 3.9V if GPS mounted) |

| 29                                | VCC_AUX           | 13.8 volt ± 20%                              |

| 31                                | VCC_AUX           | 13.8 volt ± 20%                              |

| <b>32</b> VCC_AUX 13.8 volt ± 20% |                   | 13.8 volt ± 20%                              |

| 33                                | VCC_MAIN          | 5 volt ± 10% regulated                       |

| 34                                | VCC_MAIN          | 5 volt ± 10% regulated                       |

**Table 5: CM52 Power Supply Signals**

## 2.4.1.2 Ground Signal Pins<sup>3</sup>

The ground signal in the CM52 is Digital Ground, **GND**, connected to the system connector interface through pin numbers 5, 6, 8, 21 and 22.

Following is a list of the ground pins:

| Pin | Signal | Description    |

|-----|--------|----------------|

| 5   | GND    | Digital Ground |

| 6   | GND    | Digital Ground |

| 8   | GND    | Digital Ground |

| 21  | GND    | Digital Ground |

| 22  | GND    | Digital Ground |

**Table 6: CM52 Ground Signals**

Digital Ground (GND) is the logical reference of all digital signals in the System Interface as well as the DC return of the power supply signal, VCC\_MAIN and VCC\_AUX (used for AMPS Class I operation). All 5 ground pins in the module need to be connected to the application ground. The PCB mounting holes will not substitute the regular ground connections.

### 2.4.2 Power Consumption

The following tables show typical and maximum currents that can be expected from the module for various conditions.

<sup>&</sup>lt;sup>3</sup> Only applicable to units with GPS or RTC functions

| [VCC_AUX power supply supports the 3W mode AMPS circuitry] |                  |                  |                  |       |

|------------------------------------------------------------|------------------|------------------|------------------|-------|

| Parameter                                                  | Minimum<br>Value | Typical<br>Value | Maximum<br>Value | Units |

| Input Voltage                                              | 11               | 13.8             | 16.6             | V     |

| In a Call on Power Level 0 (Power Class I)                 |                  | 0.88             | 1.3              | А     |

| In a Call on Power Level 2                                 |                  | 3.5              | 4.5              | mA    |

| AMPS Burst Duration for network update                     |                  | 0.16             |                  | S     |

| Stand-by/Idle mode (RX ON)                                 |                  | 0.5              | 1                | μA    |

| Powered Down Current Draw                                  |                  | 1                |                  | μA    |

| Inrush Current (Entering PL0)                              |                  | 16               |                  | Α     |

| Duration of Inrush (Entering PL0)                          |                  | 40               |                  | μs    |

| Inrush Current (contact)                                   |                  | 28               |                  | Α     |

| Duration of Inrush (contact)                               |                  | 40               |                  | μs    |

Table 7: VCC\_AUX Supply Power Consumption

**Note:** The typical values observed in AMPS call are made with voice channel set at 358.

4/198 17-LXE 108 566 Uen

PA7 IVCC MAIN supply is the primary CM52 power supply

Revision

| [VCC_INIAIN Supply is the primary Civisz power supply] |                  |                  |                  |       |  |  |  |  |  |

|--------------------------------------------------------|------------------|------------------|------------------|-------|--|--|--|--|--|

| Parameter                                              | Minimum<br>Value | Typical<br>Value | Maximum<br>Value | Units |  |  |  |  |  |

| Input Voltage                                          | 4.5              | 5                | 5.5              | V     |  |  |  |  |  |

| In AMPS Call on Power Level 0 (Power Class I)          |                  | 0.62             | 0.82             | A     |  |  |  |  |  |

| In AMPS Call on Power Level 2                          |                  | 0.94             | 1.4              | Α     |  |  |  |  |  |

| In CDMA call-Cellular Mode                             |                  | 0.77             | 1.2              | Α     |  |  |  |  |  |

| In CDMA call-PCS Mode                                  |                  | 0.84             | 1.3              | Α     |  |  |  |  |  |

| CDMA burst duration for Network update                 |                  | 1.2              |                  | S     |  |  |  |  |  |

| Standby/Idle Current Draw in Slotted Mode (CDMA)       |                  |                  |                  |       |  |  |  |  |  |

| 1.28 sec slot                                          |                  | 9.6              |                  | mA    |  |  |  |  |  |

| 2.56 sec slot                                          |                  | 7.2              |                  | mA    |  |  |  |  |  |

| 5.12 sec slot                                          |                  | 4.5              |                  | mA    |  |  |  |  |  |

| Stand-by/Idle mode (AMPS)                              |                  | 45               |                  | mA    |  |  |  |  |  |

| Powered Down Current Draw                              |                  | 1                | 5                | μA    |  |  |  |  |  |

| Inrush Current (on wake up)                            |                  | 2.2              | 3.3              | Α     |  |  |  |  |  |

| Duration of Inrush (on wake-up)                        |                  | 200              |                  | μs    |  |  |  |  |  |

| Inrush Current (contact)                               |                  | 9.1              | 15               | Α     |  |  |  |  |  |

| Duration of Inrush (contact)                           |                  | 150              |                  | μs    |  |  |  |  |  |

**Table 8: VCC MAIN Supply Power Consumption**

#### **Notes**

- 1. The typical current measurements noted in CDMA mode are with the following settings:

- a. CDMA-Cellular (800MHz): Band = IS-2000, Cell-Power = -104dBm, Channel Number 358

- b. CDMA-PCS (1900MHz): Band = IS-2000, Cell-Power = -104dBm, Channel Number 563 Maximum Slot Cycle Index for both 800MHz and 1900MHz modes = 1

- 2. The inrush current measurements noted here are with respect to the stand alone CM52 module at room temperature, the results might vary when the CM52 is used in the Customer Application.

- 3. Measurements are based on worst case scenario—CM52 with 3W option. Values for CM52 with no 3W option could be marginally lower.

- 4. A +20% tolerance is considered for the listed maximum values.

PA7

....

#### 2.4.2.1 Wakeup-Inrush Current

The wakeup inrush current occurs when the MODULE\_PWR\_EN\_B signal transitions from High to Low. The wakeup-inrush event occurs on the VCC\_MAIN supply input and not the VCC\_AUX supply. The magnitude of the inrush is dependent on power supply output impedance.

#### 2.4.2.2 Contact-Inrush Current

The contact inrush current simulates application of power to the VCC\_MAIN input lines and measures the impact of the input impedance of the module.

While holding the MODULE\_PWR\_EN\_B signal HIGH, a direct contact of VCC\_MAIN input pins to the output of the corresponding VCC\_MAIN power supply is made and the peak current measured. Similarly the contact inrush current of the VCC\_AUX lines was measured by making a direct contact of VCC\_AUX pins to the output of the corresponding VCC\_AUX power supply.

#### 2.4.2.3 Power Down Mode (Minimum DC Power Consumption)

In power down mode the module is placed in a low power consumption state under control of the host application. In this mode, the unit consumes approximately 1 uA of current as measured from the VCC\_MAIN supply input and 1 uA of current as measured from the VCC\_AUX supply input. To activate this mode, the Module\_PWR\_EN\_B signal on pin 12 of the system connector is pulled to a logic level 1, which puts the module into the low power state. The module will stay in the low power state until the Module\_PWR\_EN\_B signal is driven low by an external open collector transistor in the application circuitry. Turning the external open collector transistor off will cause the Module\_PWR\_EN\_B signal to float high and turn the module off. The Module\_PWR\_EN\_B line is tied to VCC\_MAIN through a  $220k\Omega$  pull-up resistor so the sink current in the external open collector transistor is minimal.

#### 2.4.3 VREF Signal Details

The following table defines the current sourcing capabilities and behavior of the VREF signal.

| Parameter                | Min  | Typical | Max  | Units |

|--------------------------|------|---------|------|-------|

| Supply Voltage Reference | 2.45 | 2.9     | 3.1  | V     |

| Output Current           |      |         | 1000 | μΑ    |

| Application Load         | 10   | 100     |      | ΚΩ    |

| Rise Time                |      |         | 3300 | μs    |

| Fall Time                |      |         | 0.8  | ms    |

**Table 9: VREF Supply Details**

## 2.5 Real Time Clock (RTC) Circuit

The purpose of this section is to detail the design of incorporating the Real Time Clock feature into the CM52.

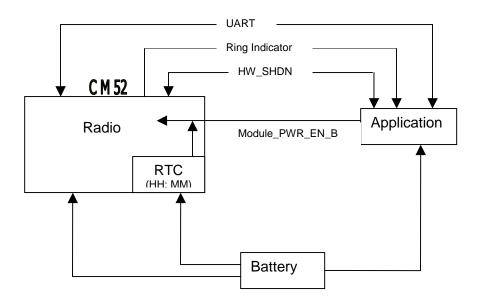

Figure 7: RTC Functional Block Diagram

#### 2.6 Audio Interface

The audio-related signals are: the analog audio signals

- ATMS (Audio to Mobile Station),

- **AFMS** (Audio from Mobile Station),

- PCM (Pulse Code Modulation) signals (PCMULD, PCMDLD, PCMCLK, and PCMSYNC).

| Pin | Signal  | Description                        |

|-----|---------|------------------------------------|

| 7   | AFMS    | Audio Output From Module.          |

| 10  | ATMS    | Audio Input to Module.             |

| 9   | AGND    | Analog Reference                   |

| 17  | PCMCLK  | PCM Clock Output from module.      |

| 18  | PCMSYNC | PCM Frame Sync Output from module. |

| 19  | PCMULD  | PCM Voice Input to module          |

| 20  | PCMDLD  | PCM Voice Output from module.      |

**Table 10: CM52 Audio Signals**

PA7

### 2.6.1 Digital Audio

The CM52 provides digital audio capability over the system connector. The digital audio signals enable the connection of a digital audio source. The receiver is bypassing the analog audio processing functions performed within the module. The digital audio interface includes the following PCM signals:

| Pin | CM52    | Description                   |

|-----|---------|-------------------------------|

| 17  | PCMCLK  | PCM Clock Output from module. |

| 18  | PCMSYNC | PCM Frame Sync from module    |

| 19  | PCMULD  | PCM Voice Input to module.    |

| 20  | PCMDLD  | PCM Voice Output from module. |

**Table 11: CM52 Digital Audio Signals**

Already defined CMOS output/input electrical characteristics apply (see Section 2.3.3).

The PCM format (for **PCMULD** and **PCMDLD**) follows a linear PCM data format with 13-bit data embedded in a 16-bit word. The data bits in **PCMULD** (input) and **PCMDLD** (output) are aligned so that the MSB in each word occurs on the same clock edge. See timing diagram in 2.6.1.2.

#### 2.6.1.1 Data Format

The CM-52 module implements a 13-bit PCM with the 13-bit data embedded in a 16-bit word as follows.

Each PCM word shall contain 16-bits D15 – D00. D15 – D03 is the 2's-complement value of the 13-bit PCM, with D15 as the sign bit. D15 is the MSB while D03 is the LSB. Note that the MSB is sent in first place. Ensure that the read data from PCMDLD is right shifted three times and sign extended before being used

|     | 13-bit linear |    |    |    |    |   |   |   |   |   |   |     |   |   |   |

|-----|---------------|----|----|----|----|---|---|---|---|---|---|-----|---|---|---|

| 15  | 14            | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0 |

| MSB |               |    |    |    |    |   |   |   |   |   |   | LSB | Х | Х | Х |

| Bit        |   | Contents                          |

|------------|---|-----------------------------------|

| D15<br>D03 | - | Two complement of the 13-bit PCM. |

| D02<br>D00 | - | Bits are undefined.               |

### 2.6.1.2 Timing

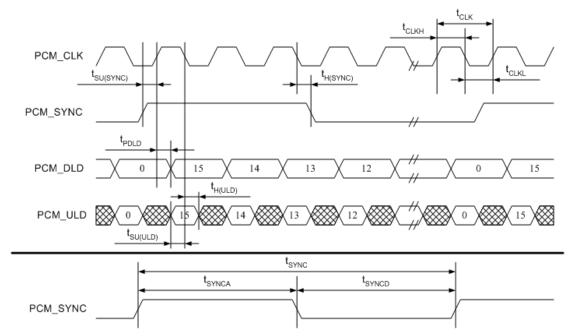

Timing shall be according to the following diagram (see **Figure 8: PCM Timing Diagram**). The signals in the diagram shall be interpreted according to the following relation.

Figure 8: PCM Timing Diagram

The meaning and value of the timing parameters are described in **Table 12**.

| Name                 | Description                                             | Min  | Typical | Max | Unit |

|----------------------|---------------------------------------------------------|------|---------|-----|------|

| 1                    | PCM_SYNC cycle time.                                    |      | 125     |     | μs   |

| t <sub>SYNC</sub>    | PCM_SYNC frequency                                      |      | 8.0     |     | kHz  |

| t <sub>SYNCA</sub>   | PCM_SYNC asserted time.                                 | 62.4 | 62.5    |     | μs   |

| t <sub>SYNCD</sub>   | PCM_SYNC de-asserted time.                              | 62.4 | 62.5    |     | μs   |

| t <sub>SU(SYN</sub>  | PCM_SYNC setup time to PCM_CLK rising.                  | 1.95 |         |     | μs   |

| t <sub>H(SYNC)</sub> | PCM_SYNC hold time after PCM_CLK falling.               | 1.95 |         |     | μs   |

|                      | PCM_CLK cycle time.                                     |      | 7.8     |     | μs   |

| t <sub>CLK</sub>     | PCM_CLK frequency                                       |      | 128     |     | kHz  |

| t <sub>CLKH</sub>    | PCM_CLK high time.                                      | 3.8  | 3.9     |     | μs   |

| t <sub>CLKL</sub>    | PCM_CLK low time.                                       | 3.8  | 3.9     |     | μs   |

| t <sub>PDLD</sub>    | Propagation delay from PCM_CLK rising to PCM_DLD valid. |      |         | 50  | ns   |