# eUniStone

BlueMoon<sup>™</sup> Universal Platform Embedded

PBA 31309 Version 1.x

**Intel Public**

# **User's Manual**

Hardware Description Revision 1.2, 1-Feb-2013

Information in this document related to the Intel product or, if any, related to its use is provided in connection with Intel products. no license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. except as provided in agreements concluded individually or Intel's terms and conditions of sale for such products, Intel assumes no liability whatsoever and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Unless otherwise agreed in writing by Intel, the Intel products are not designed nor intended for any application in which the failure of the Intel product could create a situation where personal injury or death may occur.

Unless otherwise agreed upon, Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Unless otherwise agreed, the information here is subject to change without notice. Do not finalize a design with this information.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/#/en\_US\_01.

Any software source code reprinted in this document is furnished under a software license and may only be used or copied in accordance with the terms of that license.

This document may contain information on products in the design phase of development.

Intel product numbers are not a measure of performance. Product numbers differentiate features within each product family, not across different product families.

Code Names are only for use by Intel to identify products, platforms, programs, services, etc. ("products") in development by Intel that have not been made commercially available to the public, i.e., announced, launched or shipped. They are never to be used as "commercial" names for products. Also, they are not intended to function as trademarks.

SMARTI, SMARTI & Device, BlueMoon, Comneon, Comneon & Device, M-GOLD, S-GOLD, E-GOLD, A-GOLD, X-GOLD, XMM, X-PMU, XPOSYS are trademarks of Intel Corporation and related companies.

Copyright © 2013, Intel Corporation. All rights reserved.

\*Other names and brands may be claimed as the property of others.

| Revision History                                              |  |  |  |  |  |  |

|---------------------------------------------------------------|--|--|--|--|--|--|

| Page or Item Subjects (major changes since previous revision) |  |  |  |  |  |  |

| Feb-2013                                                      |  |  |  |  |  |  |

|                                                               |  |  |  |  |  |  |

|                                                               |  |  |  |  |  |  |

|                                                               |  |  |  |  |  |  |

| , <yyyy-mm-dd></yyyy-mm-dd>                                   |  |  |  |  |  |  |

|                                                               |  |  |  |  |  |  |

| •                                                             |  |  |  |  |  |  |

## Contents

| 1.0 | Gene                                                   | al Device Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 1.1<br>1.2<br>1.3<br>1.4<br>1.5                        | Features8Block Diagram9Pin Configuration LGA10Pin Description11System Integration13                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 1.6                                                    | SW Patch in EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.0 | Basic                                                  | Operating Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     | 2.1<br>2.2<br>2.3                                      | Power Supply15Clocking.15Low Power Modes.152.3.1Low Power Mode152.3.2Complete Power Down15                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |                                                        | 2.3.3 ON/OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.0 |                                                        | tone Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 3.1                                                    | UART Interface       16         3.1.1       UART         3.1.1.1       Baud Rates         3.1.1.2       Detailed UART Behavior         17       3.1.1.3         UARTCTS Response Time       18                                                                                                                                                                                                                                                                                                                        |

|     | 3.2                                                    | Low Power Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.0 | Gene                                                   | al Device Capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | 4.1<br>4.2                                             | RF Test Application19Firmware ROM Patching194.2.1Patch Support19                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.0 | Bluet                                                  | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.0 | 5.1<br>5.2                                             | both Capabilities20Supported Features20eUniStone Bluetooth Features205.2.1Secure Simple Paining205.2.2Role Switch205.2.3Sniff Mode215.2.4Sniff Subrating215.2.5Enhanced Power Control215.2.6Encryption Pause and Resume21                                                                                                                                                                                                                                                                                             |

| 5.0 | 5.1<br>5.2<br>Elect                                    | Supported Features20eUniStone Bluetooth Features205.2.1 Secure Simple Paining205.2.2 Role Switch205.2.3 Sniff Mode215.2.4 Sniff Subrating215.2.5 Enhanced Power Control215.2.6 Encryption Pause and Resume21 <b>ical Characteristics</b> 22                                                                                                                                                                                                                                                                           |

|     | 5.1<br>5.2                                             | Supported Features20eUniStone Bluetooth Features205.2.1 Secure Simple Paining205.2.2 Role Switch205.2.3 Sniff Mode215.2.4 Sniff Subrating215.2.5 Enhanced Power Control215.2.6 Encryption Pause and Resume21 <b>ical Characteristics</b> 22Operating Conditions22DC Characteristics236.3.1 Pad Driver and Input Stages236.3.2 Pull-ups and Pull-downs256.3.3 Protection Circuits25                                                                                                                                    |

|     | 5.1<br>5.2<br>Elect<br>6.1<br>6.2                      | Supported Features20eUniStone Bluetooth Features205.2.1 Secure Simple Paining205.2.2 Role Switch205.2.3 Sniff Mode215.2.4 Sniff Subrating215.2.5 Enhanced Power Control215.2.6 Encryption Pause and Resume21 <b>ical Characteristics</b> 22Absolute Maximum Ratings22DC Characteristics236.3.1 Pad Driver and Input Stages236.3.2 Pull-ups and Pull-downs25                                                                                                                                                           |

|     | 5.1<br>5.2<br><b>Elect</b><br>6.1<br>6.2<br>6.3<br>6.4 | Supported Features20eUniStone Bluetooth Features205.2.1Secure Simple Paining205.2.2Role Switch205.2.3Sniff Mode215.2.4Sniff Subrating215.2.5Enhanced Power Control215.2.6Encryption Pause and Resume215.2.6Encryption Pause and Resume21 <b>ical Characteristics</b> 22Absolute Maximum Ratings22Operating Conditions22DC Characteristics236.3.1Pad Driver and Input Stages236.3.2Pull-ups and Pull-downs256.3.3Protection Circuits256.3.4System Power Consumption26RF Part266.4.1Characteristics RF Part26           |

| 6.0 | 5.1<br>5.2<br><b>Elect</b><br>6.1<br>6.2<br>6.3<br>6.4 | Supported Features20eUniStone Bluetooth Features205.2.1 Secure Simple Paining205.2.2 Role Switch205.2.3 Sniff Mode215.2.4 Sniff Subrating215.2.5 Enhanced Power Control215.2.6 Encryption Pause and Resume21ical Characteristics22Absolute Maximum Ratings22Operating Conditions22DC Characteristics236.3.1 Pad Driver and Input Stages236.3.2 Pull-ups and Pull-downs256.3.3 Protection Circuits256.3.4 System Power Consumption26RF Part266.4.1 Characteristics RF Part266.4.1.1 Bluetooth Related Specifications26 |

|     | 8.1   | Reference Design                               |

|-----|-------|------------------------------------------------|

|     | 8.2   | FCC Class B Digital Devices Regulatory Notice  |

|     | 8.3   | FCC Wireless Notice                            |

|     | 8.4   | FCC Interference Statement                     |

|     | 8.5   | FCC Identifier                                 |

|     | 8.6   | European R&TTE Declaration of Conformity       |

|     | 8.7   | Bluetooth Qualified Design ID                  |

|     | 8.8   | Industry Canada Certification                  |

|     | 8.9   | Label Design of the Host Product               |

|     | 8.10  | Regulatory Test House                          |

| 9.0 | Accer | nbly Guidelines                                |

| 510 | 9.1   | General Description of the Module              |

|     | 9.2   | Printed Circuit Board Design                   |

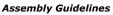

|     | 9.3   | Solder Paste Printing                          |

|     | 9.4   | Assembly                                       |

|     | 5.4   | 9.4.1 Component Placement                      |

|     |       | 9.4.2 Pin Mark                                 |

|     |       | 9.4.3 Package                                  |

|     | 9.5   | Soldering Profile                              |

|     | 9.6   | Rework                                         |

|     |       | 9.6.1 Removal Procedure                        |

|     |       | 9.6.2 Replacement Procedure                    |

|     |       | 9.6.2.1 Alternative 1: Dispensing Solder       |

|     |       | 9.6.2.2 Alternative 2: Printing Solder         |

|     | 9.7   | Inspection                                     |

|     | 9.8   | Component Salvage 44                           |

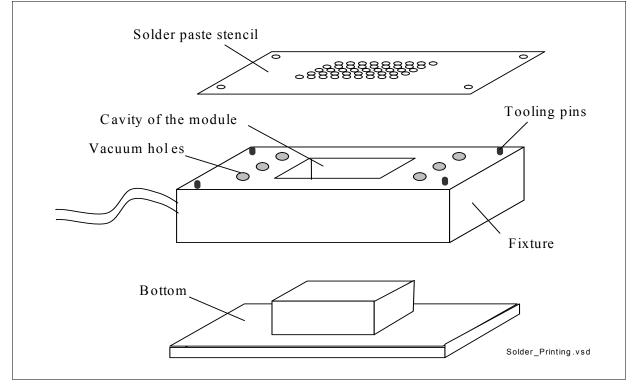

|     | 9.9   | Voids in the Solder Joints 44                  |

|     |       | 9.9.1 Expected Void Content and Reliability 44 |

|     |       | 9.9.2 Parameters with an Impact on Voiding 45  |

## **Figures**

| 1  | Simplified Block Diagram of eUniStone                   | 9    |

|----|---------------------------------------------------------|------|

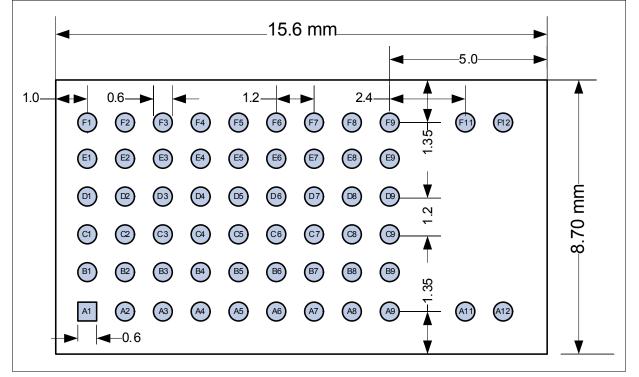

| 2  | Pin Configuration for eUniStone in Top View (footprint) | . 10 |

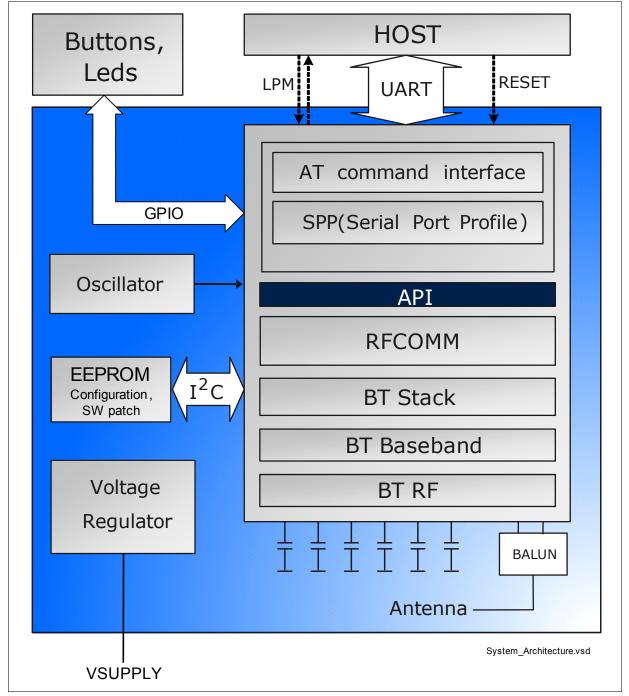

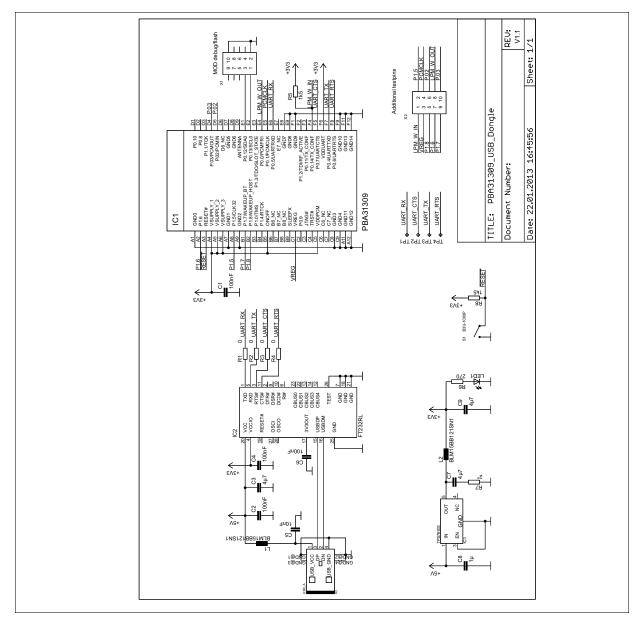

| 3  | System Architecture Example with eUniStone              |      |

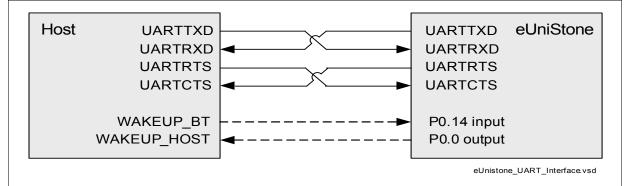

| 4  | UART Interface                                          | . 16 |

| 5  | UARTCTS Response Time                                   | . 18 |

| 6  | Package Marking                                         |      |

| 7  | Production Package                                      | . 30 |

| 8  | Top View and Bottom View                                |      |

| 9  | Reference Design Schematics                             | . 31 |

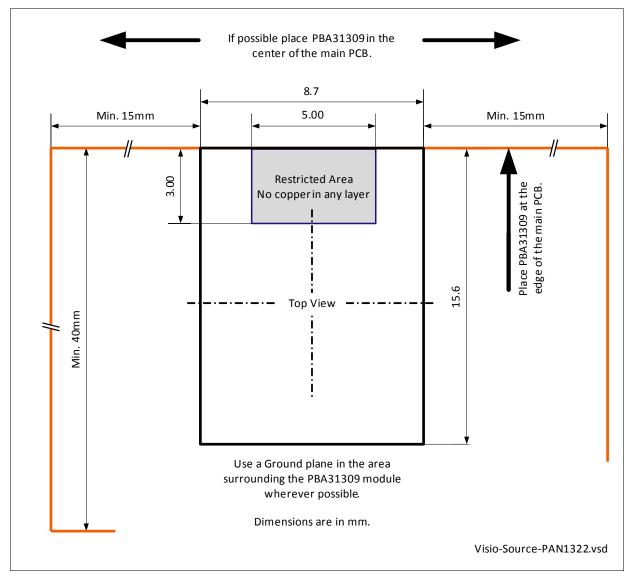

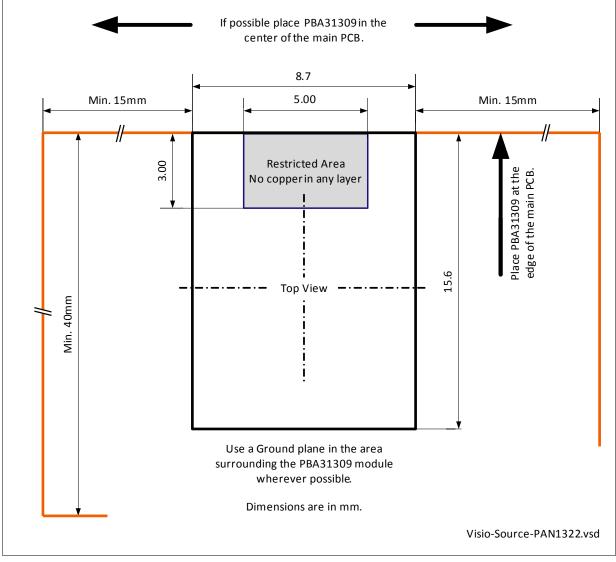

| 10 | Cutout Drawing                                          | . 33 |

| 11 | Equipment Label                                         | . 34 |

| 12 | Declaration of Conformity                               | . 35 |

| 13 | Pad Layout on the Module (top view)                     |      |

| 14 | Cutout Drawing                                          | . 38 |

| 15 | Pin Marking                                             | . 39 |

| 16 | Tape on Reel                                            |      |

| 17 | Eutectic Lead-Solder Profile                            | . 41 |

| 18 | Eutectic Leadfree-Solder Profile                        |      |

| 19 | Solder Printing                                         |      |

| 20 | X-ray Picture Showing Voids Conforming to IPC-A-610D    | . 44 |

## Tables

| 1  | Pin Description                                 | 11 |

|----|-------------------------------------------------|----|

| 2  | UART Baud Rates                                 | 17 |

| 3  | Default (non-inverted) behavior of UART signals | 17 |

| 4  | Absolute Maximum Ratings                        | 22 |

| 5  | Operating Conditions                            | 22 |

| 6  | Internal1 (1.5 V) Supplied Pins                 | 23 |

| 7  | Internal2 (2.5 V) Supplied Pins                 | 23 |

| 8  | VDDUART Supplied Pins                           | 24 |

| 9  | VDD1 Supplied Pins                              | 24 |

| 10 | ONOFF PIN                                       | 24 |

| 11 | Pull-up and Pull-down Currents                  | 25 |

| 12 | Max. Load at the Different Supply Voltages      | 26 |

| 13 | BDR - Transmitter Part                          | 26 |

| 14 | BDR -Receiver Part                              | 27 |

|    | EDR - Transmitter Part                          |    |

| 16 | EDR -Receiver Part                              | 28 |

|    |                                                 |    |

## **1.0 General Device Overview**

### **1.1** Features

#### General

- Complete Bluetooth 2.1 + EDR solution

- Implements a single point-to-point data link to other SPP capable Bluetooth devices

- Ultra low power design in 0.13  $\mu m$  CMOS

- Temperature range from -40°C to +85°C

- Integrates ARM7TDMI, RAM and patchable ROM

- On-module voltage regulators. External supply 2.9 4.1 V

- On-module EEPROM with configuration data

- On-module tuned reference clock

- Module can enter low power mode in idle state and during sniff intervals

#### Interfaces

- AT command interface over UART with HW flow control

- Default UART baudrate 115200 bit/s

- Module configuration reprogrammable for 9600 bit/s up to 3.25 Mbit/s UART baudrate

- JTAG for boundary scan in production test

#### RF

- Class 2 device up to +4 dBm

- Receiver sensitivity typ. -86 dBm

- Integrated antenna, balun and ISM band filter

- Integrated LNA with excellent blocking and intermodulation performance

- Digital demodulation for optimum sensitivity and co-/adjacent channel performance

#### Bluetooth

- Bluetooth V2.1 + EDR compliant

- Secure Simple Pairing

- Device A (initiating link) or Device B (accepting link) role supported

- Single point-to-point data link, role switch supported

- Packet data mode and stream data mode supported

- Sniff mode and Sniff Subrating is supported with above capabilities

- 5 trusted devices stored in EEPROM

- SW version available to configure specific RF certification tests

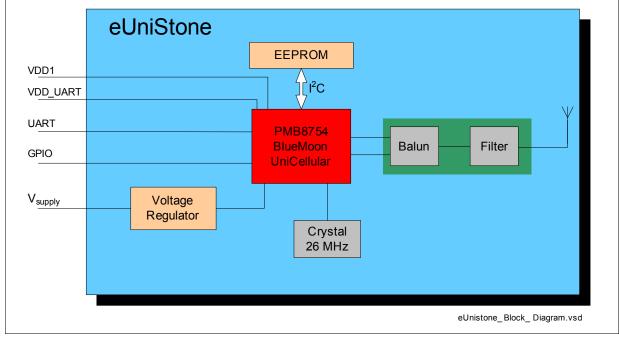

## 1.2 Block Diagram

Figure 1. Simplified Block Diagram of eUniStone

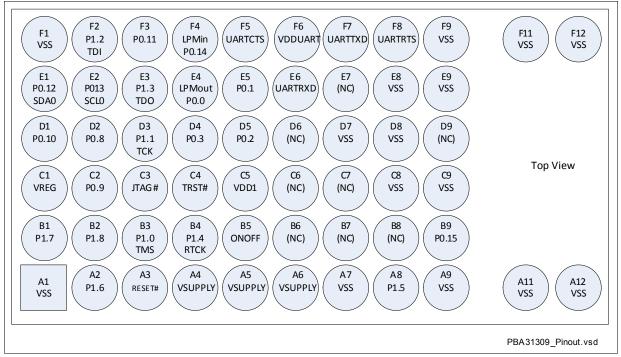

## **1.3 Pin Configuration LGA**

Figure 2. Pin Configuration for eUniStone in Top View (footprint)

General Device Overview

## **1.4 Pin Description**

The non-shaded cells indicate pins that will be fixed for the product lifetime. Shaded cells indicate that the pin might be removed/changed in future variants. Pins not listed below shall not be connected.

| Table            | e 1. Pin De       | escription        |                |                  |                  |                                              |

|------------------|-------------------|-------------------|----------------|------------------|------------------|----------------------------------------------|

| Pin<br>No.       | Symbol            | Input /<br>Output | Supply Voltage | During<br>Reset  | After<br>Reset   | Function                                     |

| A2               | P1.6              | I/O/OD            | Internal1      | Z                | Z                | Port 1.6                                     |

| A3               | RESET#            | AI                | Internal1      | Input            | Input            | Hardware Reset                               |

| A8               | P1.5              | I/O/OD            | Internal1      | Input            | Input            | Port 1.5                                     |

| B1               | P1.7              | I/O/OD            | Internal1      | PD/ Input        | PD/ Input        | Port 1.7                                     |

| B2               | P1.8              | I/O/OD            | Internal1      | PD               | PD               | Port 1.8                                     |

| B3               | P1.0 /<br>TMS     | I/O/OD            | Internal2      | PU <sup>1</sup>  | PU <sup>1.</sup> | Port 1.0 or<br>JTAG interface                |

| B4               | P1.4 /<br>RTCK    | I/O/OD            | Internal2      | Z                | Z                | Port 1.4 or<br>JTAG interface                |

| B5               | ONOFF             | I                 |                | -                | -                | Turns off module completely                  |

| B9               | P0.15             | I/O               | VDDUART        | PD               | Н                | Port 0.15                                    |

| C2               | P0.9              | I/O/OD            | Internal2      | Z                | Z                | Port 0.9                                     |

| C3               | JTAG#             | I                 | Internal2      | PU               | PU               | Mode selection Port 1:<br>0: JTAG<br>1: Port |

| C4               | TRST#             | I                 | Internal2      | PD               | PD               | JTAG interface                               |

| D1               | P0.10             | I/O/OD            | Internal2      | Z                | Z                | Port 0.10                                    |

| D2               | P0.8              | I/O/OD            | Internal2      | PD               | PD               | Port 0.8                                     |

| D3               | P1.1 /<br>TCK     | I/O/OD            | Internal2      | PU <sup>1.</sup> | PU <sup>1.</sup> | Port 1.1 or<br>JTAG interface                |

| D4               | P0.3 I/O/OD VDD1  |                   | VDD1           | Conf.<br>PD def. | Conf.<br>PD def. | Port 0.3                                     |

| D5               | P0.2              | I/O/OD            | VDD1           | Z                | Z                | Port 0.2                                     |

| E1               | P0.12 / SDA0      | I/O/OD            | Internal2      | PU               | PU               | I2C data signal                              |

| E2               | P0.13 / SCL0      | I/O/OD            | Internal2      | PU               | PU               | I2C clock signal                             |

| E3               | P1.3 /<br>TDO     | I/O/OD            | Internal2      | Z                | Z                | Port 1.3 or<br>JTAG interface                |

| E4               | P0.0 LPMout       | I/O/OD            | VDD1           | PD               | PD               | Port 0.0<br>LPM wakeup output                |

| E5               | P0.1              | I/O/OD            | VDD1           | PD               | PD               | Port 0.1                                     |

| E6               | P0.5 /<br>UARTRXD | I/O/OD            | VDDUART        | Z                | Z                | Port 0.5 or<br>UART receive data             |

| F2               | P1.2 /<br>TDI     | I/O/OD            | Internal2      | PU <sup>1.</sup> | PU <sup>1.</sup> | Port 1.2 or<br>JTAG interface                |

| F3               | P0.11             | I/O/OD            | Internal2      | Z                | Z                | Port 0.11                                    |

| F4               | P0.14 LPMin       | I/O               | VDDUART        | Z                | Z                | Port 0.14<br>LPM wakup input                 |

| F5               | P0.7 /<br>UARTCTS | I/O/OD            | VDDUART        | Z                | Z                | Port 0.7 or<br>UART CTS flow control         |

| F7               | P0.4 /<br>UARTTXD | I/O/OD            | VDDUART        | PU               | PU               | Port 0.4 or<br>UART transmit data            |

| F8               | P0.6 /<br>UARTRTS | I/O/OD            | VDDUART        | PU               | PU               | Port 0.6 or<br>UART RTS flow control         |

| A4,<br>A5,<br>A6 | VSUPPLY           | SI                |                | -                | -                | Power supply                                 |

| C1               | VREG              | SO                |                | -                | -                | Regulated Power supply                       |

| F6               | VDDUART           | SI                |                | -                | -                | UART interface Power supply                  |

| C5               | VDD1              | SI                |                | -                | -                | Power supply                                 |

#### Table 1. Pin Description

#### General Device Overview

#### Table 1. Pin Description (Continued)

| Pin<br>No.                                                                                                      | Symbol | Input /<br>Output | Supply Voltage | During<br>Reset | After<br>Reset | Function      |

|-----------------------------------------------------------------------------------------------------------------|--------|-------------------|----------------|-----------------|----------------|---------------|

| A1,<br>A7,<br>A9,<br>A11,<br>A12,<br>C8,<br>C9,<br>D7,<br>D8,<br>E8,<br>F1,<br>F9,<br>F1,<br>F9,<br>F11,<br>F12 | VSS    |                   |                | -               | -              | Ground        |

| B6,<br>B7,<br>B8,<br>C6,<br>C7,<br>D6,<br>D9,<br>E7                                                             | NC     | -                 | -              | -               | -              | No connection |

1. Fixed pull-up/pull-down if JTAG interface is selected, not affected by any chip reset. If JTAG interface is not selected the port is tristate.

#### Descriptions of acronyms used in the pin list:

| Acronym | Description                          |

|---------|--------------------------------------|

| I       | Input                                |

| 0       | Output                               |

| OD      | Output with open drain capability    |

| Z       | Tristate                             |

| PU      | Pull-up                              |

| PD      | Pull-down                            |

| A       | Analog (e.g. AI means analog input)  |

| S       | Supply (e.g. SO means supply output) |

## 1.5 System Integration

eUniStone is optimized for a low bill of material (BOM) and a small PCB size. Figure 3 shows a typical application example.

#### General Device Overview

The UART interface is used for communication between the host and eUniStone. The lines UARTTXD and UARTRXD are used for commands, events and data. The lines UARTRTS and UARTCTS are used for hardware flow control.

Low power mode control of eUniStone and the host can be implemented in by using the pins P0.14 and P0.0. P0.14 is used by the host to allow eUniStone to enter low power mode and P0.0 is used by eUniStone to wake-up the host when attention is required. To save current in idle mode, the host could hardware reset the module using the RESET#.

Power is supplied to a single VSUPPLY input from which internal regulators can generate all required voltages. The UART and the GPIO's interfaces have separate supply voltages so that they can comply with host signaling.

#### **1.6 SW Patch in EEPROM**

Bugfixes for the SW in ROM are downloaded from the EEPROM. Intel may include new bugfixes in EEPROM during product lifetime..

## **2.0 Basic Operating Information**

### 2.1 **Power Supply**

eUniStone is supplied from a single supply voltage VSUPPLY. This supply voltage must always be present. The Bluetooth chip is supplied from an internally generated 2.5 V supply voltage. This voltage can be accessed from the VREG pin. This voltage shall not be used for supplying other components in the host system but can be used for referencing the host interfaces.

The GPIO's and the UART interface are supplied with dedicated, independent, reference levels via the VDD1 and VDDUART pins. All other digital I/O pins are supplied internally by either 2.5 V (Internal2) or 1.5 V (Internal1). Section 1.4 provides a mapping between pins and supply voltages.

The I/O power domains (VDD1 and VDDUART) are completely separated from the other power domains and can stay present also in low power modes.

#### 2.2 Clocking

eUniStone contains a crystal from which the internal 26 MHz system clock is generated. Also, the low power mode clock of 32.768 kHz is generated internally, which means that no external clock is needed.

### 2.3 Low Power Modes

To minimize current consumption, eUniStone automatically switches between different low power modes. The major modes are described below.

#### 2.3.1 Low Power Mode

In Low Power Mode (LPM) most parts of eUniStone are powered down. This is done automatically in idle mode or if the link is in Sniff mode and the host allows LPM with the pin P0.14.

#### 2.3.2 Complete Power Down

If Bluetooth functionality is not needed at all, VSUPPLY should be grounded to minimize power consumption. In this state there is no activity in eUniStone and the Bluetooth state (native clock, etc.) is not updated.

### 2.3.3 ON/OFF

eUniStone provides an alternative way to power down using the ONOFF logic input. When the ONOFF is low, the internal regulator on the module is turned OFF. The intention with the signal is to have the possibility to turn off the module without having to turn off the supply voltage. In the OFF state, the module will consume less than 1 mA excluding the interface currents that is mainly set by the external load. If this signal isn't used then it should be connected to VSUPPLY on the host PCB.

## 3.0 eUniStone Interfaces

### **3.1 UART Interface**

The UART interface is the main communication interface between the host and eUniStone. AT commands are described in detail in the AT Commands specification [1].

The interface consists of four UART signals and two LPM control signals as shown in Figure 4.

#### Figure 4. UART Interface

#### 3.1.1 UART

The lines UARTTXD and UARTRXD are used for commands, responses and data. The lines UARTRTS and UARTCTS are used for hardware flow control. A separate supply voltage, VDDUART, defines the UART reference levels to fit any system requirements.

#### 3.1.1.1 Baud Rates

The UART baud rate can be configured with the BD\_DATA parameter *UART\_Baudrate*. The module is programmed for a default baudrate of 115200 baud. Reprogramming of the EEPROM configuration is possible by AT commands at manufacturing time of the end product. The baudrate written to EEPROM will be used each time eUniStone starts or, HW or SW reset is done.

The host is also able to change the baudrate temporarily with an AT command. This baudrate is used by eUniStone until a HW or SW reset is done, when it will change back to the baudrate stored in the EEPROM.

#### Table 2 shows the UART baudrates supported.

#### Table 2.UART Baud Rates

| Standard Baud Rate | Module Baud Rate | Deviation in % |  |

|--------------------|------------------|----------------|--|

| 9600               | 9615             | 0.16           |  |

| 19200              | 19230            | 0.16           |  |

| 38400              | 38461            | 0.16           |  |

| 57600              | 57522            | -0.14          |  |

| 115200             | 115044           | -0.14          |  |

| 230400             | 230088           | -0.14          |  |

| 460800             | 464285           | 0.76           |  |

| 921600             | 928571           | 0.76           |  |

| 1843200            | 1857142          | 0.76           |  |

| 3250000            | 3250000          | 0              |  |

#### 3.1.1.2 Detailed UART Behavior

After reset the UART interface is configured with one start bit, eight data bits, no parity bit and one stop bit. The least significant bit is transmitted first.

The polarity of the UART signals can be changed with the BD\_DATA parameter <code>UART\_Invert</code>. The default (non-inverted) behavior is shown in Table 3

| Table 3. | <b>Default</b> ( | (non-inverted) | behavior of UART signals |

|----------|------------------|----------------|--------------------------|

|----------|------------------|----------------|--------------------------|

| Signal            | Level | Meaning                          |

|-------------------|-------|----------------------------------|

| UARTTXD / UARTRXD | 0     | Start bit, '0' bit in character. |

|                   | 1     | Idle level, stop bit             |

| UARTRTS / UARTCTS | 0     | Flow on                          |

|                   | 1     | Flow stopped                     |

eUniStone Interfaces

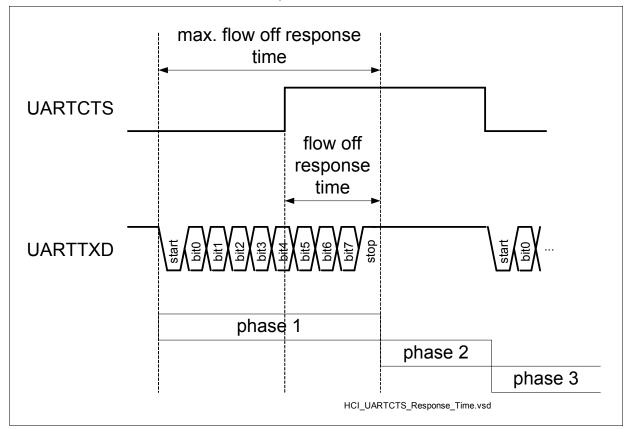

#### 3.1.1.3 UARTCTS Response Time

Figure 5 shows the UARTCTS response time. Assuming non-inverted UART signals, the data flow stops within the "flow off response time" after UARTCTS has been set to high. If UARTCTS goes high during the transmission of a byte (phase 1 in the figure) this byte will be completely transmitted. While UARTCTS is high, no data will be transmitted (phase 2). When UARTCTS goes low again, data transmission will continue (phase 3).

The maximum flow off response time is 10 UART bits (including start and stop bits). As an example, if the UART baud rate is 115200 Baud, the maximum flow off response time is  $10 \times 1/115200 \text{ s} = 87 \text{ µs}$ .

#### Figure 5. UARTCTS Response Time

#### 3.2 Low Power Control

Pin P0.14 and P0.0 are optional, but strongly recommended to be used. P0.14 is used to allow eUniStone to enter Low Power Mode (LPM). P0.0 is used by eUniStone when in LPM to wake up the host.

## 4.0 General Device Capabilities

This chapter describes features available in the eUniStone (PBA 31309).

Actual feature set and how to access the features can be found in the AT Command document [1]. Release specific performance characteristics, data throughput and current consumption are listed in the SW Release Notes [2].

### 4.1 **RF Test Application**

The eUniStone module can be programmed over UART with a specific application for RF test purposes, e.g. TX continuous or TX burst mode. This test application is controlled over the UART through Intel specific HCI commands. The commands supported by this test application are described in the document "T8753-2-Intel\_Specific\_HCI\_Commands-7600.pdf".

### 4.2 Firmware ROM Patching

In any chip with complex firmware in ROM it is wise to support patching. The risk of project delay is significantly reduced when problems can be solved without hardware changes. Enhancements, adaptations and bug fixes can be handled very late during design-in, even after the chip has been soldered in the final product.

The well-proven patch concept used in BlueMoon UniCellular is described below.

#### 4.2.1 Patch Support

The Bluetooth chip contains dedicated hardware that makes it possible to apply patches to the code and data in the firmware ROM. The hardware is capable of replacing up to 32 blocks of 16 bytes each with new content. This area can be filled with any combination of code and data. The firmware patch is stored in EEPROM and automatically loaded after startup. This provides a flexible bugfix solution for the software in ROM.

## 5.0 Bluetooth Capabilities

### 5.1 Supported Features

- Bluetooth V2.1 + EDR compliant

- Enhanced Data Rate 2 and 3 Mbit/s symbol rate on the air

- Secure Simple Pairing

- Device A (initiating link) or Device B (accepting link) role supported

- Single point-to-point data link, role switch supported

- Packet data mode and stream data mode supported

- Link in sniff mode supported. Device enters Low Power Mode in sniff intervals if permitted by the host.

- Sniff Subrating

- 5 trusted devices stored in EEPROM

- Connection to a Bluetooth Tester

## 5.2 eUniStone Bluetooth Features

#### 5.2.1 Secure Simple Paining

The device implements Secure Simple Pairing with the following association models according to BT2.1 core specification:

- Numeric Comparisoon

- Just Works

- Passkey Entry

Also pairing with legacy (BT2.0 and older) devices is supported.

#### 5.2.2 Role Switch

The initiating device (devA) starts as Bluetooth master of the link, the accepting device starts as Bluetooth slave of the link. The remote device can request a role change to accomodate with other Bluetooth links. If that happens, the module will send an event to the host. Also if the eUniStone start as slave, (Device B), the other device can change it's own role making eUniStone master. The host controlling eUniStone will be notified with the same event.

eUniStone PBA 31309

Bluetooth Capabilities

#### 5.2.3 Sniff Mode

The local host or the remote device can request sniff mode for the link. During sniff mode, the devices synchronize on sniff instants only. The module will enter low power mode in the sniff intervals, if allowed by the host LPM control signals. Data packets can be exchanged at the sniff instants only, so the data rate is reduced in sniff mode. The module will wake up the host when data is received or other responses need to be transmitted.

#### 5.2.4 Sniff Subrating

The local host or the remote device can request Sniff Subrating for the link. When in sniff mode, the device will automatically switch between Sniff Mode and Sniff Subrating Mode making it possible to stay longer in Low Power Mode when there is no data transmitted or received.

#### 5.2.5 Enhanced Power Control

eUniStone support Enhanced Power Control according to Bluetooth specification 3.0. The Enhanced Power Control is handled automatically to make different modulations modes transmit on optimal levels.

#### 5.2.6 Encryption Pause and Resume

Encryption Pause Resume is supported making it possible to change connection link key on an encrypted link, pause the encryption and resume it with the new link key. This is handled automatically by eUniStone to make the link more secure.

## 6.0 Electrical Characteristics

## 6.1 Absolute Maximum Ratings

| Parameter              | Symbol | Values |      | Unit        | Note / Test Condition |                                        |

|------------------------|--------|--------|------|-------------|-----------------------|----------------------------------------|

|                        |        | Min.   | Тур. | Max.        |                       |                                        |

| Storage temperature    |        | -40    | -    | 125         | °C                    | -                                      |

| VSUPPLY supply voltage |        | -0.3   | -    | 6.0         | V                     | -                                      |

| VDDUART supply voltage |        | -0.9   | -    | 4.0         | V                     | -                                      |

| VDD1 supply voltage    |        | -0.9   | -    | 4.0         | V                     | -                                      |

| VREG                   |        | -0.3   | -    | 4.0         | V                     | VSUPPLY > 4 V                          |

| VREG                   |        | -0.3   | -    | VSUPPLY     | V                     | VSUPPLY < 4 V                          |

| ONOFF                  |        | -0.3   | -    | VSUPPLY+0.3 | V                     |                                        |

| Input voltage range    |        | -0.9   | -    | 4.0         | V                     | -                                      |

| Output voltage range   |        | -0.9   | -    | 4.0         | V                     | -9                                     |

| ESD                    |        | -      | -    | 1.0         | kV                    | According to MIL-STD883D method 3015.7 |

#### Table 4. Absolute Maximum Ratings

*Note:* Stresses above those listed here are likely to cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Maximum ratings are absolute ratings; exceeding only one of these values may cause

Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit. Maximum ratings are not operating conditions.

## 6.2 **Operating Conditions**

| Table 5. Operating conditions |        |        |      |           |      |                       |  |  |  |

|-------------------------------|--------|--------|------|-----------|------|-----------------------|--|--|--|

| Parameter                     | Symbol | Values |      |           | Unit | Note / Test Condition |  |  |  |

|                               |        | Min.   | Тур. | Max.      |      |                       |  |  |  |

| Operating temperature         |        | -40    | -    | 85        | °C   | -                     |  |  |  |

| Main supply voltage (Vsupply) |        | 2.9    | -    | $4.1^{1}$ | V    | -                     |  |  |  |

| VDDUART                       |        | 1.35   | -    | 3.6       | V    | -                     |  |  |  |

| VDD1                          |        | 1.35   | -    | 3.6       | V    | -                     |  |  |  |

#### Table 5.Operating Conditions

1. At ambient temperatures above 65°C the maximum allowed power dissipation in the module is limited to 200 mW

## 6.3 DC Characteristics

### 6.3.1 Pad Driver and Input Stages

For more information, see Chapter 1.4.

#### Table 6.Internal1 (1.5 V) Supplied Pins

| Parameter                    | Symbol |      | Values | ;    | Unit | Note / Test Condition             |

|------------------------------|--------|------|--------|------|------|-----------------------------------|

|                              |        | Min. | Тур.   | Max. |      |                                   |

| Input low voltage            |        | -0.3 | -      | 0.27 | V    | -                                 |

| Input high voltage           |        | 1.15 | -      | 3.6  | V    | -                                 |

| Output low voltage           |        | -    | -      | 0.25 | V    | IOL = 1 mA                        |

| Output high voltage          |        | 1.1  | -      | -    | V    | IOH = -1 mA                       |

| Continuous Load <sup>1</sup> |        | -    | -      | 1    | mA   | -                                 |

| Pin Capacitance              |        | -    | -      | 10   | pF   | -                                 |

| Magnitude Pin Leakage        |        | -    | 0.01   | 1    | μA   | Input and output drivers disabled |

1. The total continuous load for all Internal1 supplied pins shall not exceed 2 mA at the same time

#### Table 7.Internal2 (2.5 V) Supplied Pins

| Parameter                    | Symbol |      | Values | 5    | Unit | Note / Test Condition             |

|------------------------------|--------|------|--------|------|------|-----------------------------------|

|                              |        | Min. | Тур.   | Max. |      |                                   |

| Input low voltage            |        | -0.3 | -      | 0.45 | V    | -                                 |

| Input high voltage           |        | 1.93 | -      | 2.8  | V    | P0.10                             |

| Input high voltage           |        | 1.93 | -      | 3.6  | V    | Other pins                        |

| Output low voltage           |        | -    | -      | 0.25 | V    | IOL = 5 mA                        |

| Output low voltage           |        | -    | -      | 0.15 | V    | IOL = 2 mA                        |

| Output high voltage          |        | 2.0  | -      | -    | V    | IOH = -5 mA                       |

| Output high voltage          |        | 2.1  | -      | -    | V    | IOH = -2 mA                       |

| Continuous Load <sup>1</sup> |        | -    | -      | 5    | mA   | -                                 |

| Pin Capacitance              |        | -    | -      | 10   | pF   | -                                 |

| Magnitude Pin Leakage        |        | -    | 0.01   | 1    | μA   | Input and output drivers disabled |

1. The total continuous load for all Internal2 supplied pins shall not exceed 35 mA at the same time

| Parameter                    | Symbol |                  | Value | s           | Unit | Note / Test Condition             |  |

|------------------------------|--------|------------------|-------|-------------|------|-----------------------------------|--|

|                              |        | Min.             | Тур.  | Max.        |      |                                   |  |

| Input low voltage            |        | -0.3             | -     | 0.2*VDDUART | V    | -                                 |  |

| Input high voltage           |        | 0.7*VDDUART      | -     | VDDUART+0.3 | V    | P0.5/UARTRXD                      |  |

| Input high voltage           |        | 0.7*VDDUART      | -     | 3.6         | V    | Other pins                        |  |

| Output low voltage           |        | -                | -     | 0.25        | V    | IOL = 5 mA<br>VDDUART = 2.5 V     |  |

| Output low voltage           |        | -                | -     | 0.15        | V    | IOL = 2 mA<br>VDDUART = 2.5 V     |  |

| Output high voltage          |        | VDDUART<br>-0.25 | -     | -           | V    | IOH = -5 mA<br>VDDUART = 2.5 V    |  |

| Output high voltage          |        | VDDUART<br>-0.15 | -     | -           | V    | IOH = -2 mA<br>VDDUART = 2.5 V    |  |

| Continuous Load <sup>1</sup> |        | -                | -     | 5           | mA   | -                                 |  |

| Pin Capacitance              |        | -                | -     | 10          | pF   | -                                 |  |

| Magnitude Pin Leakage        |        | -                | 0.01  | 1           | μΑ   | Input and output drivers disabled |  |

#### Table 8. VDDUART Supplied Pins

1. The total continuous load for all VDDUART supplied pins shall not exceed 35 mA at the same time

#### Table 9. VDD1 Supplied Pins

| Parameter                    | Symbol |               | Value | s        | Unit | Note / Test Condition             |

|------------------------------|--------|---------------|-------|----------|------|-----------------------------------|

|                              |        | Min.          | Тур.  | Max.     |      |                                   |

| Input low voltage            |        | -0.3          | -     | 0.2*VDD1 | V    | -                                 |

| Input high voltage           |        | 0.7*VDD1      | -     | 3.6      | V    | -                                 |

| Output low voltage           |        | -             | -     | 0.25     | V    | IOL = 5 mA<br>VDD1 = 2.5 V        |

| Output low voltage           |        | -             | -     | 0.15     | V    | IOL = 2 mA<br>VDD1 = 2.5 V        |

| Output high voltage          |        | VDD1<br>-0.25 | -     | -        | V    | IOH = -5 mA<br>VDD1 = 2.5 V       |

| Output high voltage          |        | VDD1<br>-0.15 | -     | -        | V    | IOH = -2 mA<br>VDD1 = 2.5 V       |

| Continuous Load <sup>1</sup> |        | -             | -     | 5        | mA   | -                                 |

| Pin Capacitance              |        | -             | -     | 10       | pF   | -                                 |

| Magnitude Pin Leakage        |        | -             | 0.01  | 1        | μA   | Input and output drivers disabled |

1. The total continuous load for all VDD1 supplied pins shall not exceed 35 mA at the same time

#### Table 10. ONOFF PIN

| Parameter          | Symbol | Values |      |         |    | Note / Test Condition |

|--------------------|--------|--------|------|---------|----|-----------------------|

|                    |        | Min.   | Тур. | Max.    |    |                       |

| Input low voltage  |        | -      | -    | 0.7     | V  | -                     |

| Input high voltage |        | 1.7    | -    | VSUPPLY | V  | -                     |

| Input current      |        | -1     | 0.01 | 1       | μA | ONOFF = 0 V           |

## 6.3.2 Pull-ups and Pull-downs

| Pin                                                                              | Pull U | p Currei | nt   | Pull Do | own Curre | nt   | Unit | Conditions                                                                                                                                    |

|----------------------------------------------------------------------------------|--------|----------|------|---------|-----------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                  | Min.   | Тур.     | Max. | Min.    | Тур.      | Max. |      |                                                                                                                                               |

| P0.12<br>P0.13                                                                   | 260    | 740      | 1300 | N/A     | N/A       | N/A  | μΑ   | Pull-up current measured<br>with pin voltage = $0 V$                                                                                          |

| P0.0<br>P0.1<br>P0.2<br>P0.3                                                     | 22     | 130      | 350  | 23      | 150       | 380  | μA   | Pull-down current measured<br>with pin voltage =<br>supply voltage                                                                            |

| P0.4<br>P0.5<br>P0.6<br>P0.7<br>P0.10<br>P0.8<br>P0.9<br>P0.11<br>P0.14<br>P0.15 | 4.2    | 24       | 68   | 3.0     | 20        | 55   | μA   | Min measured at 125°C with<br>supply = 1.35 V<br>Typ. measured at 27°C with<br>supply = 2.5V<br>Max measured at -40°C with<br>supply = 3.63 V |

| P1.0<br>P1.1<br>P1.2<br>P1.3<br>P1.4<br>P1.5<br>P1.6<br>P1.7<br>P1.8             | 1.1    | 6.0      | 17   | 0.75    | 5.0       | 14   | μA   |                                                                                                                                               |

#### Table 11. Pull-up and Pull-down Currents

## 6.3.3 **Protection Circuits**

All pins have an inverse protection diode against VSS. P0.10 has an inverse diode against Internal2. P0.5/UARTRXD has an inverse diode against VDDUART. All other pins have no diode against their supply.

### 6.3.4 System Power Consumption

#### Table 12.Max. Load at the Different Supply Voltages

| Parameter | Symbol | Values |      | Unit | Note / Test Condition |              |

|-----------|--------|--------|------|------|-----------------------|--------------|

|           |        | Min.   | Тур. | Max. |                       |              |

| Vsupply   |        | _      | -    | 100  | mA                    | Peak current |

*Note:* I/O currents are not included since they depend mainly on external loads. For more details see [2].

## 6.4 RF Part

#### 6.4.1 Characteristics RF Part

The characteristics involve the spread of values to be within the specific temperature range. Typical characteristics are the median of the production.

All values refers to Intel reference design.

#### 6.4.1.1 Bluetooth Related Specifications

#### Table 13.BDR - Transmitter Part

| Parameter                                             | Symbol |      | Value  | S      | Unit      | Note / Test Condition                                |  |

|-------------------------------------------------------|--------|------|--------|--------|-----------|------------------------------------------------------|--|

|                                                       |        | Min. | Тур.   | Max.   |           |                                                      |  |

| Output power (high gain)                              |        | 0.5  | 2.5    | 4.5    | dBm       | Default settings                                     |  |

| Output power (highest gain)                           |        | -    | 4.5    | -      | dBm       | Maximum settings                                     |  |

| Power control step size                               |        | 4    | 6      | 8      | dB        | -                                                    |  |

| Frequency range fL                                    |        | 2400 | 2401.3 | -      | MHz       | -                                                    |  |

| Frequency range fH                                    |        | -    | 2480.7 | 2483.5 | MHz       | -                                                    |  |

| 20 dB bandwidth                                       |        | -    | 0.930  | 1      | MHz       | -                                                    |  |

| 2nd adjacent channel power                            |        | -    | -40    | -20    | dBm       | -                                                    |  |

| 3rd adjacent channel power                            |        | -    | -60    | -40    | dBm       | -                                                    |  |

| >3rd adjacent channel power                           |        | -    | -64    | -40    | dBm       | Max. 2 of 3 exceptions @ 52 MHz offset might be used |  |

| Average modulation deviation for 00001111 sequence    |        | 140  | 156    | 175    | kHz       | -                                                    |  |

| Minimum modulation deviation for 01010101 sequence    |        | 115  | 145    | -      | kHz       | -                                                    |  |

| Ratio Deviation 01010101 /<br>Deviation 00001111      |        | 0.8  | 1      | -      |           | -                                                    |  |

| Initial carrier frequency tolerance<br> foffset       |        | -    | -      | 75     | kHz       | -                                                    |  |

| Carrier frequency drift<br>(one slot)  fdrift         |        | -    | 10     | 25     | kHz       | -                                                    |  |

| Carrier frequency drift<br>(three slots)  fdrift      |        | -    | 10     | 40     | kHz       | -                                                    |  |

| Carrier frequency drift<br>(five slots)  fdrift       |        | -    | 10     | 40     | kHz       | -                                                    |  |

| Carrier frequency driftrate<br>(one slot)  fdriftrate |        | -    | 5      | 20     | kHz/50 ms | -                                                    |  |

#### Electrical Characteristics

### Table 13. BDR - Transmitter Part (Continued)

| Parameter                                               | Symbol | Values |      | Unit | Note / Test Condition |   |

|---------------------------------------------------------|--------|--------|------|------|-----------------------|---|

|                                                         |        | Min.   | Тур. | Max. |                       |   |

| Carrier frequency driftrate (three slots)  fdriftrate   |        | -      | 5    | 20   | kHz/50 ms             | - |

| Carrier frequency driftrate<br>(five slots)  fdriftrate |        | -      | 5    | 20   | kHz/50 ms             | - |

#### Table 14.BDR -Receiver Part

| Parameter                                                        | Symbol |      | Values |      |     | Note / Test Condition                                      |

|------------------------------------------------------------------|--------|------|--------|------|-----|------------------------------------------------------------|

|                                                                  |        | Min. | Тур.   | Max. |     |                                                            |

| Sensitivity                                                      |        | -    | -86    | -81  | dBm | Ideal wanted signal                                        |

| C/I-performance:<br>-4th adjacent channel                        |        | -    | -51    | -40  | dB  | -                                                          |

| C/I-performance:<br>-3rd adjacent channel<br>(1st adj. of image) |        | -    | -46    | -20  | dB  | -                                                          |

| C/I-performance:<br>-2nd adjacent channel (image)                |        | -    | -35    | -9   | dB  | -                                                          |

| C/I-performance:<br>-1st adjacent channel                        |        | -    | -4     | 0    | dB  | -                                                          |

| C/I-performance: co. channel                                     |        | -    | 9      | 11   | dB  | -                                                          |

| C/I-performance:<br>+1st adjacent channel                        |        | -    | -4     | 0    | dB  | -                                                          |

| C/I-performance:<br>+2nd adjacent channel                        |        | -    | -40    | -30  | dB  | -                                                          |

| C/I-performance:<br>+3rd adjacent channel                        |        | -    | -50    | -40  | dB  | -                                                          |

| Blocking performance<br>30 MHz - 2 GHz                           |        | 10   | -      | -    | dBm | Some spurious responses, but according to BT-specification |

| Blocking performance<br>2 GHz - 2.4 GHz                          |        | -27  | -      | -    | dBm | -                                                          |

| Blocking performance<br>2.5 GHz - 3 GHz                          |        | -27  | -      | -    | dBm | -                                                          |

| Blocking performance<br>3 GHz - 12.75 GHz                        |        | 10   | -      | -    | dBm | Some spurious responses, but according to BT-specification |

| Intermodulation performance                                      |        | -39  | -34    | -    | dBm | Valid for all intermodulation tests                        |

| Maximum input level                                              |        | -20  | -      | -    | dBm | -                                                          |

#### Table 15. EDR - Transmitter Part

| Parameter                                 | Symbol | Values |      | Unit | Note / Test Condition |   |

|-------------------------------------------|--------|--------|------|------|-----------------------|---|

|                                           |        | Min.   | Тур. | Max. |                       |   |

| Output power (high gain)                  |        | -2.5   | -    | 2    | dBm                   |   |

| Relative transmit power:<br>PxPSK - PGFSK |        | -4     | -0.6 | 1    | dB                    |   |

| Carrier frequency stability  ωi           |        | -      | -    | 75   | kHz                   | - |

| Carrier frequency stability  ωi+ω0        |        | -      | -    | 75   | kHz                   | - |

| Carrier frequency stability  ω0           |        | -      | 2    | 10   | kHz                   | - |

| DPSK - RMS DEVM                           |        | -      | 10   | 20   | %                     | - |

| 8DPSK - RMS DEVM                          |        | -      | 10   | 13   | %                     | - |

| DPSK - Peak DEVM                          |        | -      | 20   | 35   | %                     | - |

| 8DPSK - Peak DEVM                         |        | -      | 20   | 25   | %                     | - |

| DPSK - 99% DEVM                           |        | -      | -    | 30   | %                     | - |

| 8DPSK - 99% DEVM                          |        | -      | -    | 20   | %                     | - |

| Differential phase encoding               |        | 99     | 100  | -    | %                     | - |

#### Electrical Characteristics

## Table 15. EDR - Transmitter Part (Continued)

| Parameter                  | Symbol | Values |      |      | Unit | Note / Test Condition                |

|----------------------------|--------|--------|------|------|------|--------------------------------------|

|                            |        | Min.   | Тур. | Max. |      |                                      |

| 1st adjacent channel power |        | -      | -40  | -26  | dBc  | -                                    |

| 2nd adjacent channel power |        | -      | -    | -20  | dBm  | Carrier power measured at basic rate |

| 3rd adjacent channel power |        | -      | -    | -40  | dBm  | Carrier power measured at basic rate |

#### Table 16.EDR -Receiver Part

| Parameter                                                             | Symbol | Values |      |      | Unit | Note / Test Condition |

|-----------------------------------------------------------------------|--------|--------|------|------|------|-----------------------|

|                                                                       |        | Min.   | Тур. | Max. | -    |                       |

| DQPSK-Sensitivity                                                     |        | -      | -88  | -83  | dBm  | Ideal wanted signal   |

| 8DPSK-Sensitivityl                                                    |        | -      | -83  | -77  | dBm  | Ideal wanted signal   |

| DQPSK - BER Floor Sensitivity                                         |        | -      | -84  | -60  | dBm  | -                     |

| 8DPSK - BER Floor Sensitivity                                         |        | -      | -79  | -60  | dBm  | -                     |

| DQPSK - C/I-performance:<br>-4th adjacent channel                     |        | -      | -53  | -40  | dB   | -                     |

| DQPSK - C/I-performance:<br>-3rd adjacent channel (1st adj. of image) |        | -      | -47  | -20  | dB   | -                     |

| DQPSK - C/I-performance:<br>-2nd adjacent channel (image)             |        | -      | -31  | -7   | dB   | -                     |

| DQPSK - C/I-performance:<br>-1st adjacent channel                     |        | -      | -7   | 0    | dB   | -                     |

| DQPSK - C/I-performance:<br>co. channel                               |        | -      | 11   | 13   | dB   | -                     |

| DQPSK - C/I-performance:<br>+1st adjacent channel                     |        | -      | -9   | 0    | dB   | -                     |

| DQPSK - C/I-performance:<br>+2nd adjacent channel                     |        | -      | -44  | -30  | dB   | -                     |

| DQPSK - C/I-performance:<br>+3rd adjacent channel                     |        | -      | -50  | -40  | dB   | -                     |

| 8DPSK - C/I-performance:<br>-4th adjacent channel                     |        | -      | -48  | -33  | dB   | -                     |

| 8DPSK - C/I-performance:<br>-3rd adjacent channel (1st adj. of image) |        | -      | -44  | -13  | dB   | -                     |

| 8DPSK - C/I-performance:<br>-2nd adjacent channel (image)             |        | -      | -25  | 0    | dB   | -                     |

| 8DPSK - C/I-performance:<br>-1st adjacent channel                     |        | -      | -5   | 5    | dB   | -                     |

| 8DPSK - C/I-performance:<br>co. channel                               |        | -      | 17   | 21   | dB   | -                     |

| 8DPSK - C/I-performance:<br>+1st adjacent channel                     |        | -      | -5   | 5    | dB   | -                     |

| 8DPSK - C/I-performance:<br>+2nd adjacent channel                     |        | -      | -36  | -25  | dB   | -                     |

| 8DPSK - C/I-performance:<br>+3rd adjacent channel                     |        | -      | -46  | -33  | dB   | -                     |

| Maximum input level                                                   |        | -20    | -    | -    | dBm  | -                     |

## 7.0 Package Information

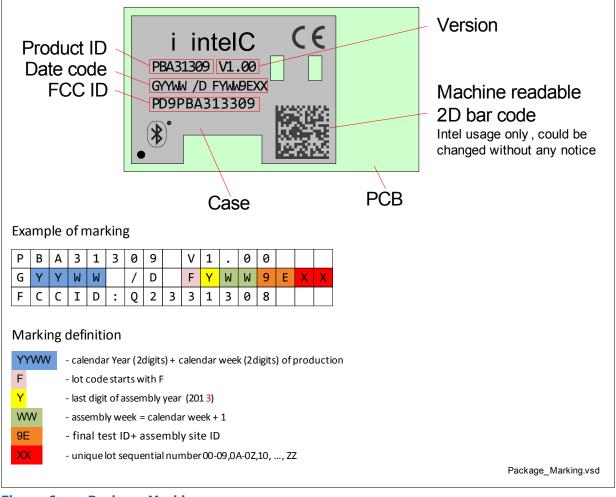

## 7.1 Package Marking

## 7.2 Production Package

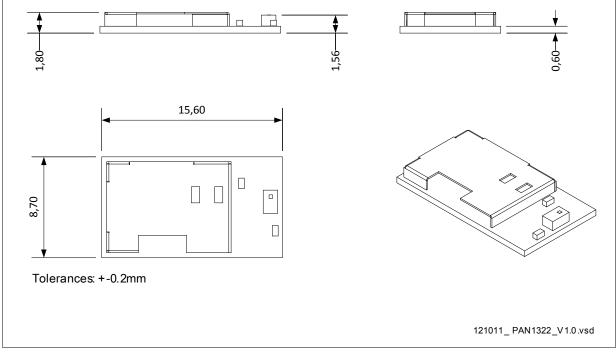

#### Figure 7. Production Package

All dimensions are in mm.

Tolerances on all outer dimensions, height, width and length, are +/- 0.2 mm.

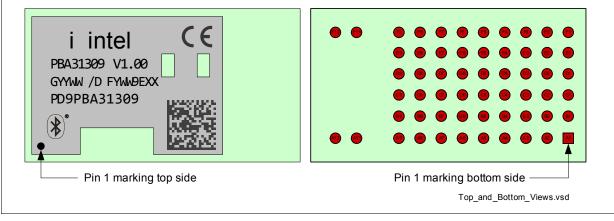

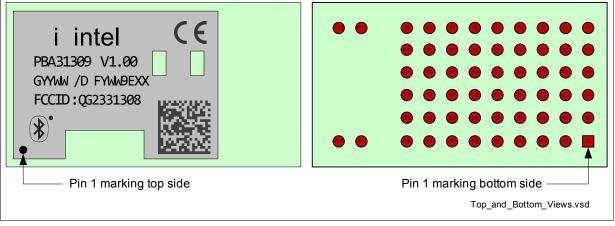

### 7.2.1 Pin Mark

Pin 1 (A1) is marked on bottom footprint and on the top of the shield on the module according to Figure 8. Diameter of pin 1 mark on the shield is 0.40 mm.

## 8.0 Bluetooth Qualification and Regulatory Certification

## 8.1 Reference Design

#### Figure 9. Reference Design Schematics

PBA 31309 is intended to be installed inside end user equipment. PBA 31309 is Bluetoooth-qualified and also FCC-certified, and conforms to R&TTE (European) requirements and directives with the reference design described in Figure 9.

Manufacturers of mobile, fixed or portable devices incorporating this device are advised to clarify any regulatory questions and to have their complete product tested and approved for compliance (FCC or other when applicable).

There are no parts in PBA 31309 that can be modified by the user except modifications of the device BD data and loading of SW patches. Any changes or modifications made to this device that are not expressly approved by Intel, may void the user's authority to operate the equipment.

## 8.2 FCC Class B Digital Devices Regulatory Notice

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by 1 or more of the following measures:

- Reorient or relocate the antenna

- Increase the separation between the equipment and receiver

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected

- Consult the dealer or an experienced radio or television technician for help

## 8.3 FCC Wireless Notice

This product emits radio frequency energy, but the radiated output power of this device is far below the FCC radio frequency exposure limits. Nevertheless, the device should be used in such a manner that the potential for human contact with the antenna during normal operation is minimized.

To meet the FCC's RF exposure rules and regulations:

- The system antenna used for this transmitter must not be co-located or operating in conjunction with any other antenna or transmitter.

- The on-board antenna used must not be altered.

- Users and installers must be provided with antenna installation instructions and transmitter operating conditions for satisfying RF exposure compliance. See Figure 10.

#### Figure 10. Cutout Drawing

Manufacturers of mobile, fixed or portable devices incorporating this module are advised to clarify any regulatory questions and to have their complete product tested and approved for FCC compliance.

## 8.4 FCC Interference Statement

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- 1. This device may not cause harmful interference

- 2. This device must accept any interference received, including interference that may cause undesired operation.

## 8.5 FCC Identifier

FCC ID: PD9PBA31309

## 8.6 European R&TTE Declaration of Conformity

Hereby, Intel declares that the Bluetooth module PBA 31309 is in compliance with the essential requirements and other relevant provisions of Directive 1999/5/EC.

As a result of the conformity assessment procedure described in Annex III of the Directive 1999/5/EC, the end-customer equipment should be labelled as follows:

CE

#### Figure 11. Equipment Label

eUniStone in the specified reference design can be used in the following countries:

Austria, Belgium, Cyprus, Czech Republic, Denmark, Estonia, Finland, France, Germany, Greece, Hungary, Ireland, Italy, Latvia, Lithuania, Luxembourg, Malta, Poland, Portugal, Slovakia, Slovenia, Spain, Sweden, The Netherlands, the United Kingdom, Switzerland, and Norway.

#### Figure 12. Declaration of Conformity

The product will be compliant to R&TTE Directive 1999/5/EC: EN 60950-1 2006, EN 50371: 2002 Health and Safety of the User EN301 489-1, v1.8.1, EN301 489-17 v2.1.1 Electromagnetic Compatibility EN300 328 v1.8.1 Effective use of spectrum allocated.

## 8.7 Bluetooth Qualified Design ID

Intel has submitted End Product Listings (EPL) for eUniStone and eBMU in the Qualified Product List of the Bluetooth SIG. These EPLs are referencing the Bluetooth qualification of the SPP-AT application running on the eBMU chip under QD ID t.b.d.

Manufacturers of Bluetooth devices incorporating eUniStone or eBMU can reference the same QD ID number.

Bluetooth QD ID: B021246

## 8.9 Label Design of the Host Product

It is recommended to include the following information on the host product label:

Contains transmitter Module FCC ID: PD9PBA31309

### 8.10 Regulatory Test House

The test house used by Intel in the Bluetooth and Regulatory approvals for the module PBA 31309:

AT4wireless Parque Tecnologico de Andalucia c/ Severo Ochoa 2 E-29590 - Malaga SPAIN Tel: (34) 95 261 91 00 Fax: (34) 95 261 91 13 www.at4wireless.com

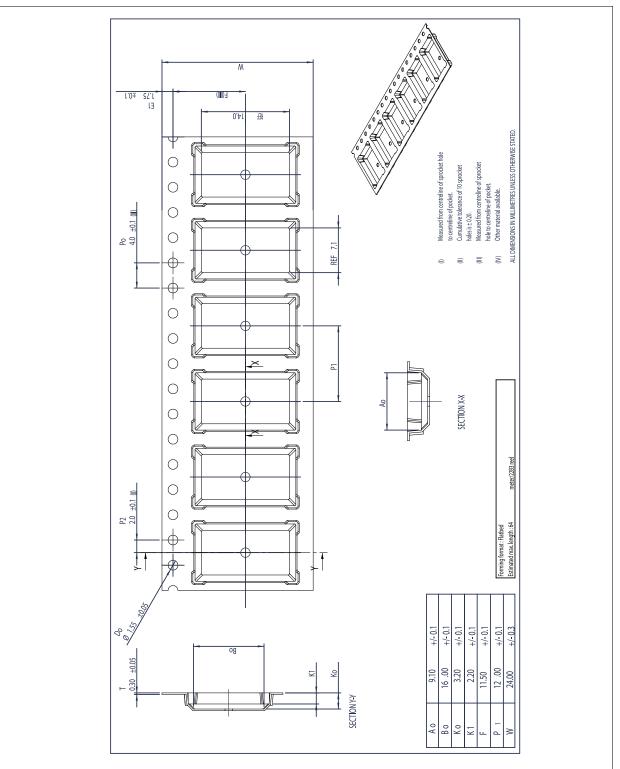

The target of this chapter is to provide guidelines for customers to successfully introduce the eUniStone module in production. This includes general description, PCB-design, solder printing process, assembly, soldering process, rework and inspection.

## 9.1 General Description of the Module

eUniStone is a Land Grid Array (LGA 6x12) module made for surface mounting. The pad diameter is 0.6 mm and the pitch 1.2 mm.

All solder joints on the module will reflow during soldering on the mother board. All components and shield will stay in place due to wetting force. Wave soldering is not possible.

Surface treatment on the module pads is Nickel (5-8  $\mu$ m)/Gold (0.04 - 0.10  $\mu$ m).

Figure 13 shows the pad layout on the module, seen from the component side.

Figure 13. Pad Layout on the Module (top view)

# 9.2 Printed Circuit Board Design

The land pattern on the PCB shall be according to the land pattern on the module, which means that the diameter of the LGA pads on the PCB shall be 0.6 mm. It is recommended that each pad on the PCB shall be surrounded by a solder mask clearance of about 75  $\mu$ m to avoid overlapping solder mask and pad.

## Figure 14. Cutout Drawing

In order to preserve the characteristics of the embedded antenna, a cutout must be respected under the antenna through all metal layers of the PCB, as shown in drawing Figure 14.

Placing the module inside a metal housing or close to metal parts like fasteners, shielding cages, washers, etc. can significantly affect the antenna characteristics.

# 9.3 Solder Paste Printing

The solder paste deposited on the PCB by stencil printing has to be of eutectic or near eutectic tin leadfree / lead composition. A no-clean solder paste is preferred, since cleaning of the solder joints is difficult because of the small gap between the module and the PCB.

Preferred thickness of the solder paste stencil is  $100 - 127 \mu$ mm (4 - 5 mils). The apertures on the solder paste stencil shall be of the same size as the pads, 0.6 mm.

## 9.4 Assembly

## 9.4.1 Component Placement

In order to assure a high yield, good placement on the PCB is necessary. As a rule of thumb the tolerable misplacement is  $150 \mu$ mm. This means that the eUniStone module can be assembled with a variety of placement systems.

It is recommended to use a vision system capable of package pad recognition and alignment that evaluates the pad locations on the package (in contrast to outline centring). This eliminates the pad to package edge tolerance.

The recommendation is to pick and place the module with a nozzle in the centre of the shield. The nozzle diameter shall not be bigger than 4 mm.

## 9.4.2 Pin Mark

Pin 1 (A1) is marked on bottom footprint and on the top of the shield on the module according to Figure 15. Diameter of pin 1 mark on the shield is 0.40 mm.

eUniStone PBA 31309

Assembly Guidelines

## 9.4.3 Package

eUniStone is packed in tape on reel according to Figure 16.

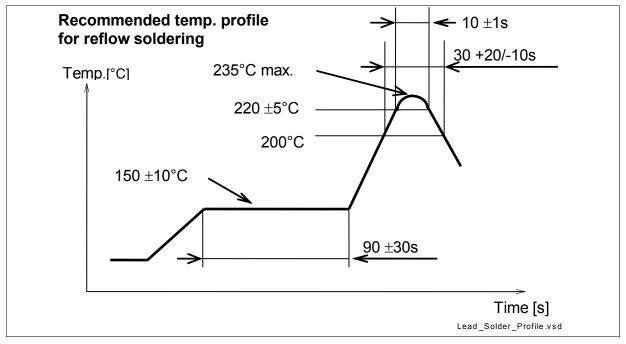

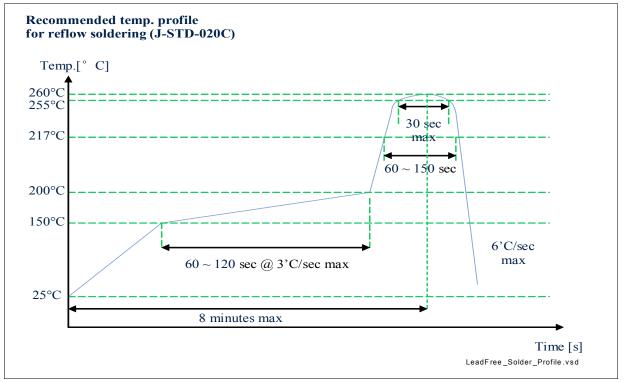

# 9.5 Soldering Profile

Generally all standard reflow soldering processes (vapour phase, convection, infrared) and typical temperature profiles used for surface mount devices are suitable for the eUniStone module. **Wave soldering is not possible.**

Figure 17 and Figure 18 shows example of a suitable solder reflow profile. One for leaded and one for leadfree solder.

At the reflow process each solder joint has to be exposed to temperatures above solder liquids for a sufficient time to get the optimum solder joint quality, whereas overheating the board with its components has to be avoided. Using infrared ovens without convection special care may be necessary to assure a sufficiently homogeneous temperature profile for all solder joints on the PCB (especially on large, complex boards with different thermal masses of the components). The most recommended types are therefore forced convection or vapour phase reflow. Nitrogen atmosphere can generally improve solder joint quality, but is normally not necessary.