tial

Revised Date: July 20, 2005

# UW2453/2453L Data Sheet

# (Preliminary)

### Doc. #: DS-2453-01 <Rev. 0.1>

The content of this technical information is subject to change without notice. Please contact UBEC for further information.

All rights strictly reserved. Any portion of this paper shall not be reproduced, copied, or transformed to any other forms without permission from Uniband electronics corp. .

#### Uniband Electronics Corp. (Taiwan)

3F-2, No. 192, Dongguang Rd. Hsinchu 300, Taiwan TEL: +886-3-5729898 FAX: +886-3-5718599 http:// www.ubec.com.tw

#### Uniband Electronics Corp. (U.S.A.)

826, North Hillview Drive, Milpitas. CA 95035, USA TEL: +1-408-935-7888 FAX: +1-408-935-7889

#### **Revision History**

| Revision | Date           | Description of Change                                              |

|----------|----------------|--------------------------------------------------------------------|

| 0.0      | March 18, 2005 | Initial Version                                                    |

| 0.1      | July 20, 2005  | Change GS5 and Bit[15] of Register 0101 step size from 0.5 to 3 dB |

|          |                |                                                                    |

|          |                |                                                                    |

#### 1 **Product Description**

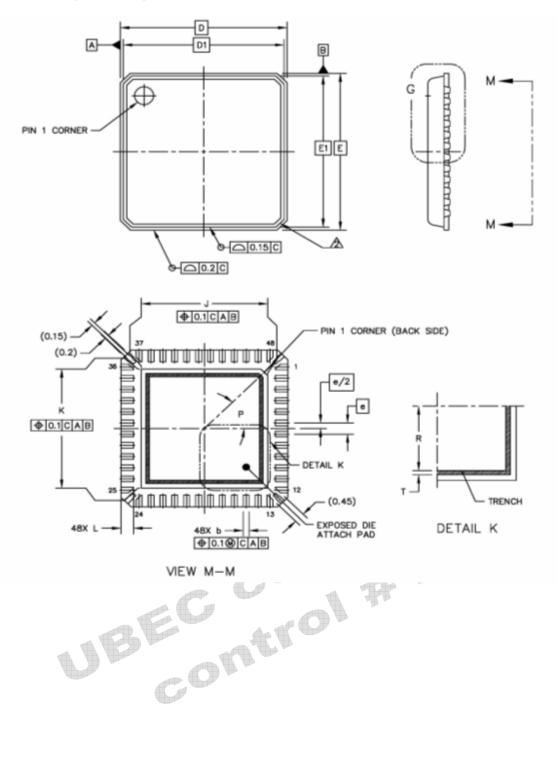

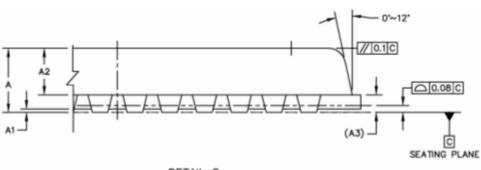

The UW2453 is a fully integrated single-chip transceiver (including PA) specifically designed for IEEE802.11b/g wireless local area networks (WLANs) applications. It supports data rate 6, 9, 12, 18, 24, 36, 48 and 54 Mbits/s in OFDM mode, 5.5 and 11 Mbits/s in CCK mode, 1 and 2 Mbits/s in DSSS mode. The UW2453 integrates a receiver, transmitter, VCO and PLL as well a power amplifier into a single IC. It uses direct conversion radio architecture to minimize external parts count and power consumption. Only one or two switches, one RF bandpass filter, one lowpass filter and several passive components are required to build a spec compliant 11b/g radio. The patented DC cancellation technique allows the receiver set its gain at super fast speed as required for the gain settling in the OFDM mode. The patent pending power amplifier design assures a very good TX linearity at a minimum current consumption. The UW2453 is fabricated by advanced SiGe BiCMOS process and is housed in a 48-pin QFN 7x7 mm<sup>2</sup> package. The UW2453L is a lower output power and lower current (TX) version of the UW2453. The UW2453L has the same package and pinout.

The low power consumption of the UW2453/UW2453L makes it an ideal candidate for WLAN applications in desktop/laptop PC, handheld devices and mobile handsets.

#### 2 **Features**

- IEEE 802.11 b/g specification compliant 0

- 6, 9, 12, 18, 24, 36, 48 and 54 Mbit/s in OFDM mode 0

- 1, 2, 5.5 and 11 Mbits/s in DSSS and CCK mode 0

- 2.4 to 2.5 GHz frequency operation 0

- -87 dBm sensitivity at 11 Mbits/s CCK mode 0

- -73 dBm sensitivity at 54M bits/s OFDM mode 0

- High performance and low power consumption 0

- Zero IF receive and direct conversion transmit architecture 0

- Integrated low phase noise VCO and PLL loop filter 0

- Integrated power amplifier 0

- Shared RX and TX filter structure to minimize die size 0

- High performance  $\Sigma\Delta$  frequency synthesizer 0

- High receiver and RSSI dynamic range 0

- Support antenna diversity 0

- Patented super fast DC cancellation 0

- Ultra fast digital RX and TX gain settling time 0

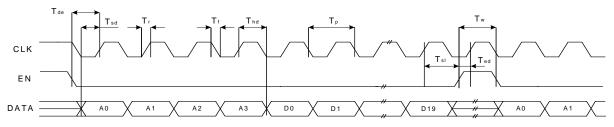

- Complementary 3-wire bus RX and TX gain control 0

- +18 dBm transmit power (54 Mbits/s OFDM) for UW2453 0

- +14 dBm transmit power (54 Mbits/s OFDM) for UW2453L 0

- +21 dBm transmit power (11 Mbits/s CCK) for UW2453 0

- +17 dBm transmit power (11 Mbits/s CCK) for UW2453L 0

- MIMO transceiver support 0

- 5 uA sleep mode 0

- Support  $2.7 \sim 3.6$  V supply 0

- Small 48-pin leadless QFN 7x7 mm<sup>2</sup> package 0

- SiGe BiCMOS technology 0

- Low external component count 0

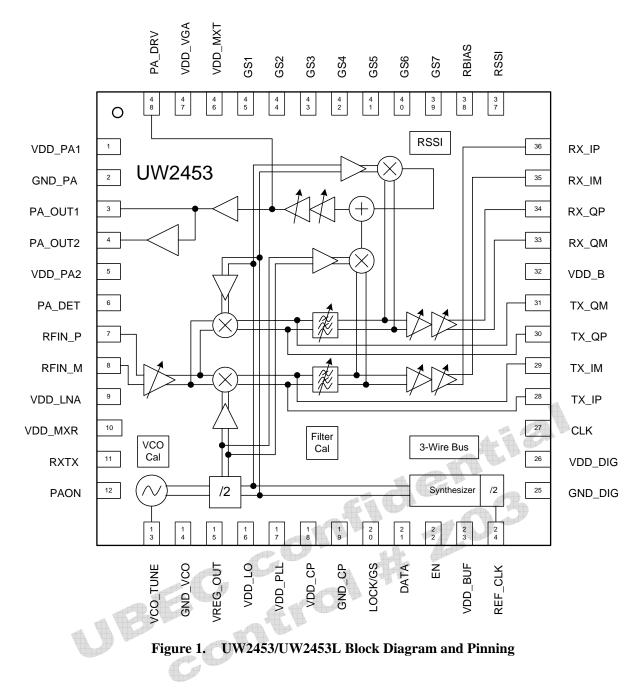

#### 3 Block Diagram and Pin Configuration

#### Table 1.Pin Descriptions

Pin type abbreviation: A = Analog, D = Digital, I = Input, O = Output

| PIN | SYMBOL   | ТҮРЕ | DESCRIPTION                                                                |

|-----|----------|------|----------------------------------------------------------------------------|

| 1   | VDD_PA1  |      | PA power supply. Bypass with a cap as close to the pin as possible.        |

| 2   | GND_PA   |      | PA ground                                                                  |

| 3   | PA_OUT1  | AO   | PA 1 <sup>st</sup> stage open collector output.                            |

| 4   | PA_OUT2  | AO   | PA 2 <sup>nd</sup> stage open collector output. It is TX RF output.        |

| 5   | VDD_PA2  |      | PA power supply. Bypass with a cap as close to the pin as possible.        |

| 6   | PA_DET   |      | PA power detector output.                                                  |

| 7   | RFIN_P   | AI   | LNA differential RF input (+)                                              |

| 8   | RFIN_M   | AI   | LNA differential RF input (-)                                              |

| 9   | VDD_LNA  |      | LNA power supply. Bypass with a cap as close to the pin as possible.       |

| 10  | VDD_MXR  |      | RX mixer power supply. Bypass with a cap as close to the pin as possible.  |

| 11  | RXTX     | DI   | RX and TX mode select                                                      |

| 12  | PAON     | DI   | PA turn on/off control                                                     |

| 13  | VCO_TUNE |      | PLL loop cap to ground                                                     |

| 14  | GND_VCO  |      | VCO ground                                                                 |

| 15  | VREG_OUT |      | Regulated supply for VCO. Bypass with caps to ground                       |

| 16  | VDD_LO   |      | LO power supply. Bypass with a cap as close to the pin as possible.        |

| 17  | VDD_PLL  |      | PLL power supply. Bypass with a cap as close to the pin as possible.       |

| 18  | VDD_CP   |      | Charge-pump supply. Bypass with a cap as close to the pin as possible.     |

| 19  | GND_CP   |      | Ground for charge pump circuit                                             |

| 20  | LOCK/GS  | DIO  | Synthesizer lock indicator or GS1~7 latch control                          |

| 21  | DATA     | DI   | Three-wire bus data signal                                                 |

| 22  | EN       | DI   | Three-wire bus enable                                                      |

| 23  | VDD_BUF  |      | Clock buffer supply. Bypass with a cap as close to the pin as possible.    |

| 24  | REF_CLK  | AI   | Reference clock input                                                      |

| 25  | GND_DIG  |      | Ground for digital circuit                                                 |

| 26  | VDD_DIG  |      | Digital circuit supply. Bypass with a cap as close to the pin as possible. |

| 27  | CLK      | DI   | Three-wire bus clock                                                       |

| 28  | TX_IP    | AI   | Transmitter I channel differential input (+)                               |

| 29  | TX_IM    | AI   | Transmitter I channel differential input (-)                               |

| 30  | TX_QP    | AI   | Transmitter Q channel differential input (+)                               |

| 31  | TX_QM    | AI   | Transmitter Q channel differential input (-)                               |

# Bubec

| VDD_B                                                                                   |                                                                                                                           | Analog circuit supply. Bypass with a cap as close to the pin as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| RX_QM                                                                                   | AO                                                                                                                        | Receiver Q channel differential output (-)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| RX_QP                                                                                   | AO                                                                                                                        | Receiver Q channel differential output (+)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| RX_IM                                                                                   | AO                                                                                                                        | eceiver Q channel differential output (-)<br>eceiver Q channel differential output (+)<br>eceiver I channel differential output (+)<br>eceiver I channel differential output (+)<br>SSI output<br>ias resistor pin. Connect an 12 k $\Omega$ (1%) resistor to the bias ground.<br>dB VGA gain control pin<br>dB VGA gain control pin<br>dB VGA gain control pin<br>dB VGA gain control pin<br>edB VGA gain control pin<br>bidB VGA gain control pin<br>control pin<br>control pin<br>dB VGA gain control pin<br>control pin<br>cont |  |  |  |  |  |

| RX_IP                                                                                   | AO                                                                                                                        | Receiver I channel differential output (+)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| RSSI                                                                                    | AO                                                                                                                        | RSSI output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| RBIAS                                                                                   |                                                                                                                           | Bias resistor pin. Connect an 12 k $\Omega$ (1%) resistor to the bias ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| GS7                                                                                     | DI                                                                                                                        | 2 dB VGA gain control pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| GS6                                                                                     | DI                                                                                                                        | 4 dB VGA gain control pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| GS5                                                                                     | DI                                                                                                                        | 8 dB VGA gain control pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| GS4                                                                                     | DI                                                                                                                        | 16 dB VGA gain control pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GS3                                                                                     | DI                                                                                                                        | 32 dB VGA gain control pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GS2                                                                                     | DI                                                                                                                        | LNA/filter gain control pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GS1                                                                                     | DI                                                                                                                        | LNA/filter gain control pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| VDD_MXT                                                                                 |                                                                                                                           | TX mixer power supply. Bypass with a cap as close to the pin as<br>possible.TX VGA power supply. Bypass with a cap as close to the pin as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| VDD_VGA         TX VGA power supply. Bypass with a cap as close to the pin as possible. |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 48     PA_DRV     AO     PA driver stage open collector output                          |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| GND_SLUG                                                                                |                                                                                                                           | Chip ground. Connect to PCB ground plane using several via.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| UB                                                                                      | EC                                                                                                                        | Chip ground. Connect to PCB ground plane using several via.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|                                                                                         | RX_QP<br>RX_IM<br>RX_IP<br>RSSI<br>RBIAS<br>GS7<br>GS6<br>GS5<br>GS4<br>GS3<br>GS2<br>GS1<br>VDD_MXT<br>VDD_VGA<br>PA_DRV | RX_QMAORX_QPAORX_IMAORX_IMAORX_IPAORSSIAORBIASOGS7DIGS6DIGS3DIGS1DIVDD_VGAPA_DRVPA_DRVAO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

#### 4 Operation Condition

| Table 2.   Absolute Maximum Ratings   |      |         |      |  |  |  |  |  |

|---------------------------------------|------|---------|------|--|--|--|--|--|

| PARAMETER                             | MIN  | MAX     | UNIT |  |  |  |  |  |

| Storage temperature                   | -55  | +150    | °C   |  |  |  |  |  |

| Supply voltage VDD pin to ground      | -0.5 | +4.2    | V    |  |  |  |  |  |

| Voltage applied to input pins         | -0.5 | VDD+0.5 | V    |  |  |  |  |  |

| Voltage applied to output pins        | -0.5 | VDD+0.5 | V    |  |  |  |  |  |

| Short circuit duration, to GND or VDD |      | 5       | sec  |  |  |  |  |  |

| Table 3. | <b>Recommended Operating Conditions</b> |

|----------|-----------------------------------------|

|----------|-----------------------------------------|

| PARAMETER                                     | MIN     | ТҮР | MAX     | UNITS |

|-----------------------------------------------|---------|-----|---------|-------|

| Ambient Operating Temperature                 | -30     |     | +85     | °C    |

| Supply Voltage                                | 2.7     | 3.0 | 3.6     | V     |

| Logical high input voltage (for DI type pins) | VDD-0.4 |     | VDD+0.3 | V     |

| Logical low input voltage (for DI type pins)  | -0.3    |     | 0.4     | V     |

#### 5 Current Consumptions

Table 4.Current Consumptions

$T_A = 25 \ ^{\circ}C, \ VDD = 2.85 \ V$

| CHIP MODE                   | CONDITION                               | MIN | ТҮР | MAX | UNIT |

|-----------------------------|-----------------------------------------|-----|-----|-----|------|

| SLEEP                       | Register 0000, Mode Bits = 0000         |     | 5   |     | uA   |

| IDLE                        | Register 0000, Mode Bits = 0001         |     | 28  |     | mA   |

| TX (18 dBm OFDM<br>UW2453)  | Register 0000, Mode Bits = 0010, RXTX=0 |     | 228 |     | mA   |

| TX (14 dBm OFDM<br>UW2453L) | Register 0000, Mode Bits = 0010, RXTX=0 |     | 164 |     | mA   |

| RX                          | Register 0000, Mode Bits = 0010, RXTX=1 |     | 76  |     | mA   |

| CAL_FIL                     | Register 0000, Mode Bits = 0011         |     | 3   |     | mA   |

| CAL_VCO                     | Register 0000, Mode Bits = 0100         |     | 22  |     | mA   |

| RESET                       | Register 0000, Mode Bits = 0111         |     | NA  |     | mA   |

# Bubec

#### 6 UW2453/UW2453L Functional Description

The UW2453/UW2453L receiver consists of a LNA, a pair of down-conversion mixers, I&Q channel filters, I&Q variable gain amplifiers (VGA), RSSI and programmable DC blocking cancellation blocks. The LO generation circuits (VCO, PLL and buffers) are shared with the receiver and transmitter. The LNA features a differential input for high performance. An external balum matching network is required. The LNA has 2 stepped gains. Along with one stepped gain inside the channel filter, three stepped gains are achieved in the receive chain from the LNA to the channel filters and they are controlled by two digital I/O pins, GS1 and GS2. The additional receive gain is realized by the RX VGA. The RX VGA has a gain resolution of 2 dB and the gain is set by Pins GS3~GS7. Pin GS7 sets a two dB change. Since the RX gain is set by the digital I/O pins, fast gain settling is realized. The RX gain can also be set by the regular or 3-wire bus in addition to the pins GS1~GS7.

The UW2453/UW2453L features a patented DC blocking circuit and the DC blocking circuit settles the receive DC offset for less than 10 mV at the RX outputs within 400 ns for any gain size change. To have a better control over the DC settling process, the settling time is programmable.

To set a proper RX gain without a prior knowledge of the received signal strength, the UW2453/UW2453L only needs a maximum of three times of gain adjustment with the help of the high dynamic range RSSI output. When the input signal is below -41 dBm, only two times of gain adjustment is required thanks to the high dynamic range of the RSSI circuit.

The UW2453/UW2453L also supports antenna diversity. However, antenna diversity requires a total settling time equivalent to a maximum of four times of gain adjustment. That means if in no diversity case, the worst total gain settling time is 2.4 us, it is 3.2 us with diversity.

Before the receiver properly demodulates the signal, filter and VCO calibration are needed. The filter and VCO calibration finds the correct filter corner frequency and VCO subband respectively, amid process, supply and temperature variation. The VCO and filter calibration are self-contained and no support from DSP side is required.

One unique feature is the receiver and transmitter share a pair of I&Q channel filter in order to minimize the die size and cost. However, the filter bandwidth in RX and TX mode can be independently programmed, thanks to the innovative design.

The switch between receive and transmit is controlled by Pin RXTX in the RXTX\_EN chip mode. This pin also determines the filter bandwidth in conjunction with other register settings.

The transmitter features direct conversion architecture with +18 dBm output power with OFDM signal and +21 dBm output power with CCK signal with the integrated power amplifier for the UW2453 while the corresponding numbers are 14 and 17 dBm for the UW2453L. The output power adjustment range is 16 dB in one dB step. Pins GS1 to GS4 are used to set the TX front end gain (16 dB range). Like the receiver, the TX front end gain can also be programmed by the regular 3-wire bus.

The LO generation scheme of the UW2453/UW2453L employs a divided by 2 scheme to minimize pulling effect and to get a better phase imbalance. The VCO operates at the twice of the channel frequency. Additional feature is the  $\Sigma\Delta$  frequency synthesizer having a fine frequency resolution. The wider loop bandwidth allowed by the  $\Sigma\Delta$  frequency synthesizer is also helpful in tracking the VCO pulling and pushing effect. The VCO has a switched band design such that low phase noise, low VCO gain factor and high stability are realized. The advanced VCO calibration scheme makes it possible that the carrier frequency is always in the middle of one of the VCO bands. After reprogramming the channel frequency, a VCO calibration action is required. The PLL charge pump current is programmable so that the VCO gain variation for different bands can be compensated.

The UW2453/UW2453L has a power-up reset to set the registers to their default values. There is also a reset mode to allow the 3-wire bus to reset the IC at any time. After a reset, the UW2453/UW2453L automatically enters the sleep mode.

Pin 20 (LOCK/GS) is a special input/output pin. It can be programmed as the PLL lock detector output or as an enable pin for Pin GS1~GS7. If Pin 20 is configured as the GS1~GS7 enable pin, when Pin 20=1, any change on GS1~GS7 will cause RX or TX gain change. When Pin 20=0, any change on GS1~GS7 has no effect

on RX/TX gain and the receiver or transmitter uses the last GS1~GS7 values when Pin 20=1. That is a high to low transition will latch the GS1~GS7 value. This feature is useful so that multiple of the UW2453/UW2453L is used in a MIMO configuration without doubling or tripling the parallel control pins.

#### 7 Receiver AC Characteristics

#### Table 5.Receiver AC Characteristics

Typical values are at  $T_A = 25$  °C, VDD = 2.85 V, LO frequency=2.447 GHz

| PARAMETER                           | CONDITION                                                                                | MIN | ТҮР | MAX | UNIT |

|-------------------------------------|------------------------------------------------------------------------------------------|-----|-----|-----|------|

| RF input frequency                  |                                                                                          | 2.4 |     | 2.5 | GHz  |

| RF input range                      | Measured at balun matching input (DSSS/CCK)                                              | -97 |     | 10  | dBm  |

|                                     | Measured at balun matching input (OFDM)                                                  | -92 |     | 4   |      |

| LO frequency                        | VCO frequency divided by 2                                                               | 2.4 |     | 2.5 | GHz  |

| LO leakage                          | Measured at balun matching network input                                                 |     |     | -65 | dBm  |

| Input return loss                   | External matched to $50\Omega$ source by a balun matching network and for all gain range | -10 | -12 |     | dB   |

| RX stepped voltage gain             | GS1=1, GS2=1                                                                             |     | 48  |     | dB   |

|                                     | GS1=1, GS2=0                                                                             |     | 32  |     |      |

|                                     | GS1=0, GS2=1 or 0                                                                        |     | 9   |     |      |

| RX VGA maximum gain                 | GS3 GS4 GS5 GS6 GS7 = 11111                                                              |     | 46  |     | dB   |

| RX VGA minimum gain                 | GS3 GS4 GS5 GS6 GS7 = 00000                                                              |     | -16 |     | dB   |

| RX VGA gain step                    | GS3                                                                                      |     | 32  |     | dB   |

|                                     | GS4                                                                                      |     | 16  | 1   |      |

|                                     | GS5                                                                                      |     | 8   |     |      |

|                                     | GS6                                                                                      | 4   | 4   |     |      |

|                                     | GS7                                                                                      |     | 2   |     |      |

| Maximum RX voltage gain<br>(Note 1) | GS1 GS2 GS3 GS4 GS5 GS6 GS7 = 1111111                                                    |     | 94  |     | dB   |

| Minimum RX voltage gain<br>(Note 1) | GS1 GS2 GS3 GS4 GS5 GS6 GS7 = 0000000                                                    |     | -7  |     | dB   |

| Gain settling time (Note 2)         | Any gain size change                                                                     |     | 300 |     | ns   |

| DSB noise figure                    | GS1=1, GS2=1, VGA gain = 22 dB                                                           |     | 3   |     | dB   |

| (Including matching)                | GS1=1, GS2= 0, VGA gain = 22 dB                                                          |     | 7   |     |      |

| V                                   | GS1=0, GS2=1, VGA gain = 22 dB                                                           |     | 24  |     |      |

|                                     | GS1=0, GS2=0, VGA gain = 22 dB                                                           |     | 40  |     |      |

| Input IP3<br>(Including matching)   | GS1=1, GS2=1, VGA gain = 16 dB                                                           |     | -12 |     | dBm  |

| (Note 3)                            | GS1=1, GS2= 0, VGA gain = 16 dB                                                          |     | -8  |     |      |

|                                     | GS1=0, GS2=1, VGA gain = 16 dB                                                           |     | 10  |     |      |

|                                           | GS1=0, GS2=0, VGA gain = 16 dB                                     |      | 21   |     |                  |

|-------------------------------------------|--------------------------------------------------------------------|------|------|-----|------------------|

| Input IP2                                 | GS1=1, GS2=1, VGA gain = 16 dB                                     | 30   |      |     | dBm              |

| (Including matching)                      | GS1=1, GS2= 0, VGA gain = 16 dB                                    | 30   |      |     |                  |

| (Note 4)                                  | GS1=0, GS2=1, VGA gain = 16 dB                                     | 50   |      |     |                  |

|                                           | GS1=0, GS2=0, VGA gain = 16 dB                                     | 66   |      |     |                  |

| I&Q Gain Mismatch                         | Without calibration                                                | -0.3 |      | 0.3 | dB               |

| I&Q Phase Imbalance                       | Without calibration                                                | -2   |      | 2   | deg              |

| Channel filter characteristics            | Passband ripple (peak-to-peak 0.3~8.5 MHz )                        |      |      | 0.5 | dB               |

| (after calibration)                       | Max group delay (peak-to-peak 0.3~8.5 MHz )                        |      | 50   |     | ns               |

|                                           | Attenuation @ freq >= 12 MHz                                       | 8    |      |     | dB               |

|                                           | Attenuation @ freq >= 15 MHz                                       | 25   |      |     | dB               |

|                                           | Attenuation @ freq >= 25 MHz                                       | 60   |      |     | dB               |

| CCK adjacent channel attenuation @25 MHz  | Referenced to in-band CCK signal power                             | 50   |      |     | dB               |

| OFDM adjacent channel attenuation @25 MHz | Referenced to in-band OFDM signal power                            | 45   |      |     | dB               |

| 3 dB DC blocking frequency                | After DC settling                                                  |      | 10   |     | kHz              |

| Linear RSSI voltage output                | Input power –95 ~ -40 dBm. GS1GS2=11                               | 0.7  |      | 2   | V                |

|                                           | Input power –90 ~ -22 dBm. GS1GS2=10                               | 0.4  |      | 2   | V                |

|                                           | Input power –67 ~ 1 dBm. GS1GS2=01 or 00                           | 0.4  | 39   | 2   | V                |

| RSSI slope                                | Average RSSI voltage change per 1 dB input level change            |      | 23.5 | 7   | mV<br>/dB        |

| RSSI error                                | With OFDM short preamble                                           | -3   | D.   | 3   | dB               |

| RSSI settling time                        | GS1GS2=11 change to GS1GS2=10 or 0x<br>while GS3=GS4=GS5=GS6=GS7=1 | 10   | 300  |     | ns               |

| Resistive RSSI output load                | CO H                                                               | 10   |      |     | kΩ               |

| Capacitive RSSI output load               | G AT                                                               |      |      | 5   | pF               |

| TX to RX switching time                   | Output signal within 1 dB of final value with CW input             |      |      | 2   | us               |

| Resistive I&Q output load                 | Pin to ground/differential                                         | 5/10 |      |     | kΩ               |

| Capacitive I&Q output load                | Pin to ground/differential                                         |      |      | 6/3 | pF               |