# NCS801A HARDWARE DESCRIPTION

# 1. INTRODUCTION

The Wireless Network Camera is a device which is able to provide video streaming images through Local-Area-Network and Internet. It supports both Ethernet or 802.11g WLAN. With a CMOS type digital image sensor and advanced MPEG-4 technology, it is able to display high quality video over Wireless LAN, LAN, and Internet.

### 2. FUNCTION DESCRIPTION

This project uses the TI TMS320DM270 Digital Media Processor which include an ARM7 CPU core and a DSP subsystem to process image and voice data.

Video images captured by the CMOS image sensor are processed by the video encoder using MPEG-4 technology and transmitted over the internet through the Ethernet or 802.11g WLAN interface. The LAN interface supports 10/100BaseT with Auto-MDIX function whereas the wireless LAN interface supports 802.11b and 802.11g.

This device also supports voice that can be transferred and recorded simultaneously with the video images. The analog signals captured by a microphone are digitized by the audio codec and processed by the DSP subsystem.

There are several LEDs to display the status of the camera, LAN and wireless interfaces. Refer to Table 1.

This device derives its power from a 5V DC power adapter which needs to be converted to 1.5V, and 3.3V DC.

The functional requirements of the system are as follows:

| 1. CPU                | TI TMS320DM270                                        |  |  |

|-----------------------|-------------------------------------------------------|--|--|

| 2. CODE SIZE          | 4 Mbytes expandable to 8Mbytes                        |  |  |

| 3. SDRAM              | 32Mbytes expandable to 64Mbytes                       |  |  |

| 4. RTC                | Seiko S-3530A                                         |  |  |

| 5. Image Sensor       | CMOS, VGA 644x484 pixels, Effective:640x480 pixels    |  |  |

| 6. Audio Analog Codec | TI TLV320AIC23                                        |  |  |

| 7. LAN MAC            | Davicom DM9000                                        |  |  |

| 8. LAN PHY            | Realtek RTL8201CP, Auto-MDIX                          |  |  |

| 9. Wireless Module    | Broadcom 802.11b/g PCMCIA Module (mini-PCI connector) |  |  |

| 10. Antenna           | 1.8dBi, 2.4GHz                                        |  |  |

| 11. Debug Support     | Provide JTAG interface for S/W Development            |  |  |

|                       | Serial port                                           |  |  |

| 12. LEDs              | See Table 1.                                          |  |  |

| 13. EMC               | FCC Class B (RF), CE_RF, RSS-210, ICES-003            |  |  |

| 14. PCB Size          | 140*68 mm                                             |  |  |

| 15. PCB Layout        | 4 layers                                              |  |  |

| 16. PCB Power input   | 5V/2A, 2.5mm                                          |  |  |

**Table1. LED Status**

| LED      | Color | Control | Activity | Actions                         |

|----------|-------|---------|----------|---------------------------------|

| Power    | Green | F/W     | Off      | Camera is Powered Off           |

|          |       |         | On       | Camera is Powered On            |

|          |       |         | Blink    | Camera is booting               |

| Active   | Green | F/W     | Off      | Camera is not capturing video   |

|          |       |         | Blink    | Camera is capturing video       |

| LAN      | Green | H/W     | On       | Ethernet Connection is detected |

|          |       |         | Blink    | Sending/Receiving Data          |

| Wireless | Green | F/W     | On       | Wireless Connection is detected |

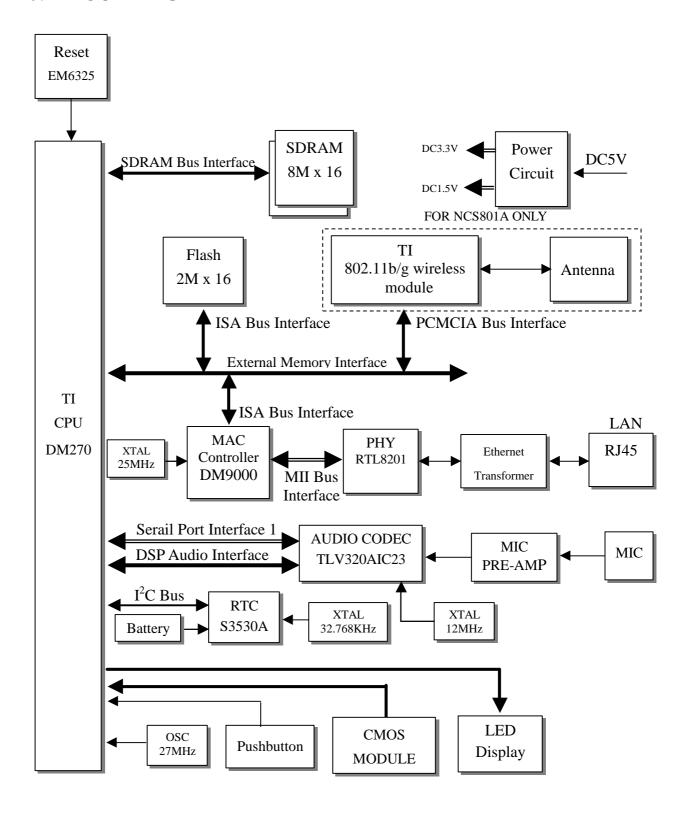

## 3. BLOCK DIAGRAM

#### 4. FUNCTIONAL BLOCK DESCRIPTION

For the following description, please refer to the block diagram.

#### a) VIDEO SUBSYSTEM

Video images are captured by the CMOS sensor in the CMOS module and the data is transferred to the video encoder inside the DM270 Digital Media Processor. The video data is encoded using MPEG-4 technology and will be transmitted either through the wired LAN or wireless LAN interface.

#### b) AUDIO SUBSYSTEM

Audio sound is captured up either by the built-in microphone or an external microphone. The signal is amplified by the pre-amplifier before being sent to the audio codec. The audio codec digitizes the analog signal and the data is transferred to the DSP subsystem inside the DM270 Digital Media Processor.

#### c) WIRED LAN SUBSYSTEM

The wired LAN subsystem consists of the DM9000 MAC controller and the PHY transceiver RTL8201CP, which provide a LAN interface according to the IEEE 802.3 specification. The PHY transceiver, together with the transformer implements auto-cross over detection features thus allowing the use of a plain or a cross-over cable to connect to the Ethernet.

#### d) WIRELESS LAN SUBSYSTEM

The wireless LAN consists of the Mini-PCI wireless module which is based on the TI TNETW1100 Wireless LAN MAC and Baseband processor. The host interface of the TNETW1100 is configured in the generic slave mode to communicate with the DM270 processor. The wireless module supports both the IEEE 802.11b and IEEE 802.11g standards.

#### e) MEMORY SUBSYSTEM

The memory subsystem consists of 4Mbytes Flash and 32Mbytes SDRAM. Configuration data for the device and the firmware required to run the device are stored in the Flash EEPROM. Upon power-up, the firmware in the flash is transferred to the SDRAM and executed from there for increased performance. In addition to executing the firmware to run the device, the SDRAM also stores video and audio data from the video and audio subsystems.

#### f) REAL-TIME CLOCK SUBSYSTEM

The Real-Time Clock (RTC) uses the Seiko S3530A, which keeps timing information required by the video subsystem. The RTC communicates with the DM270 processor through the I<sup>2</sup>C bus interface. A rechargeable battery is provided to back up the RTC when the device is powered down.

### g) POWER SUBSYSTEM

The input power required by the device is 5V DC. The 5V input power is converted to 3.3V to power the peripheral subsystems, and 1.5V required by the core of the DM270 processor. The power subsystem incorporates protection against input voltage polarity reversal and overvoltage.