# Processing Gain Measurements for IBM3920 DCT TEST report

Introduction

SONUS TELECOM, INC. FCC ID: OU3IBM3920

JOB #: 244AK1-1

Scope

EXHIBIT#: 24A

This document is a SONUS TELECOM Engineering test report for IBM3920 DCT cordlessphone. This document details the results of measurement of the processing gain of a DCT FFF phone.

### Reference Documents

This section lists documents that are referenced within or are materially relevant to this document. Code of Federal Regulations, Title 47, Chapter 1, Part 15 Radio Frequency Devices (FCC)

## Definitions

| and the second |                                        |  |

|----------------|----------------------------------------|--|

| FCC            | Federal Communications Commission      |  |

| SNR            | Signal to Noise Ratio                  |  |

| JSR            | Jammer to Signal Ratio                 |  |

| CW             | Continuous wave (jammer)               |  |

| HS             | Handset                                |  |

| BS             | Basestation                            |  |

| DBPSK          | Differential Binary Phase Shift Keying |  |

Table 1: Definitions and Abbreviations

An Overview of the FCC Method for measuring Processing Gain

The FCC in 15.247 (e) specifies two methods for measuring processing gain. The first method simply involves calculating the signal to ratio noise (SNR) with the spreading code switched on with the SNR when the spreading code is switched off.

The difference between the two is the processing gain.

The SNR is measured at the demodulated output of the receiver.

In principle this an acceptable method to measure the processing gain of any direct sequence spread spectrum communication system, however, it does not take into consideration that the non-spread spectrum portion of the system may operate under the assumption that the signal being transmitted is a spread spectrum signal and when the spreading code is switched off the system may fail to operate or operate at greatly reduced efficiency, In either case the measurement of processing gain will be meaningless. The second method specified by the FCC to measure processing gain is detailed in 15.247 (e)(1).

This involves transmitting a CW jammer in the RF passband of the system and measuring the jammer to signal ratio (JSR) required to achieve a certain bit error rate.

The choice of the actual value of the bit error rate is left up to the tester.

The jammer is stepped in 50 kHz increments across the entire passband and in each case the JSR to achieve the desired bit error rate is measured.

The JSR is measured at the RF input to the system under test.

The lowest 20% of the JSR data (in dB) is discarded.

The processing gain can then be calculated as follows:-

$$G_p = \left(\frac{S}{N}\right)_{theory} + \left(\frac{J}{S}\right)_{measured} + L_{system}$$

where  $G_p$  is the processing gain, the SNR is that theoretically predicted for the system under the test to achieve the desired bit error rate, the JSR is the lowest value (in dB) in the remaining data set and  $L_{sys}$  adjusts for non-ideal system losses.  $L_{sys}$  can not be greater than 2 dB.

### **Processing Gain Measurement Results**

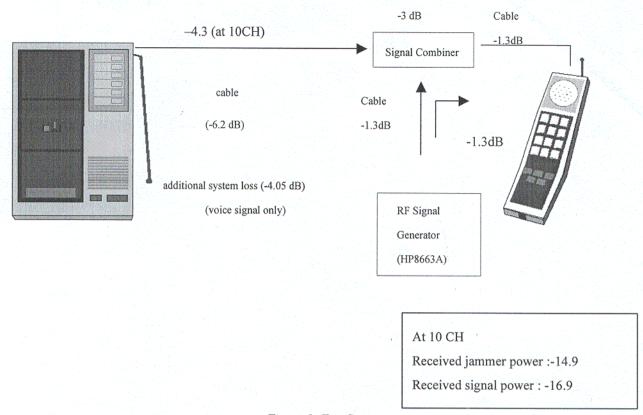

The following parameters were used in the test setup.

| HS Tx power (dBm)                | -4.3   |                                                                |

|----------------------------------|--------|----------------------------------------------------------------|

| BS LNA gain (dB)                 | 0      |                                                                |

| Test system losses (signal) (dB) | -14.55 | -4.05 dB (system), -3 dB (signal combiner), -7.5 dB (2 cables) |

| Test system losses (jammer) (dB) | -5.6   | -3 dB (signal combiner),<br>-2.6 dB (2cables)                  |

Table 2: Test Setup Parameters

The following measurement results were taken at the basestation.

The desired bit error rate was set at 10<sup>-3</sup>.

EXHIBIT#: 248

Figure 1: Test Setup

For DBPSK at 10<sup>-3</sup> bit error rate the required SNR is 8.0 dB. Using the results above and the data in the table below the processing gain is calculated to be 12.0 dB.

| Required SNR (dB)           | 8.0  |

|-----------------------------|------|

| System losses (dB)          | 2.0  |

| J/S ratio at 80% point (dB) | 2.0  |

| FCC Processing gain (dB)    | 12.0 |

Table 4: Processing Gain Calculation data

#### Conclusions

The result measured for processing gain of 12.0 dB is close to the actual processing gain due to a 12 chip spreading code of

$10 \times log_{10}(12) = 10.8 dB$

EXHIBIT#: 24C