# SPECIFICATION

Doc Desc:

# MMT-3160 PPC Hardware Design Description

| Ver. | E.C.O. No. | Description of Change | Prepared By | Released By | Valid Date |

|------|------------|-----------------------|-------------|-------------|------------|

| Α    | 5-8087     | Production Release    | LT          |             |            |

| В    |            | See ECO               | LT          |             |            |

|      |            |                       |             |             |            |

|      |            |                       |             |             |            |

|      |            |                       |             |             |            |

|      |            |                       |             |             |            |

|      |            |                       |             |             |            |

|      |            |                       |             |             |            |

|      |            |                       |             |             |            |

|      |            |                       |             |             |            |

|      |            |                       |             |             |            |

| Approved By:                  | Date |

|-------------------------------|------|

| Approved By: Varaz Shahmirian | Date |

| Reviewed By: David Choy       | Date |

| Prepared By: Lou Tondino      | Date |

| This document contains information, which is the property of Medtronic MiniMed. This document may not, in whole or in part, be duplicated, disclosed, or used for design or manufacturing purposes without the prior written permission of Medtronic MiniMed. |               |      |          |         |      |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|----------|---------|------|--|--|

| Medtronic                                                                                                                                                                                                                                                     | Save Date     | Туре | Document | Sheet   | Ver. |  |  |

| MINIMED                                                                                                                                                                                                                                                       | June 23, 2004 | Z20  | ES9313   | 1 of 43 | В    |  |  |

|                                                                                                                                                                                                                                                               |               |      |          |         |      |  |  |

# TABLE OF CONTENTS

| 1.0  | PURPOSE                                      | 4  |

|------|----------------------------------------------|----|

|      | SCOPE                                        |    |

| 3.0  | ASSOCIATED DOCUMENTS                         | 4  |

| 4.0  | DEFINITIONS AND ABBREVIATIONS                | 4  |

| 5.0  | OVERVIEW                                     |    |

| 6.0  | DETAILED DESIGN DESCRIPTION                  | 6  |

| 6    | 6.1 Power                                    | 6  |

| 6    | 5.2 Power Management                         | 7  |

| 6    | 6.3 Up-converter                             | 16 |

| 6    | 6.4 Processor                                | 17 |

| 6    | 0.5 PLD                                      | 17 |

| 6    | 6.6 Clock                                    | 18 |

| 6    | 6.7 Reset                                    | 18 |

| 6    | 5.8 External Interrupts                      | 18 |

| 6    | 5.9 External RAM                             | 19 |

| 6    | 6.10 Serial ROM                              | 20 |

| 6    | 0.11 RF                                      | 21 |

| 6    | 6.12 External I/O Ports                      | 21 |

| 6    | 5.13 Keypad                                  | 23 |

| 6    | 5.14 Buzzer                                  | 24 |

| 6    | 6.15 Vibration Motor                         | 25 |

| 6    | 6.16 AA Battery Measurement Dummy Load       | 25 |

|      | 6.17 LCD Module and Support Circuit          |    |

|      | 5.18 EL Backlight                            |    |

| 6    | 6.19 IrDA Port                               | 28 |

| 6    | 0.20 Battery Life                            | 28 |

| 6    | 6.21 Test Connector                          | 30 |

| 6    | 3.22 PLD Programming                         | 31 |

| 7.0  | XILINX COOLRUNNER PLD PROGRAMMING            | 31 |

| 8.0  | HARDWARE CHANGES AS COMPARED TO MMT315X PPC  | 34 |

| 9.0  | HARDWARE CHANGES INDUCED SOFTWARE CHANGES AS |    |

|      | COMPARED TO MMT-315X PPC                     | 41 |

| 10.0 | PC BOARD LAYOUT                              |    |

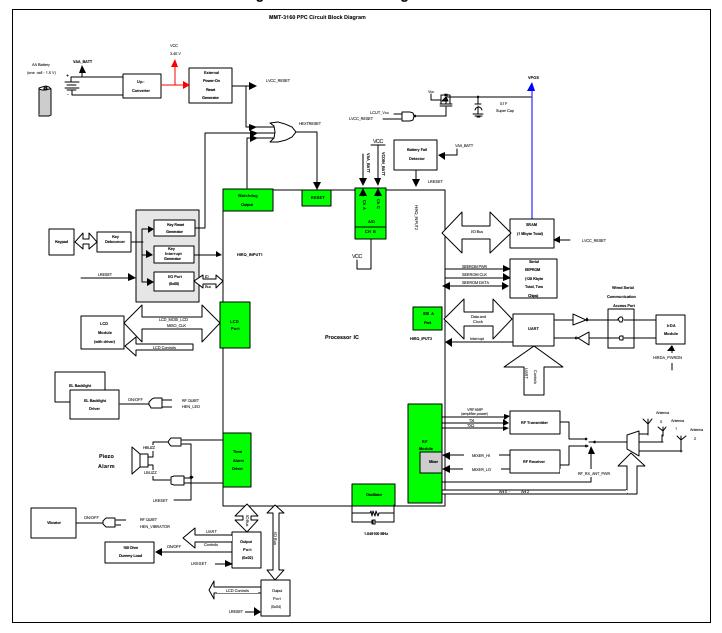

| Figure 1: PPC Block Diagram         | 5  |

|-------------------------------------|----|

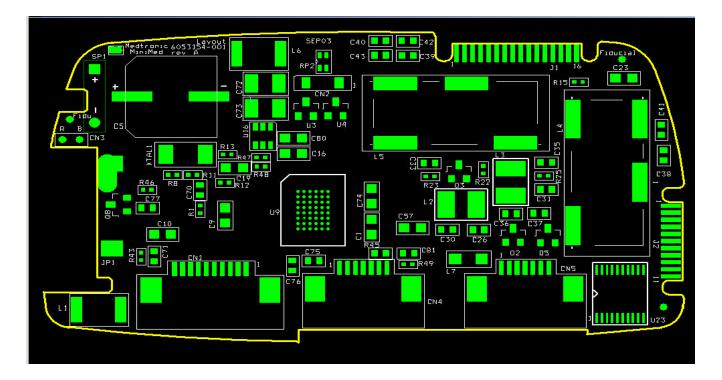

| Figure 2: MMT3160 PPC Bottom View   |    |

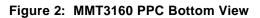

| Figure 3: MMT3160 PPC Top Side View | 43 |

| an a | ave Date      | Туре | Document | Sheet   | Ver. |

|------------------------------------------|---------------|------|----------|---------|------|

|                                          | June 23, 2004 | Z20  | ES9313   | 2 of 43 | В    |

| Table 1: Powers                                                               | . 7  |

|-------------------------------------------------------------------------------|------|

| Table 2: Depleted Battery State                                               |      |

| Table 3: Other Battery Detector Parameters                                    | . 10 |

| Table 4: Hardware VCC Voltage Detector And System Power-Down State            | . 11 |

| Table 5 : Power Backup Calculations                                           | . 12 |

| Table 6: Circuit Power Backup Time Calculation                                | . 14 |

| Table 7: Backup Capacitor, SRAM Backup and Circuit Power Backup               | . 15 |

| Table 8: Up-Converter                                                         | . 17 |

| Table 9: External Interrupts (IRQs)                                           | . 19 |

| Table 10: External SRAM                                                       | . 20 |

| Table 11: Serial EEPROM                                                       | . 20 |

| Table 12: RF Circuit Signals                                                  |      |

| Table 13: I/O Ports                                                           | . 22 |

| Table 14: Key and I/O Bit Assignments                                         | . 24 |

| Table 15: Buzzer Alarm Circuit Parameters                                     | . 24 |

| Table 16: Vibration Motor Circuit Parameters                                  | . 25 |

| Table 17: LCD Circuit Parameters                                              | . 26 |

| Table 18: LCD Initialization Table                                            | . 26 |

| Table 19: EL Circuit Parameters                                               | . 28 |

| Table 20: IrDA Port                                                           | . 28 |

| Table 21: Signals at Test Connector                                           | . 30 |

| Table 22: Process Properties for Implement Design                             | . 33 |

| Table 23: Process Properties for Generate Programming File                    | . 33 |

| Table 24: Hardware Changes as Compared to MMT3150 PPC                         | . 34 |

| Table 25: Hardware Changes Induced Software Changes As Compare to MMT315x PPC |      |

|                                                                               |      |

| Medtronic Sa | ave Date      | Туре | Document | Sheet   | Ver. |

|--------------|---------------|------|----------|---------|------|

| MINIMED      | June 23, 2004 | Z20  | ES9313   | 3 of 43 | В    |

# 1.0 PURPOSE

The purpose of this document is to describe design details of the MMT-3160 Personal Programming Communicator (PPC) board hardware.

# 2.0 SCOPE

This document covers the design of the MMT-3160 PPC electronic hardware.

## 3.0 ASSOCIATED DOCUMENTS

| 3.1 | 9013174 | Schematics, MMT-3160 PPC                                 |

|-----|---------|----------------------------------------------------------|

| 3.2 | 9013175 | Schematics, PLD Circuit, MMT-3160 PPC                    |

| 3.3 | 6053154 | Layout, MMT-3160 PPC                                     |

| 3.4 | ES1160  | Specifications, MMT-3160 PPC Hardware/Software Interface |

| 3.5 | RD1142  | Requirements, MMT-3160 PPC Hardware                      |

| 3.6 | DD1008  | Design Description, Processor IC                         |

# 4.0 DEFINITIONS AND ABBREVIATIONS

| 4.1  | ADC    | Analog to Digital Converter                       |

|------|--------|---------------------------------------------------|

| 4.2  | EEPROM | Electrical Erasable Programmable Read Only Memory |

| 4.3  | IC     | Integrated Circuit                                |

| 4.4  | I/O    | Input/Output                                      |

| 4.5  | IrDA   | Infrared Data Association                         |

| 4.6  | IU     | Implant Unit - An Medtronic MiniMed product       |

| 4.7  | LCD    | Liquid Crystal Display                            |

| 4.8  | PPC    | Personal Programming Communicator                 |

| 4.9  | RAM    | Random Access Memory                              |

| 4.10 | ROM    | Read Only Memory                                  |

| 4.11 | UART   | Universal Asynchronous Receiver Transmitter       |

| 4.12 | EL     | Electro luminescent                               |

| 4.13 | EMI    | Electro-Magnetic Interference                     |

| 4.14 | ESD    | Electro Static Discharge                          |

| 4.15 | PCB    | Printed Circuit Board                             |

| 4.16 | CPLD   | Complex Programmable Logic Device                 |

|      |        |                                                   |

## 5.0 OVERVIEW

- 5.1 The PPC device is used to communicate with Medtronic MiniMed implantable devices such as Implantable Glucose Monitor (IGM) and implantable insulin pumps, collectively called Implant Unit (IU).

- 5.2 The PPC device is to be carried externally by a patient who has an implant unit.

| Medtronic | Save Date     | Туре | Document | Sheet   | Ver. |

|-----------|---------------|------|----------|---------|------|

| MINIMED   | June 23, 2004 | Z20  | ES9313   | 4 of 43 | В    |

- 5.3 The circuit contains an up-converter, external serial ROM (SEEPROM), vibrator for vibrational alarm, piezo for tone alarm, RF circuitry for 131KHz telemetry, processor of the system (Medtronic MiniMed custom Processor IC), external SRAM, power manager, external IO, LCD, EL backlight, UART/IrDA port, keypad connector, interrupt generator and other supporting logic circuitry. Block diagram of the PPC is given in *Figure 1: PPC Block Diagram*

- 5.4 This device is considered an incremental upgrade to the existing MMT-315x PPC. Therefore, it is an intention to make necessary improvements based on the MMT-315x models yet keeping the software changes minimal. For this reason, major circuit design and component selections are carried over from the MMT-315x models where possible.

| Medtronic | Save Date     | Туре | Document | Sheet   | Ver. |

|-----------|---------------|------|----------|---------|------|

| MINIMED   | June 23, 2004 | Z20  | ES9313   | 5 of 43 | В    |

|           |               |      |          |         |      |

# 6.0 DETAILED DESIGN DESCRIPTION

#### 6.1 Power

- 6.1.1 The main source of power to the entire circuit is a single AA battery (the main battery VAABATT). This voltage is up converted to +3.45 V as VCC by a switching type up-converter. VCC is the main operating power for the circuit.

- 6.1.2 A secondary operating power, VPOS, is connected to the system's external SRAM as its supply voltage. As will be discussed more in subsequent sections, VPOS is derived from VCC, backed up by a super cap, and used to power the SRAM in long term memory backup mode and to power the entire circuit when the up-converter is shutdown temporarily in some situations.

- 6.1.3 A 0.1 Farad super capacitor (C5, the backup capacitor or the super cap) is connected to VPOS. When VCC is normally supplied by the up-converter, it charges the super cap and keeps it in the charged state. When the up-converter no long supplies VCC, either due that the up-converter is being temporarily shut down (during RF reception, for example) or due to depleted main battery (including battery removal), the super cap will support both VCC and VPOS until either the VCC voltage goes down to 2.87V or when the processor asserts HCUT\_VCC, whichever comes first. At that time, a switch (Q1) will cut off the connection between VCC and VPOS. From that point on, the super cap will only supply for VPOS to keep the external SRAM powered for as long as the charge in the capacitor will last. See table below for more details.

- 6.1.4 Also counted as a supply voltage is LCD\_VCC. This is the output of a low dropout linear regulator U16. The nominal level is set to 2.87V. This voltage is used to power the LCD module only.

- 6.1.5 The AA battery source is brought in through connector CN5.

- 6.1.6 The AA battery voltage is connected to ADC channel "A" of the processor for voltage monitoring.

- 6.1.7 The VCC voltage is connected to ADC channel "B" internally to the processor IC for voltage monitoring.

- 6.1.8 In selecting the nominally 3.45V VCC voltage and the nominally 2.87V LCD\_VCC voltage, the following are the major considerations.

- 6.1.8.1 VCC should be low voltage for low power operation. Some components selected are of low voltage rated components with the recommended maximum supply voltage of 3.6 V.

- 6.1.8.2 VCC should be high enough to provide adequate working voltage differential so that there is enough stored energy for orderly shutdown after battery removal. Working voltage differential here is the difference between the initial VCC voltage and the final VCC voltage at which low VCC is detected (LVCC\_RESET asserts, at which the circuit is in hardware controlled system power-down state).

- 6.1.8.3 VCC should be high enough to provide adequate working voltage differential so that there is enough stored energy for long-term memory backup. Working voltage differential here is the difference between the initial VPOS voltage entering memory backup mode and the specified minimum external SRAM data retention voltage.

- 6.1.8.4 VCC should be high enough to provide adequate working voltage differential so that there is enough stored energy for circuit backup during the short periods when the up-converter is shut down in RF QUIET mode.

|  | Save Date     | Туре | Document | Sheet   | Ver. |  |

|--|---------------|------|----------|---------|------|--|

|  | June 23, 2004 | Z20  | ES9313   | 6 of 43 | В    |  |

The voltage differential here is the difference between the initial VCC voltage when the up-converter is shut down and the voltage at which LCD\_VCC is out of regulation. When LCD\_VCC is out of regulation, LCD contrast change might be noticeable by the user, which is undesirable.

|  | 6.1.9 | Table 1: Powers shows more details on the powers. |

|--|-------|---------------------------------------------------|

|--|-------|---------------------------------------------------|

|                                | Table 1: Powers                                                                                                                                       |  |  |  |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| VCC voltage (main power)       | 3.45 V, +/-100 mV, supporting a max load of 30 ohm connected to it, with battery voltage of 1.15 V to 1.8 V measured at the input of the up-converter |  |  |  |  |  |

| main power source (AA battery) | One AA battery (nominally 1.5 V), typically alkaline type, lithium AA cell with voltage up to 1.8V acceptable                                         |  |  |  |  |  |

| VPOS voltage (secondary power) | Within 50mV of VCC when VCC is at normal level                                                                                                        |  |  |  |  |  |

| LCD_VCC                        | 2.87 V +/-3%                                                                                                                                          |  |  |  |  |  |

#### 6.2 Power Management

- 6.2.1 The functions of the power management circuit are as followed: a) to provide proper power-up reset; b) to provide backup power for the on-board SRAM; c) to provide interrupt signal to inform the processor when battery is low; d) and to provide adequate time for orderly system shut-down when the main battery is dead or removed.

- 6.2.2 Battery Voltage and VCC Voltage Monitoring By The Processor

- 6.2.2.1 The AA battery voltage, VAABATT, is connected to ADC channel "A" of the processor for voltage monitoring by the processor.

- 6.2.2.2 It is expected that the software will make battery voltage measurements and provide warning of low battery at a voltage level higher than the depleted battery voltage level which will be detected by the hardware. To ensure enough pre-warning of low battery conditions, it is expected that the measurements would be done under load, using dummy load R30.

- 6.2.2.3 The dummy load is a 100 ohm load connected to VCC for a typical load current of 34.5 mA from VCC. Because of the high load, for battery life consideration, it is not recommended that this load is used often. Battery voltage measurement of once per day under this load is recommended.

- 6.2.2.4 The VCC voltage is connected to ADC channel "B" internally to the processor IC for voltage monitoring by the processor.

- 6.2.2.5 ADC channel "C" was used in MMT315x models to measure the backup coin battery voltage. Coin battery is not used in this circuit. This channel is now connected to VCC so that MMT315x model software can run on this hardware without changing with respect to this item.

- 6.2.2.6 VCC is a regulated voltage of nominally 3.45 V. If this voltage is out of range, it might be caused by the following: a) the battery voltage is too low, typically below 0.9V; b) the up-converter circuit has problem; c) the entire circuit is taking too much power (typically greater than 60mA at 3.45 V, this current is also battery condition dependent).

|  | Save Date Type I |     | Document | Sheet   | Ver. |

|--|------------------|-----|----------|---------|------|

|  | June 23, 2004    | Z20 | ES9313   | 7 of 43 | В    |

6.2.2.7 VCC can be measured periodically, but not necessarily under load, for the purpose of detecting faulty conditions. It should be noted that this measurement should not be relied upon for battery voltage tracking. This is because when VCC is too low, most likely the battery is already deeply depleted. It should be enough to rely on the hardware VCC voltage detection for power management purposes.

#### 6.2.3 Hardware Battery Voltage Detector And Depleted Battery State

- 6.2.3.1 A battery voltage detector is implemented with U7, R4, R5, R6 and C76. The output signal is named LRESET (low asserted). The designed detection threshold is 1.0 V on battery voltage falling and 1.16 V on voltage rising. At 1.0 V battery voltage, VCC is still in the normal level of 3.45 V, but the battery cannot support heavy loads. When the battery gets close to this level, activating high load activities such as turning on the vibrator would most likely cause the battery voltage to dip below this threshold level, which will trigger a hardware low battery shutdown, but with enough time provided for orderly shutdown. For this reason, it is expected that the software would do regular battery voltage measurements and issue low battery warning at a higher level so that enough warning is provided before this state.

- 6.2.3.2 U7 is a voltage comparator (MAX837EUS, Maxim). The internal threshold is typically 1.204V +/-1%. In order to have the detection battery voltage threshold of 1.0 V, which is lower than the internal threshold, VCC is used as the reference point instead of the normally used system ground.

- 6.2.3.3 R6 is used to provide hysteresis. In the event of battery voltage rising (battery insertion, for example), the detection threshold is determined by the facts that R4 connects to VAABATT (battery voltage), R5 connects to VCC and R6 connects to GND (because LRESET is asserted at that point). In the event of battery voltage falling (battery natural depletion or battery removal), the detection threshold is determined by the facts that R4 connects to VAABATT (battery voltage), R5 connects to the facts that R4 connects to VAABATT (battery voltage), R5 connects to VCC and R6 also connects to VCC (because LRESET is de-asserted at that point). This way, the circuit will only starts operating (when LRESET de-asserts) when the battery voltage is high and VCC is up to the normal level in battery insertion event; and the circuit will only stops operating as the battery drops really low. See Table 3: Other Battery Detector Parameters for more details.

- 6.2.3.4 This hysteresis also ensures that LRESET is clean of glitches as the battery voltage rises and falls.

- 6.2.3.5 Because of the hysteresis, when a battery is inserted, or when the battery has gradually depleted, the circuit might be in a state such that the upconverter is fully operational, but the system is locked from powering up due to the assertion of LRESET. The voltage at which the circuit is allowed to start normal operation is the rising battery voltage threshold. This design prevents an oscillation condition that when a very weak battery is inserted, the system starts to boot up, then higher power demand from the very weak battery causes a rapid battery voltage drop, causing LRESET to be asserted, the system is then put back to power-down state.

- 6.2.3.6 HRESET, the inverted state of LRESET, is used as a power-fail interrupt signal to the processor. This interrupt signal is fed directly to the HIRQ\_INPUT2 input of the processor. The software is expected to

|  | Save Date Type |     | Document | Sheet   | Ver. |  |

|--|----------------|-----|----------|---------|------|--|

|  | June 23, 2004  | Z20 | ES9313   | 8 of 43 | В    |  |

perform orderly shutdown when it receives this interrupt. In this design, because the use of the super cap, the time for the software to perform orderly shutdown is ample. However, it is expected that the software will perform that orderly shutdown timely so that more energy stored in the super cap will be used for long-term backup of the external SRAM.

- 6.2.3.7 In order to save more energy for long-term SRAM backup, the software is expected to perform timely orderly shutdown, then asserts the signal LCUT\_VCC (I/O port 0x02, bit 2). The assertion of LCUT\_VCC disconnects VPOS from VCC in a uni-directional fashion, meaning current can go from VCC to VPOS (if VCC is still high) but not the other way around. The connecting PFET gate, Q1, is turned off when LCUT\_VCC is asserted, but the intrinsic diode in the PFET would still conduct in the VCC to VPOS direction (with a diode drop in voltage). In the battery removal case, VCC will drop very rapidly when LCUT\_VCC is asserted, but the VPOS voltage level will stay. In the case when battery depletes gradually, low VAABATT will cause the assertion of LRESET, which should trigger orderly shutdown. In turn, it will lead to the assertion (software controlled) of LCUT VCC and the turning off of Q1. At that time, VCC might still be at normal level because that the up-converter can operate down to 0.9 V of VAABATT, so VCC is still supplying VPOS with PFET diode conduction.

- 6.2.3.8 After orderly shutdown, the software is expected to check the state of LRESET by reading the corresponding I/O bit periodically. It should not attempt to resume normal operation as long as LRESET is asserted. This is because while the initial assertion of LRESET causes an interrupt to the processor, the asserted level would not prevent the processor from attempting to resume normal operation, even though the attempt would not be successful because the lock-out of the devices as listed in Table 2: Depleted Battery State by the asserted LRESET.

- 6.2.3.9 LRESET is connected to input port 0x00, bit 6 for software reading.

- 6.2.3.10 When LRESET is asserted, it immediately disables the output ports, which in turn shuts down all high power devices. This is to save more energy in the super cap for orderly shutdown and SRAM backup. Refer to *Table 2: Depleted Battery State* for more information.

#### Table 2: Depleted Battery State

Key press no longer generates key board interrupt to the processor

5-key reset no longer works

UART disabled, IrDA module shut down

The output ports, 0x02 and 0x04, are cleared

LCD is held in un-selected and reset state

Backlight is disabled

Vibrator is disabled

The 100-ohm dummy load is disabled

|  | Save Date Type |     | Document | Sheet   | Ver. |  |

|--|----------------|-----|----------|---------|------|--|

|  | June 23, 2004  | Z20 | ES9313   | 9 of 43 | В    |  |

|  |                |     |          |         |      |  |

| Table 3: Other Batter                             | y Detector Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Battery voltage falling detection threshold       | 1.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Battery voltage rising detection threshold        | 1.16 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Time between battery removal and LRESET assertion | Approximately 20 microseconds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| When LRESET is asserted:                          | See table above                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Major design considerations                       | <ul> <li>Static power consumption</li> <li>Voltage detection threshold: on rising, high enough<br/>so the circuit would only be allowed to operate when<br/>VCC is good and stable; on falling, low enough so the<br/>battery energy would be fully utilized, but high enough<br/>so power would be available for orderly shutdown<br/>(especially high enough so that in any situation,<br/>orderly shutdown can be completed before hardware<br/>controlled low VCC system power-down would<br/>happen)</li> <li>Immunity to noise, especially due to ESD events</li> <li>Hysteresis – to avoid oscillation condition due to<br/>battery voltage fluctuation</li> </ul> |

| Major components                                  | <ul> <li>U7 – Chosen because of low static power<br/>consumption, push-pull output, small package.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

- 6.2.4 Hardware VCC Voltage Detector And System Power-down State

- 6.2.4.1 The VCC voltage detector is comprised of U16, R47, R48, C80 and C75.

- 6.2.4.2 U16 is an integrated micro-power voltage regulator and voltage detector. U16, in conjunction with R47 and R48, sets the output voltage, LCD\_VCC, as well as the threshold for the LVCC\_RESET signal.

- 6.2.4.3 The output voltage, LCD\_VCC, is set to:

Voutput = 1.23(1+R47/R48) = 1.23(1+365K/274K) = 2.87 V, +/-3%

- 6.2.4.4 C80 is a low ESR capacitor needed by U16. C75 provides noise immunity of LVCC\_RESET, especially in the event of ESD. For enhanced noise immunity, U16 is well decoupled with a 0.1 uF VCC bypass capacitor placed very close to its VCC pin.

- 6.2.4.5 This detector detects low VCC voltage level. The threshold is set to:

Vth = 0.925(Vout) = 0.925 X 2.87 = 2.65 V (typ) Vth = 0.965(Vout) = 0.965 x 2.87 x (1+3%) = 2.85 V (max) Vth = 0.885(Vout) = 0.885 x 2.87 x (1-3%) = 2.46 V (min)

6.2.4.6 The output of this detector is LVCC\_RESET.

|  | Save Date Type |     | Document | Sheet    | Ver. |  |

|--|----------------|-----|----------|----------|------|--|

|  | June 23, 2004  | Z20 | ES9313   | 10 of 43 | В    |  |

- 6.2.4.7 When VCC falls below the set threshold, LVCC\_RESET is asserted. The assertion of this signal disables essentially the entire circuit, with the exception of the processor oscillator. However, the processor is not operational because this signal also holds the processor in reset state by setting HEXTRESET high.

- 6.2.4.8 In addition, the assertion of this signal disables the accessing of the external SRAM for the purpose of preventing the corruption of the SRAM content by uncontrolled address and data line state changes due to out of spec VCC level.

- 6.2.4.9 This signal also turns off the VCC to VPOS gate, Q1, if this has not be done so by the processor setting LCUT\_VCC. This is the latest time for the circuit to enter memory backup mode. The earlier time would be when the software asserts LCUT\_VCC after orderly shutdown.

- 6.2.4.10 When VCC falls below this threshold, it means that the battery has depleted to a level that it cannot produce a regulated VCC. At this point, it is assumed that the system has been in low battery shutdown state because low battery (LRESET asserted) should have been detected before this point.

| VCC voltage detector output signal       | LVCC_RESET                                                                                                                                                                                                 |  |  |  |  |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| VCC voltage detection threshold          | 2.85 V (max)                                                                                                                                                                                               |  |  |  |  |

|                                          | 2.65 V (typ)                                                                                                                                                                                               |  |  |  |  |

|                                          | 2.46 V (min)                                                                                                                                                                                               |  |  |  |  |

| When LVCC_RESET asserted:                | <ul> <li>External SRAM, U9, cannot be accessed; SRAM I/O line<br/>tri-stated</li> </ul>                                                                                                                    |  |  |  |  |

|                                          | <ul> <li>Q1 turned off to preserve VPOS power</li> </ul>                                                                                                                                                   |  |  |  |  |

|                                          | <ul> <li>HEXTRESET is set to static high so processor is held in</li> </ul>                                                                                                                                |  |  |  |  |

|                                          | reset (note that the processor will not operation until this signal is low, or called released from reset state)                                                                                           |  |  |  |  |

| Major design considerations              | Static power consumption                                                                                                                                                                                   |  |  |  |  |

|                                          | <ul> <li>Low dropout voltage regulation</li> </ul>                                                                                                                                                         |  |  |  |  |

|                                          | <ul> <li>Linear voltage regulator output (LCD_VCC): VCC voltage<br/>detection threshold follows this setting</li> </ul>                                                                                    |  |  |  |  |

|                                          | <ul> <li>LCD_VCC has to be capable of powering the LCD<br/>module</li> </ul>                                                                                                                               |  |  |  |  |

|                                          | <ul> <li>VCC voltage detection threshold: high enough so VPOS<br/>can backup the SRAM for the specified duration, low<br/>enough so VCC fluctuation would not cause premature<br/>circuit reset</li> </ul> |  |  |  |  |

|                                          | <ul> <li>Immunity to noise in the event of ESD (because the<br/>output signal, LVCC_RESET, affects the entire circuit<br/>operation)</li> </ul>                                                            |  |  |  |  |

| Major component selection considerations | <ul> <li>U16 – Max6349TLUT: This part was chosen mainly for i<br/>low static state power and the fact that it has a built-in</li> </ul>                                                                    |  |  |  |  |

|                                          | voltage detector. This part is to be active all the time so                                                                                                                                                |  |  |  |  |

|                                          | power consumption is a major consideration. This part has                                                                                                                                                  |  |  |  |  |

|                                          | a pre-programmed output voltage, but this is                                                                                                                                                               |  |  |  |  |

|  | Save Date Type |     | Document | Sheet    | Ver. |  |

|--|----------------|-----|----------|----------|------|--|

|  | June 23, 2004  | Z20 | ES9313   | 11 of 43 | В    |  |

| Table 4: Hardware VCC Voltage Detector And System Power-Down State |                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| VCC voltage detector output signal                                 | LVCC_RESET                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                                                                    | over-ridden by the use of the output voltage setting resistor<br>divider. Lower than the pre-programmed output and<br>detection voltage is desired here. Availability was a factor<br>in selecting this part over other parts in the same family.<br>Push-pull detector output wins over open-drain output to<br>save a pull-up resistor. Low dropout is a must. The<br>100mA+ output has no problem of powering the LCD<br>module. |  |  |  |  |

- 6.2.5 Backup Capacitor, Memory Backup and Circuit Power Backup

- 6.2.5.1 Memory Backup and Circuit Power Backup are implemented with components C5, Q1 and U10. SP1 is for test purposes.

- 6.2.5.2 A double layer capacitor (super cap), C5, is used as a power backup cell, which supplies VPOS. This source is used to power the external memory in memory backup mode, when the AA battery is absent (depleted or removed) and is used to power the entire circuit when the up-converter is temporarily turned off during RF QUIET mode.

- 6.2.5.3 The time in RF QUIET mode when the up-converter is shut down, and the super cap is powering the entire circuit is referred to as the circuit power backup mode, or simply circuit backup mode.

- 6.2.5.4 RF QUIET mode is enabled by setting bit 4 of VO port 0x04.

- 6.2.5.5 Q1 connects VCC and VPOS. During normal circuit operation, Q1 is turned on so VCC charges the super cap as well as supplying VPOS.

- 6.2.5.6 When VCC falls below the low VCC threshold (assertion of LVCC\_RESET), or when the processor asserts LCUT\_VCC, Q1 is turned off. The connection is cut in the direction of VPOS to VCC, but the direction of VCC to VPOS is still somewhat open by the diode conduction in the PFET.

- 6.2.5.7 In RF QUIET mode, when the up-converter is shut down by the action of turning on the RF receiver, the software must not assert LCUT\_VCC. Doing so will cause a total loss of VCC power.

- 6.2.5.8 Memory backup duration is required to be a minimum of 1 hour. Actual memory backup duration is calculated as follows:

|                                                  | Table 5 : Power Backup Calculations |                           |                                   |                              |                           |                         |                                            |                                     |  |  |

|--------------------------------------------------|-------------------------------------|---------------------------|-----------------------------------|------------------------------|---------------------------|-------------------------|--------------------------------------------|-------------------------------------|--|--|

| Memory backup time with NEC SuperCap, 0.1F, 5.5V |                                     |                           | Γ                                 |                              |                           |                         |                                            |                                     |  |  |

| SuperCap Use as                                  | s Memory Backup                     |                           |                                   |                              |                           |                         |                                            |                                     |  |  |

| nominal<br>capacitance (F)                       | capacitance<br>change factor (%)    | actual<br>capacitance (F) | starting<br>backup<br>voltage (V) | ending backup<br>voltage (V) | net backup<br>voltage (V) | total charge Q (<br>C ) | averaged<br>power<br>consumption I<br>(uA) | calculated<br>backup time<br>(hour) |  |  |

| Fs                                               |                                     | Fa                        | Vi                                | Vf                           | Vn                        | С                       | I                                          | t                                   |  |  |

|  | Save Date     | Туре | Document | Sheet    | Ver. |

|--|---------------|------|----------|----------|------|

|  | June 23, 2004 | Z20  | ES9313   | 12 of 43 | В    |

|                                             |                  | Tab                 | le 5 : Po | ower Backu | p Calculation | S           |   |                          |

|---------------------------------------------|------------------|---------------------|-----------|------------|---------------|-------------|---|--------------------------|

| Memory backup                               | time with NEC Su | ıperCap, 0.1F, 5.5V |           |            |               |             |   |                          |

|                                             |                  |                     |           |            |               |             |   |                          |

| SuperCap Use a                              | s Memory Backup  | )                   |           |            |               |             |   |                          |

|                                             | % of spec value  | (spec value) x (%)  |           |            | (Vi - Vf)     | (Fa) x (Vn) |   | ((C*1000000)/I)/<br>3600 |

| based on initial<br>cap value               |                  |                     |           |            |               |             |   |                          |

| 0.1                                         | -20              | 0.08                | 3.45      | 1.8        | 1.65          | 0.132       | 1 | 36.7                     |

| 0.1                                         | -20              | 0.08                | 3.45      | 1.8        | 1.65          | 0.132       | 5 | 7.3                      |

| 0.1                                         | -20              | 0.08                | 3.3       | 1.8        | 1.5           | 0.12        | 1 | 33.3                     |

| 0.1                                         | -20              | 0.08                | 3.3       | 1.8        | 1.5           | 0.12        | 5 | 6.7                      |

| 0.1                                         | -20              | 0.08                | 3         | 1.8        | 1.2           | 0.096       | 1 | 26.7                     |

| 0.1                                         | -20              | 0.08                | 3         | 1.8        | 1.2           | 0.096       | 5 | 5.3                      |

| worst case in cap<br>value based on<br>spec |                  |                     |           |            |               |             |   |                          |

| 0.1                                         | -50              | 0.05                | 3.45      | 1.8        | 1.65          | 0.0825      | 1 | 22.9                     |

| 0.1                                         | -50              | 0.05                | 3.45      | 1.8        | 1.65          | 0.0825      | 5 | 4.6                      |

| 0.1                                         | -50              | 0.05                | 3.3       | 1.8        | 1.5           | 0.075       | 1 | 20.8                     |

| 0.1                                         | -50              | 0.05                | 3.3       | 1.8        | 1.5           | 0.075       | 5 | 4.2                      |

| 0.1                                         | -50              | 0.05                | 3         | 1.8        | 1.2           | 0.06        | 1 | 16.7                     |

| 0.1                                         | -50              | 0.05                | 3         | 1.8        | 1.2           | 0.06        | 5 | 3.3                      |

| lower memory<br>data retention<br>voltage   |                  |                     |           |            |               |             |   |                          |

| 0.1                                         | -50              | 0.05                | 3.45      | 1.3        | 2.15          | 0.1075      | 1 | 29.9                     |

| 0.1                                         | -50              | 0.05                | 3.45      | 1.3        | 2.15          | 0.1075      | 5 | 6.0                      |

| 0.1                                         | -50              | 0.05                | 3.3       | 1.3        | 2             | 0.1         | 1 | 27.8                     |

| 0.1                                         | -50              | 0.05                | 3.3       | 1.3        | 2             | 0.1         | 5 | 5.6                      |

| 0.1                                         | -50              | 0.05                | 3         | 1.3        | 1.7           | 0.085       | 1 | 23.6                     |

| 0.1                                         | -50              | 0.05                | 3         | 1.3        | 1.7           | 0.085       | 5 | 4.7                      |

- 6.2.5.9 This super cap also serves the purpose of lessening the burden on the upconverter and the battery in supporting short high power bursts.

- 6.2.5.10 Another function, as discussed earlier, of the super cap is providing the time for orderly shutdown at battery removal.

- 6.2.5.11 High power devices such as the vibrator and the backlight, are disabled by hardware in circuit backup mode, when the up-converter is shutdown.

- The high power dummy load has higher priority RF QUIET mode. This 6.2.5.12 means that if the dummy load is turned on, the up-converter is inhibited from shutting down for that duration.

- 6.2.5.13 All hardware disabled devices, including the up-converter, during circuit backup mode would automatically be enabled, without affecting the software set states, once RF receive becomes inactive.

|  | Save Date     | Туре | Document | Sheet    | Ver. |

|--|---------------|------|----------|----------|------|

|  | June 23, 2004 | Z20  | ES9313   | 13 of 43 | В    |

- 6.2.5.14 The software is expected not to perform other tasks, which could result in the consumption of higher than available total charge as specified in Table 5 : Power Backup Calculations, during circuit power mode. Consumption in term of charge is calculated by Q=I \* t.

- 6.2.5.15 The software is expected to de-assert LCUT\_VCC during normal operation, only to be asserted after orderly shutdown.

- 6.2.5.16 The solder pad, SP1, and signal SUPERCAP are provided for ATS testing. In board level testing, SP1 is to be left open so the super cap can be tested by the ATS through the use of the signal SUPERCAP, which is brought to the board-edge connector. After testing, SP1 is to be shorted with solder. It is designed this way because in board level testing, circuit power consumption tests might have to deal with sub-milliamp current measurements. Having a super cap connected in the circuit would make such test difficult because of the relatively long super cap charging period. Isolating the super cap also makes the testing of the super cap itself easier.

- 6.2.5.17 Circuit power backup calculation is as shown in Table 7: Backup Capacitor, SRAM Backup and Circuit Power Backup.

|                                                       | Table 6: Circuit Power Backup Time Calculation |                              |                                   |                                 |             |                         |                                            |                                          |  |

|-------------------------------------------------------|------------------------------------------------|------------------------------|-----------------------------------|---------------------------------|-------------|-------------------------|--------------------------------------------|------------------------------------------|--|

|                                                       |                                                | SuperCap l                   | Jse as Pow                        | er Source D                     | uring RF Re | ceive                   |                                            |                                          |  |

| nominal<br>capacitance<br>(F)                         | capacitance<br>change factor<br>(%)            | actual<br>capacitance<br>(F) | starting<br>backup<br>voltage (V) | ending<br>backup<br>voltage (V) |             | total charge<br>Q ( C ) | averaged<br>power<br>consumption<br>I (uA) | calculated<br>backup<br>time<br>(second) |  |

| based on<br>initial cap<br>value                      |                                                |                              |                                   |                                 |             |                         |                                            |                                          |  |

| 0.1<br>worst case in<br>cap value<br>based on<br>spec | -20                                            | 0.08                         | 3.45                              | 3                               | 0.45        | 0.036                   | 1000                                       | 36                                       |  |

| 0.1                                                   | -50                                            | 0.05                         | 3.45                              | 3                               | 0.45        | 0.0225                  | 1000                                       | 22.5                                     |  |

| Medtronic | Save Date     | Туре | Document | Sheet    | Ver. |

|-----------|---------------|------|----------|----------|------|

| MINIMED   | June 23, 2004 | Z20  | ES9313   | 14 of 43 | В    |

|           |               |      |          |          |      |

| Table 7: Backup Capacitor, SRA                                                                                   | Table 7: Backup Capacitor, SRAM Backup and Circuit Power Backup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Super cap                                                                                                        | 0.1 F (nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| VCC cannot drop below this voltage in circuit power<br>backup mode to avoid noticeable change in LCD<br>contrast | 2.95 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| SRAM data retention voltage                                                                                      | 1.8V minimum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| In circuit power backup mode:                                                                                    | <ul> <li>RF RX on</li> <li>Up-converter shut down</li> <li>Vibrator disabled</li> <li>Backlight disabled</li> <li>Dummy load on would disable this mode for the duration</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Major design considerations                                                                                      | <ul> <li>The backup power has to be able to backup SRAM for a minimum of 1 hour.</li> <li>The backup power has to be able to support circuit operation for a minimum of 1.5 seconds during circuit power backup mode. In this backup mode, VCC cannot drop below 2.95 V to avoid noticeable change in LCD contrast. In other words, LCD_VCC should not be out of regulation.</li> <li>No coin cell because of higher cost, bigger size and it is perishable.</li> <li>No lithium rechargeable coin cell because the size of such would be too big for one that can support the operation of the circuit. Such design would need more parts too.</li> <li>The PFET gate must have low Ron to minimize VCC drop during circuit power backup.</li> <li>Long-term reliability. Have to use high design margins.</li> <li>U10 was not integrated into the CPLD because this part has to be powered by VPOS, and this is because the PFET Q1 has to be turned off (need a high voltage level to do that) when VCC is gone.</li> </ul> |  |  |  |  |  |

| Major component selection considerations                                                                         | <ul> <li>NEC super cap, 0.1F, C5: This part was selected because NEC is reputable in quality. Manufacturer test data show long-term reliability. This part is a desirable surface-mount part, designed for auto pick-n-place and regular reflow process. Cheap in price. Good availability. Low ESR. 5.5V rated. Essentially no limit on charging current and charging cycle. Another major factor is this part meets the 5.5 mm max height requirement (height restriction because of spacing between PC board and back cover).</li> <li>ZETEX ZXM61P02 PFET, Q1: Small package, low Ron.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|  | Save Date     | Туре | Document | Sheet    | Ver. |

|--|---------------|------|----------|----------|------|

|  | June 23, 2004 | Z20  | ES9313   | 15 of 43 | В    |

- 6.3 Up-converter

- 6.3.1 The up-converter is constructed around a switching controller, U24, Linear Technology LT1307, with switching coil, L6, and diode D2. Feedback is provided by R31 and R32. Input and output filtering is provided by C72, C68, C73 and C61. Loop control is by R33 and C63. Shutdown is controlled by LUC\_SHDN from the CPLD, with pull-up RP1G.

- 6.3.2 The up-converter up converts the voltage of the single AA battery (nominally 1.5 V) to a nominal voltage of 3.45 V.

- 6.3.3 The output voltage of the up-converter is set by selecting the resistance ratio of R58 and R60. The formula is:

Vout=1.22(1+R58/R60) V.

- 6.3.4 This is a switching type up-converter. The switching frequency is between 550 kHz and 750 kHz, nominally 600 kHz. However, under light load, the up-converter utilizes burst mode, resulting a wide noise spectrum.

- 6.3.5 For best RF performance, during RF reception, it is expected that the software will set the RF QUIET mode, in that, the up-converter is shutdown during the RF receive windows.

- 6.3.6 During RF transmit, the transmit current is high enough to put the up-converter in the fixed 600KHz switching frequency mode (instead of burst mode), resulting low harmonic noise at 131KHz (the RF center primary frequency).

- 6.3.7 Minimum start-up voltage of this up-converter is guaranteed to be no greater than 1.00 V (0.92 V typical) with starting load of no more than 100 ohm load at the output.

- 6.3.8 Typical efficiency of this up-converter is 70% to 80%, depending on load and input voltage.

- 6.3.9 This up-converter switching controller can tolerate reversed battery input voltage up to 1.8V. Furthermore, because of the external switching diode, the rest of the circuit would experience no negative current flow when the reversed battery voltage is applied. This provides protection against accidental reversed battery insertion.

- 6.3.10 Shutdown of the up-converter is controlled by the LUC\_SHDN signal from the CPLD, with the 10Kohm pull-up. LUC\_SHDN is the combined result of RF QUIET mode bit and RF RX state.

- 6.3.11 For proper start-up, the output of LUC\_SHDN must be tri-stated before VCC gets to the operating level, and defaults to high level once VCC gets to that operating level. At start-up, LUC\_SHDN needs to be tri-stated because the /SHDN pin of the switching controller needs to be at or above Vin in order to operate. As battery is inserted, VCC follows Vin, and if the LUC\_SHDN output is tri-stated, because of the 10K pull-up, the /SHDN pin will follow VCC (which follows Vin). As Vin reaches the startup voltage, the up-converter starts to operate and produce VCC.

- 6.3.12 This design takes advantage of the high impedance nature of CPLD outputs (the Xilinx CPLD selected) at low voltage for the purpose of saving parts.

| Ver. | Sheet    | Document | Туре | Save Date     |         |

|------|----------|----------|------|---------------|---------|

| 43 B | 16 of 43 | ES9313   | Z20  | June 23, 2004 |         |

| 43   | 16 of 43 | ES9313   | Z20  | June 23, 2004 | MINIMED |

| -                                        | Table 8: Up-Converter                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Input voltage (VAABATT)                  | AA battery                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Output voltage (VCC) and load regulation | 3.45 V nominal, 3.35 to 3.6 V range<br>input <sup>1</sup> of 1.15 minimum, load up to 30 ohm at VCC: VCC = 3.35<br>to 3.60 V<br>input of 1.10 minimum, load up to 30 ohm at VCC: VCC = 3.30<br>to 3.60 V<br>input of 1.00 minimum, load up to 100 ohm at VCC: VCC = 3.35<br>to 3.60 V                                                                                                    |  |  |  |  |  |

| Туре                                     | Current mode PWM                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Switching frequency                      | 600KHz nominal, 550KHz to 750KHz range                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Minimum start-up input voltage           | 1.0 V max with start-up load of no more than 100 ohm at VCC                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| output ripple                            | less than 80 mVpp                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Major design considerations              | <ul> <li>Low startup voltage</li> <li>Can support a minimum of 110mA at 3.45V, with input of 1.15V and up</li> <li>Reversed battery insertion protection</li> <li>High efficiency</li> <li>Has shutdown capability</li> <li>Noise consideration</li> <li>Can handle the worst start up conditions: with a totally discharged 0.1F super cap, battery voltage as low as 1.15 V</li> </ul> |  |  |  |  |  |

| Major component selection considerations | <ul> <li>Linear Technology LT1307, switching controller, U24: This part was selected because it meets the major requirements quite well.</li> <li>CoilCraft DO1608C inductor, 10uH, L6: Low profile, small SMD package, high rated current, low cost.</li> <li>Motorolla MBR0530 power diode: High current, high voltage, small SMD package.</li> </ul>                                  |  |  |  |  |  |

# 6.4 Processor

| 6.4.1 | A Medtronic MiniMed custom processor is used as the system processor. This      |

|-------|---------------------------------------------------------------------------------|

|       | Processor IC, U8, incorporates an low power 8086 processor core and much custom |

|       | support logics, including ADC, RF module, sensor module and pump module.        |

- 6.4.2 Refer to DD1008 for details of the Processor IC.

- 6.5 PLD

- 6.5.1 A Xilinx Complex Programmable Logic Device (cPLD), U27, is used to integrate all integratable support logics. The integration reduces part count, thus lowers cost and required board space. This also enhances manufacturability and product reliability.

- 6.5.2 This is a low power, low voltage in-circuit re-programmable device.

<sup>1</sup> Voltage measured at the input of the up-converter, not at the battery.

|  | Save Date     | Туре | Document | Sheet    | Ver. |

|--|---------------|------|----------|----------|------|

|  | June 23, 2004 | Z20  | ES9313   | 17 of 43 | В    |

|  |               |      |          |          |      |

6.5.3 A 100-pin flat-pack package is selected, over a smaller super fine pitch BGA package, because this package eases up the requirement on the layout tool and leads to the reduction in PC board fabrication cost.

#### 6.6 Clock

- 6.6.1 The system clock is generated by the on-chip (Processor IC) oscillator in conjunction with an external 1.049100 MHz, +/-525 Hz (+/-500 PPM) crystal, XTAL1.

- 6.6.2 The clock frequency is 1.049100 MHz, +/-525 Hz (+/-500 PPM). This clock supports the 131KHz RF frequency.

- 6.6.3 The accuracy and drift of the clock is important in this design because the system design requires that this device is to be in sync with the companion implant unit for telemetry communication.

- 6.6.4 To keep this device and the implant unit in sync even with the allowable clock tolerance of +/-525 Hz, the clock stealer function of the processor should be used by the software design.

- 6.6.5 Even with the tight clock tolerance and the use of clock stealer in the processor, significant time drift may still exist between the two devices, depending on the elapsed time between telemetry communications. Software will deal with the expected time drift.

- 6.6.6 The crystal, XTAL1, Micro Crystal CC4V-T2, was selected for its availability in the selected frequency, tight tolerance, low drift and small package. This exact crystal is also used in the companion implant units, again, for minimum relative time drift.

#### 6.7 Reset

- 6.7.1 The Processor IC, U8, can be reset by one of several ways: (a) 5-key reset (KEYRESET). (b) Watchdog reset (HWDRESET). (c) Power-on reset (LVCC\_RESET).

- 6.7.2 The reset of the processor is initiated by a logic high signal to its HEXTRESET pin. The reset is level sensitive, meaning a high level will hold it in reset and a subsequent low level will release it from the reset.

- 6.7.3 The 5-key reset is generated whenever all five keys on the keypad are pressed simultaneously. Logics in the PLD generate a high HEXTRESET level as long as all five keys are being pressed.

- 6.7.4 The watchdog reset is generated when the processor does not service the watchdog timer in a timely manner. The watchdog reset signal from the processor is OR'ed with the other reset signals inside the PLD and outputs as HEXTRESET.

- 6.7.5 The power-on reset signal, LVCC\_RESET, is generated by the VCC level detector U16. This signal is also OR'ed with the other reset signals inside the PLD and outputs as HEXTRESET.

- 6.7.6 It should be noted that HEXTRESET does not affect the content of the external SRAM.

- 6.7.7 R1 is used on the HEXTRESET line to isolate the output from the PLD so production ATS can reset the board (device-under-test). C70 is used for noise immunity purpose, especially for ESD induced noise.

#### 6.8 External Interrupts

6.8.1 There are three external interrupts to the processor: key interrupt, power interrupt and UART interrupt.

| Medtronic | Save Date     | Туре | Document | Sheet    | Ver. |

|-----------|---------------|------|----------|----------|------|

| MINIMED   | June 23, 2004 | Z20  | ES9313   | 18 of 43 | В    |

- 6.8.2 The key interrupt is generated by any key press and is fed to the HIRQ\_INPUT1 input of the Processor IC.

- 6.8.3 The power interrupt is generated by the AA-battery voltage detector, U7, with the signal named HRESET (inverted signal of LRESET). This signal is fed to the HIRQ\_INPUT2 input of the Processor IC.

- 6.8.4 The UART interrupt is generated by the UART chip, U22. This interrupt signal is fed to the HIRQ\_INPUT3 input of the Processor IC. A UART interrupt is generated on serial communication events such as data received, transmission buffer empty, etc.

| Table 9: External Interrupts (IRQs)                   |                            |             |  |  |  |  |

|-------------------------------------------------------|----------------------------|-------------|--|--|--|--|

| Processor Input Function and Signal Name Active Level |                            |             |  |  |  |  |

| HIRQ_INPUT1                                           | key interrupt (HIRQ_KBD)   | active high |  |  |  |  |

| HIRQ_INPUT2                                           | power interrupt (HRESET)   | active high |  |  |  |  |

| HIRQ_INPUT3                                           | UART interrupt (HIRQ_UART) | active high |  |  |  |  |

#### 6.9 External RAM

- 6.9.1 An 8-Mbit, 512K x 16 bit, low power SRAM chip, U9 is provided as the external SRAM memory for the system.

- 6.9.2 The memory can be accessed either byte-wide or word-wide, controlled by LXRAMLO and LXRAMHI from the processor.

- 6.9.3 Memory access is further controlled by signal LVCC\_RESET. When LVCC\_RESET is asserted, memory access is denied. This is designed to prevent memory access during unstable VCC periods and to tri-state the memory chip outputs so they are not driving low impedance inputs when VCC is absent in backup mode.

- 6.9.4 These memory chip is powered by power signal VPOS. This power is derived from VCC as it is available and from the super cap when VCC is not available in backup mode.

- 6.9.5 Address lines used are A1 to A17 and HPUMP\_FIRE (function as bank switch line) from the Processor. HXRAM\_A18 and HXRAM\_CS are derived from LXRAM1 and LXRAM2 from the processor. This is needed because the processor was originally designed to access two lower density SRAM chips.