## CIRCUIT DESCRIPTION

### GENERAL INFORMATION

The SVC99L has three printed circuit boards; CPU board, Radio Frequency(RF)board, Audio Frequency (SUB)board. The CPU board contains the Microprocessor/Control section. The RF board contains the VCO/ Synthesizer section, Transmitter section and Receiver section. The SUB board contains the Transmitter Audio circuitry and the Receiver Audio circuitry.

Circuitry is described in the following order: Microprocessor/Control Section, VCO/Synthesizer Section, Transmitter Section , Receiver Section and Battery Section. Refer to the Block Diagram and the Schematics.

### MICROPROCESSOR/CONTROL SECTION

The microprocessor **0105** is constantly operating when the radio is turned ON. It is continuously monitoring the channel selector switch, The PTT line and other internal inputs such as the squelch detect, etc. When a change occurs, the microprocessor makes the appropriate response. The microprocessor is used for control, The Radio emits a beep on channel change and the synthesizer is loaded with the correct frequency information. The microprocessor runs off a 4.19 MHz oscillator which is composed of **X1 01**, **Cl 27**, **Cl 28**, and **RL 28**.

When the radio is first turned on, the microprocessor reads the radio status from the EEPROM **0104**. The microprocessor determines the receive frequency codes, then loads the synthesizer via its pins 17, 19 and 42.

### VCO/SYNTHESIZER SECTION

This section consists of the Temperature-Compensated Crystal Oscillator (TCXO), Voltage Controlled Oscillator(VCO), Synthesizer and the Loop Filter. These circuits are found on the RF board.

Temperature Compensated Crystal Oscillator (TCXO) The reference oscillator is a temperature compensated crystal-controlled, Pierce type circuit. It utilizes a logic gate within **Q402** as a gain element. **C407** is used to adjust the oscillator on frequency (6.4MHz) at room temperature (22°C). Temperature variations cause resistance changes in thermistor **R410**, which is on the base of **Q404**, thus varying the voltage applied to varactor **Q403**. This changes the impedance across crystal **X401** in a manner complementary to the temperature drift characteristic of the crystal. In this way, the reference oscillator is held within the specified  $\pm 5$  PPM from -30 to +60°C.

#### Voltage-Controlled Oscillator (VCO)

Only one of the VCOs run at a time, which is controlled by the **+SVTX (W402 Pin3)** and **Q429**. When the FITT is pressed, **+5VTX** goes high (approx.5V) disabling the receive VCO and biases on **Q429** to enable the transmitter VCO. Both the receive and transmitter VCOs are Colpits type oscillators.

The receive VCO consists of **C420-C423**, **L401-L403**, and **0410-0412**. This VCO oscillates at 21.4 MHz below the programmed receive frequency. The VCO's oscillating frequency is tuned by the varactors **0410** and **Q411**. The tuning voltage is supplied from the output of the Loop Filter. The output of the VCO is AC coupled (**C424** and **C425**) to the synthesizer input buffer **Q424** and the output buffer **Q413** respectively.

The transmitter VCO consists of **C466-C469**, **L414-L416**, and **0426-0428**. This VCO oscillates on the programmed transmit frequency. The VCO's oscillating frequency is tuned by the varactors **0426** and **Q427**.

The tuning voltage is supplied from the output of the Loop Filter. The output of the VCO is AC coupled (**C471** and **C472**) to the synthesizer input buffer **Q424** and the output buffer **Q430** respectively.

The transmit voltage controlled oscillator is directly frequency-modulated and operates on the carrier frequency. In the receive mode, the transmit VCO is disabled and the receive VCO is enabled, producing the receive local oscillator signal at a frequency 21.4MHz below the incoming receive frequency.

The synthesizer is tuned in 2.50kHz or 5.00kHz or 6.25kHz steps.

### Synthesizer

The frequency synthesizer is a large scale monolithic synthesizer integrated circuit **0402**.

The synthesizer IC contains a dual modular prescaler, programmable divide-by-N counter, prescale control (swallow) counter, reference oscillator, reference divider, phase detector, charge pump and lock detector. Also, included in **0402** are shift registers and control circuits for frequency controls and general device control.

RF output from the active VCO is buffered by **Q424** and AC coupled to the synthesizer **Q402** prescaler input at pin 8. The divide-by-N counter chain in **Q402**, consisting of the dual-modulus prescaler, swallow counter and programmable counter, divides the VCO signal down to a frequency very close to 2.50kHz or 5.00kHz or 6.25kHz, which is applied to the phase detector. The phase comparator compares the edges of this signal with that of the 2.50kHz or 5.00kHz or 6.25MHz reference signal from the reference divider and drives the external charge pump (**0407** and **Q406**).

The synthesizer unlock detector circuit prevents the operation of the transmitter, when the phase lock loop (PLL) is unlocked. The following discussion assumes the unit has been placed in the transmit mode. **Q402** lock detector Pin 7 goes high when the PLL is locked. **C413** charges through **R416** cutting off **Q406**, then **0401** goes into cutoff thus applying a high to Pin 17 of the microprocessor **QIOS**. A software timing routing brings the RX/TX line low (Pin 15 of 01 05). With the RXITX line low, **Q222B** is cut off and **Q221B** is biased on passing **+SVTX (W402 Pin3)** to saturate **0445B**. After **0445** goes into saturation, it biases on **Q446** to pass switched battery B+ to the transmitter amplifier string which enables transmission.

Should the PLL become unlocked, the lock detector at **Q402** Pin7 will begin pulsing low. **C413** quickly discharges, biasing on **0406**. This, in turn, saturates **0401**, presenting a low to the microprocessor. The microprocessor then changes the RXITX line to a high, thus signaling the other transistor switches to drive **0446** into cutoff, which disables transmission. Therefore, the transmitter remains disabled while the loop remains out of lock.

### Loop Filter

The Loop Filter, a passive lead-lag filter consisting of **R426-R428** and **C416-C417**, integrates the charge pump output to produce the DC turning voltage for the VCO. One parasitic pole, consisting of **R429IC418** and RF chokes **L401/L414**, prevent modulation of the VCOs by the 2.50kHz or 5.00kHz or 6.25kHz reference energy remaining at the output of the loop filter. Direct FM is obtained for modulating frequencies outside the PLL bandwidth by applying the CTCSS signals and the pre-emphasized, limited microphone audio to the VCO modulation circuit. The modulation circuit consists of **R459, R460, 0425** and **C464**.

## TRANSMITTER SECTION- These circuits are found on the RF board.

### RF Power Amp I if i e r

After the PTT is pressed, the **+SVTX** line (W402 Pin3) switches to approximately 5V. **Q429** is turned on enabling transmit VCO. The VCO buffer, pre-driver, driver and power amplifier are biased on by **0446**, which is biased on by the **+SVTX** line switching to 5V. RF output from the transmit VCO(0428) is applied to the VCO output buffer **0430**. Output from **Q430** feeds the pre-driver amplifier **Q431**. The output signal from **Q431** feeds the driver amplifier **G432**, whose output from the driver stage feeds the final RF power amplifier **Q433** to produce the rated output power of 5 watts. The output of the final is applied to a low-pass filter(C483, and **L422**) and then to the transmit/receive switch **0423**. RF power is then fed to the antenna via the output low-pass filter consisting of **C456-C461, L411**, and **L412**.

### Antenna Switching

Switching of the antenna between the transmitter and the receiver is accomplished by the antenna transmit receive switch consisting of PIN diodes **G422** and **0423** in conjunction with **C455** and **R455**. In the transmit mode, switched Battery B+ is applied through **R475** and RF choke L421, hard forward biasing the two PIN diodes on, **Q423** thus permits the flow of RF power from output of the low-pass filter fed by the

output amplifier to the output low-pass filter. **0422** shorts the receiver input to **C455**, which is AC coupled to ground. **L410**, **C454**, **C455** and **R455** then function as a lumped constant quarter-wave transmission line, thus presenting a high impedance to the RF output path, effective isolating the receiver input and transmitter output sections.

#### Power Control

The output level of the amplifier **0433** is controlled by a feedback leveling loop. A small sample of RF Output power is controlled via the dual Op-Amp (**Q452**), which is used as a comparator. Current is sensed by the voltage drop across **R511** and **R512**. This voltage is compared to the one set by the 5-watt adjustment **R289(Hi** power mode) and 1 -watt adjustment **R288(Lo** power mode). The power output is then reduced or increased by varying the **Q454**'s output voltage applied to the power amplifier **Q433**'s pin 2.

#### Transmitter Audio Circuits

The transmitter audio circuits consist of the speech amplifier circuits, the CTCSS circuits and the DCS circuits, These circuits are found on the SUB board.

#### SPEECH AMPLIFITER CIRCUIT

Transmit speech audio is provided by ether the internal electret microphone **NIO1** or the external electret microphone. The microphone audio is applied to pre-emphasis network **C240**, **C324**, **R334** and **R276** and is amplified by **0220D**. This establishes a high frequency breakpoint for the pre-emphasis curve. **Q220C** serves as a clipper, limiting the maximum deviation and increasing the average value of the speech waveform.

**0220A** and **Q220B** form the transmitter "splatter filter which reduces the harmonics from the clipper stage to an acceptable low value. Splatter filter output is fed to the master deviation control **R266**. This sets the maximum allowable frequency deviation and delivers audio to the direct FM input of the transmit VCO module.

CTCSS TONE ENCODER/Digital Code Squelch(DCS)Encoder CTCSS signals and DCS signals are synthesized by microprocessor **0105** and appear as pulse waveform on 1/0 line pin 9. This 1/0 line is applied to a resistive digital-to-analog converter network (consisting of **C 157**, **R143**, and **R167**) which produces a pseudo-sine wave at its output. The waveform is smoothed by low pass filters **0701B** to produce an acceptable sine wave oLApLA. The CTCSS tone signal is adjusted to the proper level by **R705**. The DCS signal is adjusted to the proper balance by **R291**. The signal is then summed with speech audio at the Transmit VCO.

#### RECEIV.ER SECTION These circuits are found on **the RF board**

##### Receiver Front End

In the receive mode, the RF signal enters through the antenna, then through the low-pass filter **C454**, **C456**, **C461**, and **L410-L412**. The PIN diodes **0422** and **0423** are biased off so that the output of the low-pass filter is coupled (**C453**) to the first band-pass filter **C451**, **L409**, **G419** and to the Front End RF overload protection diode pair **0421**. The signal from the band-pass filter is applied to the input of the RF amplifier **0420**. The output of the RF amplifier feeds the input to three more stages of band-pass filters consisting of **C438-C447**, **L406-L408**, and **0416-Q418**. The pass band of the RF front end is tuned to the receiver frequency by the tracking voltage applied to the varactor diodes **0416-0419**. The tracking voltage is supplied from the output buffer **0409** of the synthesizer loop filter. the output from the band-pass filter is applied to the mixer's **0415** gate G1.

##### Local Oscillator (LO)

The Receive VCO (**0410-0412**, and **C420-C422**) provides the LO signal. The VCO is running at 21.4 MHz below the desired receive frequency and is applied to output Buffer **0413**. The output of the buffer is applied to **G2** of the mixer **0415**.

##### M i x e r

The LO's output from **Q413** mixes with the incoming desired signal from bandpass filter(**C438**, **C439**, **L406** and **0416**) that is applied to **G1**. The mixer's resultant output is a 21.4 MHz signal. This first IF signal

is applied to the matching network **L405** and **C435** before being applied to the crystal filter pair **F401**. The output of Crystal Filter **F401 B** is applied to the IF amp **Q414**. The output from the IF amp is applied to the low-pass filter **L204** and **C275**. The output of the low-pass filter is applied to the IF IC **0201** via **C201**. Inside **Q201**, the 21.4MHz IF signal becomes the input to a second mixer with a LO frequency of 20.945 MHz set by **X201**. The 455kHz ceramic filter **F201** filters the second mixer's output, which is the second IF signal. The mixer's output is then fed to the internal limiting amplifier and then on to the FM decoder. The adjustment of the discriminator coil **L201** maximizes the recovered audio output of the detector.

#### FM Detector and Squelch

The FM detector output is used for squelch, decoding tones and audio output. The setting of the squelch adjustment potentiometer **S299(SOL)** sets the input to the squelch amplifier. The squelch amplifier is internal to **0201** and its output is fed to an internal rectifier and squelch detector. The output on **0201** Pin 13 signals the microprocessor **0105** with a low (-OV) to unmute the radio. The audio is unmuted by the microprocessor **QIOS** Pin 13 switching to a high (-5V) thus biasing on **Q700**. The audio is then routed to the audio amplifier **0216** via the volume control **S299 (VOL)**.

#### Receiver Audio Circuits

The detector's audio output also is fed to the tone (CTCSS and DCS) Low-pass filter **Q210C** via 0701A. Then the output of the low-pass filter is routed to the second stage filter **021 CB**. The output of **021 CB** is applied to the squaring circuit **0210A** and finally to the microprocessor **Q101** Pin42 for decoding.

Another branching of the detector output feeds the audio high-pass filter **0226** via **Q21 CD**. The output of the audio high-pass filter feeds the Volume Control **S299(VOL)**. From the wiper arm on the Volume Control, the audio is routed to Pin 2, the input to the audio power amplifier **0216**. The Output of the audio power amplifier is routed through the earphone jack **J401** to the internal speaker **EICI**.

#### BATTERY SECTION

The battery connects to the contact pins (+BC1 and -BC2) on the bottom end of the Radio. The positive terminal of the battery connects to the ON/OFF Volume/Squelch Control switch (**S299**) via **W201 Pin 7** and the negative terminal connects to chassis ground. From the ON/OFF switch, the battery voltage (nominal @ 7.5V) feeds **J202** pin 1 via **W201** Pin 1, Low battery sense **R113/RI14**, voltage regulator **Q211** and transmit power module **Q433** via **W402**

Battery voltage status is monitored by the microprocessor **Q101** through **R113/R114**. When the battery voltage is approximately 5.5V, the output is inputted into the Pin 1 of the microprocessor **0105**. The upper left of LCD 0 1 12 is blinking '-' sign, when the battery voltage is below the preset value.

When the Radio is on a channel with no tone programmed, the BATTERY SAVER Mode is enabled when programmed. In the BATTERY SAVER Mode, the microprocessor **0105** generates a square wave signal on Pin 21. The signal's duty cycle varies according to what the POWER SAVE TIMER Bit is set to in the configuration register (CH 00). If the POWER SAVE TIMER BR is set to a value other than 0, this signal will be low (approx. 0 V) for approximately 200 ms and high (approx. 5 V) for the selected time. The signal from Pin 21 on the microprocessor **Q105** feeds **W101** Pin I 1. When Pin 11 goes high (approx. 5 V) **Q224** is biased off, **Q223** is biased on, **0222A** is cut off, and **0221A** is cut off, thus turning the supply off to **Q201**.

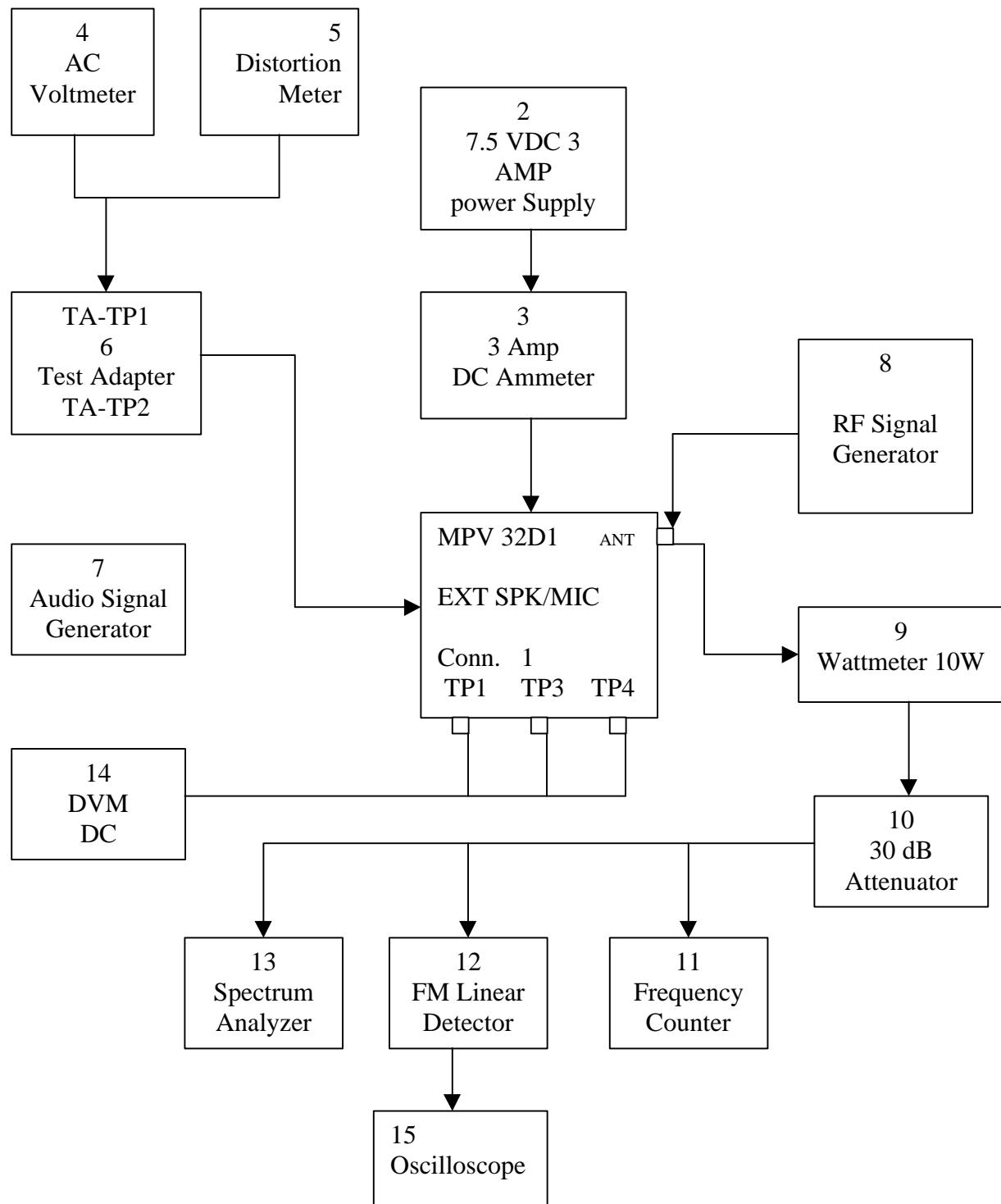

Figure 5. Equipment Test Set-Up