# **Product Technical Specifications & Design guide**

Product Name: M14Q6

Author: Wistron NeWeb Corporation

Revision: 0.2

**Revision Date: 2022/07/03**

# **Contact Information**

| Technical Support website | https://SupportIoT.wnc.com.tw |

|---------------------------|-------------------------------|

| Company Website           | www.wnc.com.tw                |

# **Revision History**

| Rev. # | Author | Summary of Changes   | Date       |

|--------|--------|----------------------|------------|

| 0.1    | WNC    | First release        | 2022/05/14 |

| 0.2    | WNC    | Removed WCDMA & GNSS | 2022/07/03 |

|        |        |                      |            |

|        |        |                      |            |

|        |        |                      |            |

|        |        |                      |            |

|        |        |                      |            |

|        |        |                      |            |

|        |        |                      |            |

|        |        |                      |            |

|        |        |                      |            |

|        |        |                      |            |

|        |        |                      |            |

|        |        |                      |            |

|        |        |                      |            |

#### © Wistron NeWeb Corporation

THIS DOCUMENT AND THE INFORMATION CONTAINED HEREIN IS PROPRIETARY AND IS THE EXCLUSIVE PROPERTY OF WNC AND SHALL NOT BE DISTRIBUTED, REPRODUCED, OR DISCLOSED IN WHOLE OR IN PART WITHOUT PRIOR WRITTEN PERMISSION FROM WNC.

#### LIMITATION OF LIABILITY

THIS DOCUMENT AND THE INFORMATION CONTAINED HEREIN IS PURELY FOR DESIGN REFERENCE AND SUBJECT TO REVISION BY WNC AT ANY TIME. NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY WARRANTY OR RIGHT TO USE THE MATERIAL CONTAINED HEREIN WITHOUT WNC'S PRIOR EXPRESS WRITTEN CONSENT. WNC SHALL NOT BE LIABLE FOR ANY USE, APPLICATION OR DEVELOPMENT DERIVED FROM THE MATERIAL WITHOUT SUCH PRIOR EXPRESS WRITTEN CONSENT.

# Contents

| Cont  | act In | formatio  | n2                        |

|-------|--------|-----------|---------------------------|

| Revis | sion H | istory    |                           |

| Cont  | ents.  |           |                           |

| 1.    | Intro  | duction . | 7                         |

|       | 1.1.   | Abbrev    | viation7                  |

|       | 1.2.   | Feature   | es8                       |

| 2.    | Elect  | rical Spe | cifications10             |

|       | 2.1.   | Host in   | terface pin assignments10 |

|       |        | 2.1.1.    | LGA Pad Diagram10         |

|       |        | 2.1.2.    | Pin Assignments11         |

|       | 2.2.   | Power     | supply                    |

|       | 2.3.   | USB int   | terface                   |

|       | 2.4.   | SGMII     | interface22               |

|       | 2.5.   | UIM in    | terface23                 |

|       | 2.6.   | Contro    | l interface27             |

|       |        | 2.6.1.    | Power-on Signal27         |

|       |        | 2.6.2.    | Wake-up interface         |

|       |        | 2.6.3.    | Reset Signal29            |

|       |        | 2.6.4.    | WWAN state Signal         |

|       | 2.7.   | Digital   | interface                 |

|       |        | 2.7.1.    | JTAG Interface            |

|       |        | 2.7.2.    | SPI Master Interface      |

|       |        | 2.7.3.    | PCM Interface             |

|       |        | 2.7.4.    | I2S Interface             |

|    |      | 2.7.5.     | I2C Interface                   | 34 |

|----|------|------------|---------------------------------|----|

|    |      | 2.7.6.     | UART Interface                  | 35 |

|    |      | 2.7.7.     | ADC Interface                   | 35 |

| 3. | RF S | pecificati | ions                            |    |

|    | 3.1. | RF con     | nections                        |    |

|    | 3.2. | Interfe    | erence and sensitivity          | 37 |

|    | 3.3. | RF Spe     | cification                      |    |

|    |      | 3.5.1 Ba   | and support                     |    |

|    |      | 3.5.2 Ba   | andwidth support                |    |

|    |      | 3.5.3 RF   | Transmit Specification          |    |

|    |      | 3.5.4 RF   | Receiver Specification          |    |

| 4. | Pow  | er         |                                 |    |

|    | 4.1. | Power      | consumption                     | 41 |

| 5. | Soft | ware Inte  | erface                          |    |

|    | 5.1. | Suppo      | rt tools                        | 42 |

|    | 5.2. | USB in     | terface                         | 43 |

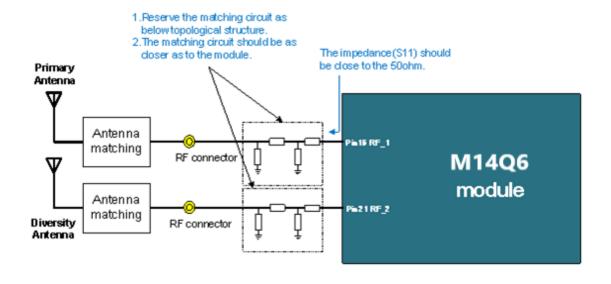

| 6. | Mec  | hanical a  | nd Environmental Certifications |    |

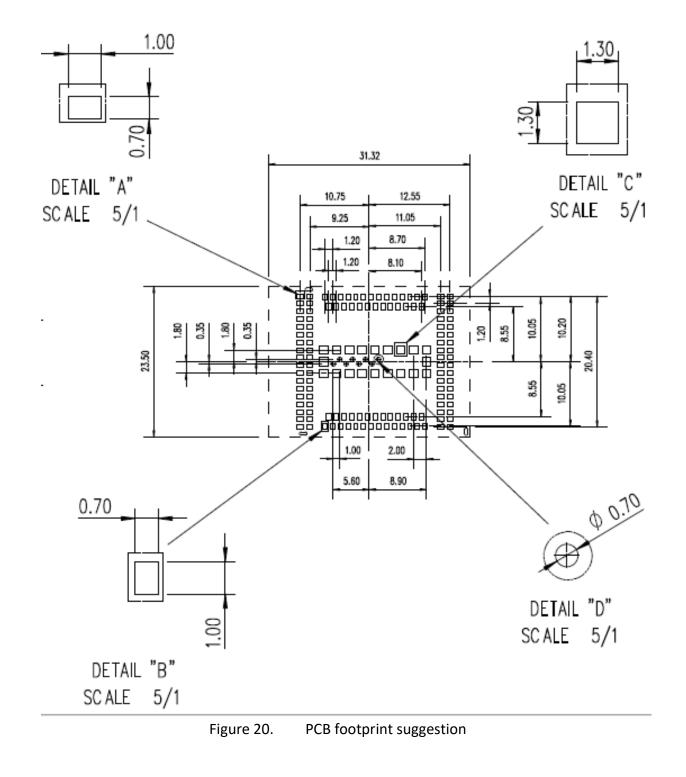

|    | 6.1. | PCBA F     | Form Factor                     | 43 |

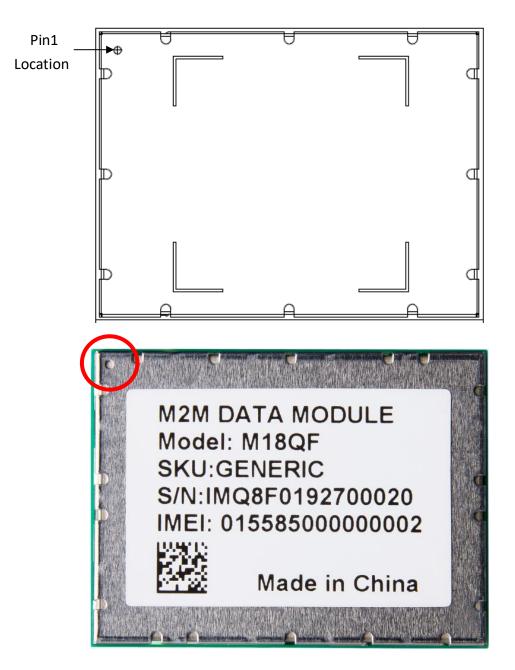

|    | 6.2. | Modul      | le orientation                  | 47 |

|    | 6.3. | Reflow     | /                               | 48 |

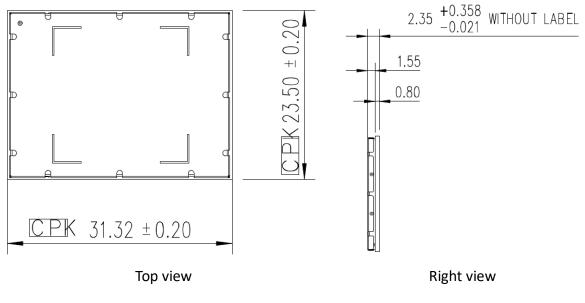

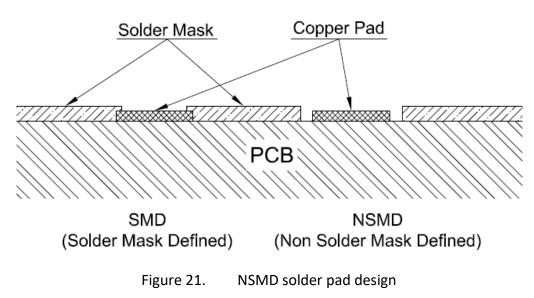

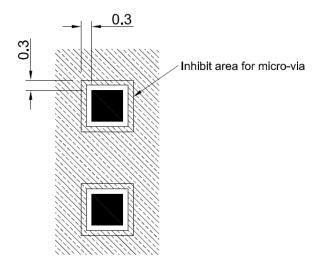

|    | 6.4. | РСВ ра     | ad design                       | 49 |

|    | 6.5. | SMT V      | oids control                    | 51 |

|    |      | 6.5.1.     | Mother board PCB thickness      | 51 |

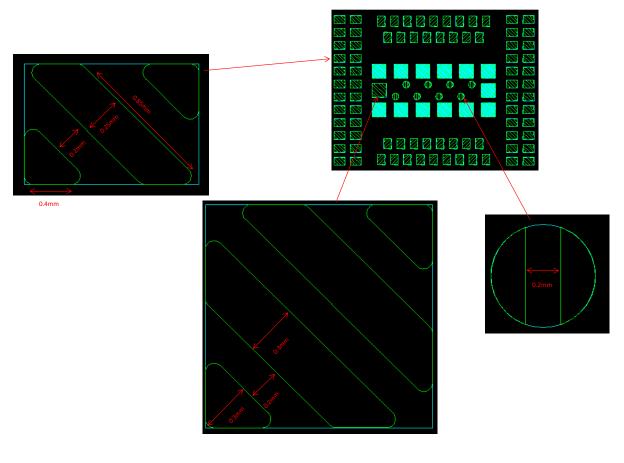

|    |      | 6.5.2.     | Stencil design                  | 51 |

|    | 6.6. | Therm      | al considerations               | 52 |

| 7. | Regul  | atory Compliance and Certification | 53  |

|----|--------|------------------------------------|-----|

|    | 7.1.   | Certification testing              | 53  |

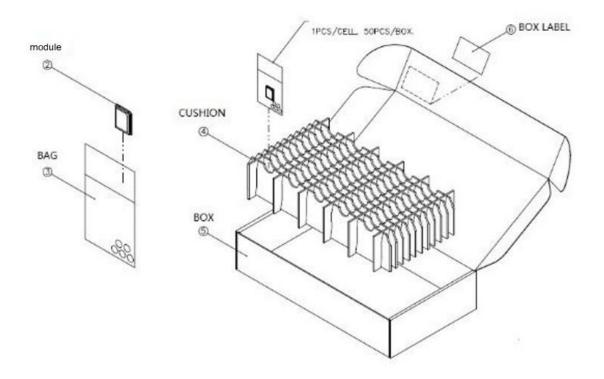

| 8. | Packa  | ging                               | 54  |

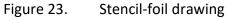

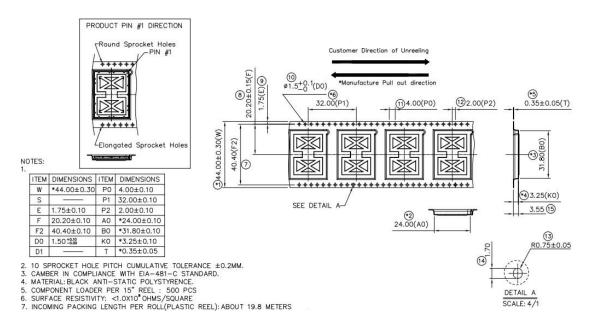

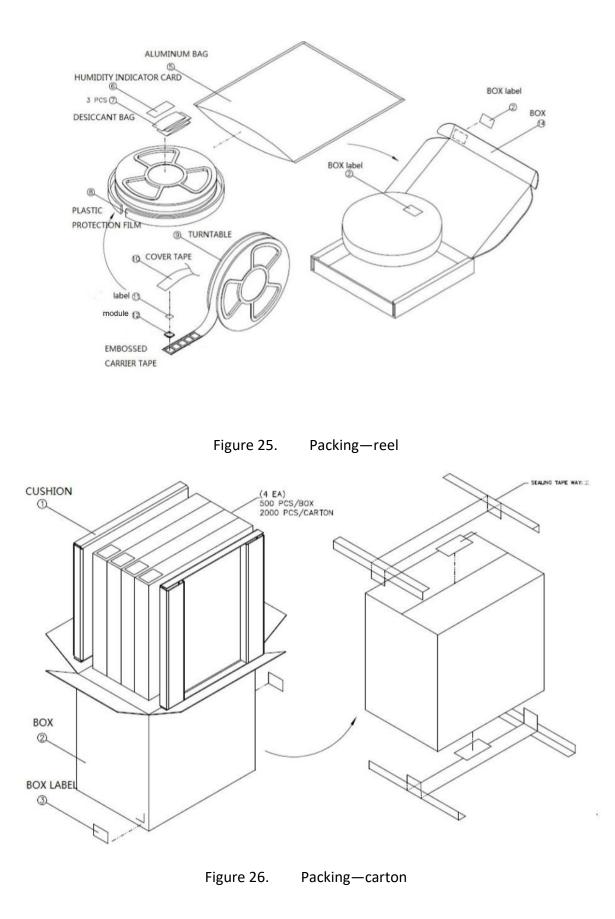

|    | 8.1.   | Tape-and-Reel Package              | 54  |

|    | 8.2.   | Single Packaging for Samples       | .56 |

|    | 8.3.   | MSL level                          | 56  |

| 9. | Safety | Recommendation                     | 57  |

# 1. Introduction

WNC

The M14Q6 modules are LTE modems which incorporate an application CPU subsystem and peripheral interfaces and functions uniquely designed to address the power/performance/cost requirements of IoT and M2M applications. The CPU is based on Qualcomm's MDM architecture which offers OFDMA-related software based signal processing capabilities that significantly exceed traditional communications ARM cores. M14Q6 modules provide a variety of interfaces including USB 2.0, SGMII, SPI, UART, PCM, I2C, UIM & SDIO.

## 1.1. Abbreviation

| Abbreviation | Definition                                                                                 |

|--------------|--------------------------------------------------------------------------------------------|

| AC           | Alternating Current                                                                        |

| DC           | Direct Current                                                                             |

| ETSI         | European Telecommunications Standards Institute                                            |

| GND          | Ground                                                                                     |

| GPS          | Global Positioning System                                                                  |

| GNSS         | Any single or combined satellite navigation system (GPS, GLONASS and combined GPS/GLONASS) |

| GPIO         | General Purpose Input Output                                                               |

| I/O          | Input/Output                                                                               |

| ют           | Internet of Things                                                                         |

| I2C          | Inter-Integrated Circuit                                                                   |

| LGA          | Land Grid Array                                                                            |

| LTE          | Long Term Evolution                                                                        |

| Mbps         | Megabits per second                                                                        |

| MIPS         | Millions of Instructions Per Second                                                        |

| N/A          | Not/Applicable                                                                             |

| OS           | Operating System                                                                           |

| PC           | Personal Computer                                                                          |

| РСМ          | Pulse Code Modulation                                                                      |

|              |                                                                                            |

### Table 1. Abbreviation

| PIN   | Personal Identification Number              |

|-------|---------------------------------------------|

| SIM   | Subscriber Identity Module                  |

| SMA   | Surface Mount Antenna                       |

| SPI   | Serial Peripheral Interface                 |

| UART  | Universal Asynchronous Receiver-Transmitter |

| UIM   | User Identity Module                        |

| USB   | Universal Serial Bus                        |

| Vref  | Voltage reference                           |

| WCDMA | Wideband Code Division Multiple Access      |

| WNC   | Wistron NeWeb Corporation                   |

## 1.2. Features

This section lists main features of M14Q6 module support. For wireless technology and band support information among different modules, please refer to table2 for detail information.

Table 2. M14Q6 module overview

| Module | Category | LTE<br>B2/4/5/12/13/14 | WCDMA<br>B2/5 | GNSS | Temperature Grade |

|--------|----------|------------------------|---------------|------|-------------------|

| M14Q6  | 1        | 0                      | х             | Х    | Industrial        |

| M14Q6* | 1        | 0                      | х             | х    | Commercial        |

Note: 1.Refer to section 6.6 for more information about industrial grade.

2."O" indicates supporting. " $\times$ " indicates not supporting.

### Feature list:

- LTE 3GPP release 10 without Carrier Aggregation

- M14Q6: 3GPP, LTE Cat. 1 with 10/5 Mbps for DL/UL

- Supports LTE B2/4/5/12/13/14

- Ultra-high-performance Cortex A7 microprocessor

- Modem subsystem (MSS)

- Resource and power management (RPM) subsystem

- Optimized for M2M and IoT markets

- Interfaces

- HS USB 2.0 with integrated PHY

- SGMII interface

- Dual UART interfaces (4 bit and 2 bit) for data transfer and diagnostic tools

- SDC1/First SPI interface

- I2C/Second SPI interface

- USIM interface

- GPIOs

- ADC

- PCM/I2S

- JTAG interface

# **2. Electrical Specifications**

# **2.1.** Host interface pin assignments

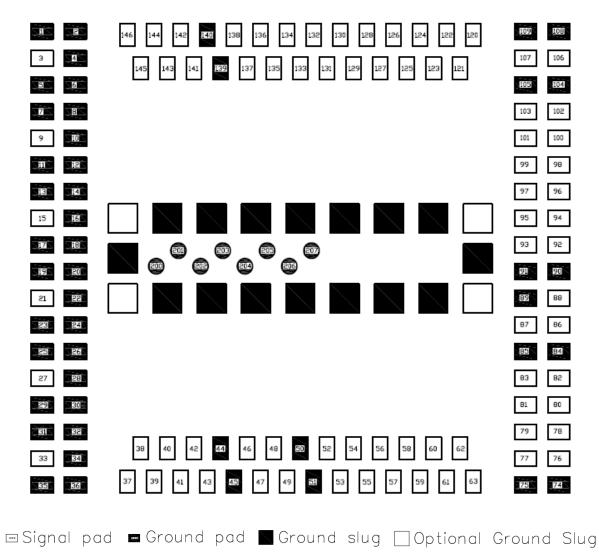

## 2.1.1. LGA Pad Diagram

Optional Custom JTAG

Figure 1. LGA pad diagram (top view)

#### 2.1.2. Pin Assignments

I/O type description:

WNC

- AO : Analog Output

- AI : Analog Input

- DO : Digital Output

- DI : Digital Input

### Table 3. Pin interface family

| Interface Family     | Signal      | Description                 | I/O   |

|----------------------|-------------|-----------------------------|-------|

| <b>RF</b> Interfaces |             |                             |       |

|                      | RF_2        | Diversity antenna           | AI    |

|                      | RF_1        | Main Antenna                | AI/AO |

| User Identity Mo     | dule        |                             |       |

|                      | UIM_VCC     | Power source for UIM        | AO    |

|                      | UIM_DATA    | Data in/out                 | DI/DO |

|                      | UIM_CLK     | Clock signal                | DO    |

|                      | UIM_RESET   | Reset signal                | DO    |

|                      | UIM_DETECT  | UIM Detect signal           | DI/DO |

| Data Interfaces- l   | JSB 2.0     |                             |       |

|                      | USB_HS_DP   | USB Data Positive           | DI/DO |

|                      | USB Detect  | USB Detect                  | DI    |

|                      | USB_HS_DM   | USB Data Negative           | DI/DO |

| Data Interfaces- S   | SGMII       |                             |       |

|                      | SGMII_RX_P  | SGMII receive - plus        | DI    |

|                      | SGMII_RX_M  | SGMII receive - minus       | DI    |

|                      | SGMII_TX_P  | SGMII transmit - plus       | DO    |

|                      | SGMII_TX_M  | SGMII transmit - minus      | DO    |

|                      | SGMII_MDIO  | SGMII Management data       | DI/DO |

|                      | SGMII_MDC   | SGMII Management data clock | DI/DO |

| Data Interfaces- l   | JART1       |                             |       |

|                      | UART1_CTS_N | Clear To Send for UART 1    | DI    |

|                      | UART1_RFR_N | Ready for receive for UART1 | DO    |

|                      | UART1_RX    | Receive for UART 1          | DI    |

|                      | UART1_TX    | Transmit for UART 1         | DO    |

| Data Interfaces- l   | JART2       |                             |       |

|                      | UART2_RX    | Receive for UART 2          | DI    |

|                      |             |                             |       |

|                  | UART2_TX             | Transmit for UART 2         | DO    |

|------------------|----------------------|-----------------------------|-------|

| Data Interfaces- | I2C/2nd_ SPI         |                             |       |

|                  | I2C_SDA              | Data in/out                 | DI/DO |

|                  | 2nd_SPI_EN_1         | 2nd_SPI chip select         | DO    |

|                  | I2C_SCL              | Clock signal                | DO    |

|                  | 2nd_SPI_CLK          | 2nd_SPI serial clock        | DO    |

|                  | SPI_MOSI             | 2nd_SPI master out slave in | DO    |

|                  | NC                   | NC                          | -     |

|                  | SPI_MISO             | 2nd_SPI master in slave out | DI    |

| Data Interfaces- | SDC1/1st_SPI         |                             |       |

|                  | SDC1_DATA_3          | SDC1_DATA_3                 | DI/DO |

|                  | 1st_SPIM_MOSI        | 1st_SPI master out slave in | DO    |

|                  | SDC1_DATA_2          | SDC1_DATA_2                 | DI/DO |

|                  | 1st_SPIM_MISO        | 1st_SPI master in slave out | DI    |

|                  | SDC1_DATA_1          | SDC1_DATA_1                 | DI/DO |

|                  | 1st_SPIM_EN_1        | 1st_SPI chip select         | DO    |

|                  | SDC1_DATA_0          | SDC1_DATA_0                 | DI/DO |

|                  | 1st_SPIM_CLK         | 1st_SPI serial clock        | DO    |

|                  | SDC1_CMD             | SDC1_CMD                    | DI/DO |

|                  | SDC1_CLK             | SDC1_CLK                    | DO    |

| Module Control   | and State Interfaces |                             |       |

|                  | WWAN_STATE           | Wireless WAN Radio State    | DO    |

|                  | POWER_ON             | Power On the module         | DI    |

|                  | WAKEUP_OUT           | Module wakes up host        | DO    |

|                  | WAKEUP_IN            | Host wakes up module        | DI    |

|                  | RESET                | Reset the module            | DI    |

| Power and Groui  | nd                   |                             |       |

|                  | VREF                 | Voltage Reference Output    | AO    |

|                  | VCC                  | Main Power                  | AI    |

|                  | GND                  | GND                         | AI    |

| General Purpose  |                      |                             |       |

|                  | GPIO                 | Digital I/O                 | DI/DO |

|                  | ADC_CONVENTOR        | ADC_CONVENTOR               | AI    |

| AUDIO- PCM/I2S   |                      |                             |       |

|                  | PCM_DIN              | PCM_DIN                     | DI    |

|                  | I2S_DATA0            | I2S_DATA0                   | DI/DO |

|                  |                      |                             |       |

|                 | PCM_DOUT              | PCM_DOUT                | DO    |

|-----------------|-----------------------|-------------------------|-------|

|                 | I2S_DATA1             | I2S_DATA1               | DI/DO |

|                 | PCM_CLK               | PCM_CLK                 | DO    |

|                 | I2S_SCK               | I2S_SCK                 | DO    |

|                 | PCM_SYNC              | PCM_SYNC                | DO    |

|                 | I2S_WS                | I2S_WS                  | DO    |

| RFU- RFU        |                       |                         |       |

|                 | RFU                   | Reserved For Future Use | -     |

| Debug- JTAG     |                       |                         |       |

|                 | JTAG_SRST_N           | JTAG reset for debug    | DI    |

|                 | JTAG_TCK              | JTAG clock input        | DI    |

|                 | JTAG_TDI              | JTAG data input         | DI    |

|                 | JTAG_TDO              | JTAG data output        | DO    |

|                 | JTAG_TMS              | JTAG mode select input  | DI    |

|                 | JTAG_TRST_N           | JTAG reset              | DO    |

|                 | PS_HOLD               | PS_HOLD                 | DI    |

| Debug- Force_US | B_BOOT                |                         |       |

|                 | Force USB BOOT CONFIG | Force USB BOOT CONFIG   | DI    |

| Table 4. | Pin Assignments |

|----------|-----------------|

|----------|-----------------|

| Pin | Modem mode   | Host Mode | Vo   | Voltage Level (V) |      |  |  |

|-----|--------------|-----------|------|-------------------|------|--|--|

| No. | Modelli mode | HOST MOUE | Min. | Тур.              | Max. |  |  |

| 1   | GND          | GND       | -    | 0                 | -    |  |  |

| 2   | GND          | GND       | -    | 0                 | -    |  |  |

| 3   | NC           | NC        | -    | -                 | -    |  |  |

| 4   | GND          | GND       | -    | 0                 | -    |  |  |

| 5   | GND          | GND       | -    | 0                 | -    |  |  |

| 6   | GND          | GND       | -    | 0                 | -    |  |  |

| 7   | GND          | GND       | -    | 0                 | -    |  |  |

| 8   | GND          | GND       | -    | 0                 | -    |  |  |

| 9   | NC           | NC        | -    | -                 | -    |  |  |

| 10  | GND          | GND       | -    | 0                 | -    |  |  |

| 11  | GND          | GND       | -    | 0                 | -    |  |  |

| 12  | GND          | GND       | -    | 0                 | -    |  |  |

| 13  | GND          | GND       | -    | 0                 | -    |  |  |

| 14  | GND          | GND       | -    | 0                 | -    |  |  |

|     |              |           |      |                   |      |  |  |

| 15 | RF_1            | RF_1            | -   | -   | -   |

|----|-----------------|-----------------|-----|-----|-----|

| 16 | GND             | GND             | -   | 0   | -   |

| 17 | GND             | GND             | -   | 0   | -   |

| 18 | GND             | GND             | -   | 0   | -   |

| 19 | GND             | GND             | -   | 0   | -   |

| 20 | GND             | GND             | -   | 0   | -   |

| 21 | RF_2            | RF_2            | -   | -   | -   |

| 22 | GND             | GND             | -   | 0   | -   |

| 23 | GND             | GND             | -   | 0   | -   |

| 24 | GND             | GND             | -   | 0   | -   |

| 25 | GND             | GND             | -   | 0   | -   |

| 26 | GND             | GND             | -   | 0   | -   |

| 27 | NC              | NC              | -   | -   | -   |

| 28 | GND             | GND             | -   | 0   | -   |

| 29 | GND             | GND             | -   | 0   | -   |

| 30 | GND             | GND             | -   | 0   | -   |

| 31 | GND             | GND             | -   | 0   | -   |

| 32 | GND             | GND             | -   | 0   | -   |

| 33 | NC              | NC              | -   | -   | -   |

| 34 | GND             | GND             | -   | 0   | -   |

| 35 | GND             | GND             | -   | 0   | -   |

| 36 | GND             | GND             | -   | 0   | -   |

| 37 | VCC1            | VCC1            | 3.3 | 3.8 | 4.2 |

| 38 | VCC2            | VCC2            | 3.3 | 3.8 | 4.2 |

| 39 | VCC3            | VCC3            | 3.3 | 3.8 | 4.2 |

| 40 | VCC4            | VCC4            | 3.3 | 3.8 | 4.2 |

| 41 | VCC5            | VCC5            | 3.3 | 3.8 | 4.2 |

| 42 | VCC6            | VCC6            | 3.3 | 3.8 | 4.2 |

| 43 | NC              | NC              | -   | -   | -   |

| 44 | GND             | GND             | -   | 0   | -   |

| 45 | GND             | GND             | -   | 0   | -   |

| 46 | PCM_SYNC/GPIO46 | PCM_SYNC/GPIO46 | 1.7 | 1.8 | 1.9 |

| 47 | PCM_DIN/GPIO47  | PCM_DIN/GPIO47  | 1.7 | 1.8 | 1.9 |

| 48 | PCM_DOUT/GPIO48 | PCM_DOUT/GPIO48 | 1.7 | 1.8 | 1.9 |

| 49 | PCM_CLK/GPIO49  | PCM_CLK/GPIO49  | 1.7 | 1.8 | 1.9 |

| 50 | GND             | GND             | -   | 0   | -   |

| 51 | GND                       | GND                       | -   | 0   | -   |

|----|---------------------------|---------------------------|-----|-----|-----|

| 52 | GPIO01/Force USB          | GPIO01/Force USB          | 1.7 | 1.8 | 1.9 |

|    | BOOT Config <sup>*4</sup> | BOOT Config <sup>*4</sup> |     |     |     |

| 53 | GPIO02                    | GPIO02                    | 1.7 | 1.8 | 1.9 |

| 54 | GPIO03                    | GPIO03                    | 1.7 | 1.8 | 1.9 |

| 55 | GPIO04                    | GPIO04                    | 1.7 | 1.8 | 1.9 |

| 56 | NC                        | SGMII_TX_P <sup>*1</sup>  | -   | -   | -   |

| 57 | NC                        | SGMII_TX_M <sup>*1</sup>  | -   | -   | -   |

| 58 | NC                        | SGMII_RX_P <sup>*1</sup>  | -   | -   | -   |

| 59 | NC                        | SGMII_RX_M <sup>*1</sup>  | -   | -   | -   |

| 60 | I2C_SDA                   | I2C_SDA/                  | 1.7 | 1.8 | 1.9 |

|    |                           | 2nd_SPI_EN_1              |     |     |     |

| 61 | I2C_SCL                   | I2C_SCL/                  | 1.7 | 1.8 | 1.9 |

|    |                           | 2nd_SPI_CLK               |     |     |     |

| 62 | NC                        | 2nd_SPI_MOSI              | 1.7 | 1.8 | 1.9 |

| 63 | NC                        | 2nd_SPI_MISO              | 1.7 | 1.8 | 1.9 |

| 74 | GND                       | GND                       | -   | 0   | -   |

| 75 | GND                       | GND                       | -   | 0   | -   |

| 76 | RFFE1_DATA                | RFFE1_DATA                | -   | -   | -   |

| 77 | RFFE1_CLK                 | RFFE1_CLK                 | -   | -   | -   |

| 78 | NC                        | NC                        | -   | -   | -   |

| 79 | NC                        | NC                        | -   | -   | -   |

| 80 | UART1_CTS (UART 1)        | UART1_CTS (UART 1)        | 1.7 | 1.8 | 1.9 |

| 81 | UART1_RTS (UART 1)        | UART1_RTS (UART 1)        | 1.7 | 1.8 | 1.9 |

| 82 | UART1_RX (UART 1)         | UART1_RX (UART 1)         | 1.7 | 1.8 | 1.9 |

| 83 | UART1_TX (UART 1)         |                           | 1.7 | 1.8 | 1.9 |

| 84 | GND                       | GND                       | -   | 0   | -   |

| 85 | GND                       | GND                       | -   | 0   | -   |

| 86 | USB_Dp <sup>*2</sup>      | USB_Dp <sup>*2</sup>      | -   | -   | -   |

| 87 | USB Detect <sup>*3</sup>  | USB Detect <sup>*3</sup>  | 1.7 | 1.8 | 1.9 |

| 88 | USB_Dn <sup>*2</sup>      | USB_Dn <sup>*2</sup>      | -   | -   | -   |

| 89 | GND                       | GND                       | -   | 0   | -   |

| 90 | GND                       | GND                       | -   | 0   | -   |

| 91 | GND                       | GND                       | -   | 0   | -   |

| 92 | NC                        | GPIO92                    | 1.7 | 1.8 | 1.9 |

| 93 | GPIO93                    | GPIO93                    | 1.7 | 1.8 | 1.9 |

| 94  | GPIO94            | GPIO94                         | 1.7     | 1.8     | 1.9     |

|-----|-------------------|--------------------------------|---------|---------|---------|

| 95  | GPIO95            | GPIO95                         | 1.7     | 1.8     | 1.9     |

| 96  | GPIO96            | GPIO96                         | 1.7     | 1.8     | 1.9     |

| 97  | GPIO97            | GPIO97                         | 1.7     | 1.8     | 1.9     |

| 98  | NC                | GPIO98                         | 1.7     | 1.8     | 1.9     |

| 99  | NC                | NC                             | -       | -       | -       |

| 100 | NC                | NC                             | -       | -       | -       |

| 101 | NC                | GPIO101                        | 1.7     | 1.8     | 1.9     |

| 102 | NC                | GPIO102                        | 1.7     | 1.8     | 1.9     |

| 103 | NC                | EPHY_RST_N                     | 1.7     | 1.8     | 1.9     |

| 104 | GND               | GND                            | -       | 0       | -       |

| 105 | GND               | GND                            | -       | 0       | -       |

| 106 | UART2_RX (UART 2) | UART2_RX (UART 2)              | 1.7     | 1.8     | 1.9     |

| 107 | UART2_TX (UART 2) | UART2_TX (UART 2)              | 1.7     | 1.8     | 1.9     |

| 108 | GND               | GND                            | -       | 0       | -       |

| 109 | GND               | GND                            | -       | 0       | -       |

| 120 | NC                | SGMII_MDC <sup>*1</sup>        | -       | -       | -       |

| 121 | NC                | SGMII_MDIO <sup>*1</sup>       | -       | -       | -       |

| 122 | AD Converter      | AD Converter                   | 0.1     | -       | 1.7     |

| 123 | NC                | SDC1_CMD                       | 1.7     | 1.8     | 1.9     |

| 124 | NC                | SDC1_CLK                       | 1.7     | 1.8     | 1.9     |

| 125 | 1st_SPI_MOSI      | SDC1_DATA_3/<br>1st _SPIM_MOSI | 1.7     | 1.8     | 1.9     |

| 126 | 1st _SPI_MISO     | SDC1_DATA_2/<br>1st _SPIM_MISO | 1.7     | 1.8     | 1.9     |

| 127 | 1st _SPI_EN_1     | SDC1_DATA_1/<br>1st _SPIM_EN_1 | 1.7     | 1.8     | 1.9     |

| 128 | 1st _SPI_CLK      | SDC1_DATA_0/<br>1st _SPIM_CLK  | 1.7     | 1.8     | 1.9     |

| 129 | GPIO05            | GPIO05                         | 1.7     | 1.8     | 1.9     |

| 130 | GPIO06            | GPIO06                         | 1.7     | 1.8     | 1.9     |

| 131 | GPIO07            | GPIO07                         | 1.7     | 1.8     | 1.9     |

| 132 | GPIO08            | EPHY_INT_N/GPIO08              | 1.7     | 1.8     | 1.9     |

| 133 | UIM_VCC           | UIM_VCC                        | 1.7/2.7 | 1.8/3.0 | 1.9/3.3 |

| 134 | UIM_DATA          | UIM_DATA                       | 1.7/2.7 | 1.8/3.0 | 1.9/3.3 |

| 135 | UIM_CLK           | UIM_CLK                        | 1.7/2.7 | 1.8/3.0 | 1.9/3.3 |

|     |                   |                                |         |         |         |

| 136 | UIM_RESET                | UIM_RESET                | 1.7/2.7 | 1.8/3.0 | 1.9/3.3 |

|-----|--------------------------|--------------------------|---------|---------|---------|

| 137 | UIM_DETECT               | UIM_DETECT               | 1.7     | 1.8     | 1.9     |

| 138 | NC                       | NC                       | -       | -       | -       |

| 139 | GND                      | GND                      | -       | 0       | -       |

| 140 | GND                      | GND                      | -       | 0       | -       |

| 141 | WWAN_STATE               | WWAN_STATE               | 1.7     | 1.8     | 1.9     |

| 142 | POWER_ON                 | POWER_ON                 | 1.7     | 1.8     | 1.9     |

| 143 | WAKEUP_OUT <sup>*5</sup> | WAKEUP_OUT <sup>*5</sup> | 1.7     | 1.8     | 1.9     |

| 144 | WAKEUP_IN                | WAKEUP_IN                | 1.7     | 1.8     | 1.9     |

| 145 | RESET                    | RESET                    | 1.7     | 1.8     | 1.9     |

| 146 | VREF                     | VREF                     | 1.7     | 1.8     | 1.9     |

| 200 | JTAG_SRST_N              | JTAG_SRST_N              | 1.7     | 1.8     | 1.9     |

| 201 | JTAG TCK                 | JTAG TCK                 | 1.7     | 1.8     | 1.9     |

| 202 | JTAG TDI                 | JTAG TDI                 | 1.7     | 1.8     | 1.9     |

| 203 | JTAG TDO                 | JTAG TDO                 | 1.7     | 1.8     | 1.9     |

| 204 | JTAG_TMS                 | JTAG_TMS                 | 1.7     | 1.8     | 1.9     |

| 205 | JTAG TRST_N              | JTAG TRST_N              | 1.7     | 1.8     | 1.9     |

| 206 | PS_HOLD                  | PS_HOLD                  | 1.7     | 1.8     | 1.9     |

| 207 | NC                       | NC                       | -       | -       | -       |

|     |                          |                          |         |         |         |

Notes:

- \*1. Refer to SGMII standard for more electronic characteristics.

- \*2. Refer to section 2.3, for more information please check USB2.0 standard

- \*3. Pull pin87 USB detect to VREF with a 100k resistor to enable module USB, pull pin87 low to disable module USB, CPU USB PHY consumes some current when USB is enabled.

- \*4. Do not pull pin52 to high before the system boot process is complete.

- \*5. Do not pull pin143 WAKEUP\_OUT to high; otherwise boot will fail.

- \*6. Leave unused pins floating

- \*7. Reserve test points on pin52/86/88/106/107 for debug purpose if possible.

- \*8. If voltage level of digital I/O from the other side is not compatible with module, level shifter is recommended to transfer the voltage level to 1.8V.

### Table 5. Digital I/O characteristics

|                   | Parameter                   | Comments                      | Min                       | Max                       | Unit |

|-------------------|-----------------------------|-------------------------------|---------------------------|---------------------------|------|

| VIH               | High-level input voltage    | CMOS/Schmitt                  | 0.65 * V <sub>DD_Px</sub> | -                         | V    |

| VIL               | Low-level input voltage     | CMOS/Schmitt                  | -                         | 0.35 * V <sub>DD_Px</sub> | V    |

| V <sub>OH</sub>   | High-level output voltage   | CMOS, at rated drive strength | V <sub>DD_Px</sub> - 0.45 |                           | v    |

| V <sub>OL</sub>   | Low-level output voltage    | CMOS, at rated drive strength | -                         | 0.45                      | V    |

| R <sub>P</sub>    | Pull resistance             | Pullup and pulldown           | 55                        | 390                       | kΩ   |

| R <sub>K</sub>    | Keeper resistance           |                               | 30                        | 150                       | kΩ   |

| IIH               | Input high leakage current  | No pulldown                   | -                         | 1                         | μA   |

| I <sub>IL</sub>   | Input low leakage current 4 | No pullup                     | -1                        | -                         | μA   |

| V <sub>SHYS</sub> | Schmitt hysteresis voltage  |                               | 100                       | -                         | mν   |

| C <sub>I/O</sub>  | I/O capacitance             |                               | -                         | 5                         | pF   |

Below is the I/O default setting table to describe the level. It's recommended to follow the pulling High or Low to choose a suitable GPIO for application.

- PU: Pull Up.

- PD: Pull Down

- NP: Non-Pull

| Pin | Signal Nama       | Tune   | Default setting in |

|-----|-------------------|--------|--------------------|

| No. | Signal Name       | Туре   | Normal mode        |

| 46  | PCM_SYNC/GPIO46   | DI /DO | PD                 |

| 47  | PCM_IN/GPIO47     | DI /DO | PD                 |

| 48  | PCM_OUT/GPIO48    | DI /DO | PD                 |

| 49  | PCM_CLK/GPIO49    | DI /DO | PD                 |

| 52  | GPIO01            | DI/DO  | PD                 |

| 53  | GPIO02            | DI/DO  | PD                 |

| 54  | GPIO03            | DI/DO  | PD                 |

| 55  | GPIO04            | DI/DO  | PD                 |

| 60  | I2C_SCL/          | DI/DO  | PD                 |

|     | 2nd_SPI_CLK       |        |                    |

| 61  | I2C_SDA/          | DI/DO  | PD                 |

|     | 2nd_SPI_EN_1      |        |                    |

| 62  | 2nd_SPI_MOSI      | DI/DO  | PD                 |

| 63  | 2nd_SPI_MISO      | DI/DO  | PD                 |

| 80  | UART1_CTS (UART1) | DI/DO  | PD                 |

|     |                   |        |                    |

### Table 6. I/O default setting table

| 81  | UART1_RTS (UART1) | DI/DO | PD |

|-----|-------------------|-------|----|

| 82  | UART1_RX (UART1)  | DI/DO | PD |

| 83  | UART1_TX (UART1)  | DI/DO | PD |

| 92  | GPIO92            | DI/DO | PD |

| 93  | GPIO93            | DO    | NP |

| 94  | GPIO94            | DI/DO | PD |

| 95  | GPIO95            | DI/DO | PD |

| 96  | GPIO96            | DI/DO | PD |

| 97  | GPIO97            | DI/DO | PD |

| 98  | GPIO98            | DI/DO | PU |

| 101 | GPIO101           | DI/DO | PD |

| 102 | GPIO102           | DI/DO | PD |

| 103 | GPIO103           | DI/DO | PD |

| 106 | UART2_RX (UART2)  | DI/DO | PD |

| 107 | UART2_TX (UART2)  | DI/DO | PD |

| 120 | GPIO120           | DI/DO | PD |

| 123 | GPIO123           | DI/DO | PD |

| 124 | GPIO124           | DI/DO | NP |

| 125 | SPIM_MOSI         | DI/DO | PD |

| 126 | SPIM_MISO         | DI/DO | PD |

| 127 | SPIM_EN           | DI/DO | PD |

| 128 | SPIM_CLK          | DI/DO | PD |

| 129 | GPIO05            | DI/DO | PD |

| 130 | GPIO06            | DI/DO | PD |

| 131 | GPIO07            | DI/DO | PU |

| 132 | GPIO08            | DI/DO | PD |

| 141 | WWAN_STATE        | DI/DO | PD |

| 143 | WAKEUP_OUT        | DI/DO | PD |

|     |                   |       |    |

# 2.2. Power supply

LTE module power input is VCC. The internal power chipset will transfer VCC to other power level.

|       | 1                         | able 7. Fower st | apply voltage level |              |      |          |  |

|-------|---------------------------|------------------|---------------------|--------------|------|----------|--|

| Dowor | Pin Name Pads Description |                  | Description         | Voltage Leve |      | evel (V) |  |

| Power | Power Pin Name            | Paus             | Description         | Min.         | Тур. | Max.     |  |

| VCC   | VCC1 to VCC6              | Nos. 37 to 42    | Main Power Supply   | 3.3          | 3.8  | 4.2      |  |

|       |                           |                  |                     |              |      |          |  |

Table 7. Power supply voltage level

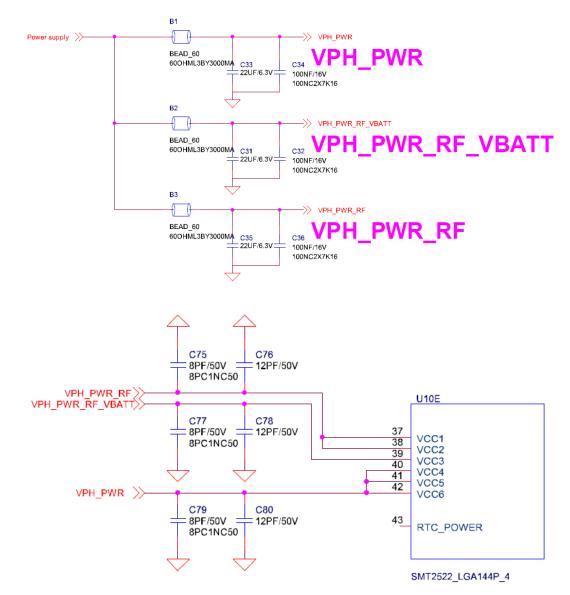

The M14Q6 include an integrated power manager enabling single and direct voltage supply from the battery, reducing the overall bill of materials. The typical voltage 3.8V is recommended.

**Schematic suggestion:** Must to separate module power supply to three paths to keep power clean as below for TX spurious performance. The VPH\_PWR is for Baseband and RF transceiver, the VPH\_PWR\_RF is for RF PA, the VPH\_PWR\_RF\_VBATT is for RF PA control circuit.

Layout Suggestion:

The 22µF, 0.1uF, 12pF and 8pF capacitors are required to place near

VCC pins as close as possible. Each power trace should possess

sufficient line width to withstand its respective current listed in the table below:

Net Name

Current Value

VCC(1-2) total

2A

| VCC(3) total   | 100mA  |

|----------------|--------|

| VCC(4–6) total | 1A     |

| UIM_VCC        | 150 mA |

| VREF           | 300 mA |

## 2.3. USB interface

The M14Q6 modules comply with USB 2.0 high-speed protocol. The USB input/output lines follow USB 2.0 specifications.

| Name | Description       | Input/Output          | Vol  | tage Level | (V)  |

|------|-------------------|-----------------------|------|------------|------|

| Name | Description       | (Direction to module) | Min. | Тур.       | Max. |

| D+   |                   |                       |      |            |      |

|      | USB data positive | (low-/full-speed)     |      |            |      |

|      |                   | Input High            | 2    | 3.3        | 3.6  |

|      |                   | Input Low             | 0    |            | 0.8  |

|      |                   | Output High           | 2.8  | 3.3        | 3.6  |

|      |                   | Output Low            |      |            | 0.3  |

|      | USB data positive | (high-speed)          |      |            |      |

|      |                   | Input High            | 0.3  |            | 0.44 |

|      |                   | Input Low             | 0    |            | 0.01 |

|      |                   | Output High           | 0.36 | 0.38       | 0.44 |

|      |                   | Output Low            | 0    |            | 0.01 |

| D-   |                   |                       |      |            |      |

|      | USB data negative | (low-/full-speed)     |      |            |      |

|      |                   | Input High            | 2    | 3.3        | 3.6  |

|      |                   | Input Low             | 0    |            | 0.8  |

|      |                   | Output High           | 2.8  | 3.3        | 3.6  |

|      |                   |                       |      |            |      |

| Table 8. | Signals of the USB interface |

|----------|------------------------------|

|----------|------------------------------|

| Output Low                     |      |      | 0.3  |

|--------------------------------|------|------|------|

| USB data negative (high-speed) |      |      |      |

| Input High                     | 0.3  |      | 0.44 |

| Input Low                      | 0    |      | 0.01 |

| Output High                    | 0.36 | 0.38 | 0.44 |

| Output Low                     | 0    |      | 0.01 |

The layout design of this circuit on the carrier board should comply with the USB 2.0 highspeed protocol.

### Layout suggestion:

- Differential impedance: 90 Ω

- Space to other signals should be at least 20 mils

- Intra-lane length difference should be less than 150 mils

- Maximum length for each trace:150 mm

#### Signals lengths on modules are tuned as below:

| Function | Net    | Length (mil) |

|----------|--------|--------------|

| USB      |        |              |

|          | USB_Dp | 545.54       |

|          | USB_Dn | 503.04       |

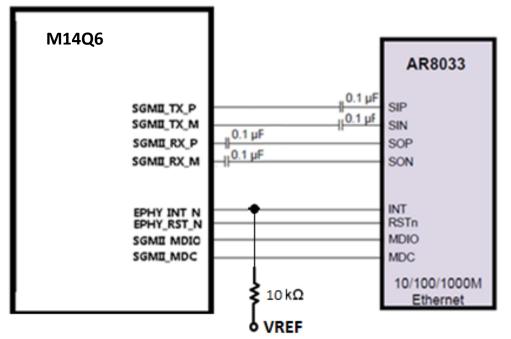

## 2.4. SGMII interface

The M14Q6 modules integrate Ethernet MAC with SGMII interfaces with the following key features:

- IEEE 802.3 compliance

- Full duplex at 1 Gbps

- Half/full duplex for 10/100 Mbps

- Supports VLAN tagging

- Supports IEEE 1588, Precision Time Protocol (PTP)

- Can be used to connect to external Ethernet PHYs such as AR8033 or to an external switch

The following figure illustrates an example of the additional logic connection between the modules and the Ethernet chip. Refer to ENG-46158, Rev 1.8 for electrical and timing

specifications.

Figure 2. SGMII circuit example

### Layout suggestion:

- Differential impedance:100 Ω

- Space to other signals: > 3x line width

- Lane-to-lane space: > 3x line width

- Intra-lane mismatch: < 0.7 mm

Signal lengths on the modules are tuned as below:

| Function | Net                     | Length (mil) |  |

|----------|-------------------------|--------------|--|

| SGMII    |                         |              |  |

|          | SGMII_TX_P              | 617.11       |  |

|          | SGMII_TX_M              | 642.13       |  |

|          | SGMII_RX_P_C+SGMII_RX_P | 661.40       |  |

|          | SGMII_RX_M_C+SGMII_RX_M | 675.06       |  |

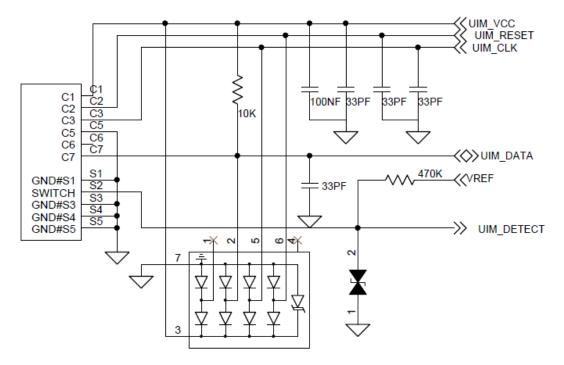

# 2.5. UIM interface

M14Q6 modules provide an UIM\_DETECT input pin for UIM connector to detect UIM card.

When UIM card is present, UIM\_DETECT should be high (1.8V). If UIM card is absent, UIM\_DETECT should be low. It's required to pull UIM\_DETECT to VREF with a 470k resistor. A 0.1µF and a 33pF capacitor are recommended to place between UIM\_VCC and Ground in parallel. A 33pF capacitor is recommended to place between UIM\_RESET, UIM\_CLK and UIM\_DATA and Ground in parallel, see Figure5 for reference.

Electrostatic discharge (ESD) protection circuit is also recommended to place near the UIM socket as close as possible, and the Ground pin of the ESD protection component must be well connected to the Ground plane.

The following figure shows an example of UIM card circuit.

Figure 3. UIM card circuit example

It's highly suggested to make sure that SIM electrical characteristics can meet ETSI TS 102 221 requirement before going to certification like PTCRB. Refer to the following capture from ETSI TS 102 221 section 5 for critical requirement:

## 5.2 Class B operating conditions

## 5.2.1 Supply voltage Vcc (contact C1)

The terminal shall operate the UICC within the following limits.

| Ī | Symbol | Minimum | Maximum | Unit |

|---|--------|---------|---------|------|

| Ι | Vcc    | 2,7     | 3,3     | V    |

### 5.2.2 Reset (RST) (contact C2)

The terminal shall operate the UICC within the following limits.

#### Table 5.6: Electrical characteristics of RESET (RST) under normal operating conditions

| Symbol                                                                                                                     | Conditions                                 | Minimum      | Maximum        | Unit |  |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------|----------------|------|--|

| V <sub>OH</sub>                                                                                                            | I <sub>OHmax</sub> = +20 μA                | 0,8 x Vcc    | Vcc (see note) | V    |  |

| V <sub>OL</sub>                                                                                                            | I <sub>OLmax</sub> = -200 μA               | 0 (see note) | 0,2 x Vcc      | V    |  |

| t <sub>R</sub> t <sub>F</sub>                                                                                              | C <sub>in</sub> = C <sub>out</sub> = 30 pF |              | 400            | μs   |  |

| NOTE: To allow for overshoot the voltage on RST should remain between -0,3 V and Vcc + 0,3 V<br>during dynamic operations. |                                            |              |                |      |  |

### 5.2.3 Clock CLK (contact C3)

The terminal shall support 1 MHz to 5 MHz. The terminal shall supply the clock. When only the interface specified in the present document is activated, no "internal clock" shall be used in the UICC.

The duty cycle shall be between 40 % and 60 % of the period during stable operation.

The terminal shall operate the UICC within the following limits.

#### Table 5.7: Electrical characteristics of Clock (CLK) under normal operating conditions

| Symbol                                                                                       | Conditions                                 | Minimum      | Maximum        | Unit |  |

|----------------------------------------------------------------------------------------------|--------------------------------------------|--------------|----------------|------|--|

| V <sub>OH</sub>                                                                              | I <sub>OHmax</sub> = +20 μA                | 0,7 x Vcc    | Vcc (see note) | V    |  |

| V <sub>OL</sub>                                                                              | I <sub>OLmax</sub> = -20 μA                | 0 (see note) | 0,2 x Vcc      | V    |  |

| t <sub>R</sub> t <sub>F</sub>                                                                | C <sub>in</sub> = C <sub>out</sub> = 30 pF |              | 50             | ns   |  |

| NOTE: To allow for overshoot the voltage on CLK should remain between -0,3 V and Vcc + 0,3 V |                                            |              |                |      |  |

| dur                                                                                          | ing dynamic operations.                    |              |                |      |  |

### 5.2.4 I/O (contact C7)

Table 5.8 defines the electrical characteristics of the I/O (contact C7). The values given in the table allow the derivation of the values of the pull-up resistor in the terminal and the impedance of the drivers and receivers in the terminal and UICC.

| Symb                          | ol                                                                                                   | Conditions                                 | Minimum                 | Maximum              | Unit |

|-------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------|----------------------|------|

| V <sub>IH</sub>               |                                                                                                      | I <sub>IHmax</sub> = ±20 μA (see note 2)   | 0,7 x Vcc               | Vcc + 0,3            | V    |

| VIL                           |                                                                                                      | I <sub>ILmax</sub> = +1 mA                 | -0,3                    | 0,2 x Vcc            | V    |

| VOH                           | ł                                                                                                    | I <sub>OHmax</sub> = +20 μA                | 0,7 x Vcc               | Vcc (see note 3)     | V    |

| (see not                      | te 1)                                                                                                |                                            |                         |                      |      |

| V <sub>OL</sub>               |                                                                                                      | I <sub>OLmax</sub> = -1mA                  | 0 (see note 3)          | 0,4                  | V    |

| t <sub>R</sub> t <sub>F</sub> |                                                                                                      | C <sub>in</sub> = C <sub>out</sub> = 30 pF |                         | 1                    | μs   |

|                               |                                                                                                      | in out                                     |                         | 100                  | ns   |

|                               |                                                                                                      |                                            |                         | (see note 4)         |      |

| NOTE 1:                       | It is as                                                                                             | sumed that a pull-up resistor is used o    | on the interface devic  | e (recommended val   | ue:  |

|                               | 20 kΩ)                                                                                               | -                                          |                         |                      |      |

|                               |                                                                                                      | static conditions (idle state) only the    |                         |                      |      |

| 1                             |                                                                                                      | ons (transmissions) short-term voltag      | e spikes on the I/O lir | ne may cause a curre | ent  |

|                               | reversa                                                                                              |                                            |                         |                      |      |

|                               | NOTE 3: To allow for overshoot the voltage on I/O shall remain between -0,3 V and Vcc + 0,3 V during |                                            |                         | during               |      |

| 1                             |                                                                                                      | ic operation.                              |                         |                      |      |

| NOTE 4:                       | This va                                                                                              | lue applies when the low impedance         | buffer is selected.     |                      |      |

## 5.3 Class C operating conditions

### 5.3.1 Supply voltage Vcc (contact C1)

The terminal shall operate the UICC within the following limits.

#### Table 5.9: Electrical characteristics of Vcc under normal operating conditions

| Symbol | Minimum | Maximum | Unit |

|--------|---------|---------|------|

| Vcc    | 1,62    | 1,98    | V    |

### 5.3.2 Reset (RST) (contact C2)

The terminal shall operate the UICC within the following limits.

#### Table 5.10: Electrical characteristics of RESET (RST) under normal operating conditions

| Symbol                                                                                                                     | Conditions                                 | Minimum      | Maximum        | Unit |  |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------|----------------|------|--|

| V <sub>OH</sub>                                                                                                            | I <sub>OHmax</sub> = +20 μA                | 0,8 x Vcc    | Vcc (see note) | V    |  |

| V <sub>OL</sub>                                                                                                            | I <sub>OLmax</sub> = -200 μA               | 0 (see note) | 0,2 x Vcc      | V    |  |

| t <sub>R</sub> t <sub>F</sub>                                                                                              | C <sub>in</sub> = C <sub>out</sub> = 30 pF |              | 400            | μs   |  |

| NOTE: To allow for overshoot the voltage on RST should remain between -0,3 V and Vcc + 0,3 V<br>during dynamic operations. |                                            |              |                |      |  |

## 5.3.3 Clock CLK (contact C3)

#### Table 5.11: Electrical characteristics of Clock (CLK) under normal operating conditions

| Symbol                        | Conditions                                                                                                                 | Minimum      | Maximum        | Unit |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------|----------------|------|--|--|

| V <sub>OH</sub>               | I <sub>OHmax</sub> = +20 μA                                                                                                | 0,7 x Vcc    | Vcc (see note) | V    |  |  |

| V <sub>OL</sub>               | I <sub>OLmax</sub> = -20 μA                                                                                                | 0 (see note) | 0,2 x Vcc      | V    |  |  |

| t <sub>R</sub> t <sub>F</sub> | C <sub>in</sub> = C <sub>out</sub> = 30 pF                                                                                 |              | 50             | ns   |  |  |

|                               | NOTE: To allow for overshoot the voltage on CLK should remain between -0,3 V and Vcc + 0,3 V<br>during dynamic operations. |              |                |      |  |  |

## 5.3.4 I/O (contact C7)

Table 5.12 defines the electrical characteristics of the I/O (contact C7). The values given in the table allow the derivation of the values of the pull-up resistor in the terminal and the impedance of the drivers and receivers in the terminal and UICC.

| Symbol                                                                                                                                                                                                            | Conditions                                 | Minimum        | Maximum          | Unit |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------|------------------|------|--|--|

| VIH                                                                                                                                                                                                               | I <sub>IHmax</sub> = ±20 µA (see note 2)   | 0,7 x Vcc      | Vcc + 0,3        | V    |  |  |

| VIL                                                                                                                                                                                                               | I <sub>ILmax</sub> = +1 mA                 | -0,3           | 0,2 x Vcc        | V    |  |  |

| V <sub>OH</sub>                                                                                                                                                                                                   | I <sub>OHmax</sub> = +20 μA                | 0,7 x Vcc      | Vcc (see note 3) | V    |  |  |

| (see note 1)                                                                                                                                                                                                      |                                            |                |                  |      |  |  |

| V <sub>OL</sub>                                                                                                                                                                                                   | I <sub>OLmax</sub> = -1mA                  | 0 (see note 3) | 0,3              | V    |  |  |

| t <sub>R</sub> t <sub>F</sub>                                                                                                                                                                                     | C <sub>in</sub> = C <sub>out</sub> = 30 pF |                | 1                | μs   |  |  |

|                                                                                                                                                                                                                   |                                            |                | 100              | ns   |  |  |

|                                                                                                                                                                                                                   |                                            |                | (see note 4)     |      |  |  |

| NOTE 1: It is assumed that a pull-up resistor is used on the interface device (recommended value:<br>20 kΩ).                                                                                                      |                                            |                |                  |      |  |  |

| NOTE 2: During static conditions (idle state) only the positive value can apply. Under dynamic operating<br>conditions (transmissions) short-term voltage spikes on the I/O line may cause a current<br>reversal. |                                            |                |                  |      |  |  |

| NOTE 3: To allow for overshoot the voltage on I/O shall remain between -0,3 V and Vcc + 0,3 V during<br>dynamic operation.                                                                                        |                                            |                |                  |      |  |  |

| NOTE 4: This value applies when the low impedance buffer is selected.                                                                                                                                             |                                            |                |                  |      |  |  |

Table 5.12: Electrical characteristics of I/O under normal operating conditions

# 2.6. Control interface

This section describes the power-on/off, wake-up and reset interface on how to control the module.

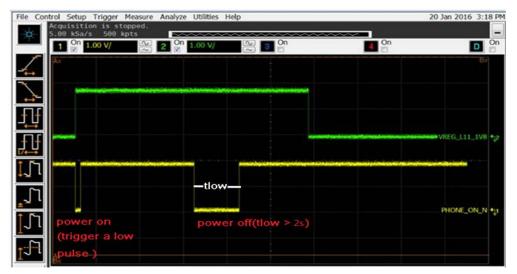

### 2.6.1. Power-on Signal

The POWER\_ON is an active Low input signal used to enable or disable the module. Do not toggle the PERST# pin during power-on. This signal has the highest priority over the wakeup, the alarms signals, and the digital control pins.

There are three possible states of the module:

- Module Off VCC is not present.

- Module Enabled VCC is supplied, and the module is enabled.

- Module Disabled VCC is supplied, and the module is disabled.

The state transitions are defined as follows:

When voltage is applied to VCC, the module shall enter the Module Disabled state.

- An input to the POWER\_ON pin shall trigger the transition from the Module Disabled to the Module Enabled state. See figure6, a low pulse(tlow > 0s) on POWER\_ON pad will enable the module after VCC is applied.

- An input to the POWER\_ON pin shall trigger the transition from the Module Enabled to the Module Disabled state. See figure6, after power on, a low pulse (tlow > 2s) on POWER\_ON pin will disable (power-off) the module.

Figure 4. Power ON/OFF timming

### 2.6.2. Wake-up interface

In applications where power consumption is a major factor in performance metrics (such as battery-operated sensors that are based on IOT/M2M modem solution and also include a third party host), it is necessary to define a simple interface that will allow both the modem and the host to be able to enter low power states whenever possible and the other side to wake it up once required.

For example, if the host has no data to transmit or any other tasks, it may enter some low power state according to its own capabilities and configurations. If during that period the host is in a low power state and the modem suddenly receives data, it must wake-up the host.

A similar requirement exists from the other side. For example, if the modem is in a low power state and suddenly the host must transmit data, it must be able to wake-up the modem.

The interface consists of two signals: One is driven by the host and received by the modem; the other is driven by the modem and received by the host.

Each side can wake the other side by toggling wakeup signal high and allowing the other side to go to sleep when not needed by toggling it low.

- "WAKEUP\_IN" (Host: Output, Modem: Input):

- LOW: SoC does not require the MODEM (allowing it to sleep).

- HIGH: SoC requires the MODEM or acknowledges it is ready following a wakeup request from the MODEM.

- "WAKEUP\_OUT" (Host: Input, Modem: Output):

- LOW: The MODEM does not require the Host (allowing it to sleep)

- HIGH: The MODEM requires the Host or acknowledges it is ready following a wakeup request from the SoC.

When M14Q6 modules act as modem, keep WAKEUP\_IN high before system boot process is complete, after system boot, keep WAKEUP\_IN low. WAKEUP\_IN and WAKEUP\_OUT behavior of host mode will be discussed according to product specification.

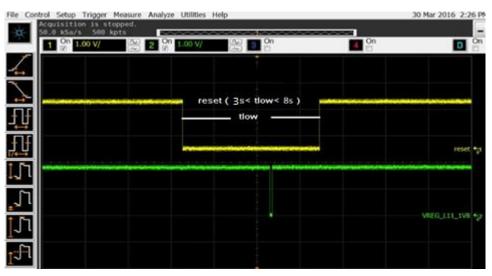

### 2.6.3. Reset Signal

The Reset Signal is a hardware reset signal to control the system reset directly. You can connect it to a key or a control signal. A low pulse (3s<tlow<8s) after power on will reset the module, see figure7.

Figure 5. Reset Signals circuit

#### 2.6.4. WWAN state Signal

The WWAN state pin definition as below.

- WWAN state pin output "high"

When device register to network, the WWAN state pin output "high".

- WWAN state pin output "low"

When device not to register to network, the WWAN state pin output "low".

## 2.7. Digital interface

This section provides required AC timing information related to module digital interfaces.

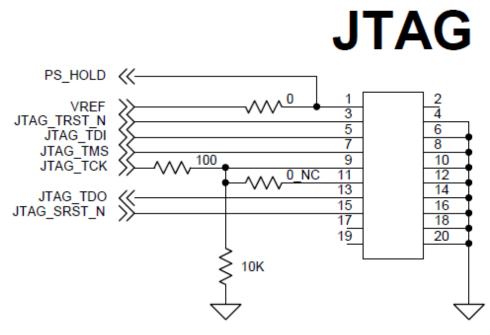

### 2.7.1. JTAG Interface

M14Q6 provide one JTAG interface, leave JTAG pins floating if not used.

Figure 6. JTAG schematic (example)

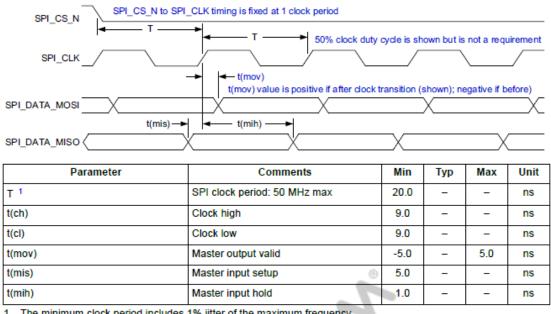

### 2.7.2. SPI Master Interface

SPIM\_CLK – Output clock

SPIM\_CS – Output, chip-select

#### SPIM\_MOSI – Output, data to slave

SPIM\_MISO – Input, data from slave

#### Timing

1. The minimum clock period includes 1% jitter of the maximum frequency.

Figure 7. SPI timing parameters

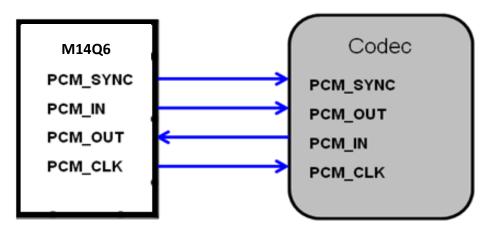

### 2.7.3. PCM Interface

M14Q6 modules provide one PCM master digital audio interface. Keep PCM signal traces far away from noise and radiating signal on PCB

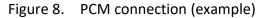

#### Timing

Figure 9. PCM timing diagram

|           | Parameter                                        | Comments | Min | Тур   | Мах | Unit |

|-----------|--------------------------------------------------|----------|-----|-------|-----|------|

| t(sync)   | PCM_SYNC cycle time                              |          | -   | 125   | -   | μs   |

| t(synca)  | PCM_SYNC asserted time                           |          | -   | 488   | -   | ns   |

| t(syncd)  | PCM_SYNC de-asserted time                        |          | -   | 124.5 | -   | μs   |

| t(clk)    | PCM_CLK cycle time                               |          | -   | 488   | -   | ns   |

| t(clkh)   | PCM_CLK high time                                |          | -   | 244   | -   | ns   |

| t(clkl)   | PCM_CLK low time                                 |          | -   | 244   | -   | ns   |

| t(susync) | PCM_SYNC offset time to<br>PCM_CLK falling       |          | -   | 122   | -   | ns   |

| t(sudin)  | PCM_DIN setup time to<br>PCM_CLK falling         |          | 60  | -     | -   | ns   |

| t(hdin)   | PCM_DIN hold time after<br>PCM_CLK falling       |          | 10  | -     | -   | ns   |

| t(pdout)  | Delay from PCM_CLK rising to<br>PCM_DOUT valid   |          | -   | -     | 60  | ns   |

| t(zdout)  | Delay from PCM_CLK falling to<br>PCM_DOUT HIGH-Z |          | -   | 160   | -   | ns   |

| Figure 10. PCM timing pa | rameters |

|--------------------------|----------|

|--------------------------|----------|

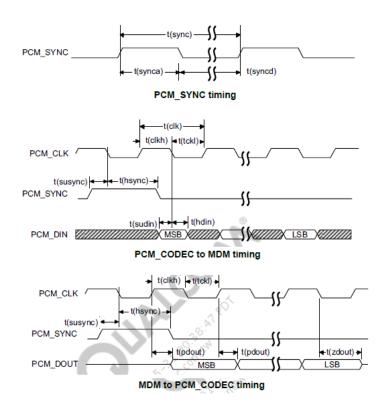

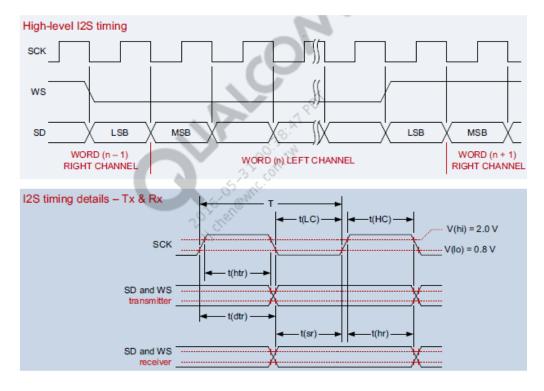

### 2.7.4. I2S Interface

PCM and I2S share the same pins on the modules, I2C only support master mode, keep I2S signal trace far away from noise and radiating signal on PCB

### Timing

|        | Parameter                  | Comments <sup>1</sup> | Min      | Тур | Max      | Unit |

|--------|----------------------------|-----------------------|----------|-----|----------|------|

| Using  | internal SCK               |                       | I        | L   |          |      |

|        | Frequency                  |                       | -        | -   | 12.288   | MHz  |

| т      | Clock period               |                       | 81.380   | -   | -        | ns   |

| t(HC)  | Clock high                 |                       | 0.45 · T | -   | 0.55 · T | ns   |

|        | Parameter                  | Comments 1            | Min      | Тур | Max      | Unit |

| t(LC)  | Clock low                  |                       | 0.45 · T | -   | 0.55 · T | ns   |

| t(sr)  | SD and WS input setup time |                       | 16.276   | -   | -        | ns   |

| t(hr)  | SD and WS input hold time  |                       | 0        | -   | -        | ns   |

| t(dtr) | SD and WS output delay     |                       | -        | -   | 65.100   | ns   |

| t(htr) | SD and WS output hold time |                       | 0        | -   | -        | ns   |

| Using  | external SCK               |                       | 0        |     |          |      |

|        | Frequency                  |                       |          | -   | 12.288   | MHz  |

| Т      | Clock period               |                       | 81.380   | -   | -        | ns   |

| t(HC)  | Clock high                 |                       | 0.45 · T | -   | 0.55 · T | ns   |

| t(LC)  | Clock low                  |                       | 0.45 · T | -   | 0.55 · T | ns   |

| t(sr)  | SD and WS input setup time |                       | 16.276   | -   | -        | ns   |

| t(hr)  | SD and WS input hold time  |                       | 0        | -   | -        | ns   |

| t(dtr) | SD and WS output delay     |                       | -        | -   | 65.100   | ns   |

| t(htr) | SD and WS output hold time | 194                   | 0        | -   | -        | ns   |

| Figure 12. | I2S timing diagram |

|------------|--------------------|

|            |                    |

Load capacitance is between 10 and 40 pF.

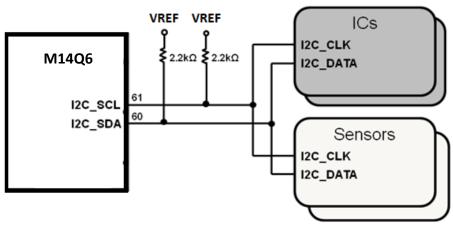

### 2.7.5. I2C Interface

M14Q6 modules provide one I2C interface, I2C only support master mode.

### 2.7.6. UART Interface

There are two UART interfaces on M14Q6: One is a 4 bit UART(UART1) for high-speed data transfer, max baud rate can be up to 4Mbps. Another is a 2 bit UART(UART2) for diagnostic tools and debugging, the default baud rate 115200bps is recommended.

| M14Q6     |                |                                            |

|-----------|----------------|--------------------------------------------|

| UART1_RTS | 81<br>82<br>83 | UART_RTS<br>UART_CTS<br>UART_TX<br>UART_RX |

Figure 15. UART connection (example)

### 2.7.7. ADC Interface

An Analog to Digital Converter (ADC) input is provided by the M14Q6. The converter is 16 bit resolution, ranging from 0.1 V to 1.7 V, with a sampling rate of 2.4 MHz.

| Parameter              | Comments                        | Minimum | Тур | Maximum | Units |

|------------------------|---------------------------------|---------|-----|---------|-------|

| Supply voltage         | Connected internally to VREG_L3 | -       | 1.8 | -       | V     |

| Resolution             | Decimated data                  | -       | -   | 15      | bits  |

| Analog-input bandwidth |                                 | -       | 100 | -       | kHz   |

| Sample rate            | XO/8                            | -       | 2.4 | -       | MHz   |

| Offset error           | Relative to full-scale          | -1      | -   | +1      | %     |

| Gain error             | Relative to full-scale          | -1      | -   | +1      | %     |

| INL                    | 15-bit output                   | -8      | -   | +8      | LSB   |

| DNL                    | 15-bit output                   | -4      | -   | +4      | LSB   |

Layout suggestion:

- ADC signal trace should be well protected by GND plane

- ADC signal trace should be protected from noise and other radiating signals

# 3. **RF Specifications**

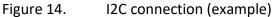

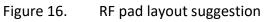

# 3.1. RF connections

The M14Q6 modules have three RF pads; developers must connect them via 50  $\Omega$  traces to the main board.

ANT0\_TRX pad (Pin15) – Primary RX/TX path ANT1\_DRX pad (Pin21) – Diversity path

It is recommended that grounds not be present under the surface of the RF pads in the layout. Details are included below. Layer2 has the same keep out size as Layer1

Figure 17. RF matching guide

### 3.2. Interference and sensitivity

This section includes tips to assist developers in identifying the interference that may affect M14Q6 modules when used in systems.

- Interference from other wireless devices

- Harmonics, inter-modulated signal generated from wireless devices that fall in RX ranges of the modules, may result in degraded RX performance.

- It is highly recommended to check RX performance of entire systems within the shielding environment.

- Interference from host interface

- High-speed signal-switching elements in systems can easily couple noise into the module (Ex.: DDR memory, LCD modules, DC-DC converter, PCM signal).

- Methods to avoid sources of interference

- Antenna location is important; we recommend directing the antenna

away from high-speed switching signals. Furthermore, the trace from the module to the antenna should be as short as possible and must be shielded by complete grounding.

- The M14Q6 modules are well shielded; the high-speed elements

(Ex.: DDR memory, LCD modules, DC-DC converter, PCM signal) on a system should have shielding reserved during the early stages of development.

### 3.3. RF Specification

#### 3.5.1 Band support

|             | Table 9. Band s | upport         |  |

|-------------|-----------------|----------------|--|

| Band        | Uplink (MHz)    | Downlink (MHz) |  |

| LTE Band 2  | 1,850–1,910     | 1,930–1,990    |  |

| LTE Band 4  | 1,710–1,755     | 2,110–2,155    |  |

| LTE Band 5  | 824–849         | 869–894        |  |

| LTE Band 12 | 699–716         | 729–746        |  |

| LTE Band 13 | 777-787         | 746-756        |  |

| LTE Band 14 | 788-798         | 758-768        |  |

#### 3.5.2 Bandwidth support

| Table  | 10. | Bandwidth | support |

|--------|-----|-----------|---------|

| i unic | ±0. | Danawiath | Juppord |

| - •         | Bandwidth    |              |              |              |              |              |  |

|-------------|--------------|--------------|--------------|--------------|--------------|--------------|--|

| Band        | 1.4 MHz      | 3 MHz        | 5 MHz        | 10 MHz       | 15 MHz       | 20 MHz       |  |

| LTE Band 2  | $\checkmark$ | ✓            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| LTE Band 4  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| LTE Band 5  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            |  |

| LTE Band 12 | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            |  |

| LTE Band 13 | -            | -            | $\checkmark$ | $\checkmark$ | -            | -            |  |

| LTE Band 14 | -            | -            | $\checkmark$ | $\checkmark$ | -            | -            |  |

#### 3.5.3 RF Transmit Specification

#### Table 11. Conductive Tx output power

| Band        | Items         | Parameter          | Unit | Min. | Тур. | Max. |

|-------------|---------------|--------------------|------|------|------|------|

| LTE Band 2  | Max. TX Power | 10 MHz 12 RBs/QPSK | dBm  | 20.3 | 23   | 25.7 |

| LTE Band 4  | Max. TX Power | 10 MHz 12 RBs/QPSK | dBm  | 20.3 | 23   | 25.7 |

| LTE Band 5  | Max. TX Power | 10 MHz 12 RBs/QPSK | dBm  | 20.3 | 23   | 25.7 |

| LTE Band 12 | Max. TX Power | 10 MHz 12 RBs/QPSK | dBm  | 20.3 | 23   | 25.7 |

| LTE Band 13 | Max. TX Power | 10 MHz 12 RBs/QPSK | dBm  | 20.3 | 23   | 25.7 |

| LTE Band 14 | Max. TX Power | 10 MHz 12 RBs/QPSK | dBm  | 20.3 | 23   | 25.7 |

Note: 1.The RF Transmit Specification is defined at the LGA pad.

2. Meet 3GPP TS 36.521-1/TS 34.121-1 test standard.

#### 3.5.4 RF Receiver Specification

#### Table 12. Conductive Rx sensitivity-3GPP

| Band                                     | Items                                  | Parameter                                      | Unit        | Тур. | 3GPP standard<br>limit |

|------------------------------------------|----------------------------------------|------------------------------------------------|-------------|------|------------------------|

| LTE Band 2                               | <b>RX</b> Sensitivity                  | 10 MHz with 50 RBs                             | dBm         | -100 | -94.3                  |

| LTE Band 4                               | <b>RX</b> Sensitivity                  | 10 MHz with 50 RBs                             | dBm         | -102 | -96.3                  |

| LTE Band 5                               | RX Sensitivity                         | 10 MHz with 50 RBs                             | dBm         | -102 | -94.3                  |

| LTE Band 12                              | RX Sensitivity                         | 10 MHz with 50 RBs                             | dBm         | -103 | -93.3                  |

| LTE Band 13                              | <b>RX</b> Sensitivity                  | 10 MHz with 50 RBs                             | dBm         | -102 | -93.3                  |

| <b>LTE Band 14</b><br>Note: 1. The RF Re | RX Sensitivity<br>ceiver Specification | 10 MHz with 50 RBs<br>on is defined at the LGA | dBm<br>pad. | -102 | -93.3                  |

2. Meet 3GPP TS 36.521-1/TS 34.121-1 test standard.

#### Table 13. Conductive Rx sensitivity-CITA

The below table show the sensitivity data of primary only and second only which is defined in the **CITA Test Plan for Wireless Device Over-the-Air Performance V 3.5.2 Table 6-6.**This data could be the reference in the OTA performance evaluation.

|--|

|    |      | 650  | 1935   | 50 RB with | 50 RB with | -98.5 | -98    |

|----|------|------|--------|------------|------------|-------|--------|

|    |      | 050  | 1992   | RBstart=0  | RBstart=0  | -90.5 | -50    |

| 2  | 10   | 900  | 1960   | 50 RB with | 50 RB with | -99   | -99    |

| 2  | . 10 | 500  | 1500   | RBstart=0  | RBstart=0  | 55    | 55     |

|    |      | 1150 | 1985   | 50 RB with | 50 RB with | -98.5 | -99    |

|    |      | 1150 | 1909   | RBstart=0  | RBstart=0  | 50.5  | 33     |

|    |      | 2000 | 2115   | 50 RB with | 50 RB with | -98.0 | -99    |

|    |      |      |        | RBstart=0  | RBstart=0  |       |        |

| 4  | . 10 | 2175 | 2132.5 | 50 RB with | 50 RB with | -99.0 | -99    |

|    | -    | -    |        | RBstart=0  | RBstart=0  |       |        |

|    |      | 2350 | 2150   | 50 RB with | 50 RB with | -98.5 | -99    |

|    |      |      |        | RBstart=0  | RBstart=0  |       |        |

|    |      | 2450 | 874    | 25 RB with | 50 RB with | -99   | -99.5  |

|    |      |      |        | RBstart=25 | RBstart=0  |       |        |

| 5  | 10   | 2525 | 881.5  | 25 RB with | 50 RB with | -99.5 | -100.0 |

|    |      |      |        | RBstart=25 | RBstart=0  |       |        |

|    |      | 2600 | 889    | 25 RB with | 50 RB with | -99   | -100.5 |

|    |      |      |        | RBstart=25 | RBstart=0  |       |        |

|    |      | 5035 | 731.5  | 20 RB with | 25 RB with | -102  | -103   |