# CVDM-2000 Cellular Voice/Data/GPS Module Theory of Operation

**General:** CVDM-2000 is a class I, 3 Watt cellular transceiver board, which operates according to AMPS cellular Standards EIA/TIA 553 and IS19B, that has been integrated with a global positioning system (GPS) receiver, modem and power management system. It is a mobile communications and tracking device that is used for vehicle and asset management.

The 3-Watt cellular transceiver design is identical to our CVDM-3 module (FCC ID: NJI CVDM-3). The CVDM-2000 module was created by extending the board outline of the existing CVDM-3 PCB design and adding the supplementary circuitry required to support the GPS receiver and power management system. Additionally, the modem was moved off of a daughter board and onto the main PCB and several digital I/O and A/D converter inputs were provided.

The receiver consists of a dual conversion superheterodyne receiver circuit as described in section V.2 below. The transmitter consists of a direct modulation of a VCO, which is upconverted by a second oscillator to transmit at the carrier frequency. A programmable power amplifier increases the power level to up to 3 Watts. More detail description of the transmitter is given in section V.3. The calibration and tune up procedure for the transceiver are described in section VII.

All call processing and control functions are performed by the software running on the ACE9050 CPU as described in section V.4.

The GPS receiver, modem, power management system, digital I/O and A/D converter inputs are all controlled be a dedicated function control processor (FCP), as described in section V.5.

The GPS receiver is an OEM module, purchased from Trimble Navigations, as described in section V.6.

During periods when the vehicle engine is not running, the CVDM-2000 generally operates solely on a 12V, 2AH sealed lead acid back-up battery. When the vehicle engine is running, a built-in battery charger, which uses the vehicle battery as it's input voltage source, is used to recharge the back-up battery. When the cellular transmitter is on and operating at the maximum output level of 3 Watts, the CVDM-2000 consumes up to 1.5 amps

The functions of all of the critical circuit devices are described in detail in section VI.

V.2. Receiver: Receiver chain includes a front-end RF amplifier, a SAW filter, another RF amplifier, and a mixer, which converts the signal to a 45 MHz IF. This first IF signal is filtered by a 4 pole band pass crystal, the output of which is amplified and mixed down

to a 450 kHz second IF. This signal is digitally demodulated to base band. The base band signal is processed by the audio processor chip described in section VI. See the schematics in section IV for more detail.

**V.3. Transmitter:** The transmit signal is processed in base band by the audio processor chip. It's output modulates the transmit VCO. The output of the VCO is mixed with the local oscillator to up covert tot he carrier frequency. It is then filtered by a SAW band pass filter and amplified before feeding the power amplifier. The output of the power amplifier is then filtered by the duplexer, which is connected to the antenna connector. See the schematics in section IV for more detail.

V.4 CPU: The AMPS, CPU functions are performed by the ACE9050 chip described in section VI. The software consists if a dual tasking operating system (DTOS), a foreground task performing all of the call processing functions and a background task controlling the test and configuration functions. See the schematics in section IV for more detail.

V.5 FCP: The CVDM2000 primary system controller is the Hitachi H8/3644 Function Control Processor (FCP) described in section VI. The FCP is responsible for power management functions, scheduling the various activities such as GPS position fixes and cellular phone calls, maintaining the Real-Time Clock (RTC), and monitoring/controlling external I/O. The software consists of a single main-loop application process. Real-time issues are handled either directly through interrupt handlers or with the use of a 2 msec interval timer which provides a set of software timers used to guarantee periodic service. See the schematics in section IV for more detail.

**V.6 GPS Module:** The GPS module is Lassen-SK8 board which is purchased as an OEM unit from Trimble Navigations. It has an 8 channel, continuous tracking receiver and 32 correlators. The module is screwed onto the CVDM-2000 module and the I/O interface to the Hitachi FCP is made through an 8 pin header. See the applications information provided in section VI for more detail.

Tracking &

Communication

Products

# Lassen-SK GPS Board for Fast Integratio

Highest performance, smaller size, and lower power consumption for embedded application

Introducing the Lassen-SK8 GPS board, Trimble's new OEM GPS module for embedded applications based on Sierra GPS technology. Using the latest 8-channel technology, Lassen-SK8 offers the highest performance available through a miniature GPS receiver. Two-thirds the size of a business card, Lassen-SK8's extremely low power consumption, 20-second hot acquisition capabilities, and two-meter differential accuracy readings make it the choice for demanding applications.

Lassen-SK8's power consumption is a mere 0.75 watts. This means that battery-powered GPS applications can start up and calculate positions with less power than any other module available today. With the fastest reacquisition time available,

Lassen-SK8 also delivers position data faster and more often. Lassen-SK8 even provides this information in areas where satellite signals are inhibited by terrain and structures.

If your application requires differential GPS accuracy, Lassen-SK8 is more than ready. Using industry standard RTCM SC-104 correction data or TSIP format corrections, Lassen-SK8 provides the highest level of DGPS available in a miniature GPS receiver. The optional full-measurement feature positions you well ahead of the competition.

Dual serial I/O ports mean greater flexibility and faster integration. One serial port uses Trimble's renowned TSIP binary data protocol to provide maximum data and control over your GPS receiver. The second port

outputs your choice of NMEA 0183 Version 2.1 standard data messages and receives RTCM SC-104 differential corrections. While TSIP data packets are output once each second, you can configure NMEA messages to output anywhere from once per second to once every 20 seconds. Use TSIP commands to configure and permanently store your serial port settings and NMEA data selections.

Lassen-SK8's Starter Kit provides everything you need to get started integrating state-of-the-art GPS into your application. The new 12-volt, RS-232 interface module and Toolkit Software included in the Starter Kit make the Lassen-SK8 GPS board computer-ready for your evaluation.

**3.** Trimble

Actual size

# Lassen<sup>™</sup>SK8

# GPS Board for Fast Integration

#### Performance Specifications

L1 frequency, C/A code (SPS), 8-channel, General:

continuous tracking receiver, 32 correlators

Position: 25 m CEP (50%) without SA

TSIP @ 1 Hz; NMEA @ 1 Hz Update rate:

Velocity: 0.1 m/sec without SA

Time: ±500 nano-seconds (nominal)

Position: 2 m CEP (50%) DGPS accuracy:

Velocity: 0.05 m/sec

Time: ±500 nano-seconds (nominal)

Acquisition (typical): Cold start: <2 minutes (90%)

Warm start: <45 seconds (90%) Hot start: <20 seconds (90%)

Cold start requires no initialization. Warm start implies last position, time and almanac are saved by back-up power. Hot start implies ephemeris also saved.

Reacouisition

Accuracy:

< 2 seconds (90%) after signal loss.

Altitude: -1000 m to +18,000 m Dynamics:

> Velocity: 515 m/sec maximum Acceleration: 4g (39.2 m/sec2) Motional Jerk: 20 m/sec3

## **Environmental Specifications**

-10°C to +60°C (standard) Operating temp:

-40°C to +85°C (optional)

-55°C to +100°C Storage temp:

0.008g2/Hz 5 Hz to 20 Hz Vibration

$\begin{array}{lll} 0.05g^2/Hz & 20~Hz~to~100~Hz\\ 3dB/octave & 100~Hz~to~900~Hz \end{array}$

Operating humidity: 5% to 95% R.H. non-condensing, @60°C

-400 m to +18,000 m Altitude:

## Physical Characteristics

+5 volts DC, ±5% Prime power:

Power consumption

GPS board only: 150 ma, 0.75 watts (nominal):

With antenna: 175 ma, 0.88 watts

+3.2 to +5 volts DC Back-up power:

2 micro-amp @ +3.5 volts, +25°(nominal)

CMOS TTL levels Serial ports/1PPS:

TSIP @ 9600 baud, 8-Odd-1 Protocols:

NMEA 0183 v2.1 @ 4800 baud, 8-None-1 RTCM SC-104 @ 4800 baud, 8-None-1

GGA, VTG, GLL, ZDA, GSV, GSA NMEA messages

and RMC messages selectable by TSIP command; selection stored in non-

volatile memory

5V at 25mA available Antenna power:

Short circuit protection Feedline fault detection

## Physical Characteristics

3.25" L x 1.25" W x 0.40" H Dimensions:

(82.6 mm x 31.2 mm x 10.2 mm)

without connectors

3.29" L x 1.30" W x 0.52" H (83.6 mm x 33.0 mm x 13.2 mm) with connectors and optional shield

0.7 oz. (19.6 g) without optional shield Weight:

1.3 oz. (36.4 g) with optional shield

RF: SMB; I/O: 8-pin (2x4), 0.100" header Connectors:

#### Accessories

GPS antenna: Compact, active micropatch antenna with 5-meter cable and magnetic mount. 1.60" x 1.90" x 0.55" high (40.6 mm x 48.3 mm x 13.9 mm)

Hard mount antenna: Compact, hard mount, active micropatch antenna with single-hole 0.75" threaded mount and TNC connector. 2.46" diameter x 0.75" high

(62.6 mm x 19.0 mm)

Rooftop antenna: Bullet antenna with 22-meter cable and SMB adapter

RF shield Optional snap-on metal cover for severe RF environments

# Ordering Information

Modules:

Standard Temperature, TSIP (binary) protocol 28835-00 and NMEA 0183 (ASCII) protocol, DGPS ready

Extended Temperature, TSIP (binary) protocol 28835-50 and NMEA 0183 (ASCII) protocol, DGPS ready

Antennas:

28367-00 26 dB magnetic mount antenna, 5-meter cable 28367-70 26 dB hard mount antenna, TNC connector 23726-00 35 dB rooftop Bullet antenna, 23-meter cable

Starter Kit:

29467-00 Includes Lassen-SK8 board, interface motherboar

in durable metal enclosure with dual DB9, RS-232 interface, AC/DC power converter, magnetic mount antenna, TSIP and NMEA protocols, software toolkit for TSIP, interface cable, and manual

Manual:

29473-00 Lassen-SK8 System Designer Reference Guide

## Section 1 Overview

#### 1.1 Overview

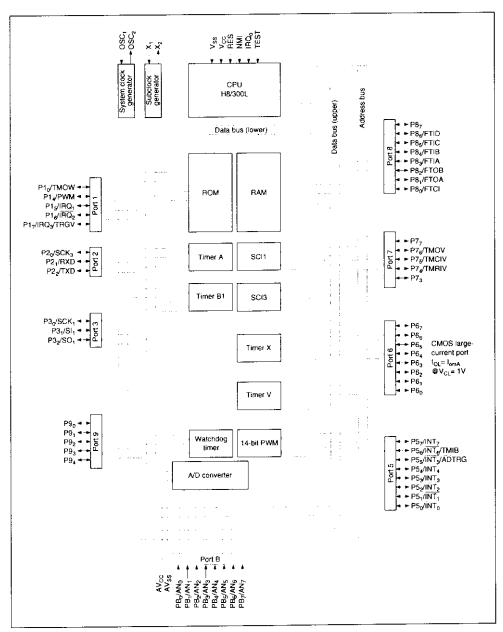

The H8/300L Series is a series of single-chip microcomputers (MCU: microcomputer unit), built around the high-speed H8/300L CPU and equipped with peripheral system functions on-chip.

Within the H8/300L Series, the H8/3644 Series of microcomputers are equipped with a UART (Universal Asynchronous Receiver/Transmitter). Other on-chip peripheral functions include five timers, a 14-bit pulse width modulator (PWM), two serial communication interface channels, and an A/D converter. Together, these functions make the H8/3644 Series ideally suited for embedded applications in advanced control systems. The ZTAT<sup>TM\*</sup> versions of the H8/3644 come with user-programmable PROM. Table 1 summarizes the features of the H8/3644 Series.

Table 1 summarizes the features of the H8/3927 Series.

Note: \* ZTAT is a trademark of Hitachi, Ltd.

Table 1-1 Features

| Item | Description                                                                        |

|------|------------------------------------------------------------------------------------|

| CPU  | High-speed H8/300L CPU                                                             |

|      | General-register architecture                                                      |

|      | General registers: Sixteen 8-bit registers (can be used as eight 16-bit registers) |

|      | Operating speed                                                                    |

|      | <ul> <li>— Max. operating speed: 5 MHz</li> </ul>                                  |

|      | <ul> <li>— Add/subtract: 0.4 μs (operating at 5 MHz)</li> </ul>                    |

|      | <ul> <li>— Multiply/divide: 2.8 μs (operating at 5 MHz)</li> </ul>                 |

|      | — Can run on 32.768 kHz subclock                                                   |

|      | <ul> <li>Instruction set compatible with H8/300 CPU</li> </ul>                     |

|      | <ul> <li>Instruction length of 2 bytes or 4 bytes</li> </ul>                       |

|      | <ul> <li>Basic arithmetic operations between registers</li> </ul>                  |

|      | <ul> <li>MOV instruction for data transfer between memory and registers</li> </ul> |

|      | Typical instructions                                                               |

|      | - Multiply (8 bits × 8 bits)                                                       |

|      | — Divide (16 bits + 8 bits)                                                        |

|      | — Bit accumulator                                                                  |

|      | Register-indirect designation of bit position                                      |

Table 1-1 Features (cont)

| Item                   | Description                                                                                                                                                           |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupts             | 33 interrupt sources                                                                                                                                                  |

|                        | <ul> <li>12 external interrupt sources (IRQ<sub>3</sub> to IRQ<sub>0</sub>, INT<sub>7</sub> to INT<sub>0</sub>)</li> </ul>                                            |

|                        | 21 internal interrupt sources                                                                                                                                         |

| Clock pulse generators | Two on-chip clock pulse generators                                                                                                                                    |

|                        | System clock pulse generator: 1 to 10 MHz                                                                                                                             |

|                        | Subclock pulse generator: 32,768 kHz                                                                                                                                  |

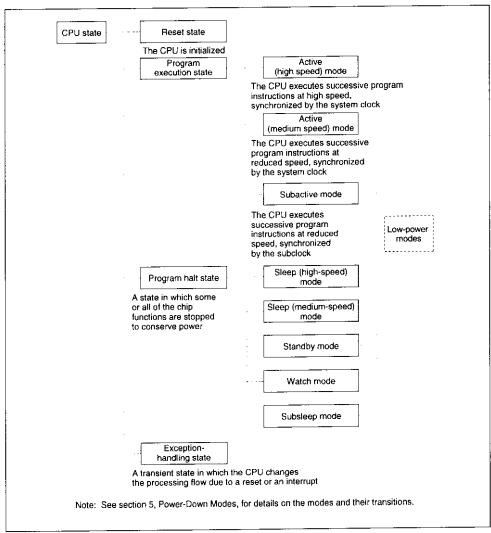

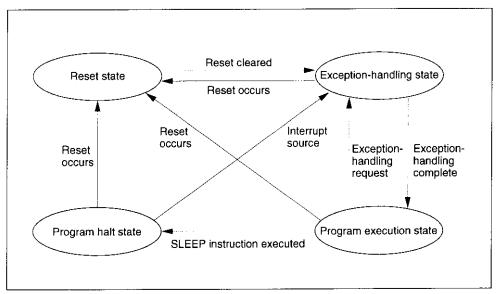

| Power-down modes       | Seven power-down modes                                                                                                                                                |

|                        | Sleep (high-speed) mode                                                                                                                                               |

|                        | Sleep (medium-speed) mode                                                                                                                                             |

|                        | Standby mode                                                                                                                                                          |

|                        | Watch mode                                                                                                                                                            |

|                        | Subsleep mode                                                                                                                                                         |

|                        | Subactive mode                                                                                                                                                        |

|                        | Active (medium-speed) mode                                                                                                                                            |

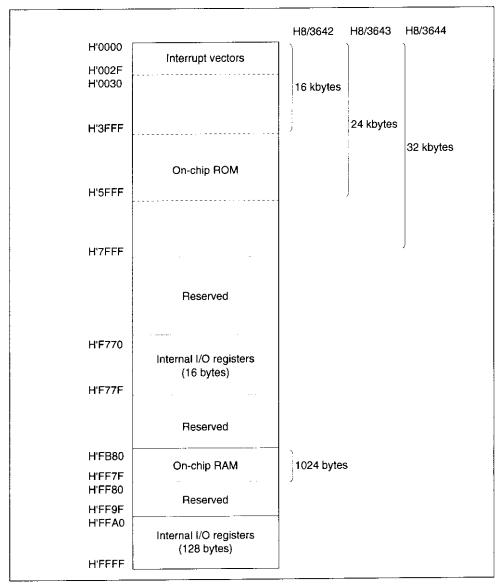

| Memory                 | Large on-chip memory                                                                                                                                                  |

|                        | • H8/3644: 32-kbyte ROM, 1-kbyte RAM                                                                                                                                  |

|                        | H8/3643: 24-kbyte ROM, 1-kbyte RAM                                                                                                                                    |

|                        | H8/3642: 16-kbyte ROM, 512 byte RAM                                                                                                                                   |

|                        | <ul> <li>H8/3641: 12-kbyte ROM, 512 byte RAM</li> </ul>                                                                                                               |

|                        | H8/3640: 8-kbyte ROM, 512 byte RAM                                                                                                                                    |

| I/O ports              | 53 pins                                                                                                                                                               |

|                        | • 45 I/O pins                                                                                                                                                         |

|                        | 8 input pins                                                                                                                                                          |

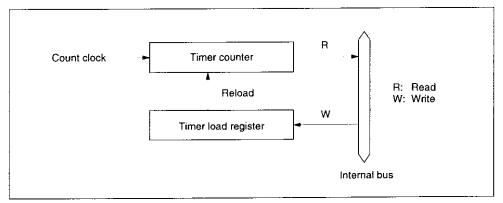

| Timers                 | Five on-chip timers                                                                                                                                                   |

|                        | Timer A: 8-bit timer                                                                                                                                                  |

|                        | Count-up timer with selection of eight internal clock signals divided from the system clock (Ø)* and four clock signals divided from the watch clock (Ø $_{\rm w}$ )* |

|                        | Timer B1: 8-bit timer                                                                                                                                                 |

|                        | <ul> <li>Count-up timer with selection of seven internal clock signals or event<br/>input from external pin</li> </ul>                                                |

|                        | — Auto-reloading                                                                                                                                                      |

|                        | Note: *ø and øw are defined in section 4, Clock Pulse Generators.                                                                                                     |

Table 1-1 Features (cont)

| Item                 | Description                                                                                                            |  |  |  |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Timers               | Timer V: 8-bit timer                                                                                                   |  |  |  |  |  |  |

|                      | <ul> <li>Count-up timer with selection of six internal clock signals or event input<br/>from external pin</li> </ul>   |  |  |  |  |  |  |

|                      | <ul> <li>Compare-match waveform output</li> </ul>                                                                      |  |  |  |  |  |  |

|                      | Externally triggerable                                                                                                 |  |  |  |  |  |  |

|                      | Timer X: 16-bit timer                                                                                                  |  |  |  |  |  |  |

|                      | <ul> <li>Count-up timer with selection of three internal clock signals or event<br/>input from external pin</li> </ul> |  |  |  |  |  |  |

|                      | Output compare (2 output pins)                                                                                         |  |  |  |  |  |  |

|                      | — Input capture (4 input pins)                                                                                         |  |  |  |  |  |  |

|                      | Watchdog timer                                                                                                         |  |  |  |  |  |  |

|                      | <ul> <li>Reset signal generated by 8-bit counter overflow</li> </ul>                                                   |  |  |  |  |  |  |

|                      | Note: * See section 4, Clock Pulse Generator for the definitions of $\emptyset$ and $\emptyset_W$ .                    |  |  |  |  |  |  |

| Serial communication | Two channels on chip                                                                                                   |  |  |  |  |  |  |

| interface            | SCI1: synchronous serial interface                                                                                     |  |  |  |  |  |  |

|                      | Choice of 8-bit or 16-bit data transfer                                                                                |  |  |  |  |  |  |

|                      | SCI3: 8-bit synchronous/asynchronous serial interface                                                                  |  |  |  |  |  |  |

|                      | Incorporates multiprocessor communication function                                                                     |  |  |  |  |  |  |

| 14-bit PWM           | Pulse-division PWM output for reduced ripple                                                                           |  |  |  |  |  |  |

|                      | Can be used as a 14-bit D/A converter by connecting to an external low-pass filter.                                    |  |  |  |  |  |  |

| A/D converter        | Successive approximations using a resistance ladder                                                                    |  |  |  |  |  |  |

|                      | 8-channel analog input pins                                                                                            |  |  |  |  |  |  |

|                      | Conversion time: 31/ø or 62/ø per channel                                                                              |  |  |  |  |  |  |

Table 1-1 Features (cont)

| Item | Specification |

|------|---------------|

| item           | Specification       |                              |                                |                         |                                  |  |

|----------------|---------------------|------------------------------|--------------------------------|-------------------------|----------------------------------|--|

| Product lineup | 1                   | Product Code                 |                                |                         |                                  |  |

|                | Mask ROM<br>Version | ZTAT <sup>™</sup><br>Version | F-ZTAT <sup>®</sup><br>Version | Package                 | ROM/RAM Size                     |  |

|                | HD6433644H          | HD6473644H<br>-              | HD64F3644H                     | 64-pin QFP<br>(FP-64A)  | ROM: 32 kbytes<br>RAM: 1 kbyte   |  |

|                | HD6433643H          | _                            | HD64F3644P                     |                         | ROM: 24 kbytes<br>RAM: 1 kbyte   |  |

|                | HD6433642H          | _                            | _                              |                         | ROM: 16 kbytes<br>RAM: 1 kbyte   |  |

|                | HD643341H           |                              | _                              |                         | ROM: 12 kbytes<br>RAM: 512 bytes |  |

|                | HD6433644P          | HD6473644P                   | _                              | 64-pin SDIP<br>(DP-64S) | ROM: 32 kbytes<br>RAM: 1 kbyte   |  |

|                | HD6433643P          | _                            | _                              |                         | ROM: 24 kbytes<br>RAM: 1 kbyte   |  |

|                | HD6433642P          | <b></b>                      |                                |                         | ROM: 16 kbytes<br>RAM: 512 bytes |  |

|                | HD643341P           | _                            | _                              |                         | ROM: 12 kbytes<br>RAM: 512 bytes |  |

|                | HD6433640H          | _                            | _                              | 64-pin QFP<br>(FP-64A)  | ROM: 8 kbytes<br>RAM: 512 bytes  |  |

|                | HD6433640P          | -                            | _                              | 64-pin SDIP<br>(DP-64S) |                                  |  |

#### 1.2 Internal Block Diagram

Figure 1-1 shows a block diagram of the H8/3644 Series.

Figure 1-1 Block Diagram

# 1.3 Pin Arrangement and Functions

#### 1.3.1 Pin Arrangement

The H8/3644 Series pin arrangement is shown in figures 1-2 and 1-3.

|                                    | PB <sub>2</sub> /AN <sub>2</sub> | PB <sub>3</sub> /AN <sub>3</sub> | PB4/AN4 | PB5/AN5 | PB <sub>6</sub> /AN <sub>6</sub> | PB <sub>7</sub> /AN <sub>7</sub> | AVcc | P17/IRQ3/TRGV | P16/IRQ2                          | P1 <sub>5</sub> /IRQ <sub>1</sub> | P14/PWM  | P1 <sub>0</sub> /TMOW             | P3 <sub>0</sub> /SCK <sub>1</sub> | P3 <sub>1</sub> /SI <sub>1</sub> | P3 <sub>2</sub> /SO <sub>1</sub>        | P2 <sub>2</sub> /TXD              |      |

|------------------------------------|----------------------------------|----------------------------------|---------|---------|----------------------------------|----------------------------------|------|---------------|-----------------------------------|-----------------------------------|----------|-----------------------------------|-----------------------------------|----------------------------------|-----------------------------------------|-----------------------------------|------|

| PB <sub>1</sub> /AN <sub>1</sub> 1 | 49                               | 64                               | 62      | 6.      | . 09                             | 59                               | 58   | 57            | 26                                | 55                                | 54       | 53                                | 25                                | 5                                | 20                                      | ∯ 48 : P2₁/RX                     | D    |

| PB <sub>0</sub> /AN <sub>0</sub> 2 |                                  |                                  |         |         |                                  |                                  |      |               |                                   |                                   |          |                                   |                                   |                                  |                                         | 47 P2 <sub>0</sub> /SC            |      |

| AV <sub>SS</sub> 3                 |                                  |                                  |         |         |                                  |                                  |      |               |                                   |                                   |          |                                   |                                   |                                  |                                         | 46 ⊟ P8 <sub>7</sub>              |      |

| TEST 4                             |                                  |                                  |         |         |                                  |                                  |      |               |                                   |                                   |          |                                   |                                   |                                  |                                         | 45 P8 <sub>6</sub> /FT            | ID   |

| X <sub>2</sub> 5                   |                                  |                                  |         |         |                                  |                                  |      |               |                                   |                                   |          |                                   |                                   |                                  |                                         | 44 P8 <sub>5</sub> /FT            | IC   |

| X <sub>1</sub> 6                   |                                  |                                  |         |         |                                  |                                  |      |               |                                   |                                   |          |                                   |                                   |                                  |                                         | 43   P8 <sub>4</sub> /FT          | IB   |

| V <sub>SS</sub> [ ]7               |                                  |                                  |         |         |                                  |                                  |      |               |                                   |                                   |          |                                   |                                   |                                  |                                         | 42 P8 <sub>3</sub> /FT            | IA   |

| OSC <sub>1</sub> [] 8              |                                  |                                  |         |         |                                  |                                  |      |               |                                   |                                   |          |                                   |                                   |                                  |                                         | 41 P8 <sub>2</sub> /FT            | ОВ   |

| OSC <sub>2</sub> [ ] 9             |                                  |                                  |         |         |                                  |                                  |      |               |                                   |                                   |          |                                   |                                   |                                  |                                         | 40 P8 <sub>1</sub> /FT            | OA   |

| RES 10                             |                                  |                                  |         |         |                                  |                                  |      |               |                                   |                                   |          |                                   |                                   |                                  |                                         | 39 P8 <sub>0</sub> /FT            | CI   |

| P9 <sub>0</sub> 11                 |                                  |                                  |         |         |                                  |                                  |      |               |                                   |                                   |          |                                   |                                   |                                  |                                         | 38 P7 <sub>7</sub>                |      |

| P9 <sub>1</sub> 12                 |                                  |                                  |         |         |                                  |                                  |      |               |                                   |                                   |          |                                   |                                   |                                  |                                         | 37 P7 <sub>6</sub> /TM            |      |

| P9 <sub>2</sub> 13                 |                                  |                                  |         |         |                                  |                                  |      |               |                                   |                                   |          |                                   |                                   |                                  |                                         | 36 P7 <sub>5</sub> /TM            |      |

| P9 <sub>3</sub> 14                 |                                  |                                  |         |         |                                  |                                  |      |               |                                   |                                   |          |                                   |                                   |                                  |                                         | 35 . P7₄/TM                       | IRIV |

| P9 <sub>4</sub> 15                 |                                  |                                  |         |         |                                  |                                  |      |               |                                   |                                   |          |                                   |                                   |                                  |                                         | 34 P7 <sub>3</sub>                |      |

| IRQ <sub>0</sub> 16                | 17                               | 8                                | 6       | 50      | 21                               | 22                               | 23   | 24            | . 25                              | 56                                | 27       | . 28                              | 53                                | 30                               | 33                                      | 33 V <sub>CC</sub>                |      |

|                                    | <br>09.                          | <br>194                          | <br>9   |         | P64                              | 965                              | 9    | P6,           | . ∘                               | Ŧ,                                | 2        | Τ3                                | Ę                                 | P.G                              | B                                       | T7.                               |      |

|                                    | а.                               | ₾.                               | Œ.      | а.      | ı.                               | <u>n</u>                         | u_   | ı.            | P5 <sub>0</sub> /INT <sub>0</sub> | $P5_1/\bar{l}N$                   | P52/INT2 | P5 <sub>3</sub> /INT <sub>3</sub> | P54/INT4                          | /ADTI                            | Te/T                                    | P5 <sub>7</sub> /INT <sub>7</sub> |      |

|                                    |                                  |                                  |         |         |                                  |                                  |      |               | _                                 | _                                 | _        | _                                 | _                                 | P5g/INTg/ADTRG                   | P5 <sub>6</sub> /INT <sub>6</sub> /TMIB |                                   |      |

Figure 1-2 Pin Arrangement (FP-64A: Top View)

| P1 <sub>7</sub> /IRQ <sub>9</sub> /TRGV : 1 | 64 P1 <sub>6</sub> /IRQ <sub>2</sub>       |

|---------------------------------------------|--------------------------------------------|

| AV <sub>CC</sub> 2                          | 63 P1₅/IRQ₁                                |

| PB <sub>7</sub> /AN <sub>7</sub> : , 3      | 62 P1 <sub>4</sub> /PWM                    |

| PB <sub>6</sub> /AN <sub>6</sub> 4          | 61 P1 <sub>0</sub> /TMOW                   |

| PB <sub>5</sub> /AN <sub>5</sub> 5          | 60 P3 <sub>0</sub> /SCK <sub>1</sub>       |

| PB <sub>4</sub> /AN <sub>4</sub> 6          | 59 P3 <sub>1</sub> /SI <sub>1</sub>        |

| PB <sub>3</sub> /AN <sub>3</sub> ,7         | 58 P3 <sub>2</sub> /SO <sub>1</sub>        |

| PB <sub>2</sub> /AN <sub>2</sub> 8          | 57 P2 <sub>2</sub> /TXD                    |

| PB <sub>1</sub> /AN <sub>1</sub> 9          | 56 P2 <sub>1</sub> /RXD                    |

| PB <sub>0</sub> /AN <sub>0</sub> 10         | 55   P2 <sub>0</sub> /SCK <sub>3</sub>     |

| AV <sub>SS</sub> 11                         | 54 P8 <sub>7</sub>                         |

| TEST 12                                     | 53 P8 <sub>6</sub> /FTID                   |

| X <sub>2</sub> : 13                         | 52 P8 <sub>5</sub> /FTIC                   |

| X <sub>1</sub> [ ] 14                       | 51 P8 <sub>4</sub> /FTIB                   |

| V <sub>S\$</sub> :, 15                      | 50 P8 <sub>3</sub> /FTIA                   |

| OSC <sub>1</sub> 16                         | 49 P8 <sub>2</sub> /FTOB                   |

| OSC <sub>2</sub> 17                         | 48 P8 <sub>1</sub> /FTOA                   |

| RES                                         | 47 P8 <sub>0</sub> /FTCI                   |

| P9 <sub>0</sub> [ ] 19                      | 46 P7 <sub>7</sub>                         |

| P9 <sub>1</sub> 20                          | 45 P7 <sub>6</sub> /TMOV                   |

| P9 <sub>2</sub> 21                          | 44 : P7 <sub>5</sub> /TMCIV                |

| P9 <sub>3</sub> 22                          | 43   P7 <sub>4</sub> /TMRIV                |

| P9 <sub>4</sub> 23                          | 42 P7 <sub>3</sub>                         |

| IRQ <sub>0</sub>                            | 41 V <sub>CC</sub>                         |

| P6 <sub>0</sub> :  ]25                      | 40 P5 <sub>7</sub> /INT <sub>7</sub>       |

| P6 <sub>1</sub> : 26                        | 39 P5 <sub>6</sub> /INT <sub>6</sub> /TMIB |

| P6 <sub>2</sub> 27                          | 38 P5 <sub>5</sub> /INT <sub>5</sub> /ADTR |

| P6 <sub>3</sub> 28                          | 37 P5 <sub>4</sub> /INT <sub>4</sub>       |

| P6 <sub>4</sub> 29                          | 36 P5 <sub>3</sub> /INT <sub>3</sub>       |

| P6 <sub>5</sub> 30                          | 35 P5 <sub>2</sub> /INT <sub>2</sub>       |

| P6 <sub>6</sub> 31                          | 34 P5 <sub>1</sub> /INT <sub>1</sub>       |

| P6 <sub>7</sub> 32                          | 33   P5 <sub>0</sub> /INT <sub>0</sub>     |

|                                             |                                            |

#### 1.3.2 Pin Functions

Table 1-2 outlines the pin functions of the H8/3644 Series.

Table 1-2 Pin Functions

|                   |                  | Pir    | No.    | _      |                                                                                                                                                                  |  |  |  |  |

|-------------------|------------------|--------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Туре              | Symbol           | FP-64A | DP-64S | I/O    | Name and Functions                                                                                                                                               |  |  |  |  |

| Power source pins | V <sub>CC</sub>  | 33     | 41     | Input  | Power supply: All V <sub>CC</sub> pins should be connected to the system power supply (+5 V)                                                                     |  |  |  |  |

|                   | V <sub>SS</sub>  | 7      | 15     | Input  | <b>Ground:</b> All V <sub>SS</sub> pins should be connected to the system power supply (0 V)                                                                     |  |  |  |  |

|                   | AV <sub>CC</sub> | 58     | 2      | Input  | Analog power supply: This is the power supply pin for the A/D converter. When the A/D converter is not used, connect this pin to the system power supply (+5 V). |  |  |  |  |

|                   | AV <sub>SS</sub> | 3      | 11     | Input  | Analog ground: This is the A/D converter ground pin. It should be connected to the system power supply (0 V).                                                    |  |  |  |  |

| Clock pins        | OSC <sub>1</sub> | 8      | 16     | Input  | System clock: These pins connect to a                                                                                                                            |  |  |  |  |

|                   | OSC <sub>2</sub> | 9      | 17     | Output | crystal or ceramic oscillator, or can be used to input an external clock.  See section 4, Clock Pulse  Generators, for a typical connection diagram.             |  |  |  |  |

|                   | X <sub>1</sub>   | 6      | 14     | Input  | Subclock: These pins connect to a                                                                                                                                |  |  |  |  |

|                   | X <sub>2</sub>   | 5      | 13     | Output | 32.768-kHz crystal oscillator. See section 4, Clock Pulse Generators, for a typical connection diagram.                                                          |  |  |  |  |

| System control    | RES              | 10     | 18     | Input  | Reset: When this pin is driven low, the chip is reset                                                                                                            |  |  |  |  |

|                   | TEST             | 4      | 12     | Input  | <b>Test:</b> This is a test pin, not for use in application systems. It should be connected to V <sub>SS</sub> .                                                 |  |  |  |  |

Table 1-2 Pin Functions (cont)

Pin No.

|                   |                                                                              | PII                  | i NO.               |        |                                                                                                                                       |

|-------------------|------------------------------------------------------------------------------|----------------------|---------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| Туре              | Symbol                                                                       | FP-64A               | DP-64S              | 1/0    | Name and Functions                                                                                                                    |

| Interrupt<br>pins | IRQ <sub>0</sub><br>IRQ <sub>1</sub><br>IRQ <sub>2</sub><br>IRQ <sub>3</sub> | 16<br>55<br>56<br>57 | 24<br>63<br>64<br>1 | Input  | IRQ interrupt request 0 to 3: These are input pins for edge-sensitive external interrupts, with a selection of rising or falling edge |

|                   | INT <sub>7</sub> to                                                          | 24 to<br>17          | 32 to<br>25         | Input  | INT interrupt request 0 to 7: These are input pins for edge-sensitive external interrupts, with a selection of rising or falling edge |

| Timer pins        | TMOW                                                                         | 53                   | 61                  | Output | Clock output: This is an output pin for waveforms generated by the timer A output circuit                                             |

|                   | TMIB                                                                         | 23                   | 31                  | Input  | Timer B1 event counter input: This is an event input pin for input to the timer B1 counter                                            |

|                   | TMOV                                                                         | 37                   | 45                  | Output | Timer V output: This is an output pin for waveforms generated by the timer V output compare function                                  |

|                   | TMCIV                                                                        | 36                   | 44                  | Input  | Timer V event input: This is an event input pin for input to the timer V counter                                                      |

|                   | TMRIV                                                                        | 35                   | 43                  | Input  | Timer V counter reset: This is a counter reset input pin for timer V                                                                  |

|                   | TRGV                                                                         | 57                   | 1                   | Input  | Timer V counter trigger input: This is a trigger input pin for the timer V counter and realtime output port                           |

|                   | FTCI                                                                         | 39                   | 47                  | Input  | Timer X clock input: This is an external clock input pin for input to the timer X counter                                             |

| Interrupt<br>pins | FTOA                                                                         | 40                   | 48                  | Output | Timer X output compare A output:<br>This is an output pin for timer X output<br>compare A                                             |

|                   | FTOB                                                                         | 41                   | 49                  | Output | Timer X output compare B output:<br>This is an output pin for timer X output<br>compare B                                             |

|                   | FTIA                                                                         | 42                   | 50                  | Input  | Timer X input capture A input: This is an input pin for timer X input capture B                                                       |

|                   | FTIB                                                                         | 43                   | 51                  | Input  | Timer X input capture B input: This is an input pin for timer X input capture B                                                       |

|                   | FTIC                                                                         | 44                   | 52                  | Input  | Timer X input capture C input: This is an input pin for timer X input capture C                                                       |

Table 1-2 Pin Functions (cont)

|                   |                                                         | Pir                 | No.            |        |                                                                                                                              |

|-------------------|---------------------------------------------------------|---------------------|----------------|--------|------------------------------------------------------------------------------------------------------------------------------|

| Туре              | Symbol                                                  | FP-64A              | DP-64S         | 1/0    | Name and Functions                                                                                                           |

| Timer pins        | FTID                                                    | 45                  | 53             | Input  | Timer X input capture C input: This is an input pin for timer X input capture D                                              |

| 14-bit<br>PWM pin | PWM                                                     | 54                  | 62             | Output | 14-bit PWM output: This is an output pin for waveforms generated by the 14-bit PWM                                           |

| I/O ports         | PB <sub>7</sub> to<br>PB <sub>0</sub>                   | 59 to 64,<br>1 to 2 | 3 to 10        | Input  | Port B: This is an 8-bit input port                                                                                          |

|                   | P1 <sub>7</sub> to P1 <sub>4</sub> ,<br>P1 <sub>0</sub> | 57 to<br>53         | 1, 64 to<br>61 | 1/0    | Port 1: This is a 5-bit I/O port. Input or output can be designated for each bit by means of port control register 1 (PCR1)  |

|                   | P2 <sub>2</sub> to P2 <sub>0</sub>                      | 49 to<br>47         | 57 to<br>55    | I/O    | Port 2: This is a 3-bit I/O port. Input or output can be designated for each bit by means of port control register 2 (PCR2)  |

|                   | P3 <sub>2</sub> to<br>P3 <sub>0</sub>                   | 50 to<br>52         | 58 to<br>60    | I/O    | Port 3: This is a 3-bit I/O port. Input or output can be designated for each bit by means of port control register 3 (PCR3)  |

|                   | P5 <sub>7</sub> to<br>P5 <sub>0</sub>                   | 32 to<br>25         | 40 to<br>33    | 1/0    | Port 5: This is an 8-bit I/O port. Input or output can be designated for each bit by means of port control register 5 (PCR5) |

|                   | P6 <sub>7</sub> to<br>P6 <sub>0</sub>                   | 24 to<br>17         | 32 to<br>25    | I/O    | Port 6: This is an 8-bit I/O port. Input or output can be designated for each bit by means of port control register 6 (PCR6) |

|                   | P7 <sub>7</sub> to<br>P7 <sub>3</sub>                   | 38 to<br>34         | 46 to<br>42    | 1/0    | Port 7: This is a 5-bit I/O port. Input or output can be designated for each bit by means of port control register 7 (PCR7)  |

|                   | P8 <sub>7</sub> to<br>P8 <sub>0</sub>                   | 46 to<br>39         | 54 to<br>47    | I/O    | Port 8: This is an 8-bit I/O port. Input or output can be designated for each bit by means of port control register 8 (PCR8) |

|                   | P9 <sub>4</sub> to                                      | 15 to<br>11         | 23 to<br>19    | I/O    | Port 9: This is a 5-bit I/O port. Input or output can be designated for each bit by means of port control register 9 (PCR9)  |

Table 1-2 Pin Functions (cont)

|                     |                  | Pin                 | No.     |        |                                                                                               |  |  |  |

|---------------------|------------------|---------------------|---------|--------|-----------------------------------------------------------------------------------------------|--|--|--|

| Туре                | Symbol           | FP-64A              | DP-64S  | I/O    | Name and Functions                                                                            |  |  |  |

| Serial<br>communi-  | SI <sub>1</sub>  | 51                  | 59      | Input  | SCI1 receive data input:<br>This is the SCI1 data input pin                                   |  |  |  |

| cation<br>interface | SO <sub>1</sub>  | 50                  | 58      | Output | SCI1 send data output:<br>This is the SCI1 data output pin                                    |  |  |  |

| (SCI)               | SCK <sub>1</sub> | 52                  | 60      | 1/0    | SCI1 clock I/O:<br>This is the SCI1 clock I/O pin                                             |  |  |  |

|                     | RXD              | 48                  | 56      | Input  | SCI3 receive data input:<br>This is the SCI3 data input pin                                   |  |  |  |

|                     | TXD              | 49                  | 57      | Output | SCI3 send data output:<br>TThis is the SCI3 data output pin                                   |  |  |  |

|                     | SCK <sub>3</sub> | 47                  | 55      | I/O    | SCI3 clock I/O:<br>This is the SCI3 clock I/O pin                                             |  |  |  |

| A/D<br>converter    | AN7 to<br>An0    | 59 to 64,<br>1 to 2 | 3 to 10 | Input  | Analog input channels 7 to 0:<br>These are analog data input channels<br>to the A/D converter |  |  |  |

|                     | ADTRG            | 22                  | 30      | Input  | A/D converter trigger input: This is the external trigger input pin to the A/D converter      |  |  |  |

## Section 2 CPU

#### 2.1 Overview

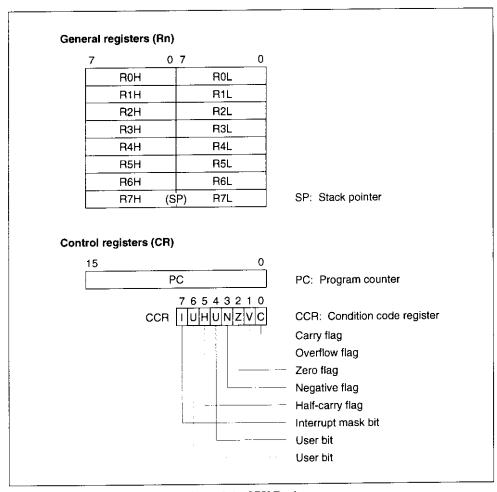

The H8/300L CPU has sixteen 8-bit general registers, which can also be paired as eight 16-bit registers. Its concise instruction set is designed for high-speed operation.

#### 2.1.1 Features

Features of the H8/300L CPU are listed below.

- General-register architecture

Sixteen 8-bit general registers, also usable as eight 16-bit general registers

- · Instruction set with 55 basic instructions, including:

- Multiply and divide instructions

- Powerful bit-manipulation instructions

- · Eight addressing modes

- Register direct

- Register indirect

- Register indirect with displacement

- Register indirect with post-increment or pre-decrement

- Absolute address

- Immediate

- Program-counter relative

- Memory indirect

- 64-kbyte address space

- · High-speed operation

- All frequently used instructions are executed in two to four states

- High-speed arithmetic and logic operations

- 8- or 16-bit register-register add or subtract:  $0.4 \mu s^*$

- $-8 \times 8$ -bit multiply:

2.8 µs\*

— 16 ÷ 8-bit divide:

$2.8 \, \mu s^*$

Low-power operation modes

SLEEP instruction for transfer to low-power operation

Note: \* These values are at  $\emptyset = 5$  MHz.

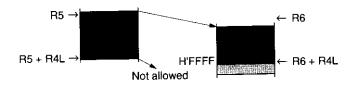

#### 2.1.2 Address Space

The H8/300L CPU supports an address space of up to 64 kbytes for storing program code and data.

See 2.8, Memory Map, for details of the memory map.

#### 2.1.3 Register Configuration

Figure 2-1 shows the register structure of the H8/300L CPU. There are two groups of registers: the general registers and control registers.

Figure 2-1 CPU Registers

#### 2.2 Register Descriptions

#### 2.2.1 General Registers

All the general registers can be used as both data registers and address registers.

When used as data registers, they can be accessed as 16-bit registers (R0 to R7), or the high bytes (R0H to R7H) and low bytes (R0L to R7L) can be accessed separately as 8-bit registers.

When used as address registers, the general registers are accessed as 16-bit registers (R0 to R7).

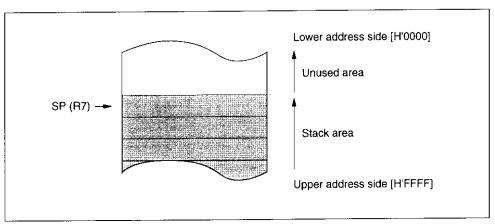

R7 also functions as the stack pointer (SP), used implicitly by hardware in exception processing and subroutine calls. When it functions as the stack pointer, as indicated in figure 2-2, SP (R7) points to the top of the stack.

Figure 2-2 Stack Pointer

#### 2.2.2 Control Registers

The CPU control registers include a 16-bit program counter (PC) and an 8-bit condition code register (CCR).

**Program Counter (PC):** This 16-bit register indicates the address of the next instruction the CPU will execute. All instructions are fetched 16 bits (1 word) at a time, so the least significant bit of the PC is ignored (always regarded as 0).

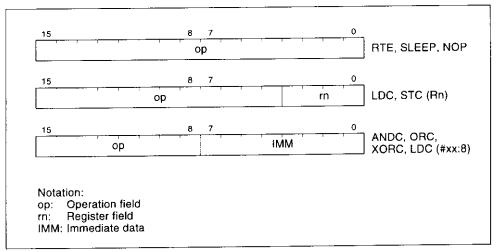

Condition Code Register (CCR): This 8-bit register contains internal status information, including the interrupt mask bit (I) and half-carry (H), negative (N), zero (Z), overflow (V), and carry (C) flags. These bits can be read and written by software (using the LDC, STC, ANDC, ORC, and XORC instructions). The N, Z, V, and C flags are used as branching conditions for conditional branching (Bcc) instructions.

Bit 7—Interrupt Mask Bit (I): When this bit is set to 1, interrupts are masked. This bit is set to 1 automatically at the start of exception handling. The interrupt mask bit may be read and written by software. For further details, see section 3.3, Interrupts.

Bit 6—User Bit (U): Can be used freely by the user.

Bit 5—Half-Carry Flag (H): When the ADD.B, ADDX.B, SUB.B, SUBX.B, CMP.B, or NEG.B instruction is executed, this flag is set to 1 if there is a carry or borrow at bit 3, and is cleared to 0 otherwise.

The H flag is used implicitly by the DAA and DAS instructions.

When the ADD.W, SUB.W, or CMP.W instruction is executed, the H flag is set to 1 if there is a carry or borrow at bit 11, and is cleared to 0 otherwise.

Bit 4—User Bit (U): Can be used freely by the user.

Bit 3—Negative Flag (N): Indicates the most significant bit (sign bit) of the result of an instruction.

Bit 2—Zero Flag (Z): Set to 1 to indicate a zero result, and cleared to 0 to indicate a non-zero result

Bit 1—Overflow Flag (V): Set to 1 when an arithmetic overflow occurs, and cleared to 0 at other times.

Bit 0—Carry Flag (C): Set to 1 when a carry occurs, and cleared to 0 otherwise. Used by:

- Add instructions, to indicate a carry

- Subtract instructions, to indicate a borrow

- · Shift and rotate instructions, to store the value shifted out of the end bit

The carry flag is also used as a bit accumulator by bit manipulation instructions.

Some instructions leave some or all of the flag bits unchanged.

Refer to the H8/300L Series Programming Manual for the action of each instruction on the flag bits.

#### 2.2.3 Initial Register Values

When the CPU is reset, the program counter (PC) is initialized to the value stored at address H'0000 in the vector table, and the I bit in the CCR is set to 1. The other CCR bits and the general registers are not initialized. In particular, the stack pointer (R7) is not initialized. The stack pointer should be initialized by software, by the first instruction executed after a reset.

#### 2.3 Data Formats

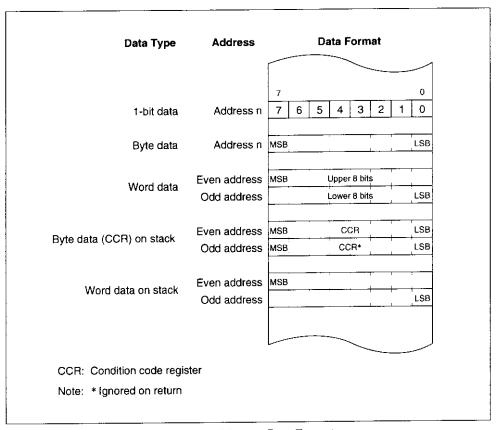

The H8/300L CPU can process 1-bit data, 4-bit (BCD) data, 8-bit (byte) data, and 16-bit (word) data.

- Bit manipulation instructions operate on 1-bit data specified as bit n in a byte operand (n = 0, 1, 2, ..., 7).

- All arithmetic and logic instructions except ADDS and SUBS can operate on byte data.

- The MOV.W, ADD.W, SUB.W, CMP.W, ADDS, SUBS, MULXU (8 bits × 8 bits), and DIVXU (16 bits ÷ 8 bits) instructions operate on word data.

- The DAA and DAS instructions perform decimal arithmetic adjustments on byte data in packed BCD form. Each nibble of the byte is treated as a decimal digit.

# 2.3.1 Data Formats in General Registers

Data of all the sizes above can be stored in general registers as shown in figure 2-3.

| Data Type                                                                             | Register                | No.       |                  |         |       |        |      | D       | ata F | orma                                         | ıt   |        |      |        |     |            |       |          |

|---------------------------------------------------------------------------------------|-------------------------|-----------|------------------|---------|-------|--------|------|---------|-------|----------------------------------------------|------|--------|------|--------|-----|------------|-------|----------|

|                                                                                       |                         | 7         |                  | 1       |       |        |      |         | 0     | ı                                            |      |        |      |        |     |            |       |          |

| 1-bit data                                                                            | RnH                     | 7         | 6                | 5       | 4     | 3      | 2    | 1       | 0     | J                                            |      |        | don' | t car  | e   | <b>.</b> . |       |          |

|                                                                                       |                         |           |                  |         |       |        |      |         |       | 7                                            |      |        |      |        | _   |            |       | 0        |

| 1-bit data                                                                            | RnL                     |           | ,                |         | don't | care   |      |         |       | 7                                            | 6    | 5_     | 4    | 3      | 2   |            | 1     | 0        |

|                                                                                       |                         | 7         |                  |         |       |        |      |         | 0     |                                              |      |        |      |        |     |            |       |          |

| Byte data                                                                             | AnH                     | MSB       |                  |         |       |        |      |         | LSB   | J                                            |      |        | don  | t car  | e   |            |       |          |

|                                                                                       |                         |           |                  |         |       |        |      |         |       | 7                                            |      |        |      |        |     |            |       | 0        |

| Byte data                                                                             | RnL                     |           |                  |         | don'i | t care |      |         |       | мѕв                                          |      | 1.     |      |        | , - |            |       | LSB      |

|                                                                                       |                         |           |                  |         |       |        |      |         |       |                                              |      |        |      |        |     |            |       | •        |

| Word data                                                                             | Rn                      | 15<br>MSB |                  |         |       |        | 1    |         |       |                                              |      |        |      |        | -   |            |       | LSB      |

|                                                                                       |                         |           |                  |         |       |        |      |         |       |                                              |      |        |      |        |     |            |       |          |

| 4-bit BCD data                                                                        | RnH                     | 7         | Uppe             | r digit | 4     | . 3    | Lowe | r digit | 0     | 1                                            |      |        | don  | 't car | е   |            |       | <b>·</b> |

| 4-bit BOD data                                                                        | 1,000                   |           |                  |         |       | •      | L    |         | · ·   | ٠                                            |      |        |      |        |     | • • • •    |       |          |

|                                                                                       |                         |           |                  |         |       |        |      |         |       | 7                                            | Unne | r digi | 4    | 3      | 0   | VAL        | digit | 0        |

| 4-bit BCD data                                                                        | RnL                     | i         |                  |         | don   | care   |      |         |       | <u>.                                    </u> | Oppe | i aigi |      |        | 1   |            | u.gir |          |

| Notation:<br>RnH: Upper byte<br>RnL: Lower byte<br>MSB: Most signi<br>LSB: Least sign | e of gene<br>ficant bit | ral reg   | gister<br>gister |         |       |        |      |         |       |                                              |      |        |      |        |     |            |       |          |

Figure 2-3 Register Data Formats

#### 2.3.2 Memory Data Formats

Figure 2-4 indicates the data formats in memory. For access by the H8/300L CPU, word data stored in memory must always begin at an even address. In word access the least significant bit of the address is regarded as 0. If an odd address is specified, the access is performed at the preceding even address. This rule affects the MOV.W instruction, and also applies to instruction fetching.

Figure 2-4 Memory Data Formats

When the stack is accessed using R7 as an address register, word access should always be performed. When the CCR is pushed on the stack, two identical copies of the CCR are pushed to make a complete word. When they are restored, the lower byte is ignored.

#### 2.4 Addressing Modes

#### 2.4.1 Addressing Modes

The H8/300L CPU supports the eight addressing modes listed in table 2-1. Each instruction uses a subset of these addressing modes.

Table 2-1 Addressing Modes

| Address Modes                                                                 | Symbol                                                                                                                                                                                               |  |  |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Register direct                                                               | Rn                                                                                                                                                                                                   |  |  |

| Register indirect                                                             | @Rn                                                                                                                                                                                                  |  |  |

| Register indirect with displacement                                           | @(d:16, Rn)                                                                                                                                                                                          |  |  |

| Register indirect with post-increment<br>Register indirect with pre-decrement | @Rn+<br>@-Rn                                                                                                                                                                                         |  |  |

| Absolute address @aa:8 or @aa:16                                              |                                                                                                                                                                                                      |  |  |

| Immediate #xx:8 or #xx:16                                                     |                                                                                                                                                                                                      |  |  |

| Program-counter relative @(d:8, PC)                                           |                                                                                                                                                                                                      |  |  |

| Memory indirect                                                               | @@aa:8                                                                                                                                                                                               |  |  |

|                                                                               | Register direct Register indirect Register indirect with displacement Register indirect with post-increment Register indirect with pre-decrement Absolute address Immediate Program-counter relative |  |  |

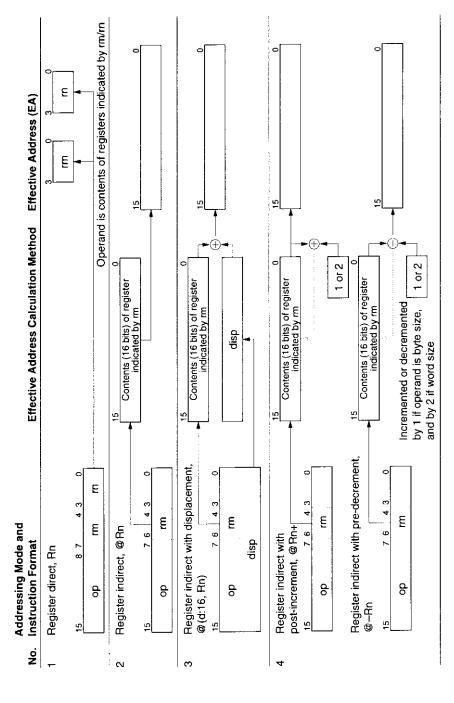

1. **Register Direct—Rn:** The register field of the instruction specifies an 8- or 16-bit general register containing the operand.

Only the MOV.W, ADD.W, SUB.W, CMP.W, ADDS, SUBS, MULXU (8 bits  $\times$  8 bits), and DIVXU (16 bits  $\div$  8 bits) instructions have 16-bit operands.

- 2. **Register Indirect—@Rn:** The register field of the instruction specifies a 16-bit general register containing the address of the operand in memory.

- 3. Register Indirect with Displacement—@(d:16, Rn): The instruction has a second word (bytes 3 and 4) containing a displacement which is added to the contents of the specified general register to obtain the operand address in memory.

This mode is used only in MOV instructions. For the MOV.W instruction, the resulting address must be even.

## 4. Register Indirect with Post-Increment or Pre-Decrement-@Rn+ or @-Rn:

· Register indirect with post-increment—@Rn+

The @Rn+ mode is used with MOV instructions that load registers from memory.

The register field of the instruction specifies a 16-bit general register containing the address of the operand. After the operand is accessed, the register is incremented by 1 for MOV.B or 2 for MOV.W. For MOV.W, the original contents of the 16-bit general register must be even.

· Register indirect with pre-decrement—@-Rn

The @-Rn mode is used with MOV instructions that store register contents to memory.

The register field of the instruction specifies a 16-bit general register which is decremented by 1 or 2 to obtain the address of the operand in memory. The register retains the decremented value. The size of the decrement is 1 for MOV.B or 2 for MOV.W. For MOV.W, the original contents of the register must be even.

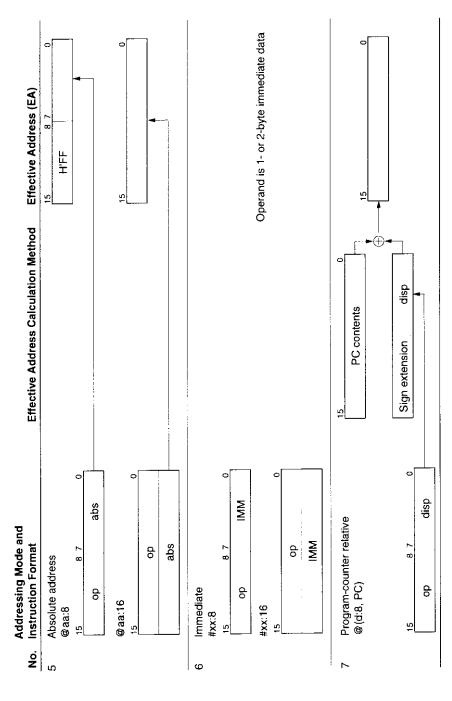

5. Absolute Address—@aa:8 or @aa:16: The instruction specifies the absolute address of the operand in memory.

The absolute address may be 8 bits long (@aa:8) or 16 bits long (@aa:16). The MOV.B and bit manipulation instructions can use 8-bit absolute addresses. The MOV.B, MOV.W, JMP, and JSR instructions can use 16-bit absolute addresses.

For an 8-bit absolute address, the upper 8 bits are assumed to be 1 (H'FF). The address range is H'FF00 to H'FFFF (65280 to 65535).

6. Immediate—#xx:8 or #xx:16: The instruction contains an 8-bit operand (#xx:8) in its second byte, or a 16-bit operand (#xx:16) in its third and fourth bytes. Only MOV.W instructions can contain 16-bit immediate values.

The ADDS and SUBS instructions implicitly contain the value 1 or 2 as immediate data. Some bit manipulation instructions contain 3-bit immediate data in the second or fourth byte of the instruction, specifying a bit number.

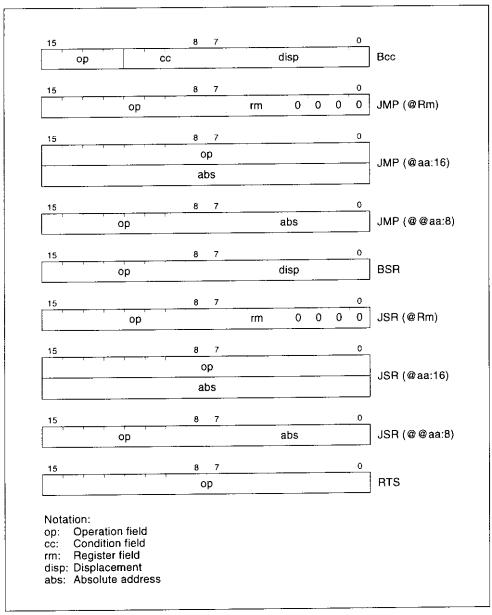

7. Program-Counter Relative—@(d:8, PC): This mode is used in the Bcc and BSR instructions. An 8-bit displacement in byte 2 of the instruction code is sign-extended to 16 bits and added to the program counter contents to generate a branch destination address. The possible branching range is -126 to +128 bytes (-63 to +64 words) from the current address. The displacement should be an even number.

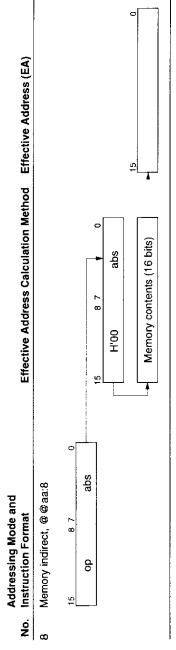

8. Memory Indirect—@@aa:8: This mode can be used by the JMP and JSR instructions. The second byte of the instruction code specifies an 8-bit absolute address. The word located at this address contains the branch destination address.

The upper 8 bits of the absolute address are assumed to be 0 (H'00), so the address range is from H'0000 to H'00FF (0 to 255). Note that with the H8/300L Series, the lower end of the address area is also used as a vector area. See 3.3, Interrupts, for details on the vector area.

If an odd address is specified as a branch destination or as the operand address of a MOV.W instruction, the least significant bit is regarded as 0, causing word access to be performed at the address preceding the specified address. See 2.3.2, Memory Data Formats, for further information.

#### 2.4.2 Effective Address Calculation

Table 2-2 shows how effective addresses are calculated in each of the addressing modes.

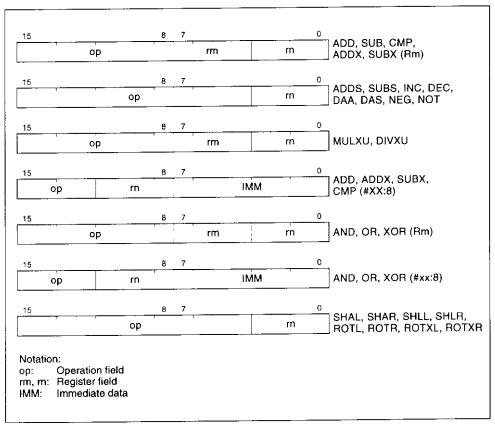

Arithmetic and logic instructions use register direct addressing (1). The ADD.B, ADDX, SUBX, CMP.B, AND, OR, and XOR instructions can also use immediate addressing (6).

Data transfer instructions can use all addressing modes except program-counter relative (7) and memory indirect (8).

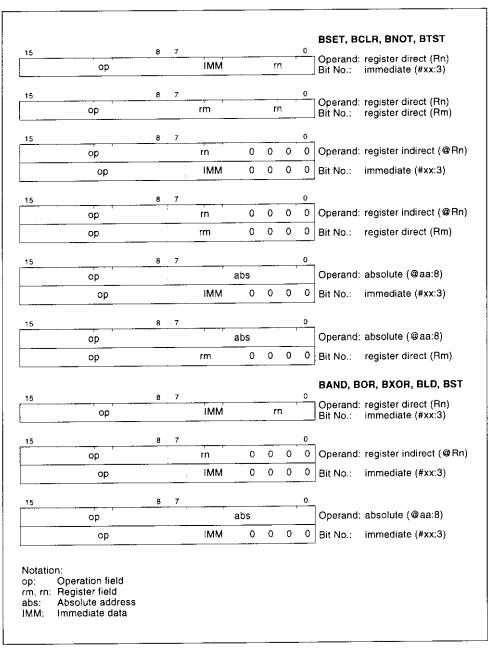

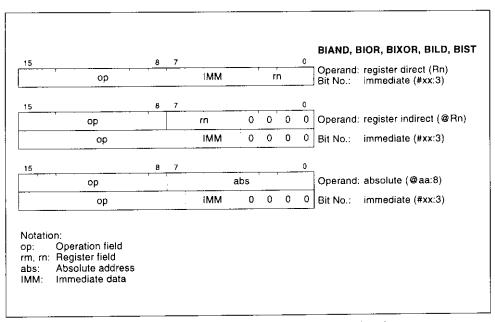

Bit manipulation instructions use register direct (1), register indirect (2), or absolute addressing (5) to specify a byte operand, and 3-bit immediate addressing (6) to specify a bit position in that byte. The BSET, BCLR, BNOT, and BTST instructions can also use register direct addressing (1) to specify the bit position.

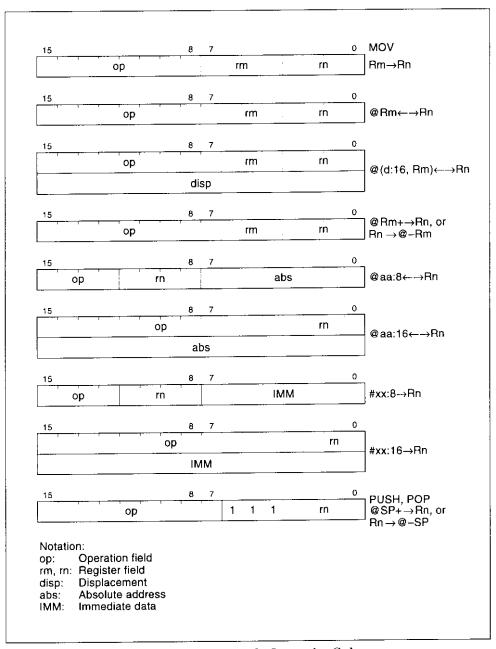

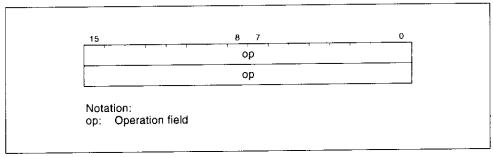

Table 2-2 Effective Address Calculation

Table 2-2 Effective Address Calculation (cont)

Table 2-2 Effective Address Calculation (cont)

Notation:

rm, rn: Register field op: Operation field disp: Displacement IMM: Immediate data abs: Absolute address

#### 2.5 Instruction Set

The H8/300L Series can use a total of 55 instructions, which are grouped by function in table 2-3.

Table 2-3 Instruction Set

| Function              | Instructions                                                                      | Number    |

|-----------------------|-----------------------------------------------------------------------------------|-----------|

| Data transfer         | MOV, PUSH*1, POP*1                                                                | 1         |

| Arithmetic operations | ADD, SUB, ADDX, SUBX, INC, DEC, ADDS,<br>SUBS, DAA, DAS, MULXU, DIVXU, CMP, NEG   | 14        |

| Logic operations      | AND, OR, XOR, NOT                                                                 | 4         |

| Shift                 | SHAL, SHAR, SHLL, SHLR, ROTL, ROTR,<br>ROTXL, ROTXR                               | 8         |

| Bit manipulation      | BSET, BCLR, BNOT, BTST, BAND, BIAND, BOR, BIOR, BXOR, BIXOR, BLD, BILD, BST, BIST | 14        |

| Branch                | Bcc*2, JMP, BSR, JSR, RTS                                                         | 5         |

| System control        | RTE, SLEEP, LDC, STC, ANDC, ORC, XORC, NOP                                        | 8         |

| Block data transfer   | EEPMOV                                                                            | 1         |

|                       |                                                                                   | Total: EE |

Total: 55

Notes: 1. PUSH Rn is equivalent to MOV.W Rn, @-SP. POP Rn is equivalent to MOV.W @SP+, Rn.

2. Bcc is a conditional branch instruction in which cc represents a condition code.

The following sections give a concise summary of the instructions in each category, and indicate the bit patterns of their object code. The notation used is defined next.

## Notation

| Notation           |                                                    |

|--------------------|----------------------------------------------------|

| Rd                 | General register (destination)                     |

| Rs                 | General register (source)                          |

| Rn                 | General register                                   |

| (EAd), <ead></ead> | Destination operand                                |

| (EAs), <eas></eas> | Source operand                                     |

| CCR                | Condition code register                            |

| N                  | N (negative) flag of CCR                           |

| Z                  | Z (zero) flag of CCR                               |

| V                  | V (overflow) flag of CCR                           |

| С                  | C (carry) flag of CCR                              |

| PC                 | Program counter                                    |

| SP                 | Stack pointer                                      |

| #IMM               | Immediate data                                     |

| disp               | Displacement                                       |

| +                  | Addition                                           |

| _                  | Subtraction                                        |

| ×                  | Multiplication                                     |

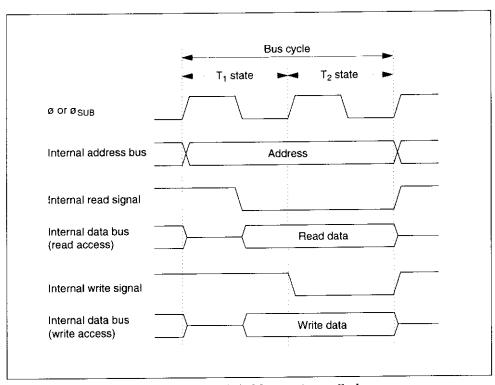

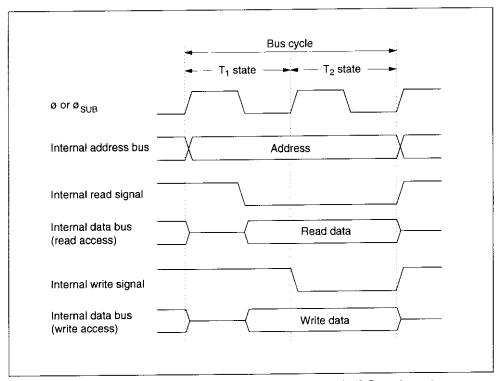

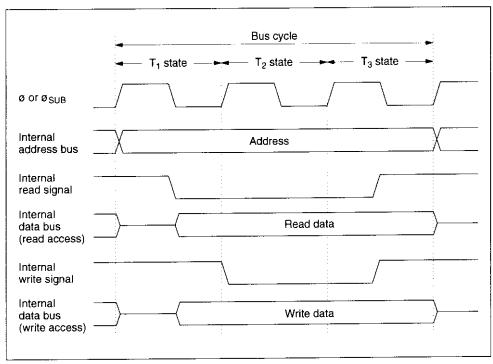

| ÷                  | Division                                           |