# **Version History**

| Version | Release Date | Author(s)   | Contents                                                                                                                                                  |

|---------|--------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α       |              | R. Couper   | For review only                                                                                                                                           |

| В       |              | David R     | Added active device and circuit descriptions                                                                                                              |

| С       | 20/05/03     | H. van Hoek | Additional Tx LPF and Modulation information                                                                                                              |

| D       | 21/05/03     | H. van Hoek | added per request of EMC Tech. NZ.  Tidy up. Assignment of document number. Relocation of LPF and modulation descriptions to circuit description sections |

| E       | 30/09/04     | David R     | Completely revise relevant sections to reflect consolidated (ETSI/ACA/FCC) build                                                                          |

|         |              |             |                                                                                                                                                           |

|         |              |             |                                                                                                                                                           |

# **Review History**

| Version | Review Date | Reviewer(s) | Review Comment Summary |

|---------|-------------|-------------|------------------------|

| A       |             |             |                        |

|         |             |             |                        |

|         |             |             |                        |

|         |             |             |                        |

|         |             |             |                        |

|         |             |             |                        |

|         |             |             |                        |

|         |             |             |                        |

# **Table of Contents**

| 1 Introduction                                                  |   |

|-----------------------------------------------------------------|---|

| 2 FCC Application for type approval Section 2.963               | 5 |

| 2.1 Part 1 (Types of emission)                                  | 5 |

| 2.2 Part 2 (Frequency range)                                    | 5 |

| 2.3 Part 3 (Range of operating power)                           |   |

| 2.4 Part 4 (Maximum power rating)                               | 6 |

| 2.5 Part 5 (Voltage/Current of final PA)                        |   |

| 2.6 Part 6 (Function of each active circuit)                    | 6 |

| 2.7 Part 7 (Complete circuit diagram)                           | 9 |

| 2.8 Part 8 (Instruction books)                                  | 9 |

| 2.9 Part 9 (Tune up procedure)                                  | 9 |

| 2.10 Part 10 (Description of circuitry)                         | 9 |

| 2.11 Part 11 (Description of circuitry)                         |   |

| 2.12 Part 12 (Identification label)                             |   |

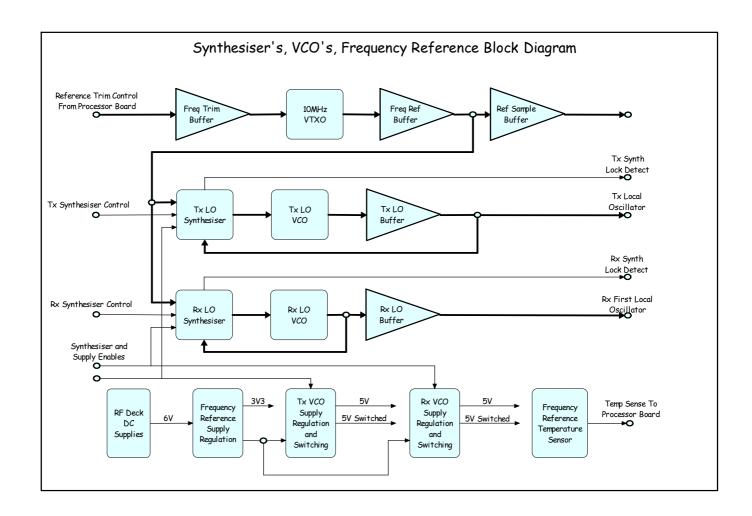

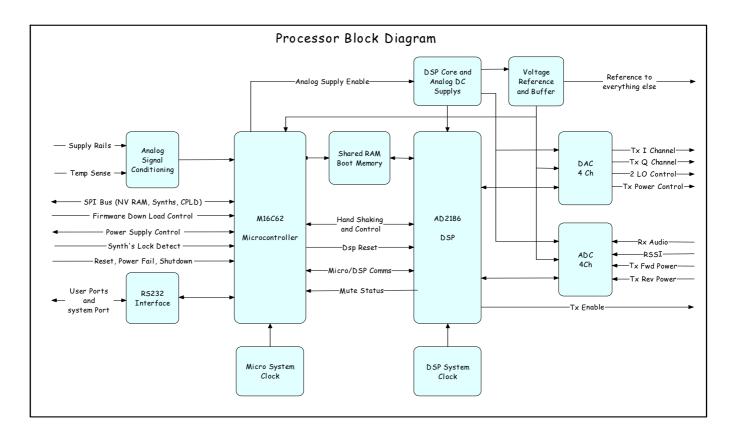

| 3 Appendix A È Series Remote and Exciter Circuit Block Diagrams |   |

Filename: TypeApprovalApplicationInfoConsolidatedE.doc Document Number: 184-40-0002, Ver: E, Rev : 35, Last Edit : 14/09/04 15:15 Page 2 of 15

#### References

| Ref. | Date | Author(s) | Title – Document Number – Version - Pages     |

|------|------|-----------|-----------------------------------------------|

| 1    |      |           | 151-00-100G Processor Board Schematics        |

| 2    |      |           | 180- 00-200B RF Deck Schematics               |

| 3    |      |           | E Series User Manual.pdf (supplied on CD-ROM) |

| 4    |      |           | 186-06-0000B Build Table                      |

| 5    |      |           |                                               |

| 6    |      |           |                                               |

| 7    |      |           |                                               |

| 8    |      |           |                                               |

#### **Abbreviations**

| Abbreviation | Description                         |  |  |

|--------------|-------------------------------------|--|--|

| PC           | IBM compatible personal computer    |  |  |

| TView+       | E Series radio programming software |  |  |

|              |                                     |  |  |

|              |                                     |  |  |

#### 1 Introduction

This document covers the requirements or makes reference to the documents which fulfil the requirements of FCC application for type approval Section 2.963 Parts 1 to 12.

This equipment has been previously submitted for the original grants (NI8ER450-XXF01) issued on 15 July 2003 and the design has since been updated to meet ETSI 300 113 requirements Approval is now sought for this class II permissive change (per FCC part 2.1001).

The radio can be supplied in half duplex and full duplex configurations. The latter has the same transmitter connector (N-Connector) as the half duplex unit, however the receiver input connector (SMA connector) is fitted to the opposite side. The design of both radios is the same except for the routing of the receive signal via the SMA connector.

#### Changes are:

- New VCO (Built on the main board. Improved phase noise)

- New Power Control loop, Analog Power control loop replaces digital for improved ramp control.

- Improved Receiver Front End.

- Introduction of new frequency types for greater flexibility for customers frequency ranges (This is not a change to the design just the final tuning of the VCO frequency and Receiver Helical filters).

- Minor changes to microprocessor clocking circuitry on processor board.

- New Modulation format available for compatibility with M series Product.

Note that the modulation circuitry / methods are unchanged.

The Low Pass Filter for the transmitter is unchanged in stripline dimensions and topology although slight changes in shunt capacitor values have been made to facilitate common PCB loading

Filename: TypeApprovalApplicationInfoConsolidatedE.doc

Document Number: 184-40-0002, Ver: E, Rev : 35, Last Edit : 14/09/04 15:15 Page 3 of 15

between band types. This document has been updated to reflect these changes and these are in italics.

Filename: TypeApprovalApplicationInfoConsolidatedE.doc Document Number: 184-40-0002, Ver: E, Rev : 35, Last Edit : 14/09/04 15:15

## 2 FCC Application for type approval Section 2.963

Text in italic in this section is the requirement from Federal Communications Commission Part 2.963.

### 2.1 Part 1 (Types of emission)

Type(s) of emission.

The radio supports operation of the following types of emissions. Only one can be selected at a time by the Tview + Programmer Software and a unique name is displayed for each.

| Description                                       | Designator | T view+ Programmer        |

|---------------------------------------------------|------------|---------------------------|

|                                                   |            | Selection                 |

| FM 9600 bps Data (4Level GMSK) 12.5 kHz channel   | 11K2F1D    | 9600 12.5kHz FCC 4 Level  |

| FM 19200 bps Data (4 Level GMSK) 12.5 kHz channel | 11K2F1D    | 19200 12.5kHz FCC 4 Level |

| FM 9600 bps Data (2 Level GMSK) 12.5 kHz channel  | 11K2F1D    | 9600 12.5kHz FCC 2 Level  |

| FM 9600 bps Data (3 Level GMSK) 12.5 kHz channel  | 11K2F1D    | 9600 12.5kHz M-Series     |

### 2.2 Part 2 (Frequency range)

Frequency range.

- *370*MHz to 520MHz.

- The radio will only operate on one transmit and one receive frequency at a time as selected by the Tview + Programmer Software.

- Covered by several bands as follows:

- Type 46 370- 388 MHz

- Type 47 380 to 396MHz

- Type 48 395 to 406MHz

- Type 50 403 to 417MHz

- Type 56 418 to 435MHz

- Type 57 428 to 443MHz

- Type 55 436 to 450MHz

- Type 51 450 to 465MHz

- Type 52 465 to 480MHz

- Type 53 480 to 494MHz

- Type 60 490 to 505MHz

- Type 54 505 to 518MHz

In Addition a number of SuperTypes are available, these allow customers to specify custom frequency ranges. For example if a customer wanted a radio to cover the range 455-470 MHz then a supertype C2 (450-487 MHz) could be custom tuned at the factory for 455-470 MHz. Note that the physical electronic hardware and performance is the same as a standard type (i.e. type 51) with the exception that the VCOs and helical filters (RX) have been tuned to the new frequency range. Supertypes are:

- Type A6 TX: 370 to 400 MHz RX: 370 to 400 MHz

- Type B3 TX: 395 to 450MHz RX:395 to 426 MHz

- Type B4 TX: 395 to 450MHz RX:413 to 447 MHz

Document Number: 184-40-0002, Ver: E, Rev : 35, Last Edit : 14/09/04 15:15 Page 5 of 15

- Type B5 TX: 395 to 450MHz RX:433 to 450 MHz

- Type C1 TX: 436 to 518MHz RX:436 to 467 MHz

- Type C2 TX: 436 to 518MHz RX:450 to 487 MHz

- Type C3 TX: 436 to 518MHz RX:473 to 518 MHz

Product model number coding is ER450-xxF01 where "xx"=type number, "F"=FCC approval, "01"=12.5 kHz channel.

### 2.3 Part 3 (Range of operating power)

Range of operating power and description of means provided for variation of operating power.

- Operating power 100mW to 5W.

- Operating power programmed using PC running TView+ programmer software connected to E-Series radio's system port via the PC's serial port. The TView+ programmer limits the maximum power that may be set.

### 2.4 Part 4 (Maximum power rating)

Maximum power rating as defined in the applicable rules.

5W

### 2.5 Part 5 (Voltage/Current of final PA)

The voltages applied to and currents into the several elements of the final radio frequency amplifying device for normal operation over the power range. Indicate whether these voltages and currents are AC or DC.

| Power O/P | Remote PA Voltage | Approximate Control Pin | Remote PA Current |

|-----------|-------------------|-------------------------|-------------------|

|           | (PA Module)       | Voltage                 | (PA Module)       |

|           |                   | (In feedback loop)      |                   |

| 100mW     | 13.8V DC          | 1.6V DC                 | 0.2A DC           |

| 1W        | 13.8V DC          | 1.9V DC                 | 0.6A DC           |

| 5W        | 13.8V DC          | 25V DC                  | 1.5A DC           |

### 2.6 Part 6 (Function of each active circuit)

Function of each electron tube, semiconductor or other active circuit device.

| Processor Board Circuit     | Designator(s) | Function                                                  |

|-----------------------------|---------------|-----------------------------------------------------------|

| Device                      |               |                                                           |

| Microprocessor              | U4            | Initialises Frequency synthesisers and Digital Signal     |

|                             |               | Processor. Handles Packet assembly /disassembly and       |

|                             |               | other high level data operations.                         |

| RS-232 Driver               | U6,U8         | Interface for the two user ports and system port to the   |

|                             |               | microprocessor.                                           |

| Static RAM                  | U1            | Data buffer between microprocessor and DSP                |

| Digital Signal Processor    | U7            | Handles data scrambling/descrambling at bit level.        |

|                             |               | Waveform generation and modulation at base band IQ        |

|                             |               | level. Receive data recovery and AFC.                     |

|                             |               | Handles PA power control.                                 |

| Linear Regulator 1          | U3            | Supplies core voltage for DSP.                            |

| Linear Regulator 2          | U13           | Analogue supply for ADC/DAC                               |

| Analog to Digital Converter | U11           | Receive signal acquisition. Monitoring Forward and        |

|                             |               | Reverse power. Monitoring receiver signal strength (RSSI) |

Filename: TypeApprovalApplicationInfoConsolidatedE.doc

Document Number: 184-40-0002, Ver: E, Rev : 35, Last Edit : 14/09/04 15:15 Page 6 of 15

| Processor Board Circuit Device | Designator(s) | Function                                                     |

|--------------------------------|---------------|--------------------------------------------------------------|

| Digital to Analog Converter    | U9            | I and Q waveform generation. TX power setting. Receiver AFC. |

| Voltage Reference              | U12,U25       | Reverence for ADC,DAC and IQ modulator.                      |

| RF Deck Circuit Device        | Designator(s) |                                                                |

|-------------------------------|---------------|----------------------------------------------------------------|

| Switching Regulators          | U31,U32       | 3.3 volt regulator for digital circuits. 6V regulator for      |

|                               |               | analogue circuits. Analogue circuits have further filtering.   |

| NV RAM                        | U26           | Stores radio configuration data set with Tview                 |

|                               |               | programmer.                                                    |

| Reset Generator               | U27           | Resets Microprocessor at Power up. Signals                     |

|                               |               | microprocessor of brown out condition.                         |

| CPLD                          | U25           | Digital IO expansion                                           |

| LED's                         | H1-H4         | User status indication                                         |

| I-Q Filtering and level       | U13,U14       | Reconstruction filters. Smooth transitions from the DAC to     |

| translation.                  | 0.0,0         | prevent reconstruction frequency spurious.                     |

| IQ Modulator                  | U18           | Quadrature Modulator for transmit RF signal. I and Q           |

| TG Woddiator                  | 0.10          | inputs are from the DSP's DAC via reconstruction filters.      |

| Tx Driver                     | U17           | Amplifies RF signal from IQ modulator to the level required    |

| TX DIIVEI                     | 017           | by the RF Power Module.                                        |

|                               |               | by the M. Tower Module.                                        |

|                               |               | Note: The part used here has changed however the               |

|                               |               | designator and circuit description are the same.               |

| Tx Power Amplifier            | Q18           | RF Power Module. Final stage of RF amplification for the       |

|                               |               | transmitter.                                                   |

|                               |               | Power lovel controlled by Angles control loop, Followed by     |

|                               |               | Power level controlled by Analog control loop. Followed by     |

| TX Power measurement.         | D12 D25 D12 L | low pass filter to attenuate harmonics.                        |

| TA Power measurement.         |               | Diodes measure forward and reverse power. Opamps               |

| TOVO                          | 12<br>Y2      | provide buffering and temperature compensation.                |

| TCXO                          | Y2            | Commercial 10 MHz reference module. Internally                 |

|                               |               | temperature compensated. Final frequency trim by DC            |

| TV 1/00 P (f                  | 1.100         | level from microprocessor.                                     |

| TX VCO Buffer                 | U30           | Provides very high isolation between the TX VCO and the        |

|                               |               | rest of the transmitter chain to prevent the VCO pulled due    |

|                               |               | to changing conditions in the TX chain.                        |

| Temperature sensor            | U8            | Monitors temperature for diagnostics purposes as well as       |

|                               |               | for high temperature PF Power foldback.                        |

| Tx and Rx Synthesisers        | U28,U23       | PLL IC controls TX and RX VCOs via an RC loop filter.          |

|                               |               | Locked to 10 MHz reference.                                    |

| Tx and Rx VCOs                | Q22,D28       | Discrete VCO. Single transistor design with High Q Air         |

|                               | Q23,D29       | core inductor and varactor used for resonator. Final TX        |

|                               |               | frequency generation and receiver first local oscillator.      |

| Tx pin switch                 |               | Switches the common antenna port between the receiver          |

|                               |               | and transmitter when PTT is activated.                         |

|                               | Q16           |                                                                |

| TX Out of Lock Disable        | Q10           | Prevents transmission if PLL has not locked by pulling         |

|                               |               | down TX enable line.                                           |

| Second Local Oscillator       | Q4,Q5         | A fundamental VCXO and x4 frequency multiplier provide         |

|                               |               | the AFC controlled second local oscillator.                    |

| LNA                           | Q9,Q6         | A BJT with active biasing provides the first gain stage for    |

|                               | ,             | the receiver.                                                  |

| Receiver Post mixer amplifier | . Q1          | IF amplification providing IF gain after the loss of the first |

|                               |               | mixer.                                                         |

|                               |               |                                                                |

|                               |               | Note: The part used here has changed however the               |

|                               |               | designator and circuit description are the same.               |

Filename: TypeApprovalApplicationInfoConsolidatedE.doc Document Number: 184-40-0002, Ver: E, Rev : 35, Last Edit : 14/09/04 15:15

Page 7 of 15

| RF Deck Circuit Device             | Designator(s) | Function                                                   |

|------------------------------------|---------------|------------------------------------------------------------|

| IF Amplifier                       | Q8            | Provides IF gain between the first and Second SAW filters. |

| Integrated IF & Demodulator        |               | Receiver second mixer, Second IF and Quadrature            |

|                                    |               | Demodulator.                                               |

| Receiver Antialiasing filter U3,U4 |               | Removes high frequency audio components that may           |

|                                    |               | cause aliasing in the ADC.                                 |

Filename: TypeApprovalApplicationInfoConsolidatedE.doc Document Number: 184-40-0002, Ver: E, Rev : 35, Last Edit : 14/09/04 15:15

Page 8 of 15

### 2.7 Part 7 (Complete circuit diagram)

Complete circuit diagram.

• See schematics provided [1] and [2] and Build Table [4].

### 2.8 Part 8 (Instruction books)

Instruction books. If the instruction book(s) is not available when the application is filed a set of draft instructions should be provided and the complete instruction book should be submitted as soon as available.

• See E-Series User Manual provided [3].

### 2.9 Part 9 (Tune up procedure)

Tune up procedure over the power range or at specific operating power levels.

- Refer to RF Parameters setup procedures in E-Series User Manual [3].

- Calibration performed at factory.

### 2.10 Part 10 (Description of circuitry)

A description of all circuitry and devices provided for determining and stabilising frequency.

- Frequency Reference A Commercial TCXO 10MHz frequency reference module is used to provide a stable reference to the transmit synthesiser/PLL. The TCXO also has a fine trim input which is controlled by a microprocessor analog output, the initial level that the trim input is set to is determined during factory setup. The TCXO module is internally temperature compensated to better than 1ppm.

- **Transmit VCO** The transmit VCO is phased locked to the 10 MHz reference with a PLL. If the PLL is out of lock the transmitter is prevented from operating by hardware.

### 2.11 Part 11 (Description of circuitry)

A description of any circuits employed for suppression of spurious radiation, for limiting modulation, and for limiting the operating power.

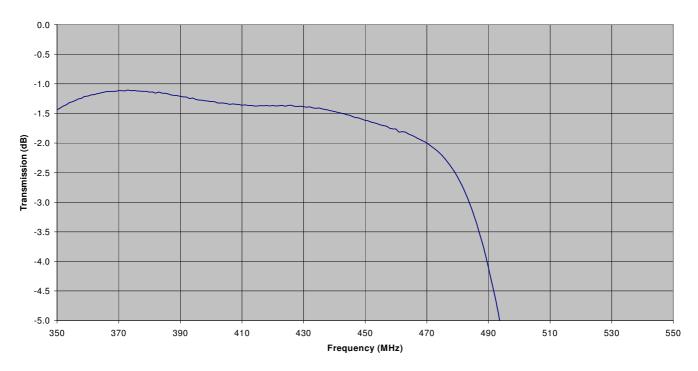

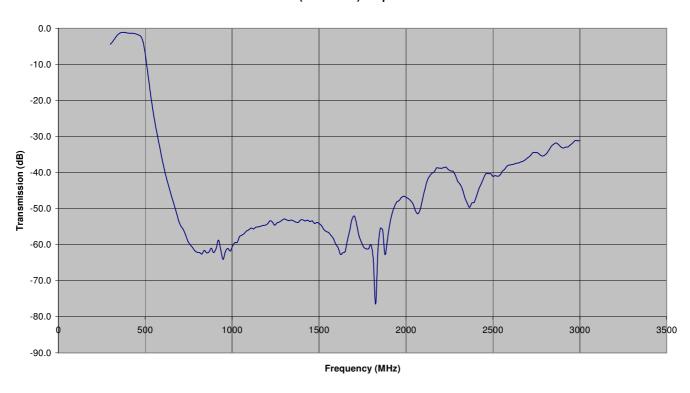

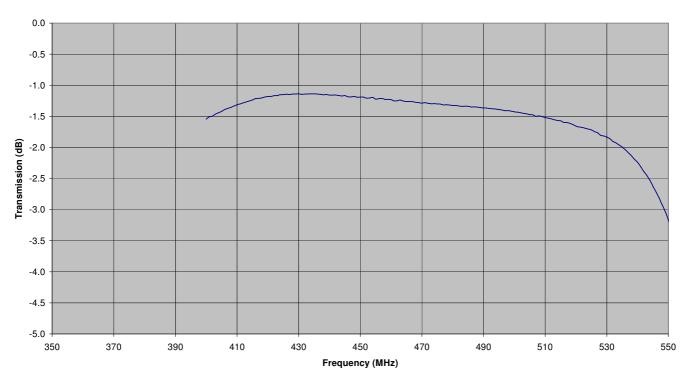

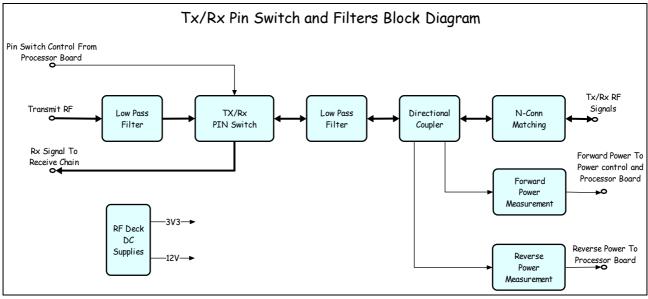

• Low pass filter – The low pass filter consists of 2 stages with a PIN switch in between. Each stage has 5 elements, 2 strip line inductors and 3 shunt capacitors. Special consideration has been given in the layout to reducing series inductance in the shunt capacitors to ensure a monotonic roll off above the cut off frequency. The low pass filter is constructed using four stripline hair-pin sections which act as the inductive elements in a nine pole Butterworth LPF. This provides low loss, low radiation and a high degree of repeatability. Each capacitive section of the filter is made up of two shunt capacitors which provide low inductance and thus better rejection at higher frequencies. In this configuration the LPF can be optimised for use in the bands between 400MHz and 520MHz by changing the values of shunt capacitance.

The Low Pass Filter for the transmitter is unchanged in stripline dimensions and topology although slight changes in shunt capacitor values have been made to facilitate common PCB loading between band types.

Filename: TypeApprovalApplicationInfoConsolidatedE.doc

Document Number: 184-40-0002, Ver: E, Rev : 35, Last Edit : 14/09/04 15:15

#### LPF (Low Build) Passband

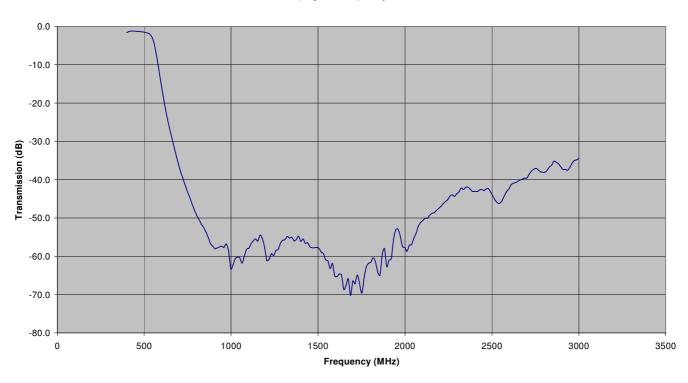

Figure 1 Low Pass Filter Pass Band Response for Low Band Builds (Radios covering 370 to 450 MHz).

#### LPF (Low Build) Stopband

Figure 2 Low Pass Filter Stop Band Response for Low Band Builds (Radios covering 370 to 450 MHz).

Filename: TypeApprovalApplicationInfoConsolidatedE.doc

Document Number: 184-40-0002, Ver: E, Rev : 35, Last Edit : 14/09/04 15:15

Page

#### LPF (High Build) Passband

Figure 3 Low Pass Filter Pass Band Response for High Band Builds (Radios covering 436 to 518 MHz).

#### LPF (High Build) Stopband

Figure 4 Low Pass Filter Stop Band Response for High Band Builds (Radios covering 436 to 518 MHz)

Filename: TypeApprovalApplicationInfoConsolidatedE.doc

Document Number: 184-40-0002, Ver: E, Rev: 35, Last Edit: 14/09/04 15:15

Page 11 of 15

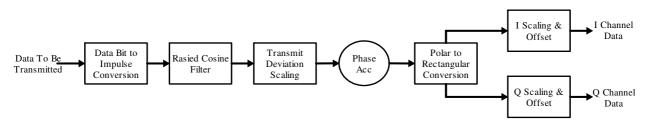

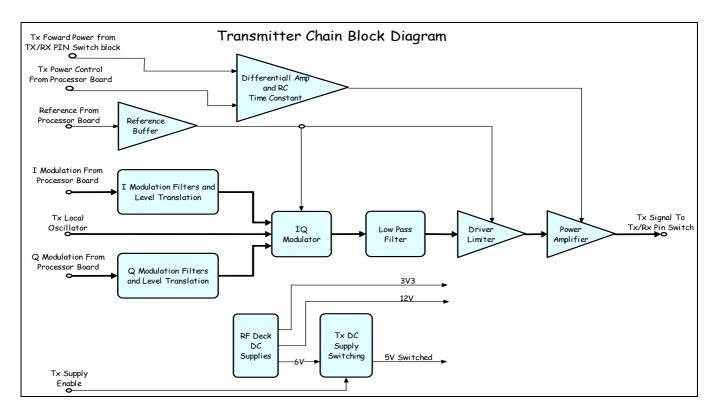

• **Modulation.** Modulation is generated numerically in the DSP located on a separate processor board and is therefore not subjected to component uncertainties. As digital modulation is employed a limiter is not required.

#### Numerically Generated I-Q Modulation

#### Analog RF Modulation I Channel I Channel 10 Bit DAC Reconstruction Data Filter Modulated RF I-O Modulator O Channel O Channe 10 Bit DAC Reconstruction Data Filter LO Generation

#### Numerically Generated I-Q Modulation

- 1.Modulation is controlled by a DSP located on a separate processor board. The DSP receives input data via a microcontroller from the external data ports or from data generated by the microcontroller in response to received messages.

- 2.Data bits to be transmitted are converted to positive/negative impulses of an amplitude that will not cause the following filter to saturate.

- 3. The impulse stream is passed through a raised cosine FIR filter which produces a numeric representation of the desired modulating signal.

- 4. The numeric modulating signal is then scaled to determine the final modulated RF deviation.

- 5. Each sample of the modulating signal's amplitude is added to a phase accumulator to produce the phase angle of a frequency modulated signal.

- 6. This phase angle is then converted into I and Q signals using polar to rectangular conversion.

- 7. Finally the I and Q signals are scaled and have a DC offset added to match the requirements of the external I-Q modulator before being output to a DAC.

Selection of different modulation types is achieved by changing the impulse conversion, raised cosine FIR filter and transmit deviation scaling parameters. The parameters for each modulation type are stored in non-volatile memory and cannot be modified by users.

Filename: TypeApprovalApplicationInfoConsolidatedE.doc

Document Number: 184-40-0002, Ver: E, Rev: 35, Last Edit: 14/09/04 15:15

Page 12 of 15

#### Analog RF Modulation

- 1. The numeric I and Q signals are converted by 2 channels of a 4 channel 10 bit DAC.

- 2. The analog I and Q signals then pass through reconstruction filters to remove sampling frequency products.

- 3. The filtered I and Q signals are then fed to a I-Q modulator along with a carrier frequency local oscillator to produce the modulated RF.

- **RF power control** The power is controlled by a conventional analog feedback loop that compares the actual power with the demanded power. The loop has a single dominant pole implemented with a passive RC circuit following an op amp. This configuration also limits the ramp up and ramp down rates. Demanded power is set by the microprocessor reading from NVRAM. The NVRAM power setting is set and limited by the programmer, a power meter is employed for this procedure

### 2.12 Part 12 (Identification label)

A photograph or drawing of the equipment identification plate or label showing the information to be placed thereon.

E Series - Remote

Model: **ER450-51F01-D00**

Serial # **52399**

FCC ID: **NI8ER450-XXF01**IC: **4630A-ER450F01**

Made by Trio Datacom

Filename: TypeApprovalApplicationInfoConsolidatedE.doc

Document Number: 184-40-0002, Ver: E, Rev : 35, Last Edit : 14/09/04 15:15

# 3 Appendix A E Series Remote and Exciter Circuit Block Diagrams

A common platform has been used for both the ER450 remote unit and the exciter which is fitted into a EB450 base station. In the case of the exciter the power amplifier is replaced with an exciter driver board which is shown in the schematics provided.

Filename: TypeApprovalApplicationInfoConsolidatedE.doc

Document Number: 184-40-0002, Ver: E, Rev: 35, Last Edit: 14/09/04 15:15

Filename: TypeApprovalApplicationInfoConsolidatedE.doc Document Number: 184-40-0002, Ver: E, Rev: 35, Last Edit: 14/09/04 15:15