# DHX91 Block Diagram & Operation Description

---

Version 1.1 2Mar2015

## Contents

|                                |   |

|--------------------------------|---|

| Objectives:.....               | 1 |

| DHX91 SOC block diagram.....   | 2 |

| DHX91 RF block diagram .....   | 3 |

| General Description.....       | 3 |

| RF Operation Description ..... | 3 |

## Objectives:

Provide DHX91 SOC high level block diagram and detail RF block diagram.

Provide operation description and RF operation description.

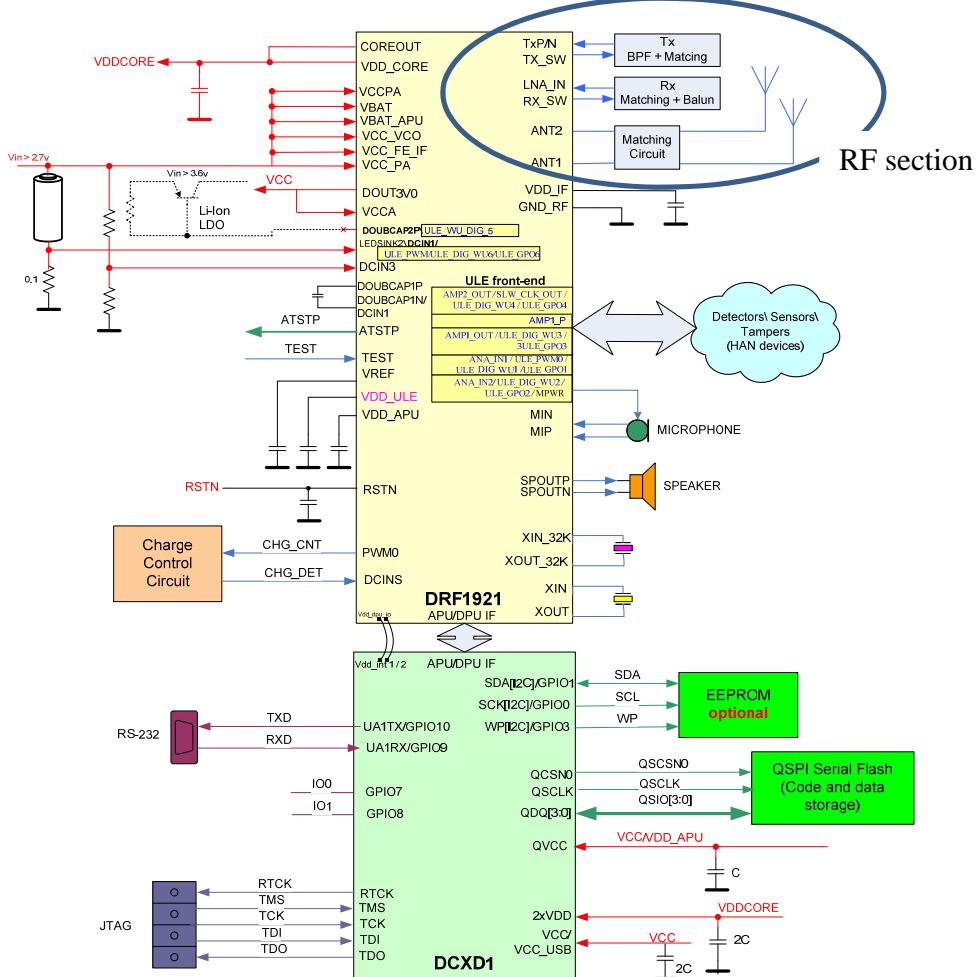

## DHX91 SOC block diagram

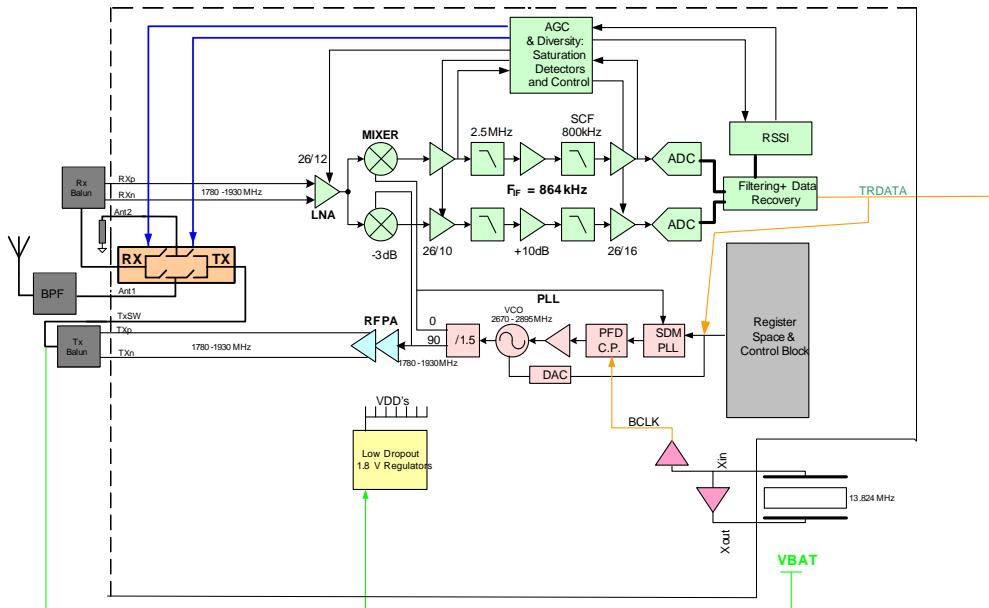

## DHX91 RF block diagram

## General Description

The DHX91 System on a Chip is a Multi-Chip Module (MCM) composed of the Digital Processing Unit (DPU) and the RF/Analog Processing Unit (APU). Designed to meet Ultra Low Energy (ULE) standards, it offers extensive support for Hibernation mode and RTC management to substantially reduce power consumption.

DHX91 is based on an ARM926EJ-S™ processor with internal memory, as well as caches enabling code and data to be run from external quad SPI (QSPI) flash. DHX91 has voice coprocessor engines.

DHX91 is designed as a solution for DECT-based home products, including:

- Home monitoring and control units, including motion detectors, smoke detectors, baby monitors, door bells, flood detection, 110 V/220 V power outlet control, gas and water metering, other sensors

- Wireless audio, home and office communication devices

## RF Operation Description

An integrated PLL synthesizer capable of operating within the band of 1780- 1930 MHz is provided on-chip. The PLL is implemented as a Fractional-N synthesizer that uses the Delta-Sigma ( $\Delta$ - $\Sigma$ ) method of frequency control.

2 point modulator is used to generate FSK modulation, this causes the output frequency to increase or decrease proportional to the digital TR\_DATA.

2-stage PA with +25.5dBm output (typical) and programmability over a 20dB range. The ramp up and ramp down characteristic are programmable to allow shaping of response within desired Power-Time template.

In order to provide a larger effective receiver dynamic range, the system provides a method of Automatic Gain Control (AGC). The gain is switched in four different locations: LNA, Internal TR Switch, and in two locations in the IF chain. By overlapping the dynamic ranges of each gain state, the chip is able to achieve an overall effective dynamic range of greater than 75dB.

CMOS embedded Double-Pole-Double-Throw switch that act as T/R switch and Diversity switch. Each RF port of the DPDT switch is DC blocked and matched to 50 ohm with external LC component.