# Merlin U520 Technical specification and Low Level Circuit Description

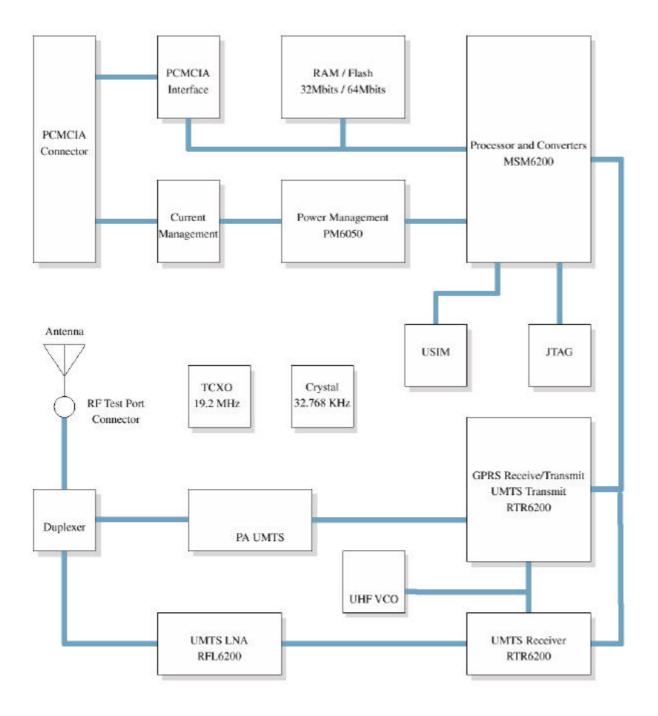

# **Block Diagram**

### Processor

The processing and DSP functions occur in the MSM6200. External to the MSM6200, 64 Mbits of Flash and 32Mbits of SRAM are provided. The FLASH is used to store the firmware and provide non-volatile storage of calibration and configuration data (NV-RAM). During operation some program code is transferred from the FLASH to the SRAM to provide the system higher operating speeds.

A 19.2 MHz clock is used for the reference for both the processor and the RF synthesizers. A 32.768 KHz crystal is used to provide the time base during the low current sleep mode.

### **PCMCIA** Interface

The PCMCIA interface is implemented using an FPGA. This provides for the possibility of field upgrades and customized host interfaces. The FPGA is initialized by the processor during the boot-up sequence. The FPGA is directly connected to the processor address and data bus to provide maximum data throughput. The standard FPGA configuration is as a multifunction PC Card supporting attribute memory (CIS and configuration registers) and two UART modules accessed in 8 bit I/O mode.

#### Power

The power for the unit is supplied via the PCMCIA VCC pins. The voltage select pins are configured for 5 volt operation. The current management circuit includes a host supply current limit and a large charge reservoir.

### RF

Using a Zero IF architecture for both transmit and receive minimizes the size and component count of the radio.

## **Host Interface**

The U530 is designed to be compatible with host devices that meet the PC Card specifications as detailed in Section 4.9 of the Electrical Specification of the PC Card Standard – March 1997. Voltage Selection pins (VS1# and VS2#) are configured for 5 volt operation. The basic DC parameters for the U530 are shown below.

| Symbol        | Parameter                            | Min                          | Тур  | Max       | Units |

|---------------|--------------------------------------|------------------------------|------|-----------|-------|

| Vcc           | Supply Voltage                       | Supply Voltage 4.75 5.0 5.25 |      | V         |       |

| Icc max       | maximum supply current               |                              | 1000 | mA        |       |

| Icc stdby     | Standby supply current               |                              | 120  |           | mA    |

| Icc csd       | CSD supply current (note 1)          |                              |      | 360       | mA    |

| Icc grps avg  | GPRS supply current average (note 2) |                              |      | 290       | mA    |

| Icc grps peak | GPRS supply current peak (note 2)    |                              |      | 620       | mA    |

| Icc WCDMA     | WCDMA supply current (note 3)        |                              |      | 600       | mA    |

| V ih          | Input High Voltage                   | 2                            |      | Vcc + 0.5 | V     |

| V il          | Input Low Voltage                    | -0.5                         |      | 0.7       | V     |

| V oh          | Output High Voltage (12 mA)          | 2.4                          |      |           | V     |

| V ol          | Output Low Voltage (-12 mA)          |                              |      | 0.4       | V     |

| Table 1 U530 DC Specifications (Vcc is 5 volts unless specified otherwise |

|---------------------------------------------------------------------------|

|---------------------------------------------------------------------------|

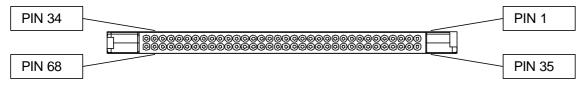

# PC Card 68 pin connector

Figure 1 PC Card 68 pin connector

#### Table 2 PC Card Pinout

|     | Memory mode |                     | I/O mode |                    |           |           |

|-----|-------------|---------------------|----------|--------------------|-----------|-----------|

| Pin | NAME        | Function            | NAME     | Function           | Direction | Supported |

| 1   | GND         | Ground              |          |                    | DC        | Yes       |

| 2   | D3          | Data bit 3          |          |                    | I/O       | Yes       |

| 3   | D4          | Data bit 4          |          |                    | I/O       | Yes       |

| 4   | D5          | Data bit 5          |          |                    | I/O       | Yes       |

| 5   | D6          | Data bit 6          |          |                    | I/O       | Yes       |

| 6   | D7          | Data bit 7          |          |                    | I/O       | Yes       |

| 7   | CE1#        | Card Enable         |          |                    | 1         | Yes       |

| 8   | A10         | Address bit 10      |          |                    | 1         | Yes       |

| 9   | OE#         | Output Enable       |          |                    | 1         | Yes       |

| 10  | A11         | Address bit 11      |          |                    | 1         | Yes       |

| 11  | A9          | Address bit 9       |          |                    | 1         | Yes       |

| 12  | A8          | Address bit 8       |          |                    | 1         | Yes       |

| 13  | A13         | Address bit 13      |          |                    | 1         | No        |

| 14  | A14         | Address bit 14      |          |                    | 1         | No        |

| 15  | WE#         | Write Enable        |          |                    |           | Yes       |

| 16  | READY       | Ready               | IREQ#    | Interrupt Request  | 0         | Yes       |

| 17  | Vcc         | Supply Voltage      |          |                    | DC in     | Yes       |

| 18  | Vpp1        | Programming and     |          |                    | DC in     | No        |

|     | 1.1.        | Peripheral Supply 1 |          |                    | _         | -         |

| 19  | A16         | Address bit 16      |          |                    | 1         | No        |

| 20  | A15         | Address bit 15      |          |                    | 1         | No        |

| 21  | A12         | Address bit 12      |          |                    | 1         | No        |

| 22  | A7          | Address bit 7       |          |                    | 1         | Yes       |

| 23  | A6          | Address bit 6       |          |                    | 1         | Yes       |

| 24  | A5          | Address bit 5       |          |                    | 1         | Yes       |

| 25  | A4          | Address bit 4       |          |                    | 1         | Yes       |

| 26  | A3          | Address bit 3       |          |                    | 1         | Yes       |

| 27  | A2          | Address bit 2       |          |                    | 1         | Yes       |

| 28  | A1          | Address bit 1       |          |                    | 1         | Yes       |

| 29  | A0          | Address bit 0       |          |                    | 1         | Yes       |

| 30  | D0          | Data bit 0          |          |                    | I/O       | Yes       |

| 31  | D1          | Data bit 1          | 1        |                    | 1/0       | Yes       |

| 32  | D2          | Data bit 2          |          |                    | I/O       | Yes       |

| 33  | WP          | Write Protect       | IOIS16#  | I/O Port Is 16-bit | 0         | Yes       |

| 34  | GND         | Ground              | 1        |                    | DC        | Yes       |

| 35  | GND         | Ground              | 1        |                    | DC        | Yes       |

| 36  | CD1#        | Card Detect         |          |                    | 0         | Yes       |

| 37  | D11         | Data bit 11         |          |                    | 1/0       | No        |

| 38  | D12         | Data bit 12         |          |                    | 1/0       | No        |

| 39  | D13         | Data bit 13         |          |                    | 1/O       | No        |

| 40  | D14         | Data bit 14         |          |                    | 1/0       | No        |

# Merlin U520 Technical specification and Low Level Circuit Description

| 41 | D15   | Data bit 15                             |         |                           | I/O   | No  |

|----|-------|-----------------------------------------|---------|---------------------------|-------|-----|

| 42 | CE2#  | Card Enable                             |         |                           |       | Yes |

| 43 | VS1#  | Voltage Sense 1                         |         |                           | O Yes |     |

| 44 | RFU   | Reserved for future<br>use              | IORD#   | I/O Read                  | I Yes |     |

| 45 | RFU   | Reserved for future use                 | IOWR#   | I/O Write                 | I     | Yes |

| 46 | A17   | Address bit 17                          |         |                           | 1     | No  |

| 47 | A18   | Address bit 18                          |         |                           | 1     | No  |

| 48 | A19   | Address bit 19                          |         |                           | 1     | No  |

| 49 | A20   | Address bit 20                          |         |                           | 1     | No  |

| 50 | A21   | Address bit 21                          |         |                           | 1     | No  |

| 51 | Vcc   | Supply Voltage                          |         |                           | DC in | Yes |

| 52 | Vpp2  | Programming and<br>Peripheral Voltage 2 |         |                           | DC in | No  |

| 53 | A22   | Address bit 22                          |         |                           | 1     | No  |

| 54 | A23   | Address bit 23                          |         |                           | 1     | No  |

| 55 | A24   | Address bit 24                          |         |                           | 1     | No  |

| 56 | A25   | Address bit 25                          |         |                           | 1     | No  |

| 57 | VS2#  | Voltage Sense 2                         |         |                           | 0     | Yes |

| 58 | RESET | Card Reset                              |         |                           | 1     | Yes |

| 59 | WAIT# | Extend bus cycle                        |         |                           | 0     | Yes |

| 60 | RFU   | Reserved for future<br>use              | INPACK# | Input Port<br>Acknowledge | 0     | Yes |

| 61 | REG#  | Register select & I/O<br>Enable         |         |                           | I     | Yes |

| 62 | BVD2  | Batter Voltage Detect 2                 | SPKR#   | Audio Digital<br>Waveform | 0     | No  |

| 63 | BVD1  | Batter Voltage Detect                   | STSCHG# | Card Status<br>Changed    | 0     | Yes |

| 64 | D8    | Data bit 8                              |         | Ĭ                         | I/O   | No  |

| 65 | D9    | Data bit 9                              |         |                           | I/O   | No  |

| 66 | D10   | Data bit 10                             |         |                           | I/O   | No  |

| 67 | CD2#  | Card Detect                             |         |                           | 0     | Yes |

| 68 | GND   | Ground                                  |         |                           | DC    | Yes |

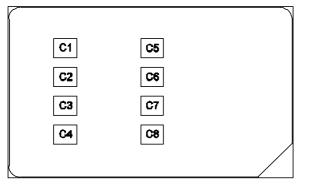

# **USIM Interface**

The USIM interface supports a 3.0 volt USIM. The VPP contact is not connected as per section 8.2 of 3GPP TS 21.111.

Figure 2 USIM Contacts (USIM as viewed from contact side)

#### **Table 3 USIM Pinout**

| PIN | Name | Description           |  |

|-----|------|-----------------------|--|

| C1  | VCC  | Supply Voltage        |  |

| C2  | RST  | Reset                 |  |

| C3  | CLK  | Clock                 |  |

| C4  |      | Reserved (No contact) |  |

| C5  | GND  | Ground                |  |

| C6  | VPP  | (not connected)       |  |

| C7  | I/O  | Data input/output     |  |

| C8  |      | Reserved (No contact) |  |

# Air interface

The Air Interface of the U530 supports both the 3GPP WCDMA specifications and the 3GPP GPRS specifications.

The RF design implements a Zero-IF architecture using the Qualcomm 6200 chipset.

#### Table 4 WCDMA Air Interface

| Specification    | 3GPP TS 34.121 |             | Release 99 |

|------------------|----------------|-------------|------------|

| Band Designation | 2100 UMTS      |             |            |

|                  | UE Tx Freq     | 1920 – 1980 | MHz        |

|                  | UE Rx Freq     | 2110 – 2170 | MHz        |

| Transmit Power   | Class 4        | +21         | dBm        |

The protocol stack supplied by QCT is based on 3GPP Standard 43.108 Release 99 and Standard 334.121 Release 99.

# **LED Display Description**

The LED Display is designed to provide the user with feedback as to the current state of the Novatel Merlin WCDMA Wireless PC Card Modem.

The following table explains the various states the LED Display can exhibit along with a description of each state and how each state is represented in terms of color and cadence.

#### Table 5 LED States

| State | Name       | Display                    | Cadence                                         | Description                                                                                                           |

|-------|------------|----------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 1     | ERROR      | FLASHING<br>RED            | 250ms ON<br>250ms OFF                           | An error has occurred in the modem firmware,<br>the modem is unable to read the USIM, or the<br>USIM is not inserted. |

| 2     | NO SERVICE | SOLID<br>RED               | ON                                              | The modem is not currently receiving a signal from the network.                                                       |

| 3     | WCDMA CS   | SINGLE<br>FLASH<br>BLUE    | 250ms ON<br>1750ms OFF                          | The modem is currently receiving a WCDMA signal from the system and is registered on the circuit switch domain.       |

| 4     | WCDMA PS   | DOUBLE<br>FLASHING<br>BLUE | 250ms ON<br>250ms OFF<br>250ms ON<br>1750ms OFF | The modem is currently receiving a WCDMA signal from the system and is registered on the packet switch domain.        |

| 5     | PDP        | SOLID<br>BLUE              | ON                                              | The modem is currently PDP context activated on the WCDMA system.                                                     |

# Hardware ID

The revision of the PCB and BOM is identified through a hardware ID. The ID is hard coded when the U530 is manufactured via component loading. This ID can be read and reported by the software.

## **Firmware**

### **Diagnostics & Logging**

The U530 supports a mechanism for obtaining diagnostic information from the modem during normal operation. This mechanism is available on each shipped product to facilitate prompt investigation of field issues.

The Qualcomm CAIT extensible diagnostic monitor tool is used to create log files and interpret diagnostic information. Diagnostic monitoring and logging is available from Qualcomm on Windows 2000/XP.

Diagnostic services are supported using the secondary port on the PC Card, while the primary port is used for data. The use of MobiLink and CAIT is mutually exclusive.

#### **Drivers**

The U530 is a multifunction PC Card. It provides two ports to the host PC; a primary modem port, and a secondary communications port. These ports are available to Microsoft Windows applications. The standard Microsoft Windows serial drivers are used to access these ports. Installation of the Novatel Wireless INF files is required for Microsoft Windows to recognize the card. These should be installed prior to the card being inserted into the host PC. Refer to the Merlin U530 User Guide.

### **Firmware Upgrades**

This U530 supports a method to locally upgrade the firmware of the device through the laptop interface only. It requires no special equipment.

# Merlin U520 Technical specification and Low Level Circuit Description

Procedures are provided to ensure that all critical modem provisioning and configuration information is protected from alteration during the upgrade operation. All such information is backed up and restored as part of the upgrade operation.

No method of reprogramming the firmware of the device over the air-interface is provided. Upgrades may be wirelessly downloaded to the host PC, and subsequently run locally.

### Firmware Stack & Interface to Host PC Stack

Data communication between the modem and the host PC is done through either a PPP or IP connection. UE-Network Protoco