## 19 PROCESSING GAIN REPORT

Certification Report For: Cisco System Document Number: 2001041 Revision 3

#### Radio Circuit Description

The MPI350 Spread Spectrum Transceiver operates in the 2.4 GHz ISM band, using Direct Sequence modulation techniques.

The transmit/receive and data packetization operations are under the control of a protocol processor (MAC) internal to the transceiver assembly.

Logic Section: A digital ASIC is employed in the logic section of the radio, providing the following functions:

- 1) Generation of the spreading code, combination of the code with the incoming data stream.

- 2) Despreading and demodulation of the incoming baseband spread signal.

- 3) Determination of the transmit/receive sequence.

RF Section (refer to MPI350 radio block diagram): The transmitter chain includes a shaping bandpass filter followed by a vector modulator. This signal is further filtered by a saw filter at the IF frequency of 374 MHz. This signal is then mixed up to the 2400-2483.5 MHz band. A RF filter at the output of the mixer removes any other mixing products. A power amplifier chain brings the signal up to the final output level of 100 mW. Through the Tx/Rx switch, the signal is passed through a dielectric bandpass filter to the antenna port. The radio has diversity, so two antenna ports are provided. Transmitter frequency is determined by the 44.0 MHz reference oscillator, with  $\pm$  25 ppm accuracy.

The receiver utilizes the same antenna filtering and Tx/Rx, followed by a LNA. A mixer circuit brings the signal to the 374 MHz IF, where a SAW filter shapes the IF spectral envelope. This filter provides the primary rejection against adjacent channel interference. An IF amplifier followed by an IF limiter brings the signal up to the level needed for the I and Q vector demodulator. A buffer amplifier and filter are used to shape the signal for the PHY digital ASIC which despreads and decodes the signal.

The 374 MHz voltage controlled oscillator is controlled by a synthesizer/PLL system comprised of a prescaler and programmable dividers. The 2026-2450 MHz voltage controlled oscillator is also controlled by a synthesizer/PLL system. Both local oscillators use a reference signal for the PLL which is derived from the 44.0 MHz master reference oscillator.

PRODUCT NAME: Cisco MPI350 Radio

NAME OF TEST: The Processing Gain of a Direct Sequence System.

FCC Part 15.247(e) specifies that the processing gain of a direct sequence system shall be at least 10 dB.

Guidance on measurement by FCC

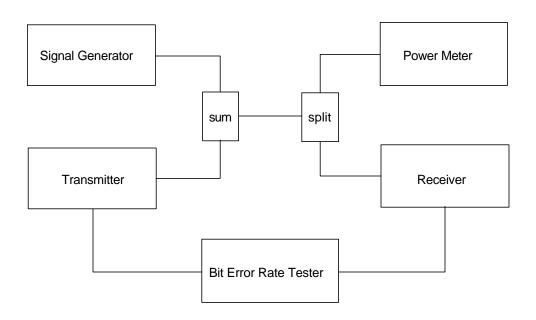

The processing gain may be measured using the CW jamming margin method (refer to figure 1). The test consists of stepping a signal generator, in 50kHz increments, across the passband of the system. At each point, the generator level required to the produce the recommended Bit Error Rate (10-5) is recorded. This is the jammer level. The output power of the transmitting unit is measured at the same point. The Jammer to Signal (J/S) ratio is then calculated, discarding the worst 20% of the J/S data points. The total losses in a system, including transmitter and receiver, should be assumed to be no more than 2 dB.

Processing Gain = S/N + Mj + Lsys

Where: S/N = Signal to noise ratio required at the receiver output for 10-5 error rate of a ideal receiver for your demodulation scheme

Mj = Jammer to signal ratio Lsys = System losses (2dB max)

#### **Test Results**

for 1 mb data rate:

S/N = 13.0 dB; taken from Wireless Information Networks by Pahlavan & Levesque

Mj = - 4.2 dB; worst case jamming margin from tests in lab

Lsys = 2.0 dB; system losses

therefore the processing gain at 1mb is 13.0 dB - 4.2 dB + 2.0 dB = 10.8 dB

for 2 mb data rate:

S/N = 13.0 dB; taken from Wireless Information Networks by Pahlavan & Levesque

Mj = - 4.2 dB; worst case jamming margin from tests in lab

Lsys = 2.0 dB; system losses

therefore the processing gain at 2mb is 13.0 dB - 4.2 dB + 2.0 dB = 10.8 dB

for 5.5 mb data rate:

S/N = 13.6 dB; taken from Harris CCK encoding modulation

Mj = - 4.9 dB; worst case jamming margin from tests in lab

Lsys = 2.0 dB; system losses

therefore the processing gain at 5.5mb is 13.6 dB - 4.9 dB + 2.0 dB = 10.7 dB

for 11 mb data rate:

S/N = 16.0 dB; taken from Harris CCK encoding modulation

Mi = - 7.4 dB; worst case jamming margin from tests in lab

Lsys = 2.0 dB; system losses

therefore the processing gain at 11mb is 16.0 dB - 7.4 dB + 2.0 dB = 10.6 dB

# **Jamming Test Setup**

| CISCO Confidential                          |              |

|---------------------------------------------|--------------|

| RF Systems Engineering                      |              |

| 2.4GHz Spread Sperctrum Radio - Jammer Test |              |

| Eng: Jim Nahra<br>Drawn: Diane Simon        | Date: 3/2/01 |

Figure 1

### **MPI350 Spread Spectrum Transceiver Alignment Procedures**

- Put the radio in Tx mode

- Set the power out (using the power meter)

- Use +20 dBm ± 1 dB for 100 mW power setting

- Use +17 dBm ± 1 dB for 50 mW power setting

- Use +15 dBm ± 1 dB for 30 mW power setting

- Use +13 dBm ± 1 dB for 20 mW power setting

- Use 0 dBm ± 1 dB for 1 mW power setting

- Turn the Tx on, ch 12-84

- Set the power amp output power by adjusting voltage to the IF attenuator in the Tx chain.

Note: This is done by software, which changes the DAC voltage output.