## **BreezeNet**

Functional Description and Block Diagram Description

AP-10D, AP-10 Access Point; SA-10D, SA-10 Station Adapter and WB-10D, WB-10 Wireless Bridge.

## 1. Functional Description.

These devices are designed to operate under IEEE 802.11 standard (Frequency Hopping Spread Spectrum).

The hardware of the AP-10, AP-10D, SA-10, SA-10D, WB-10, WB-10D is identical. All products have integrated antennas implemented in two ways: "D" models have non-standard interface for connection with antennas, non"D" models have a fixed integral antennas which require disassembly of the unit in order to be removed. A list of utilized antennas is supplied.

## 2. Block Description.

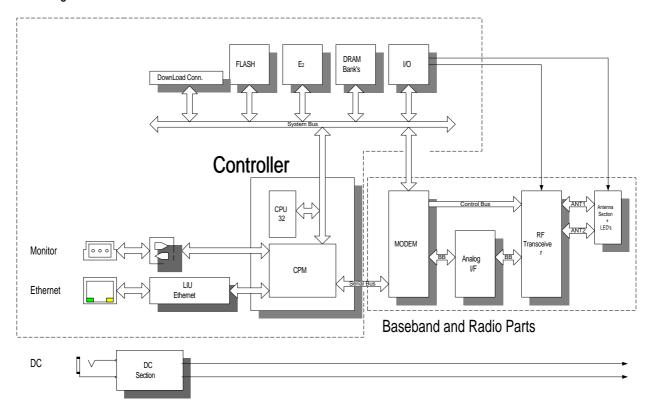

The device includes 3 main parts:

RF part.

Baseband part

Digital part

The device consists of a single board that includes the following sections:

- 1. A Radio Transceiver that transmits and receives the radio signals.

- 2. A Modem that handles the modulation/demodulation tasks.

- 3. A Controller that handles the protocol and the ethernet port.

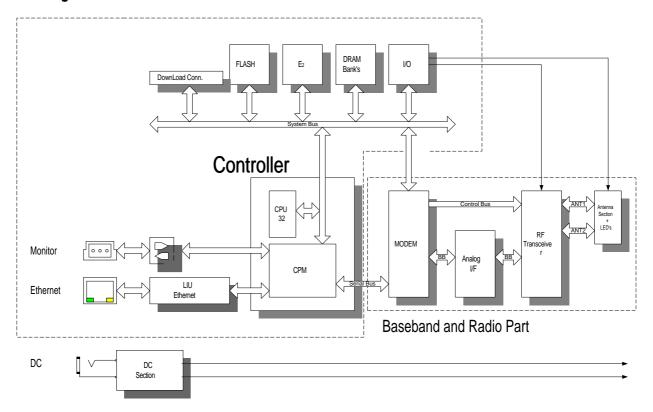

The block diagram of device is shown in Fig.1.

### Digital Part

Fig.1.Block Diagram of Device.

## 3. Block Diagram of RF Part.

- 3.1 The RF part has 2 main functions:

- 1. Modulate and transmit analog data.

- 2. Receive and demodulate the RF signals and forward these signals to the Baseband processor in analog form.

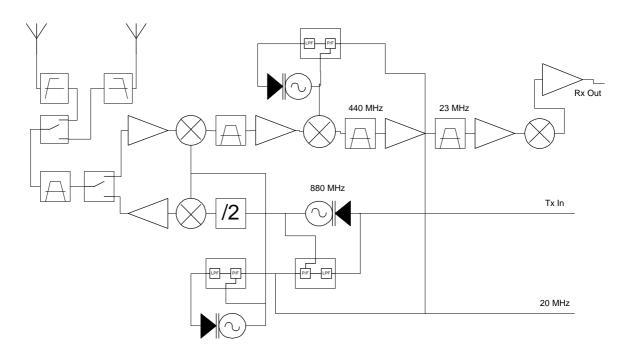

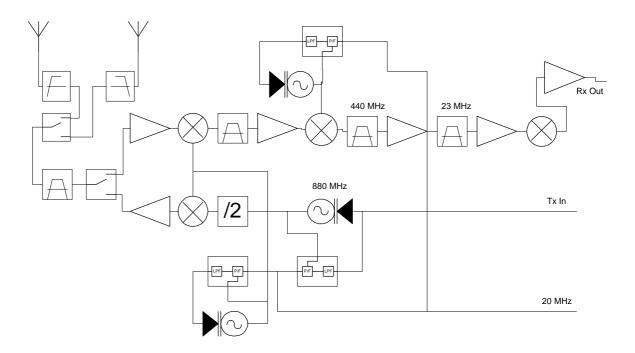

The block diagram of the radio is shown in Fig. 2.

3.2 Oscillators.

There are three RF oscillators on the RF board:

- 1. Tx VCO (Modulator), which continuously operates at 880 MHz, and in transmit mode is divided by two;

- 2. Rx VCO, serves as LO for the second conversion, Operates at 463 MHz;

- 3. Hopping synthesizer, Operate in the frequency range of 1962 MHz to 2040 MHz, Step size is 1 MHz.

There is also a Reference Oscillator that operating at 40 MHz. After division by 2 its signal is used as reference for all 3 VCO's.

All 3 synthesizers are frequency locked by use of PLL.

3.3 Transmit Path.

The transmit path consists of a modulator operating at twice the IF frequency, Hopping VCO, Up converter, PA and Diversity switch.

In transmit mode the divider is operated and thus enabling the division of the modulator by 2. This signal is upconverted by mixing it with the hopping signal that operates as LO. The mixed signal that is now in the 2.4 GHz band is filtered and fed to the PA, filtered again and through the diversity switch feeds the antenna. The modulating signal is a 2, 4 or 8 levels analog signal.

### 3.4 Receive Path.

The received signal is received in any of the antennas, selected by the diversity switch, filtered and transferred to the LNA, filtered again and down converted by mixing the received signal with the hopping synthesizer. The product has a 440 MHz IF where the signal is filtered and down converted to 23 MHz where it is demodulated into baseband signal. The baseband signal is filtered and transferred to the baseband processor. The output signal is a 2, 4, or 8 levels analog signal with 0.5 MHz bandwidth.

Fig.2. Radio Part Block Diagram

## 4. Block Diagram of Baseband Part.

Baseband Part consists of Modem and Analog interface for Radio (see Fig.1).

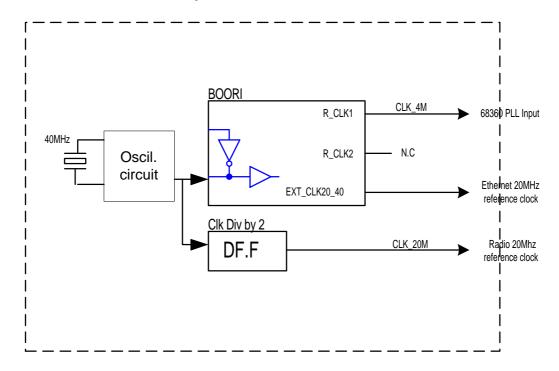

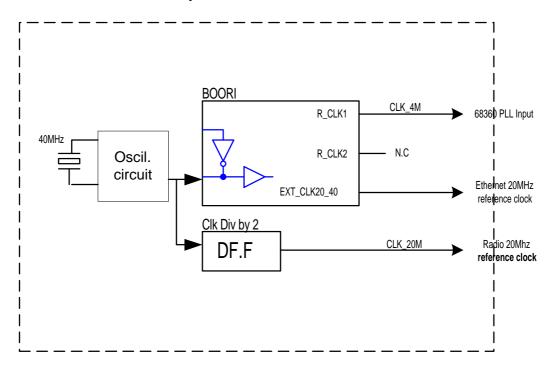

The Modem chip (BOORI) is the system master clock distributor (see Fig.3). It is running from 40MHz Crystal Oscillator Circuit (+/- 10ppm tolerance and +/- 4ppm stability ). R \_CLK1 default frequency is 4MHz which is division by 2.5 and 4 from the 40MHz clock.

Fig.3. Clock Distribution

### 5. Block Diagram of Digital Part.

The Digital Part consist of (see Fig.1):

### **CPU**

31Mhz MC68EN360 controller (QUICC);

### Memory

16/32Mbit 16 bits bus width sector erase Flash with 64kB uniform sectors; Additional 64kB E^2PROM;

#### DRAM banks;

48 bits MAC address serial ROM (BreezeCom customized special regitry);

### I/O Ports

24 bits off-QUICC Input/Output ports;

8 SMD miniature DIP switches and 8 hard jumpers for software and hardware configurations and versions.

### **Monitor Ports**

3 wires miniature connector

2 on-PCB test pads (optionally, for BOORI debugging)

**RS232** Transceiver

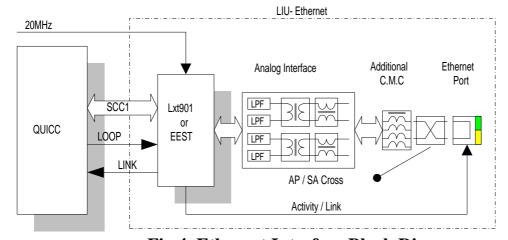

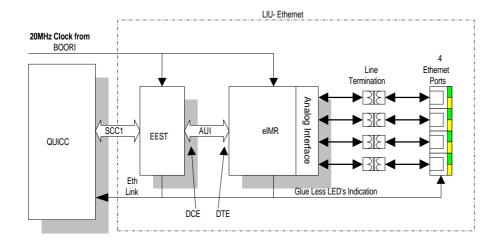

## **Ethernet (see Fig.4)**

1 10BaseT port;

Motorola compatible Ethernet transceiver;

10BaseT Analog interface for 1 port.

Fig.4. Ethernet Interface Block Diagram

# **BreezeNet**

# Functional Description and Block Diagram Description SA-40D, SA-40 Four Port Adapter

## 1. Functional Description.

These devices are designed to operate under IEEE 802.11 standard (Frequency Hopping Spread Spectrum).

The hardware of the SA-40, SA-40D is identical. All products have integrated antennas implemented in two ways: "D" models have non-standard interface for connection with antennas, non"D" models have a fixed integral antennas which require disassembly of the unit in order to be removed. A list of utilized antennas is supplied.

The SA-40(D) is based on the hardware and software of the SA-10(D). RF and Baseband parts of SA-40(D) and SA-10(D) are identical, however digital part of SA-40(D) has some additional hardware options for 4 ports Ethernet. The software of SA-40(D) is identical to SA-10.

## 2. Block Description.

The device includes 3 main parts:

RF part.

Baseband part

Digital part

The device consists of a single board that includes the following sections:

- 1. A Radio Transceiver that transmits and receives the radio signals.

- 4. A Modem that handles the modulation/demodulation tasks.

- 5. A Controller that handles the protocol and the ethernet port.

The block diagram of device is shown in Fig.1.

## **Digital Part**

Fig.1.Block Diagram of Device.

## 3. Block Diagram of RF Part.

- 3.1 The RF part has 2 main functions:

- 1. Modulate and transmit analog data.

- 2. Receive and demodulate the RF signals and forward these signals to the Baseband processor in analog form.

The block diagram of the radio is shown in Fig. 2.

3.2 Oscillators.

There are three RF oscillators on the RF board:

- 1. Tx VCO (Modulator, which continuously operates at 880 MHz, and in transmit mode is divided by two.

- 2. Rx VCO, serves as LO for the second conversion, Operates at 463 MHz.

- 3. Hopping synthesizer, Operate in the frequency range of 1962 MHz to 2040 MHz, Step size is 1 MHz.

There is also a Reference Oscillator that operating at 40 MHz. After division by 2 its signal is used as reference for all 3 VCO's.

All 3 synthesizers are frequency locked by use of PLL.

3.3 Transmit Path.

The transmit path consists of a modulator operating at twice the IF frequency, Hopping VCO, Up converter, PA and Diversity switch.

In transmit mode the divider is operated and thus enabling the division of the modulator by 2. This signal is upconverted by mixing it with the hopping signal that operates as LO. The mixed signal that is now in the 2.4 GHz band is filtered and fed to the PA, filtered again and through the diversity switch feeds the antenna. The modulating signal is a 2, 4 or 8 levels analog signal.

### 3.4 Receive Path.

The received signal is received in any of the antennas, selected by the diversity switch, filtered and transferred to the LNA, filtered again and down converted by mixing the received signal with the hopping synthesizer. The product has a 440 MHz IF where the signal is filtered and down converted to 23 MHz where it is demodulated into baseband signal. The baseband signal is filtered and transferred to the baseband processor. The output signal is a 2, 4, or 8 levels analog signal with 0.5 MHz bandwidth.

Fig.2. Radio Part Block Diagram

## 4. Block Diagram of Baseband Part.

Baseband Part consists of Modem and Analog interface for Radio (see Fig.1).

The Modem chip (BOORI) is the system master clock distributor (see Fig.3). It is running from 40MHz Crystal Oscillator Circuit (+/- 10ppm tolerance and +/- 4ppm stability ). R \_CLK1 default frequency is 4MHz which is division by 2.5 and 4 from the 40MHz clock.

Fig.3. Clock Distribution

## 5. Block Diagram of Digital Part.

The Digital Part consist of (see Fig.1):

### **CPU**

31Mhz MC68EN360 controller (QUICC);

## Memory

16/32Mbit 16 bits bus width sector erase Flash with 64kB uniform sectors; Additional 64kB E^2PROM;

DRAM banks;

48 bits MAC address serial ROM (BreezeCom customized special regitry); **I/O Ports**

24 bits off-QUICC Input/Output ports;

8 SMD miniature DIP switches and 8 hard jumpers for software and hardware configurations and versions.

### **Monitor Ports**

3 wires miniature connector 2 on-PCB test pads(optionally, for BOORI debugging) RS232 Transceiver

### **Ethernet (see Fig.4)**

4(SA40) 10BaseT ports

Motorola compatible Ethernet transceiver

10BaseT Analog interface for 4 ports

AUI using for multiport configuration

SCC1 of QUICC

Fig.4. Ethernet Interface Block Diagram