# **AES 7880-A**

# UHF DATA TRANSCEIVER

# **USER MANUAL**

December 9, 2004

**Notice:**

The exterior of any product containing this device must contain the following label:

"Contains FCC ID: L9N-7880-A"

#### Warning:

This device must be professionally installed with appropriate power supply and antenna in order to ensure proper operation. For outdoor applications, the antenna gain must not exceed 10 dBi. For indoor applications, the antenna gain must not exceed 2.2 dBi.

## Warning:

This device may not be modified by the user. Any modifications not expressly approved by AES Corporation could void the user's authority to operate the equipment.

## Warning:

For FCC RF exposure compliance purpose, this device may not be incorporated into any product which operates within 50 cm of a person under normal operation.

## 1.0 Description

The AES Model 7880-A UHF Data Transceiver permits data to be transmitted in the  $421 \sim 470$  MHz band of frequencies. The maximum output power is 1 W. The data rate is 9600 baud. The 7880-A interfaces with an embedded microprocessor using a simple 4-wire serial Programming Port. The operating parameters are set by AES approved software.

## **B2.0** Signals

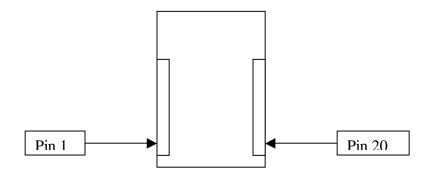

The 7880-A has 20 pins, consisting of 2 rows of 10 pins each. The following diagram (bottom view) shows the pin numbering scheme:

The following table lists the signal pins and their function:

| Pin                                 | Name                       | Function                                                                                                                                         |

|-------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 19<br>18<br>17<br>16                | PSEL<br>PCLK<br>PDI<br>PDO | Select Programming Port (active low)<br>Serial Clock for Programming Port<br>Data Input for Programing Port<br>Data Output from Programming Port |

| 2 3                                 | DCLK<br>DIO                | Data Clock for Synchronous Data<br>Data Input/Output for Synchronous Data                                                                        |

| 5<br>1<br>8<br>10<br>11<br>13<br>20 | VCC<br>GND<br>" " "        | Power (+5 volts, 900 mA max)<br>Ground                                                                                                           |

#### 3.0 Calibration

The 7880-A has a single adjustment – the Crystal Oscillator frequency. In order to adjust the Crystal Oscillator frequency, a suitable frequency counter must be attached to the antenna port. With the 7880-A set to transmit, using Manchester coding, the Crystal Oscillator may be adjusted until the average frequency measured by the frequency counter corresponds to the desired center frequency. The average frequency should be set to within 300 Hz of the desired value. Note: The frequency counter must be capable of measuring up to 470 MHz with an accuracy of 100 Hz in order to ensure proper calibration of the 7880-A.

#### 4.0 Device Programming

The operation of the 7880-A is controlled by the Programming Port. The protocol conforms to the Serial Peripheral Interface (SPI), originated by Motorola. The interface operates in a full duplex manner, with data shifted into the PDI pin at the same time as data is shifted out on the PDO pin. Data transfer cycles are initiated by the low-going transition of the PSEL pin; individual data bits are synchronized to the PCLK pin.

#### 5.0 Data Communication

The DIO pin is bidirectional. When the 7880-A is in transmit mode, the DIO pin becomes an input for the data to be transmitted. When the 7880-A is in receive mode, the DIO pin becomes an output. In both cases, the data is synchronized to the DCLK pin.