# INTRODUCTION

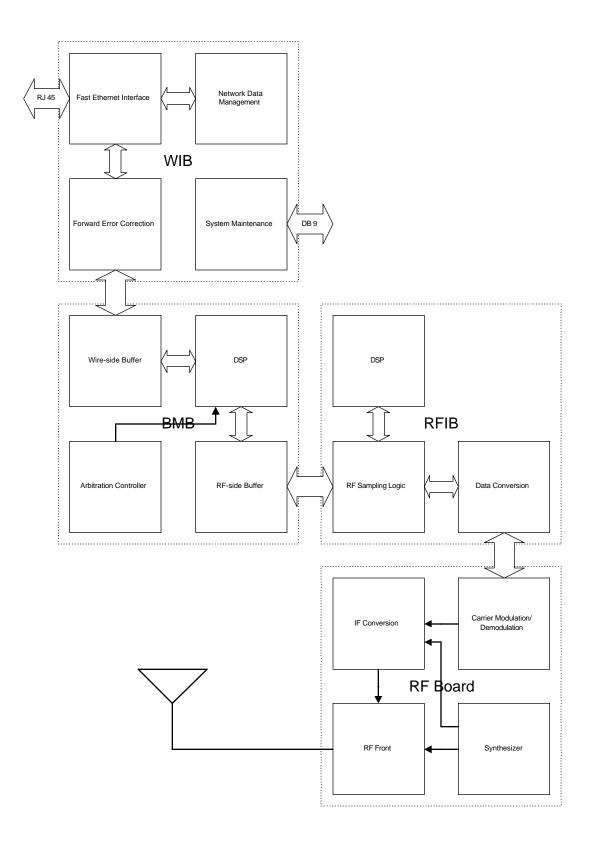

The W-OFDM 30024 is a wireless Ethernet transceiver using Wide-band Orthogonal Frequency Division Multiplexing (W-OFDM) modulation/demodulation technology. The W-OFDM transceiver transfers data in half-duplex mode at a rate of 30 Mbps within a 25 MHz bandwidth in the 2.4 GHz Industrial, Scientific and Medical (ISM) band. Figure 1.1 shows the main functional blocks of a W-OFDM 30024 system. It consists four main boards, a Wire Interface Board (WIB), a Baseband Modulation Board (BMB), an RF Interface Board (RFIB), and an RF Board. This document delineates these major function boards.

Figure 1 W-OFDM 30024 Block Diagram

# **FUNCTIONAL DESCRIPTION**

### Wire Interface Board

The Wire Interface Board connects the W-OFDM 30024 system to a data network. The board serves four major purposes, a Fast Ethernet Interface, network data management, system maintenance, and Forward Error Correction (FEC).

The Fast Ethernet Interface on the WIB, which complies with the IEEE 802.3 Standard, can operate at a maximum data rate of 100 Mbps with auto-negotiation capability.

The WIB is also responsible to control the data traffics passing through the system. Packet filtering is done on the data coming from the Ethernet network using Content Addressable Memory (CAM) to prevent local traffics from overflowing the wireless link. In addition, bandwidth management is implemented on the WIB to maintain the efficiency of the system.

The transmitted data are encoded with a Forward Error Correction (FEC) scheme, and decoded on the receiving unit accordingly on the WIB. Due to the nature of the errors in OFDM symbols in a multi-path environment, Reed-Solomon Coding, one of the FEC schemes, is the best candidate for the W-OFDM 30024 system.

There is a system maintenance port on the WIB. The major functions of the port are network statistics collection, network system configuration, and system maintenance.

## **Baseband Modulation Board**

The Baseband Modulation Board is the heart of a W-OFDM 30024 system. The board modulates the transmitted data and demodulates the received data respectively according to the OFDM algorithm. It includes four blocks, Wire-side Buffer, DSP, Arbitration Controller and RF-side Buffer.

The Wire-side Buffer is namely the storage of the transferred data between the WIB and the BMB. The requirement for the buffer on each direction is to hold minimum of two super-frames to increase the efficiency of data transferring – read from and write to the buffer simultaneously.

The DSP block is responsible to modulate or demodulate the transferred data. On the transmitting side, the OFDM scheme is performed on the complex data generated by 16 QAM, whereas the exact reverse operation is performed on the receiving side. Channel estimation and phase randomization are also implemented in the DSP block to overcome the problems of high peak-to-average signal amplitude and fading due to multi-path effects. To achieve 30 Mbps data throughput, at least four DSPs are required based on the calculation of 9 Mbps per DSP, including arbitration latency. The TMS320C6201 of Texas Instrument running at 200 MHz is used in such calculation.

The function of the Arbitration Controller is to orchestrate the DSPs. Since the arbitration scheme can directly impact the throughput of the system, an effective method is needed to maintain a desired throughput.

Similar to the Wire-side Buffer, the RF-side Buffer is used to store transferred data between the RFIB and the BMB. The buffers in each direction should be large enough to contain one modulated super-frame. Assuming a modulated super-frame is 0.5 ms long, with 25 M Samples/s, and 2 bytes (I and Q) per sample, the minimum size of the buffers in each direction therefore is 25 Kbytes.

### **RF Interface Board**

The RF Interface Board converts baseband signals to analog ones or vise versa between the BMB and RF board. The RFIB, in addition, manages the automatic gain control, signal synchronization and wireless link protocol. Three main components, RF Sampling Logic, DSP, Data Conversion are on the RFIB.

The RF Sampling Logic interfaces the A/D Conversion block and the D/A Conversion block on the RFIB with the BMB's RF-side Buffer. Since the system is half-duplex operation, coordination of A/D conversion and D/A conversion is necessary. Automatic gain control and signal synchronization are also implemented in the block when a system is used as a receiver.

The DSP serves two purposes, wireless link protocol and signal synchronization. Since the W-OFDM 30024 is designed for a point to multi-point network, a wireless link protocol is required to arbitrate the network traffics among stations. Prior to the actual OFDM data, a Direct Spread Spectrum Sequence (DSSS) header is generated by the DSP to obtain signal synchronization between a transmitter and a receiver.

Data Conversion performs two functions, A/D conversion and D/A conversion. A/D converts the transmitted digital signal to analog one and output it to the RF board, while D/A converts the received analog signal to digital one. Eight-bit data bus is used at all digital channel.

### RF Board

The RF board is the wireless link end of a W-OFDM 30024 system. As a transmitter, the board modulates the baseband signal from the RFIB to a desired frequency band, 2.4 GHz ISM band in this application. Reverse operation is performed when a system acts as a receiver. Four major blocks, Carrier Modulation/Demodulation, IF Conversion, RF Front, and Synthesizer are on the RF board.

Carrier Modulation/Demodulation block is responsible to modulate the baseband signals, both I/Q, with a carrier frequency, i.e., 915 MHz, and to demodulate the RF signal into baseband signals.

IF Conversion block upward converts the modulated signal from the Carrier Modulation/Demodulation to the final 2.4 GHz signal before it is sent off air. On the other hand, the IF Conversion block provides down conversion to the received RF signals back to the original carrier frequency.

RF Front sends or receives the OFDM modulated signals at 2.4 GHz ISM band. The block is controlled by the RFIB to switch between transmit and receive mode. The switching time should be  $1.5~\mu s$ .

Synthesizer is the central control block of the RF board. It controls both Local Oscillators (LO) to the Carrier Modulation/Demodulation and the IF Conversion.