# Measurement and Evaluation of Tracer Processing Gain

# Prepared By:

Matthew Kliesner Adtran, Inc. 901 Explorer Blvd. P.O. Box 140000 Huntsville, AL 35814-4000

#### **Measurement and Evaluation of Tracer Processing Gain**

To comply with FCC Regulations part 15.247(e), a direct-sequence spread spectrum system must have a processing gain of at least 10 dB. This document details the measurement and calculation of the processing gain of the Tracer spread spectrum system, marketed by Adtran, Inc.

The processing gain of the Tracer was measured using the CW jamming margin method. Guidelines for this method were obtained from the FCC publication "Guidance on Measurements for Direct Sequence Spread Spectrum Systems" found as Appendix C of FCC 97-114.

Results of this test, found in section 3 of this document, verify that the Tracer has between 13.5 and 15.5 dB of processing gain, satisfying part 15.247(e) requirements.

### 1.0 Test Configuration

A table of test hardware model numbers and serial numbers is attached as Appendix A.

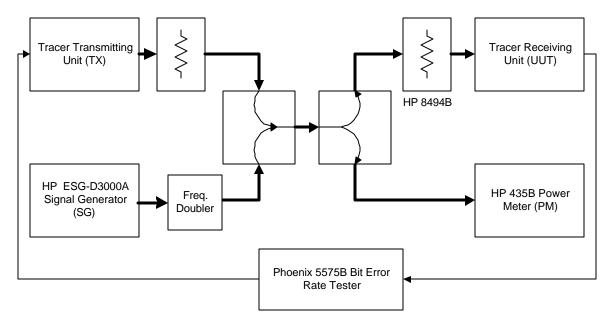

The setup of this test was derived from FCC guidance<sup>1</sup>. Jamming signals were generated with an HP ESG-D3000A signal generator and a frequency doubler. An HP 435B Power Meter was used for power measurements. Mini-Circuits power splitters and an HP 8494B RF attenuator were present in the received signal path. Figure 1 details physical test setup configurations.

The Tracer Transmitting Unit transmitted at a center frequency of 5747 MHz and at a power level of approximately 0 dBm. The HP attenuator provided 40 dB of signal loss to ensure a nominal received signal and a 20 dB pad was placed next to the Transmitting Unit to allow for a reading on the power meter to be obtained. Each power meter reading was adjusted accordingly for this extra 20 dB of signal loss. The unit under test (UUT) received at a center frequency of 5747 MHz, and did not provide a transmitting signal onto the coax.

The recommended bit error rate (BER) was chosen at 1E-6 for this test. If the UUT lost signal lock before the error rate degraded to this level, the greatest tolerable jammer level was recorded.

Page 4

Figure 1

Jamming Test Setup

#### 2.0 Testing Procedure

Test data and calculation results are listed in Appendix B.

#### 2.1 Received Signal Power

Received signal power was calculated with the power meter. The signal generator's RF was turned off then the signal was read on the power meter at -22.4 dBm. This combined with the 40 dBm of signal loss from the variable attenuator gives a measured received signal power level of -62.4 dBm.

#### 2.2 Jammer Power

The jamming signal power measurements were made by referring to the power meter. The signal generator was set on frequencies varying from 5725-5787 GHz. At every 50 KHz the jammer signal power was measured then an extra -40 dBm was added for the signal loss through the variable attenuator.

## 2.3 Jammer to Signal Ratio

Jammer to Signal (J/S) calculations were made by taking the jammer and received signal levels and computing the ratio at each frequency. These calculations are shown beside the data in Appendix A. The J/S ratios were then sorted, and the lowest 20% were discarded. The lowest remaining J/S ratio was 4.5 dB.

#### 2.4 Ideal Signal to Noise Ratio of the Tracer System

The signal to noise ratio for an ideal differential QPSK system at a 1E-6 bit error rate (BER) is approximately 13 dB<sup>2</sup>. The Tracer system employs an error-correction algorithm that provides 4 dB of gain<sup>3</sup>. This gain improves resistance to jamming signals independent of processing gain. Therefore, the ideal signal to noise ratio for the Tracer system should be 9 dB.

Measurement and Evaluation on Tracer Processing Gain

#### 3.0 Tracer System Processing Gain

The processing gain of a direct sequence spread spectrum system can be calculated with the following equation:

$$Gp = (S/N)o + Mj + Lsys$$

where: (S/N)o = Signal to noise ratio for a given modulation scheme and bit error rate (BER). Mj = J/S ratio.

Lsys = system implementation losses for a practical system.

The ideal processing gain for a 12-chip-per-bit spreading system is 10\*log(12), or 10.8 dB. Assuming a (S/N)o of 9dB, a measured Mj of 4.5dB, and no system loss (Lsys = 0), the calculated processing gain is 13.5 dB. Assuming 2dB of losses (due to filtering, etc), Gp is 15.5 dB. The actual system processing gain lies somewhere within this range.

These calculated gains, with and without system losses, both satisfy the FCC Part 15.247(e) requirement of a minimum 10 dB of processing gain for a direct sequence spread spectrum system.

<sup>&</sup>lt;sup>1</sup> "Guidance on Measurements for Direct Sequence Spread Spectrum Systems." FCC 97-114, Appendix C. Federal Communications Commission, 1997.

<sup>2</sup> Bennett, William R. and Davey, James R. <u>Data Transmission.</u> (New York, McGraw-Hill 1965), Pg. 211

<sup>3</sup> "Q1650 Viterbi Decoder Technical Data Sheet". (Qualcomm, Inc. 1995), Pg. 12