# 4G EXC-N1 Module DataSheet

Version : AB Update date : Sep. 20, 2022

# Copyright

Copyright © 2022 COMPAL ELECTRONICS, INC. All rights reserved.

Without the prior written permission of the copyright holder, any company or individual is prohibited to excerpt, copy any part of or the entire document, or distribute the document in any form.

### Notice

The document is subject to update from time to time owing to the product version upgrade or other reasons. Unless otherwise specified, the document only serves as the user guide. All the statements, information and suggestions contained in the document do not constitute any explicit or implicit guarantee.

# **Revision History**

| Versio<br>n | Date          | Name          | Major Changes                                                               |  |

|-------------|---------------|---------------|-----------------------------------------------------------------------------|--|

| AA          | Aug. 31, 2022 | <b>HW</b> V01 | First release                                                               |  |

| AB          | Sep. 20, 2022 | <b>HW</b> V01 | • Only support B41M , modify B41to B41M and frequency range on P12/49/59/60 |  |

| AD          |               |               | • Remove power consumption @ GSM/WCDMA/LTE mode on P31-35                   |  |

# **Applicability Table**

| No. | Product model | Description                                                                                                                                                              |

|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ZXG1          | 4G EXC-N1: (V1.0 Module)<br><u>All relevant LCC HW spec &gt; figures and design guidelines in this</u><br><u>document are common specification for All 4G LCC model.</u> |

|     |               |                                                                                                                                                                          |

# Content

| 1 |     | Forewor  | ·d                                         | 7  |

|---|-----|----------|--------------------------------------------|----|

|   | 1.1 | Intro    | duction                                    | 7  |

|   | 1.2 | Safet    | y Information                              | 7  |

|   | 1.3 | Refer    | ence Standard (to be update)               |    |

|   | 1.4 | Relat    | ed Documents                               |    |

| 2 |     | Overvie  | w                                          | 12 |

|   | 2.1 | Intro    | duction                                    |    |

|   | 2.2 | Speci    | fication                                   |    |

|   | 2.3 | CA c     | ombinations                                | 15 |

|   | 2.4 | EN-E     | DC combinations with in 5G FR1             | 15 |

|   | 2.5 | EN-E     | DC combinations with in 5G FR2             | 15 |

|   | 2.6 | Circu    | it Block Diagram                           | 15 |

|   | 2.7 | Appl     | ication Block Diagram                      |    |

| 3 |     | Applicat | tion Interface                             |    |

|   | 3.1 | LCC      | Interface                                  |    |

|   | 3.2 | Pin N    | 1ар                                        |    |

|   |     | 3.2.1    | Pin Definition                             |    |

|   | 3.3 | Powe     | r Interface                                | 27 |

|   |     | 3.3.1    | Power Supply                               |    |

|   |     | 3.3.2    | Logic level                                |    |

|   |     | 3.3.3    | Power Consumption                          |    |

|   | 3.4 | Signa    | Il Control Interface                       |    |

|   |     | 3.4.1    | Overview                                   |    |

|   |     | 3.4.2    | PWRKEY Pin                                 |    |

|   |     | 3.4.3    | RESET_N Pin                                |    |

|   |     | 3.4.4    | LED_MODE Signal                            |    |

|   |     | 3.4.5    | Forced Boot                                |    |

|   | 3.5 |          | T Interface                                |    |

|   |     | 3.5.1    | Overview                                   |    |

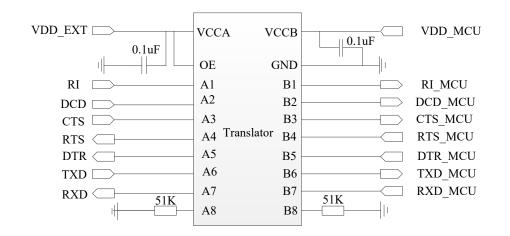

|   | 26  | 3.5.2    | Circuit Recommended for the UART Interface |    |

|   | 3.6 |          | and I2C Interface                          |    |

|   | 3.7 |          | nterface                                   |    |

|   | 3.8 |          |                                            |    |

|   |     | 3.8.1    | Overview                                   | 41 |

# COMPAL Electronics, INC.

|   | 3    | 8.8.2          | USB Interface Definition                        | 41 |

|---|------|----------------|-------------------------------------------------|----|

|   | 3    | 3.8.3          | USB Interface Application                       | 42 |

|   | 3    | 3.8.4          | USB Interface Layout Guide                      | 42 |

|   | 3.9  | PCIe           | Interface                                       | 43 |

|   | 3    | 9.1            | Overview                                        | 43 |

|   | 3    | 9.9.2          | PCIe Interface Definition                       | 43 |

|   | 3    | 9.9.3          | PCIe Interface Application                      | 43 |

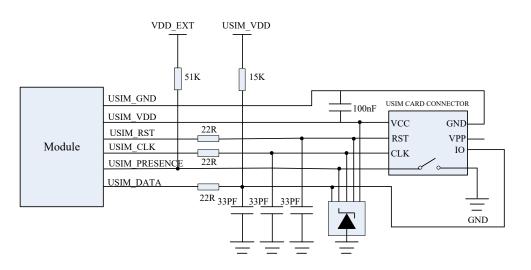

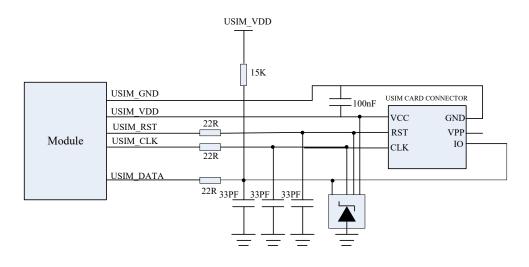

|   | 3.10 | USIM           | I Card Interface                                | 43 |

|   | 3    | 8.10.1         | Overview                                        | 44 |

|   | 3    | 3.10.2         | Circuit Recommended for the USIM Card Interface | 44 |

|   | 3.11 | Audio          | Interface                                       | 46 |

|   | 3.12 | Gener          | al Purpose I/O Interface (Reserved GPIO)        | 46 |

|   | 3.13 | JTAG           | Interface                                       | 47 |

|   | 3.14 | RF Ar          | ntenna Interface                                | 47 |

|   | 3    | 8.14.1         | RF Connector Characteristic                     | 49 |

|   | 3    | 3.14.2         | RF Connector Dimension                          | 49 |

|   | 3.15 | Reserv         | ved Interface                                   | 49 |

|   | 3.16 | NC In          | iterface                                        | 50 |

|   | 3.17 | Tunab          | ole Antenna Control                             |    |

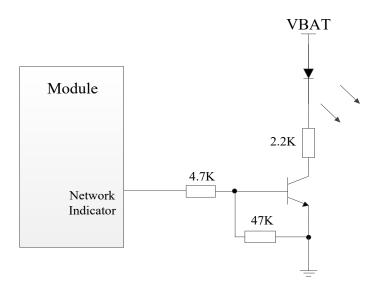

|   | 3.18 | Netwo          | ork status indication                           |    |

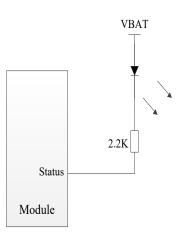

|   | 3.19 | Status         |                                                 |    |

|   | 3.20 | ADC            | Interface                                       |    |

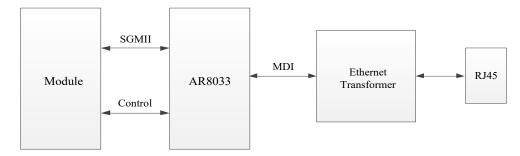

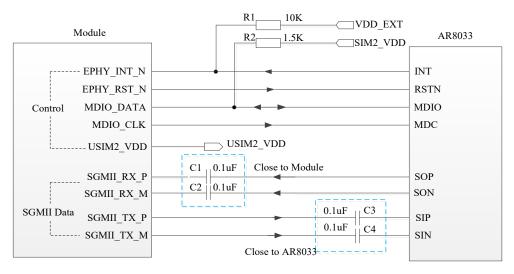

|   | 3.21 | SGMI           | II interface                                    |    |

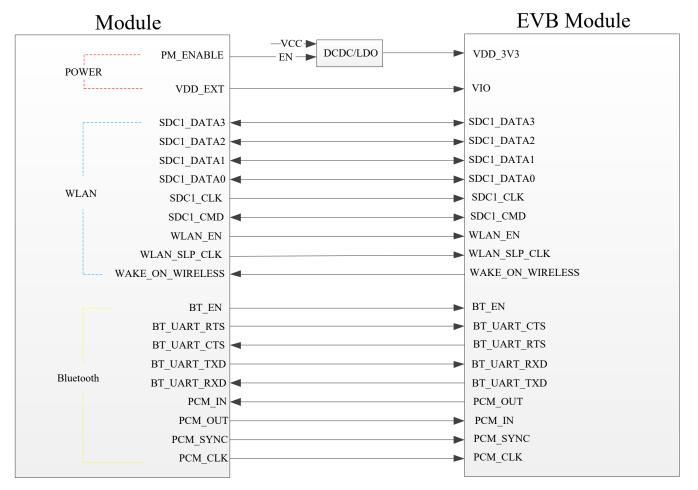

|   | 3.22 | Wirele         | ess Connectivity Interfaces                     |    |

|   |      | 3.22.1         | WLAN Interface                                  |    |

|   |      | 3.22.2         | BT Interface                                    |    |

|   | 3.23 |                | rd interface                                    |    |

| 4 | F    | Radio Fr       | equency                                         |    |

|   | 4.1  |                | view                                            |    |

|   | 4.2  |                | ting Band                                       |    |

|   | 4.3  | 1              | mpalver Sensitivity                             |    |

|   | 4.4  |                |                                                 |    |

|   | 4.5  |                | na Design                                       |    |

|   |      | Anten          |                                                 |    |

|   |      | 4.5.1<br>4.5.2 | Interference Antenna Requirements               |    |

|   | 4.6  |                | Antenna Requirements                            |    |

|   | ч.U  | ivi, a v       |                                                 | 02 |

# COMPAL Electronics, INC.

|   | 4    | 1.6.1     | Purpose                                   |    |

|---|------|-----------|-------------------------------------------|----|

|   | 4    | 1.6.2     | Co-existence Design Main Point            |    |

| 5 | N    | Mechani   | cal Specifications                        |    |

| 5 | 5.1  | Overv     | view                                      |    |

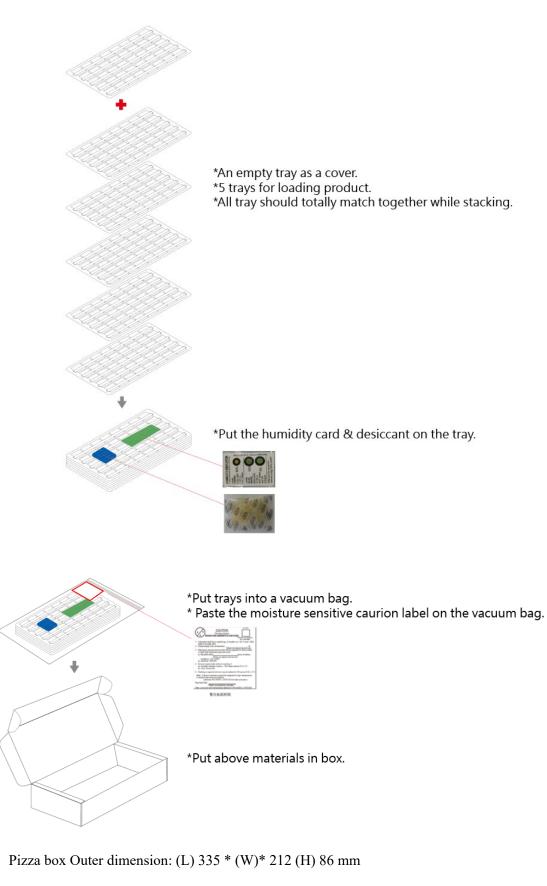

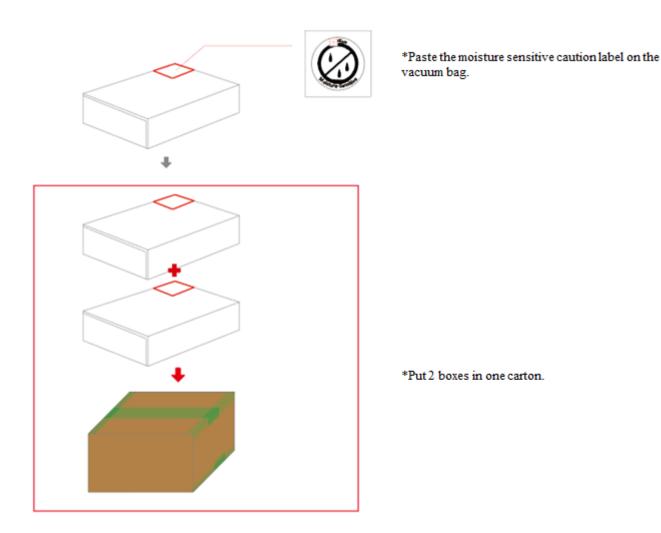

| 4 | 5.2  | Stora     | ge Requirement                            | 63 |

| 5 | 5.3  | Moist     | ture Sensitivity                          | 64 |

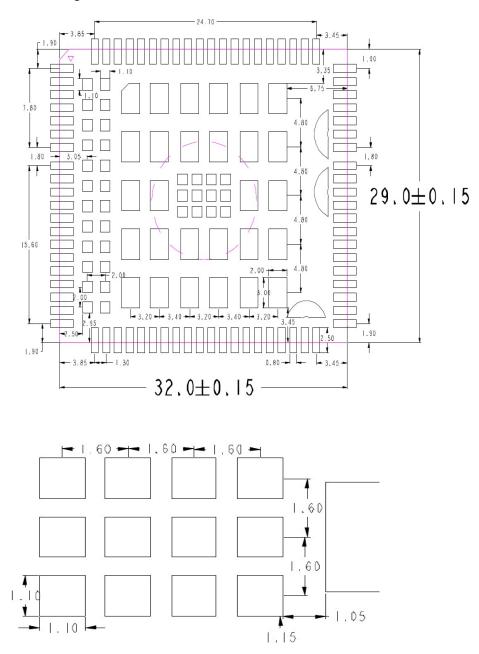

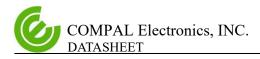

| 5 | 5.4  | Dime      | nsions and Interfaces                     | 64 |

| 4 | 5.5  | Packa     | iging (To be update)                      | 64 |

| 4 | 5.6  |           | Marking                                   |    |

|   | 5.7  |           | mer PCB Design                            |    |

|   |      | 5.7.1     | PCB Surface Finish                        |    |

|   |      | 5.7.2     | PCB Pad Design                            |    |

|   |      | 5.7.3     | Solder Mask                               |    |

|   | 5    | 5.7.4     | Requirements on PCB Layout                |    |

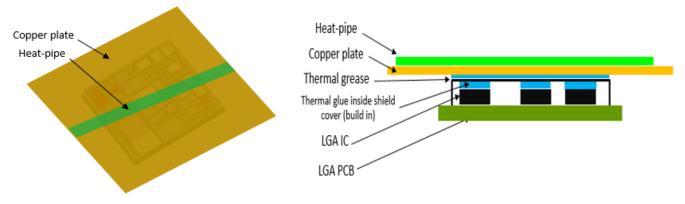

| 5 | 5.8  | Therr     | nal Design Solution                       |    |

| 4 | 5.9  | Asser     | nbly Processes                            |    |

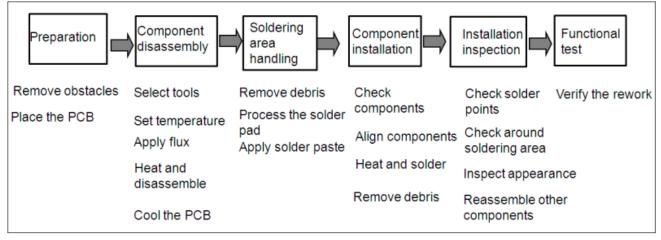

|   | 5    | 5.9.1     | General Description of Assembly Processes |    |

|   | 5    | 5.9.2     | Stencil Design                            |    |

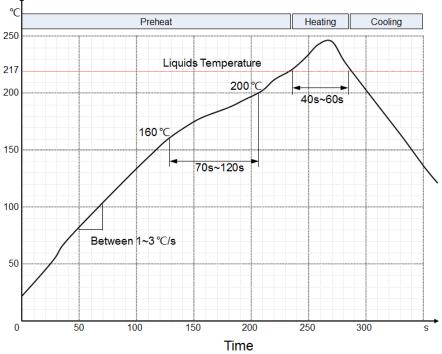

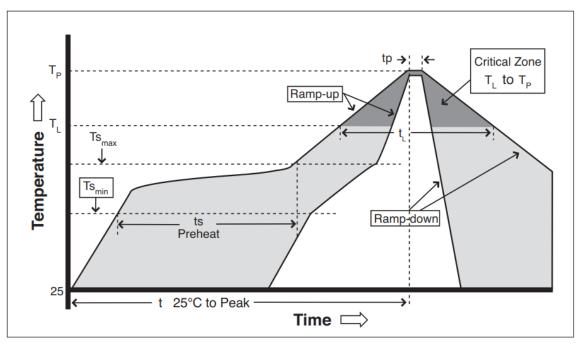

|   | 5    | 5.9.3     | Reflow Profile                            |    |

| 5 | 5.10 | Speci     | fication of Rework                        |    |

|   | 5    | 5.10.1    | Process of Rework                         |    |

|   | 5    | 5.10.2    | Preparations of Rework                    |    |

|   | 5    | 5.10.3    | Removing of the Module                    |    |

|   | 5    | 5.10.4    | Welding Area Treatment                    | 74 |

|   | 5    | 5.10.5    | Module Installation                       | 74 |

|   | 5    | 5.10.6    | Specifications of Rework                  |    |

| 5 | 5.11 | Order     | ing information                           |    |

|   | 5    | 5.11.1    | Specification-compliant devices           |    |

| 6 | F    | Reliabili | ty test                                   |    |

| 6 | 5.1  | ESD       | Features                                  |    |

# 1 Foreword

#### 1.1 Introduction

This document defines the EXC-N1 module and the air interface and hardware interface that the module connects to the client application.

This document helps customers quickly understand EXC-N1 module interface specifications, electrical characteristics, mechanical specifications, and related product information. With the help of this document, combined with our application manual and user instructions, customers can quickly apply the EXC-N1 module to wireless applications.

EXC-N1 wireless module is a vehicle standard wireless broadband terminal product applicable to TDD-LTE/FDD-LTE/WCDMA.

EXC-N1 can support access rates:

- TDD-LTE:130Mbps/35Mbps;

- FDD-LTE:150Mbps/50Mbps;

- WCDMA rate up to DC HSPA+: 42Mbps/5.76Mbps;

- GSM rate up to EDGE: 236.8kbps/236.8kbps. (N/A)

#### **1.2 Safety Information**

The following safety precautions must be observed during all phases of operation, such as usage, service or repair of any cellular terminal or mobile incorporating with 4G LCC module. Manufacturers of the cellular terminal should send the following safety information to users and operating personnel, and incorporate these guidelines into all manuals supplied with the product. If not so, we assume no liability for customers' failure to comply with these precautions.

..Full attention must be given to driving at all times in order to reduce the risk of an accident. Using a mobile while driving (even with a handsfree kit) causes distraction and can lead to an accident. Please comply with laws and regulations restricting the use of wireless devices while driving.

Switch off the cellular terminal or mobile before boarding an aircraft. The

operation of wireless appliances in an aircraft is forbidden to prevent interference with communication systems. If the device offers an Airplane Mode, then it should be enabled prior to boarding an aircraft. Please consult the airline staff for more restrictions on the use of wireless devices on boarding the aircraft.

Wireless devices may cause interference on sensitive medical equipment, so please be aware of the restrictions on the use of wireless devices when in hospitals, clinics or other healthcare facilities.

Cellular terminals or mobiles operating over radio signals and cellular network cannot be guaranteed to connect in all possible conditions (for example, with unpaid bills or with an invalid SIM card). When emergent help is needed in such conditions, please remember using emergency call. In order to make or reCompalve a call, the cellular terminal or mobile must be switched on in a service area with adequate cellular signal strength.

The cellular terminal or mobile contains a transmitter and reCompalver. When it is ON, it reCompalves and transmits radio frequency signals. RF interference can occur if it is used close to TV set, radio, computer or other electricequipment.

In locations with potentially explosive atmospheres, obey all posted signs to turn off wireless devices such as your phone or other cellular terminals. Areas with potentially explosive atmospheres include fueling areas, below decks on boats, fuel or chemical transfer or storage facilities, areas where the air contains chemicals or particles such as grain, dust or metal powders, etc.

# Safety of Children

Do not allow children to use the wireless device without guidance. Small and sharp components of the wireless device may cause danger to children or cause suffocation if children swallow the components.

# **Environment Protection**

Observe the local regulations regarding the disposal of your packaging materials, used wireless device and accessories, and promote their recycling.

# **WEEE Approval**

The wireless device is in compliance with the essential requirements and other relevant provisions of the Waste Electrical and Electronic Equipment Directive 2012/19/EU (WEEE Directive).

# **RoHS** Approval

The wireless device is in compliance with the restriction of the use of certain hazardous substances in electrical and electronic equipment Directive 2011/65/EU (RoHS Directive).

# **1.3** Reference Standard (to be update)

The design of the product complies with the following standards:

#### Table1-1 3GPP Standards

| 3GPP TS       |                                                                                       | <b>3GPP Release used as the</b> |

|---------------|---------------------------------------------------------------------------------------|---------------------------------|

| specification | Title                                                                                 | basis for this                  |

| reference     |                                                                                       | declaration                     |

| 23.122        | Non-Access-Stratum functions related to Mobile Station (MS) in idle mode              | 11.4.0                          |

| 24.008        | Mobile radio interface Layer 3 specification; Core network protocols; Stage 3         | 11.5.0                          |

| 25.331        | Radio Resource Control (RRC); protocol specification                                  | 9.0.0                           |

| 25.133        | Requirements for Support of Radio Resource Management (FDD)                           | 13.2.0                          |

| 25.101        | Radio Transmission and Reception (FDD)                                                | 14.0.0                          |

| 24.301        | (NAS) protocol for Evolved Packet System (EPS); Stage 3                               | 11.7.0                          |

| 36.101        | (E-UTRA); User Equipment (UE) radio transmission and reception                        | 12.14.1                         |

| 36.133        | (E-UTRA); Requirements for support of radio resource management                       | 14.14.0                         |

| 36.213        | (E-UTRA) Physical layer procedures                                                    | 12.11.0                         |

| 36.214        | (E-UTRA) Physical layer measurements                                                  | 12.3.0                          |

| 36.304        | (E-UTRA); User Equipment (UE) procedures in idle mode                                 | 12.8.0                          |

| 36.321        | (E-UTRA); Medium Access Control (MAC) protocol specification                          | 12.9.0                          |

| 36.322        | (E-UTRA); Radio Link Control (RLC) protocol specification                             | 12.4.0                          |

| 36.323        | (E-UTRA); Packet Data Convergence Protocol (PDCP) specification                       | 12.6.0                          |

| 36.331        | (E-UTRA); Radio Resource Control (RRC); Protocol specification                        | 15.3.0                          |

| 24.501        | Non-Access-Stratum (NAS) protocol for 5G System (5GS); Stage 3                        | 15.1.0                          |

| 38.331        | NR;Radio Resource Control (RRC) protocol specification                                | 15.3.0                          |

| 38.133        | NR; Requirements for support of radio resource management                             | 15.3.0                          |

| 38.213        | NR; Physical layer procedures for control                                             | 15.3.0                          |

| 38.323        | NR; Packet Data Convergence Protocol (PDCP) protocol specification                    | 15.3.0                          |

| 37.324        | Service Data Adaptation Protocol (SDAP) specification                                 | 15.1.0                          |

| 11.11/51.011  | Specification of the Subscriber Identity Module - Mobile Equipment (SIM-ME) Interface | 4.15.0                          |

| 31.102        | Characteristics of the Universal Subscriber Identity Module (USIM) application        | 12.11.0                         |

| 31.103        | Characteristics of the IP Multimedia Services Identity Module (ISIM) application      | 12.2.0                          |

| 31.101        | UICC-terminal interface; Physical and logical characteristics                         | 12.2.0                          |

| 27.007        | AT command set for 3GPP User Equipment (UE)                                           | 9.9.0                           |

| 36.355        | (E-UTRA); LTE Positioning Protocol (LPP)                                              | 14.2.0                          |

| 44.031        | Location Services (LCS)- MS-SMLC Radio Resource LCS Protocol (RRLP)                   | 14.3.0                          |

#### Non-3GPP documentation:

#### Table1-2 ETSI

| Document Source | Title                                                                        | Version |

|-----------------|------------------------------------------------------------------------------|---------|

| ETSI            | TS 102 221: "UICC-Terminal interface; Physical and logical characteristics". | 12.1.0  |

| ETSI            | TS 102 223: "Smart Cards; Card Application Toolkit". 12.3.0                  |         |

#### Table1-3 GSMA

| Document Source | Title                                              | Version |

|-----------------|----------------------------------------------------|---------|

| GSMA            | IR.92 IMS Profile for Voice and SMS                | 8.0.0   |

| GSMA            | IR.94 IMS Profile for Conversational Video Service | 7.0.0   |

#### Table1-4 OMA

| Document Source | Title          | Version |

|-----------------|----------------|---------|

| OMA             | OMA-AD-SUPL-V1 |         |

| OMA             | OMA-AD-SUPL-V2 |         |

## **1.4 Related Documents**

- 4G LCC Module System Driver Integration and Application Guidance

- 4G LCC Module AT Commands Manual

# 2 Overview

## 2.1 Introduction

EXC-N1 is support for TDD-LTE/FDD-LTE /WCDMA wireless communication module. It supports data connection of TDD-LTE and FDD-LTE networks, and is compatible with DC-HSPA+ of WCDMA network data connection. It can provide Voice (PCM), Analog voice, Short message, Address book and other functions for customers' special applications.

Table 2-1 EXC-N1 module support frequency bands

| Network  | EXC-N1                         |

|----------|--------------------------------|

| TDD-LTE  | B41M                           |

| FDD-LTE  | B2/4/5/7/12/13/17/<br>25/26/66 |

| WCDMA    | B2/4/5                         |

| TD-SCDMA | Not supported                  |

| EVDO     | Not supported                  |

| CDMA     | Not supported                  |

| GSM      | Not supported                  |

# 2.2 Specification

| Specification  |                                                          |  |

|----------------|----------------------------------------------------------|--|

| Platform       | QCT MDM9207 Cortex-A7 up to 1.2 GHz                      |  |

| Memory         | 1Gb NAND Flash with 1Gb LPDDR2(400MHz) MCP               |  |

| Operating Band | 5G Refarmed Sub6 : NA                                    |  |

|                | 5G NR_mmWave: N/A                                        |  |

|                | LTE FDD:<br>B2, B4, B5, B7, B12, B13, B17, B25, B26, B66 |  |

|                | LTE TDD:<br>B41M                                         |  |

|                | WCDMA/HSPA+:<br>B2, B4, B5                               |  |

|                     | Simultaneous GPS :<br>L1, GLONASS(GLO), Galileo(GAL) and BeiDou(BDS) |                               |  |  |  |

|---------------------|----------------------------------------------------------------------|-------------------------------|--|--|--|

|                     | SA                                                                   | N/A                           |  |  |  |

| Network option      | NSA                                                                  | N/A                           |  |  |  |

|                     | LTE                                                                  | LTE CAT4                      |  |  |  |

| Downlink            | 5G sub-6                                                             | N/A                           |  |  |  |

|                     | 5G mmWave                                                            | N/A                           |  |  |  |

|                     | LTE                                                                  | LTE CAT3                      |  |  |  |

| Uplink              | 5G sub-6                                                             | N/A                           |  |  |  |

|                     | 5G mmWave                                                            | N/A                           |  |  |  |

| HPUE (Class 2)      | N/A                                                                  |                               |  |  |  |

| UL 2x2 MIMO         | N/A                                                                  |                               |  |  |  |

| DL 4x4 MIMO         | N/A                                                                  |                               |  |  |  |

| Carrier aggregation | N/A                                                                  |                               |  |  |  |

| Power Supply        | DC $3.3V \sim 4.2V$ (Typical value is $3.8V$ )                       |                               |  |  |  |

|                     | Operating temperature[1]:-30°C $\sim$ +75°C                          |                               |  |  |  |

| Temperature         | Extended temperature[2] : $-40^{\circ}C \sim +85^{\circ}C$           |                               |  |  |  |

|                     | Storage temperature: $-45^{\circ}C \sim +90^{\circ}C$                |                               |  |  |  |

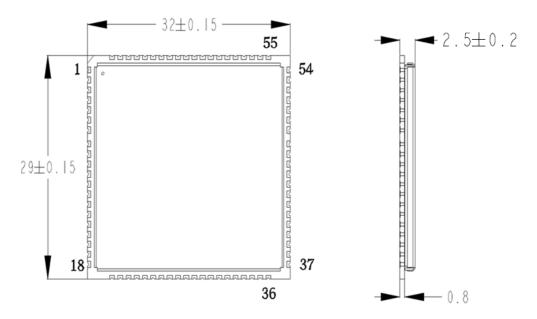

| Physical            | Dimension:32.0x2                                                     | 29.0mm, Thickness=2.5mm(typ.) |  |  |  |

| characteristics     | Weight: <5g                                                          |                               |  |  |  |

| Interface           |                                                                      |                               |  |  |  |

|                     | Main antenna (A                                                      | NT_MAIN)                      |  |  |  |

| Antenna Port        | RX- diversity ante                                                   | enna (ANT_DIV)                |  |  |  |

| Antenna Port        | GNSS antenna(A)                                                      | NT_GNSS)                      |  |  |  |

|                     | Power interface                                                      |                               |  |  |  |

|                     | USB2.0 High-Speed interface                                          |                               |  |  |  |

|                     | UART interface<br>USIM/SIM interface ( Support 3V,1.8V )             |                               |  |  |  |

|                     |                                                                      |                               |  |  |  |

|                     | PCM interface(op                                                     | tional)                       |  |  |  |

|                     | Reset interface                                                      |                               |  |  |  |

|                    | Indicator interface                |  |  |  |  |  |

|--------------------|------------------------------------|--|--|--|--|--|

|                    | Dormancy control interface         |  |  |  |  |  |

|                    | Flight mode control interface      |  |  |  |  |  |

|                    | ADC interface                      |  |  |  |  |  |

| Function Interface | I2C interface                      |  |  |  |  |  |

| Function Interface | SGMII interface(optional)          |  |  |  |  |  |

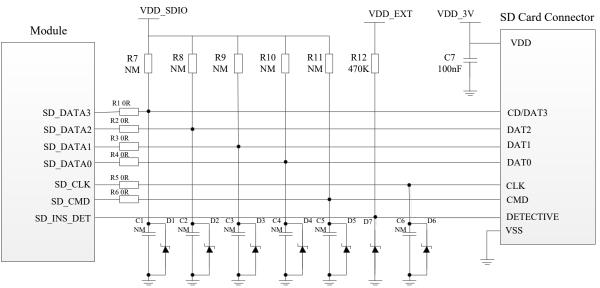

|                    | SD card interface(optional)        |  |  |  |  |  |

|                    | WLAN interface(optional)           |  |  |  |  |  |

|                    | BT_UART interface(optional)        |  |  |  |  |  |

|                    | USB_BOOT interface(optional)       |  |  |  |  |  |

| Software           |                                    |  |  |  |  |  |

| Driver             | TBD                                |  |  |  |  |  |

| Protocol Stack     | TBD                                |  |  |  |  |  |

| AT commands        | Comply with 3GPP TS 27.007, 27.005 |  |  |  |  |  |

| Firmware update    | FOTA (not support for 1Gb+1Gb )    |  |  |  |  |  |

| Others feature     | Windows MBIM support               |  |  |  |  |  |

|                    | Windows update                     |  |  |  |  |  |

|                    |                                    |  |  |  |  |  |

#

# NOTE:

[1] To meet this operating temperature range, you need to ensure effective thermal dissipation, for example, by adding passive or active heatsinks, heat pipes, vapor chambers, etc. Within this range, the module can meet 3GPP.

[2] To meet this extended temperature range, you need to ensure effective thermal dissipation, for example, by adding passive or active heatsinks, heat pipes, vapor chambers, etc. When the LCC module works at this temperature, the module remains the ability to establish and maintain functions such as voice, SMS, emergency call, etc.

Radio spectrum and radio network are not influenced, while one or more specifications, such as Pout, may undergo a reduction in value, exceeding the specified tolerances of 3GPP.

#### 2.3 CA combinations

N/A

- 2.4 EN-DC combinations with in 5G FR1 N/A

- 2.5 EN-DC combinations with in 5G FR2 N/A

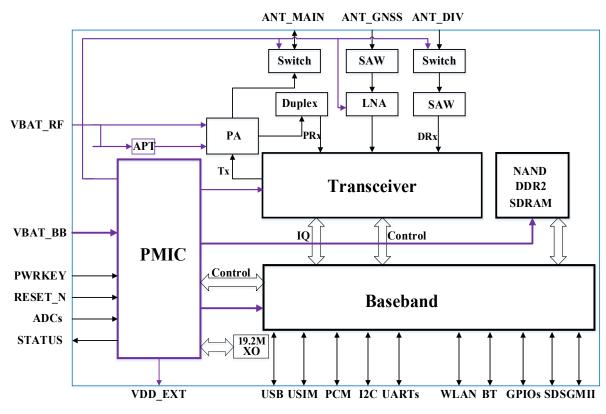

#### 2.6 Circuit Block Diagram

The following is the block diagram of EXC-N1, illustrating its main functions.

- Power management

- Baseband chip

- DDR + NAND memory

- RF part

- Peripheral interface

#### 2.7 Application Block Diagram

N/A

#### **Peripherals Interface Description:**

#### **USB Interface:**

The USB interface supports USB 2.0 high speed standard.

#### **SDIO Interface:**

Supports the SDIO 3.0 protocol

#### **USIM Interface:**

The USIM interface.

#### LCM:

N/A

#### **Audio Interface:**

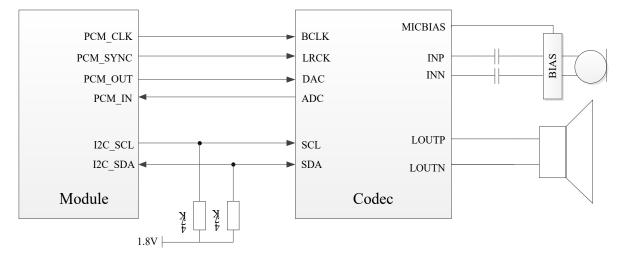

The module supports I2S/PCM interface (can be configured as either I2S or PCM interface)

#### **PCIE:**

N/A

#### **SPI Interface:**

N/A.

#### **I2C Interface:**

Reserved for intelligent module in future.

#### **UART Interface:**

The module supports 2 UART interfaces. One is 7-wire UARTs. One is 2-wire UART, which is only for debugging.

#### **External Power Supply:**

Output Power Supply from LCC module:

A. VDD\_EXT (1.8V) : External 1.8V output, Power supply for external GPIO's pull up circuits; If unused, keep it open

B. USIM\_VDD (1.8V/3V): USIM card supply voltage , Automatic module recognition 1.8V or 3.0V USIM card

C. USIM2\_VDD(1.8V/2.85V): SGMII MDIO pull-up power supply ,Output 1.8V/2.85V configurable; Can be used for pull-up, not directly for power supply. If unused, keep it open.

#### Extra Power Supply Require for LCC module:

- A. DC 3.8 V is recommended for module VPH\_PWR

- B. USB VBUS for USB detection

#### **RF Pad:**

RF antenna interface.(Main, Div, GNSS)

#### Tunable ANT CTRL:

N/A

#### SGMII:

The EXC-N1 module includes an integrated Ethernet MAC SGMII interface and two management interfaces (MDIO). Support 10/100/1000Mbps Ethernet connection

# **3** Application Interface

#### 3.1 LCC Interface

EXC-N1 adopts LCC+LGA interface, A total of 144 Pins, including 80 LCC pins and 64 LGA pins, are provided with the following functional interfaces:

- Power interface

- USB2.0 High-Speed interface

- UART interface

- USIM/SIM interface

- PCM interface

- Reset interface

- Indicator interface

- Dormancy control interface

- Flight mode control interface

- ADC interface

- I2C interface

- SGMII interface

- SD card interface

- WLAN interface

- BT\_UART interface

- USB\_BOOT interface

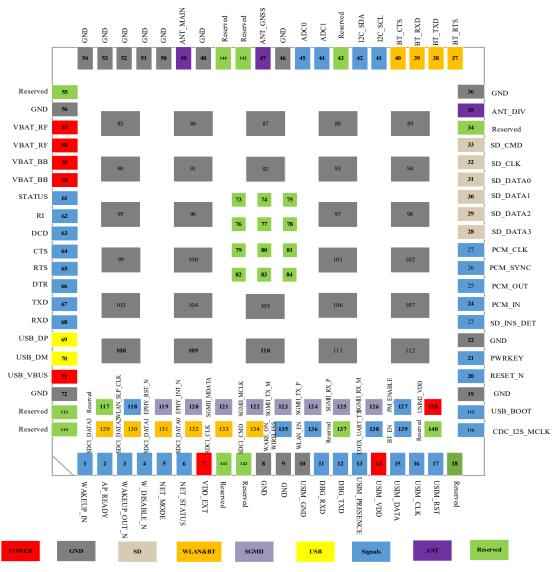

# 3.2 Pin Map

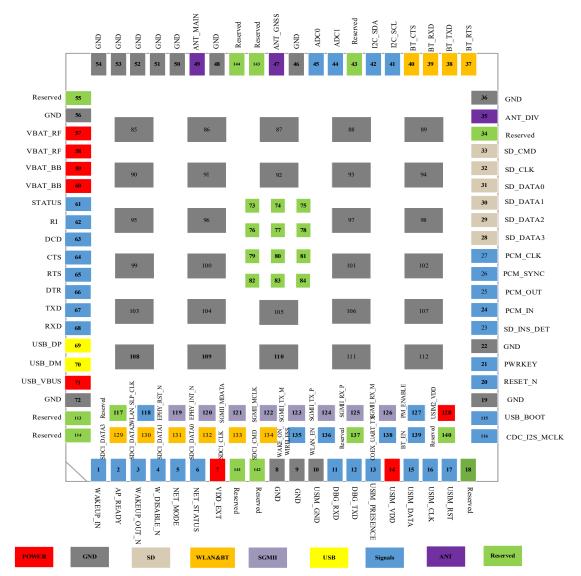

Figure 3-1 Module pin number diagram

#### 3.2.1 Pin Definition

The following table describes the definitions of the individual pins for the EXC-N1 module.

| Table 3-1 IO parameter of | definition |

|---------------------------|------------|

|---------------------------|------------|

| Туре | Description      |

|------|------------------|

| Ю    | Input and output |

| DI   | Digital input    |

| DO   | Digital output   |

| PI   | Power input      |

| РО | Power output  |

|----|---------------|

| AI | Analog input  |

| AO | Analog output |

| OD | Open drain    |

### Table 3-2 Pin description

| Pin name   | Pin<br>number                                               | I/O | Description                                           | DC features                                                                      | Note                                                                                             |

|------------|-------------------------------------------------------------|-----|-------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| VBAT_BB    | 59, 60                                                      | PI  | Power supply for module baseband                      | Vmax=4.2V<br>Vmin=3.3V<br>Vnorm=3.8V                                             | It must be able to provide<br>sufficient current up to 1A                                        |

| VBAT_RF    | 57, 58                                                      | PI  | Power supply for module<br>RF                         | Vmax=4.2V<br>Vmin=3.3V<br>Vnorm=3.8V                                             | It must be able to provide<br>sufficient current up to 2A                                        |

| VDD_EXT    | 7                                                           | РО  | 1.8V output                                           | Vnorm=1.8V<br>I₀max=80mA                                                         | Power supply for external<br>GPIO's pull up circuits; If<br>unused, keep it open                 |

| GND        | 8, 9, 19,<br>22, 36, 46,<br>48, 50~54,<br>56, 72,<br>85~112 | -   | Ground                                                | -                                                                                | -                                                                                                |

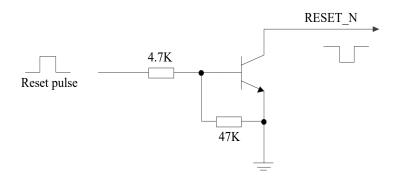

| RESET_N    | 20                                                          | DI  | Reset the module                                      | V <sub>IH</sub> max=2.1V<br>V <sub>IH</sub> min=1.3V<br>V <sub>IL</sub> max=0.5V | 1.8V power domain,<br>effective at low level; If<br>unused, keep it open                         |

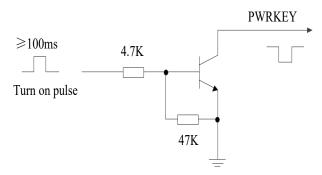

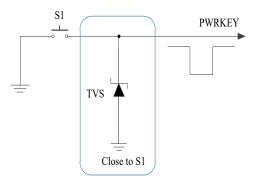

| PWRKEY     | 21                                                          | DI  | Turn on/off the<br>module                             | V <sub>IH</sub> max=2.1V<br>V <sub>IH</sub> min=1.3V<br>V <sub>IL</sub> max=0.5V | There is a voltage drop in<br>the diode inside the<br>High-pass chip, so the Pin<br>outputs 0.8V |

| STATUS     | 61                                                          | OD  | Indicate the module operating status                  | The drive current<br>should be less than<br>0.9mA                                | Require external<br>pull-up. If unused, keep it<br>open.                                         |

| NET_MODE   | 5                                                           | DO  | Indicate the module<br>network registration<br>status | V <sub>OH</sub> min=1.35V<br>V <sub>OL</sub> max=0.45V                           | 1.8V power domain; If<br>unused, keep it open                                                    |

| NET_STATUS | 6                                                           | DO  | Indicate the module<br>network activity status        | V <sub>OH</sub> min=1.35V<br>V <sub>OL</sub> max=0.45V                           | 1.8V power domain; If<br>unused, keep it open                                                    |

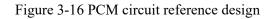

| USB_VBUS   | 71                                                          | PI  | USB detection                                         | Vmax=5.25V<br>Vmin=3.0V<br>Vnorm=5.0V                                            | -                                                                                                |

| USB_DP     | 69                                                          | Ю   | USB differential data positive signal                 | Compliant with<br>USB2.0 standard<br>specification                               | Require differential impedance of 90Ω                                                            |

| USB_DM            | 70 | Ю  | USB differential data<br>negative signal | Compliant with<br>USB2.0 standard<br>specification                                                                                                                                                             | Require differential impedance of 90Ω                                                                                     |

|-------------------|----|----|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| USIM_DATA         | 15 | Ю  | USIM card data signal                    | $\begin{array}{l} 1.8V  USIM: \\ V_{IL}max=0.6V \\ V_{IH}min=1.2V \\ V_{OL}max=0.45V \\ V_{OH}min=1.35V \\ 3.0V  USIM: \\ V_{IL}max=1.0V \\ V_{IH}min=1.95V \\ V_{OL}max=0.45V \\ V_{OH}min=2.55V \end{array}$ | -                                                                                                                         |

| USIM_CLK          | 16 | DO | USIM card clock signal                   | 1.8V USIM:<br>V <sub>OL</sub> max=0.45V<br>V <sub>OH</sub> min=1.35V<br>3.0V USIM:<br>V <sub>OL</sub> max=0.45V<br>V <sub>OH</sub> min=2.55V                                                                   | -                                                                                                                         |

| USIM_RST          | 17 | DO | USIM card reset signal                   | 1.8V USIM:<br>V <sub>OL</sub> max=0.45V<br>V <sub>OH</sub> min=1.35V<br>3.0V USIM:<br>V <sub>OL</sub> max=0.45V<br>V <sub>OH</sub> min=2.55V                                                                   | -                                                                                                                         |

| USIM_<br>PRESENCE | 13 | DI | USIM detection                           | V <sub>IL</sub> min=-0.3V<br>V <sub>IL</sub> max=0.6V<br>V <sub>IH</sub> min=1.2V<br>V <sub>IH</sub> max=2.0V                                                                                                  | 1.8V power domain, need<br>external pull up to 1.8V                                                                       |

| USIM_VDD          | 14 | РО | USIM card supply voltage                 | 1.8V USIM:<br>Vmax=1.9V<br>Vmin=1.7V<br>3.0V USIM:<br>Vmax=3.05V<br>Vmin=2.7V<br>I₀max=50mA                                                                                                                    | Automatic module<br>recognition 1.8V or 3.0V<br>USIM card                                                                 |

| USIM_GND          | 10 |    | USIM ground                              |                                                                                                                                                                                                                | Connect to the ground of the module                                                                                       |

| RI                | 62 | DO | Ring indicator                           | V <sub>OL</sub> max=0.45V<br>V <sub>OH</sub> min=1.35V                                                                                                                                                         | 1.8V power domain.do not<br>pull up to high level before<br>the module starts<br>successfully. If unused,<br>keep it open |

| DCD               | 63 | DI | Carrier detect                           | V <sub>OL</sub> max=0.45V<br>V <sub>OH</sub> min=1.35V                                                                                                                                                         | 1.8V power domain. If<br>unused, keep it open                                                                             |

|          |     |    | 1                                                           | 1                                                                                                        |                                                                                                                                                          |

|----------|-----|----|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTR      | 66  | DO | DTE ready, sleep mode control                               | $V_{IL}min=-0.3V$<br>$V_{IL}max=0.6V$<br>$V_{IH}min=1.2V$<br>$V_{IH}max=2.0V$                            | 1.8V power domain. If<br>unused, keep it open                                                                                                            |

| RXD      | 68  | DI | ReCompalve data                                             | $V_{IL}min=-0.3V$ $V_{IL}max=0.6V$ $V_{IH}min=1.2V$ $V_{IH}max=2.0V$                                     | 1.8V power domain. If<br>unused, keep it open                                                                                                            |

| TXD      | 67  | DO | Transmit data                                               | V <sub>OL</sub> max=0.45V<br>V <sub>OH</sub> min=1.35V                                                   | 1.8V power domain. If<br>unused, keep it open                                                                                                            |

| CTS      | 64  | DI | Clear to send                                               | $V_{OL}$ max=0.45V<br>$V_{OH}$ min=1.35V                                                                 | 1.8V power domain. If<br>unused, keep it open                                                                                                            |

| RTS      | 65  | DO | DTE requires to transmit data                               | $V_{IL}min=-0.3V$ $V_{IL}max=0.6V$ $V_{IH}min=1.2V$ $V_{IH}max=2.0V$                                     | 1.8V power domain. If<br>unused, keep it open                                                                                                            |

| DBG_TXD  | 12  | DO | The module sends data                                       | V <sub>OL</sub> max=0.45V<br>V <sub>OH</sub> min=1.35V                                                   | 1.8V power domain. If<br>unused, keep it open                                                                                                            |

| DBG_RXD  | 11  | DI | The module<br>reCompalves data                              | $V_{IL}min=-0.3V$ $V_{IL}max=0.6V$ $V_{IH}min=1.2V$ $V_{IH}max=2.0V$                                     | 1.8V power domain. If<br>unused, keep it open                                                                                                            |

| ADC0     | 45  | AI | Universal<br>analog-to-digital<br>conversion                | voltage range:<br>0.1V~1.7V                                                                              | If unused, keep it open                                                                                                                                  |

| ADC1     | 44  | AI | Universal<br>analog-to-digital<br>conversion                | voltage rang:<br>0.1V~1.7V                                                                               | If unused, keep it open                                                                                                                                  |

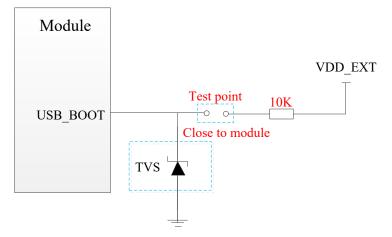

| USB_BOOT | 115 | DI | Mandatory download<br>mode control,<br>High level effective | $V_{IL}min=-0.3V$ $V_{IL}max=0.6V$ $V_{IH}min=1.2V$ $V_{IH}max=2.0V$                                     | 1.8V power domain. It is<br>recommended to reserve<br>test points.                                                                                       |

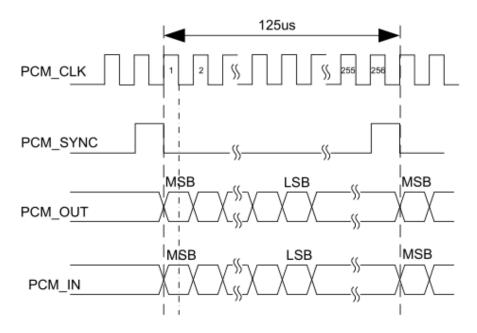

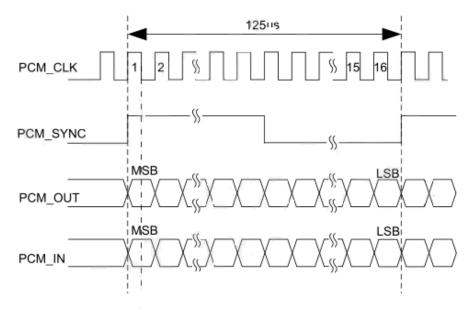

| PCM_IN   | 24  | DI | PCM data input                                              | $V_{IL}min=-0.3V$ $V_{IL}max=0.6V$ $V_{IH}min=1.2V$ $V_{IH}max=2.0V$                                     | 1.8V power domain.<br>If unused, keep it open.                                                                                                           |

| PCM_OUT  | 25  | DO | PCM data output                                             | V <sub>OL</sub> max=0.45V<br>V <sub>OH</sub> min=1.35V                                                   | 1.8V power domain.<br>If unused, keep it open.                                                                                                           |

| PCM_CLK  | 27  | Ю  | PCM clock                                                   | $V_{OL}max=0.45V$ $V_{OH}min=1.35V$ $V_{IL}min=-0.3V$ $V_{IL}max=0.6V$ $V_{IH}min=1.2V$ $V_{IH}max=2.0V$ | 1.8V power domain.Module as the main device,the pin is the output signal,module as the slave device,the pin is the input signal.If unused, keep it open. |

| PCM_SYNC         | 26  | Ю  | PCM data<br>synchronization<br>signal             | $V_{OL}max=0.45V$ $V_{OH}min=1.35V$ $V_{IL}min=-0.3V$ $V_{IL}max=0.6V$ $V_{IH}min=1.2V$ $V_{IH}max=2.0V$      | 1.8V power domain.<br>Module as the main device,<br>the pin is the output signal,<br>module as the slave device,<br>the pin is the input signal.<br>If unused, keep it open. |

|------------------|-----|----|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CDC_I2S_<br>MCLK | 116 | DO | 19.2MHz clock signal                              | -                                                                                                             | The module outputs a<br>19.2mhz clock signal to<br>provide a clock signal to<br>the external CODEC, If<br>unused, keep it open.                                              |

| I2C_SCL          | 41  | ю  | I2C clock                                         | -                                                                                                             | Require external pull-up<br>to 1.8V.If unused, keep it<br>open.                                                                                                              |

| I2C_SDA          | 42  | Ю  | I2C data                                          | -                                                                                                             | Require external pull-up<br>to 1.8V.If unused, keep it<br>open.                                                                                                              |

| ANT_DIV          | 35  | AI | Diversity antenna                                 | $50\Omega$ impedance                                                                                          |                                                                                                                                                                              |

| ANT_MAIN         | 49  | IO | Main antenna                                      | 50Ω impedance                                                                                                 |                                                                                                                                                                              |

| ANT_GNSS         | 47  | AI | GNSS antenna                                      | $50\Omega$ impedance                                                                                          |                                                                                                                                                                              |

| WAKEUP_IN        | 1   | DI | Sleep mode control                                | $V_{IL}min=-0.3V$<br>$V_{IL}max=0.6V$<br>$V_{IH}min=1.2V$<br>$V_{IH}max=2.0V$                                 | 1.8V power domain.<br>High level wakes up the<br>module; in low level the<br>module enters into sleep<br>mode. If unused, keep it<br>open.                                   |

| AP_READY         | 2   | DI | Application<br>processor sleep<br>state detection | V <sub>OL</sub> max=0.45V<br>V <sub>OH</sub> min=1.35V                                                        | 1.8V power domain.<br>Do not pull up to high level<br>before the module starts<br>successfully. If unused,<br>keep it open.                                                  |

| WAKEUP_<br>OUT_N | 3   | DO | Sleep mode output                                 | V <sub>OL</sub> max=0.45V<br>V <sub>OH</sub> min=1.35V                                                        | <ul><li>1.8V power domain.</li><li>If unused, keep it open.</li><li>The module output low</li><li>level after entering sleep.</li></ul>                                      |

| W_DISABLE_N      | 4   | DI | Airplane mode<br>control                          | V <sub>IL</sub> min=-0.3V<br>V <sub>IL</sub> max=0.6V<br>V <sub>IH</sub> min=1.2V<br>V <sub>IH</sub> max=2.0V | 1.8V power domain.<br>The low level puts the<br>module into flight mode, If<br>unused, keep it open.                                                                         |

| BT_RTS           | 37  | DO | DTE requires to transmit data                     | V <sub>IL</sub> min=-0.3V<br>V <sub>IL</sub> max=0.6V<br>V <sub>IH</sub> min=1.2V<br>V <sub>IH</sub> max=2.0V | 1.8V power domain. If<br>unused, keep it open                                                                                                                                |

| BT_TXD           | 38  | DO | Transmit data                                     | V <sub>OL</sub> max =0.45V                                                                                    | 1.8V power domain. If                                                                                                                                                        |

| L                | 1   | 1  | I                                                 | 1                                                                                                             | i                                                                                                                                                                            |

|                      |     |    |                                                                | V <sub>OH</sub> min =1.35V                                                                                                                                              | unused, keep it open                              |

|----------------------|-----|----|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| BT_RXD               | 39  | DI | ReCompalve data                                                | V <sub>IL</sub> min=-0.3V<br>V <sub>IL</sub> max=0.6V<br>V <sub>IH</sub> min=1.2V<br>V <sub>IH</sub> max=2.0V                                                           | 1.8V power domain. If<br>unused, keep it open     |

| BT_CTS               | 40  | DI | Clear to send                                                  | $V_{OL}$ max =0.45V<br>$V_{OH}$ min =1.35V                                                                                                                              | 1.8V power domain. If<br>unused, keep it open     |

| BT_EN                | 139 | DO | Bluetooth enable                                               | $V_{OL}max = 0.45V$<br>$V_{OH}min = 1.35V$                                                                                                                              | 1.8V power domain. If<br>unused, keep it open     |

| WLAN_SLP<br>_CLK     | 118 | DO | WLAN sleep clock                                               |                                                                                                                                                                         | If unused, keep it open                           |

| PM_ENABLE            | 127 | DO | WLAN external power<br>enable control, high<br>level effective | V <sub>OL</sub> max =0.45V<br>V <sub>OH</sub> min =1.35V                                                                                                                | 1.8V power domain. If<br>unused, keep it open     |

| SDC1_DATA3           | 129 | Ю  | WLAN SDIO Bus data<br>line 3                                   | V <sub>OL</sub> max=0.45<br>V <sub>OH</sub> min=1.35V<br>V <sub>IL</sub> min=-0.3V<br>V <sub>IL</sub> max=0.6V<br>V <sub>IH</sub> min=1.2V V <sub>IH</sub> max<br>=2.0V | 1.8V power domain. If<br>unused, keep it open     |

| SDC1_DATA2           | 130 | Ю  | WLAN SDIO Bus data<br>line 2                                   | V <sub>OL</sub> max=0.45<br>V <sub>OH</sub> min=1.35V<br>V <sub>IL</sub> min=-0.3V<br>V <sub>IL</sub> max=0.6V<br>V <sub>IH</sub> min=1.2V V <sub>IH</sub> max<br>=2.0V | 1.8V power domain. If<br>unused, keep it open     |

| SDC1_DATA1           | 131 | Ю  | WLAN SDIO Bus data<br>line 1                                   | $V_{OL}max=0.45$ $V_{OH}min=1.35V$ $V_{IL}min=-0.3V$ $V_{IL}max=0.6V$ $V_{IH}min=1.2V V_{IH}max$ $=2.0V$                                                                | 1.8V power domain. If<br>unused, keep it open     |

| SDC1_DATA0           | 132 | Ю  | WLAN SDIO Bus data<br>line 0                                   | V <sub>OL</sub> max=0.45<br>V <sub>OH</sub> min=1.35V<br>V <sub>IL</sub> min=-0.3V<br>V <sub>IL</sub> max=0.6V<br>V <sub>IH</sub> min=1.2V V <sub>IH</sub> max<br>=2.0V | 1.8V power domain. If<br>unused, keep it open     |

| SDC1_CLK             | 133 | DI | WLAN SDIO clock                                                | V <sub>OL</sub> max=0.45<br>V <sub>OH</sub> min=1.35V                                                                                                                   | 1.8V power domain. If<br>unused, keep it open     |

| SDC1_CMD             | 134 | ΙΟ | WLAN SDIO command                                              | V <sub>OL</sub> max=0.45<br>V <sub>OH</sub> min=1.35V                                                                                                                   | 1.8V power domain. If<br>unused, keep it open     |

| WAKE_ON_<br>WIRELESS | 135 | DI | WLAN wake up the module                                        | V <sub>IL</sub> min=-0.3V<br>V <sub>IL</sub> max=0.6V                                                                                                                   | 1.8V power domain. If<br>unused, keep it open. Do |

|                  |     |    |                                                 | V <sub>IH</sub> min=1.2V V <sub>IH</sub> max<br>=2.0V                                                                                                                                                    | not pull up to high level<br>before the module starts<br>successfully                                                        |

|------------------|-----|----|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| WLAN_EN          | 136 | DO | WLAN enabled, high<br>level effective           | V <sub>OL</sub> max=0.45<br>V <sub>OH</sub> min=1.35V                                                                                                                                                    | 1.8V power domain, high<br>level effective, Do not pull<br>up to high level before the<br>module starts successfully         |

| COEX_<br>UART_TX | 138 | DO | GPIO                                            | V <sub>OL</sub> max=0.45<br>V <sub>OH</sub> min=1.35V                                                                                                                                                    | 1.8V power domain. If<br>unused, keep it open. Do<br>not pull up to high level<br>before the module starts<br>successfully   |

| EPHY_RST_N       | 119 | DO | Ethernet PHY reset                              | For 1.8V:<br>V <sub>OL</sub> max=0.45V<br>V <sub>OH</sub> min=1.35V<br>For 2.85V:<br>V <sub>OL</sub> max=0.35V<br>V <sub>OH</sub> min=2.14V                                                              | 1.8V /2.85Vpower domain.<br>If unused, keep it open.                                                                         |

| EPHY_INT_N       | 120 | DI | Ethernet PHY<br>interruption                    | V <sub>IL</sub> min=-0.3V<br>V <sub>IL</sub> max=0.6V<br>V <sub>IH</sub> min=1.2V<br>V <sub>IH</sub> max=2.0V                                                                                            | 1.8V /2.85Vpower domain.<br>If unused, keep it open.                                                                         |

| SGMII_MDATA      | 121 | Ю  | SGMII MDIO data                                 | For 1.8V:<br>$V_{OL}max=0.45V$<br>$V_{OH}min=1.4V$<br>$V_{IL}max = 0.58V$<br>$V_{IH}min = 1.27V$<br>For 2.85V:<br>$V_{OL}max=0.35V$<br>$V_{OH}min = 2.14V$<br>$V_{IL}max = 0.71V$<br>$V_{IH}min = 1.78V$ | 1.8V /2.85Vpower domain.<br>If unused, keep it open.<br>External pull up to<br>USIM2_VDD, pull up<br>resistance is 1.5K;     |

| SGMII_MCLK       | 122 | DO | SGMII MDIO clock                                | For 1.8V:<br>V <sub>OL</sub> max=0.45V<br>V <sub>OH</sub> min=1.4V<br>For 2.85V:<br>V <sub>OL</sub> max=0.35V<br>V <sub>OH</sub> min=2.14V                                                               | 1.8V /2.85Vpower domain.<br>If unused, keep it open.                                                                         |

| USIM2_VDD        | 128 | РО | SGMII MDIO pull-up<br>power supply              | -                                                                                                                                                                                                        | Output 1.8V/2.85V<br>configurable; Can be used<br>for pull-up, not directly for<br>power supply. If unused,<br>keep it open. |

| SGMII_TX_M       | 123 | AO | SGMII differential data sends a negative signal | -                                                                                                                                                                                                        | If unused, keep it open.                                                                                                     |

| SGMII_TX_P | 124 | AO | SGMII differential data sends a positive signal            | -                                                                                                                                                                                                                                                                                           | If unused, keep it open.                                                                                                                                                    |

|------------|-----|----|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SGMII_RX_P | 125 | AI | SGMII differential data<br>reCompalve positive<br>signals  | -                                                                                                                                                                                                                                                                                           | If unused, keep it open.                                                                                                                                                    |

| SGMII_RX_M | 126 | AI | SGMII differential data<br>reCompalves negative<br>signals | -                                                                                                                                                                                                                                                                                           | If unused, keep it open.                                                                                                                                                    |

| SD_INS_DET | 23  | DI | SD card insertion detection                                | V <sub>IL</sub> min=-0.3V<br>V <sub>IL</sub> max=0.6V<br>V <sub>IH</sub> min=1.2V V <sub>IH</sub> max<br>=2.0V                                                                                                                                                                              | 1.8V power domain. If<br>unused, keep it open.                                                                                                                              |

| SD_CMD     | 33  | Ю  | SD card SDIO<br>instruction signal                         | 1.8V SD card:<br>$V_{OL}max=0.45$<br>$V_{OH}min=1.4V$<br>$V_{IL}min=-0.3V$<br>$V_{IL}max=0.58V$<br>$V_{IH}min=1.27V$<br>$V_{IH}max = 2.0V$<br>3.0V SD card:<br>$V_{OL}max=0.38V$<br>$V_{OH}min=2.01V$<br>$V_{IL}min=-0.3V$<br>$V_{IL}max=0.76V$<br>$V_{IH}max=3.34V$                        | SDIO signal level can be<br>selected according to the<br>signal level supported by<br>SD card. For details, please<br>refer to SD 3.0 protocol. If<br>unused, keep it open. |

| SD_CLK     | 32  | DO | SD card SDIO clock<br>signal                               | 1.8V SD card:<br>$V_{OL}max=0.45V$<br>$V_{OH}min = 1.4V$<br>3.0V SD card:<br>$V_{OL}max=0.38V$<br>$V_{OH}min=2.01V$                                                                                                                                                                         | SDIO signal level can be<br>selected according to the<br>signal level supported by<br>SD card. For details, please<br>refer to SD 3.0 protocol. If<br>unused, keep it open. |

| SD_DATA3   | 28  | Ю  | SD card SDIO Bus<br>DATA3                                  | $\begin{array}{c} 1.8V \mbox{ SD card:} \\ V_{OL}max=0.45 \\ V_{OH}min=1.4V \\ V_{IL}min=-0.3V \\ V_{IL}max=0.58V \\ V_{IH}min=1.27V \\ V_{IH}max=2.0V \\ 3.0V \mbox{ SD card:} \\ V_{OL}max=0.38V \\ V_{OH}min=2.01V \\ V_{IL}min=-0.3V \\ V_{IL}max=0.76V \\ V_{IH}min=1.72V \end{array}$ | SDIO signal level can be<br>selected according to the<br>signal level supported by<br>SD card. For details, please<br>refer to SD 3.0 protocol. If<br>unused, keep it open. |

|          |             |       |                              | V = max - 2.24V                            |                                        |

|----------|-------------|-------|------------------------------|--------------------------------------------|----------------------------------------|

|          |             |       |                              | V <sub>IH</sub> max=3.34V<br>1.8V SD card: |                                        |

|          |             |       |                              |                                            |                                        |

|          |             |       |                              | $V_{OL}$ max=0.45                          |                                        |

| SD_DATA2 |             |       |                              | $V_{OH}$ min=1.4V                          |                                        |

|          |             |       |                              | $V_{IL}$ min=-0.3V                         |                                        |

|          |             |       |                              | V <sub>IL</sub> max=0.58V                  | SDIO signal level can be               |

|          |             |       |                              | V <sub>IH</sub> min=1.27V                  | selected according to the              |

|          | 29          | IO    | SD card SDIO Bus             | $V_{IH}$ max =2.0V                         | signal level supported by              |

|          |             |       | DATA2                        | 3.0V SD card:                              | SD card. For details, please           |

|          |             |       |                              | V <sub>OL</sub> max=0.38V                  | refer to SD 3.0 protocol. If           |

|          |             |       |                              | V <sub>OH</sub> min=2.01V                  | unused, keep it open.                  |

|          |             |       |                              | V <sub>IL</sub> min=-0.3V                  |                                        |

|          |             |       |                              | V <sub>IL</sub> max=0.76V                  |                                        |

|          |             |       |                              | V <sub>IH</sub> min=1.72V                  |                                        |

|          |             |       |                              | V <sub>IH</sub> max=3.34V                  |                                        |

|          |             |       |                              | 1.8V SD card:                              |                                        |

|          |             |       |                              | V <sub>OL</sub> max=0.45                   |                                        |

|          |             |       |                              | V <sub>OH</sub> min=1.4V                   |                                        |

|          | 30 IC       | 30 IO | IO SD card SDIO Bus<br>DATA1 | V <sub>IL</sub> min=-0.3V                  |                                        |

|          |             |       |                              | V <sub>IL</sub> max=0.58V                  | SDIO signal level can be               |

|          |             |       |                              | V <sub>IH</sub> min=1.27V                  | selected according to the              |

|          |             |       |                              | $V_{IH}$ max = 2.0V                        | signal level supported by              |

| SD_DATA1 |             |       |                              | 3.0V SD card:                              | SD card. For details, please           |

|          |             |       |                              | V <sub>OL</sub> max=0.38V                  | refer to SD 3.0 protocol. If           |

|          |             |       |                              | V <sub>OH</sub> min=2.01V                  | unused, keep it open.                  |

|          |             |       |                              | V <sub>IL</sub> min=-0.3V                  | ······································ |

|          |             |       |                              | $V_{IL}$ max=0.76V                         |                                        |

|          |             |       |                              | V <sub>III</sub> min=1.72V                 |                                        |

|          |             |       |                              | $V_{IH}$ max=3.34V                         |                                        |

|          |             |       |                              | 1.8V SD card:                              |                                        |

|          |             |       |                              | $V_{OL}$ max=0.45                          |                                        |

|          |             |       |                              |                                            |                                        |

|          |             |       |                              | $V_{OH}$ min=1.4V                          |                                        |

|          |             |       |                              | $V_{IL}$ min=-0.3V                         |                                        |

|          |             |       |                              | $V_{IL}$ max=0.58V                         | SDIO signal level can be               |

|          |             |       |                              | $V_{IH}$ min=1.27V                         | selected according to the              |

| SD_DATA0 | 31          | IO    | SSD card SDIO Bus            | $V_{\rm IH}$ max =2.0V                     | signal level supported by              |

| _        |             |       | DATA0                        | 3.0V SD card:                              | SD card. For details, please           |

|          |             |       |                              | V <sub>OL</sub> max=0.38V                  | refer to SD 3.0 protocol. If           |

|          |             |       |                              | V <sub>OH</sub> min=2.01V                  | unused, keep it open.                  |

|          |             |       |                              | V <sub>IL</sub> min=-0.3V                  |                                        |

|          |             |       |                              | V <sub>IL</sub> max=0.76V                  |                                        |

|          |             |       |                              | V <sub>IH</sub> min=1.72V                  |                                        |

|          |             |       |                              | V <sub>IH</sub> max=3.34V                  |                                        |

| DEGEDYED | 18, 34, 43, |       |                              |                                            | 17 1                                   |

| RESERVED | 55, 73~84,  |       |                              |                                            | Keep it open.                          |

|          | 55, 75~84,  |       |                              |                                            |                                        |

| 113, 114, |  |  |

|-----------|--|--|

| 117, 137, |  |  |

| 140~144   |  |  |

# NOTE:

The unused pins can be left floating.

- P indicates power pins; I indicate pins for digital signal input; O indicates pins for digital signal output; PO indicates power output pins; PI indicates power input pins.

- VIL indicates Low-level Input voltage; VIH indicates High-level Input voltage; VOL indicates Low-level Output voltage; VOH indicates High-level Output voltage.

- The **Reserved** pins are internally connected to the module. Therefore, these pins should not be used, otherwise they may cause problems. Please contact with us for more details about this information.

# **3.3** Power Interface

EXC-N1 has four VBAT pins for connecting an external power supply, which can be divided into two power supply domains:

- Two VBAT\_RF pins are used to power the module's RF;

- Two VBAT\_BB pins are used to power the baseband of the module.

The following table shows the distribution of power pins and ground pins for the module:

| Table 3-3 | VBAT pin and ground pin |

|-----------|-------------------------|

|-----------|-------------------------|

| Pin           | Pin Name    | Din Description                  | DC Pa | ramete | <b>r</b> ( <b>V</b> ) |

|---------------|-------------|----------------------------------|-------|--------|-----------------------|

| r III         | r in Ivanie | Pin Description                  | Min   | Тур    | Max                   |

| 57, 58        | VBAT_RF     | Power supply for module baseband | 3.3   | 3.8    | 4.2                   |

| 59, 60        | VBAT_BB     | Power supply for module RF       | 3.3   | 3.8    | 4.2                   |

| 8, 9, 10, 19, |             |                                  |       |        |                       |

| 22, 36, 46,   |             |                                  |       |        |                       |

| 48, 50~54,    | GND         | Ground                           | -     | 0      | -                     |

| 56, 72,       |             |                                  |       |        |                       |

| 85~112        |             |                                  |       |        |                       |

4G LCC Module can use any power source which is followed "Table 3-3 power supply input" as an Input power. Then, it has 2 output powers for each function such as, USIM, and SGMII. Due to the limited power trace, all of them should use efficiently when design the layout.

When the 4G LCC module is used for different external applications, pay special attention to the design for the power supply. When the 4G LCC module works at 4G mode and transmits signals at the maximum power, the transient current may reach the transient peak value of about 4A due to the differences in actual network environments. In this case, the VBAT voltage drops. If you want wireless good performance, please make sure that the voltage does not decrease below 3.4 V in any case. Otherwise, exceptions such as restart of the 4G LCC module may occur.

It is recommended that customers add the EMI ferrite bead (FBMJ1608HS280NT manufactured by TAIYO YUDEN or MPZ1608S300ATAH0 manufactured by TDK is recommended) to directly isolate DTE from DCE in the power circuit.

# 3.3.1 Power Supply

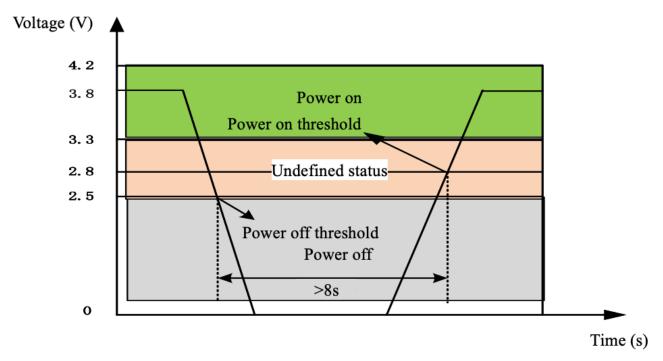

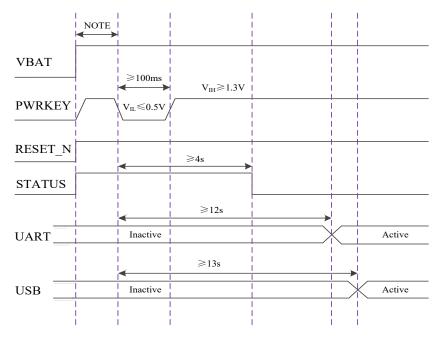

The power supply range of EXC-N1 is from 3.3V to 4.2V. During data transmission or conversation, instantaneous high-power emission will form a peak current up to 2A, which will lead to a large ripple of VBAT. If instantaneous voltage drop leads to too low VBAT power supply voltage, the module will shut down. Make sure there are sufficient power supply capabilities and the input voltage will never drop below 3.3V to make the module work well. The following figure is the module switch threshold state definition

Figure 3-2 Switching machine threshold

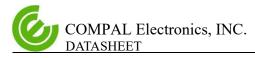

The following figure shows the voltage drop during transmitting burst in 2G network. The voltage drop will be less in 3G and 4G networks.

Figure 3-3 Power requirements for burst transmission

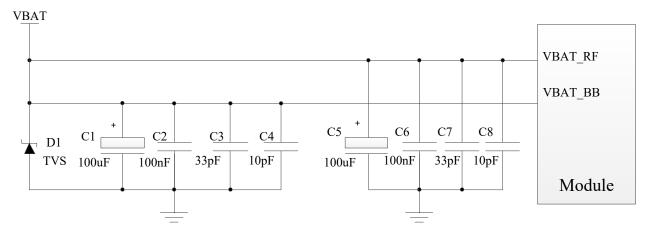

To reduce voltage sags, a 100uF filter capacitor with a low ESR is required. MLCC has the best ESR. It is recommended to add 3 ceramic capacitors (100nF, 33pF, 10pF) to VBAT\_BB and VBAT\_RF pins, and the capacitors should be placed close to the VBAT pins. At the same time, in order to ensure better power supply performance, a TVS tube is added near the input end of the module VBAT to improve the surge voltage bearing capacity of the module. It is recommended to use Changyuan Vian, model WS4.5DPV. When the external power supply is connected to the module, VBAT\_BB and VBAT\_RF need to adopt star routing. VBAT\_BB wire width shall not be less than 1mm, and VBAT\_RF wire width shall not be less than 2mm. In principle, the longer the line in VBAT, the wider the line.

The reference circuit is as follows:

Figure 3-4 Reference Circuit for Power Supply

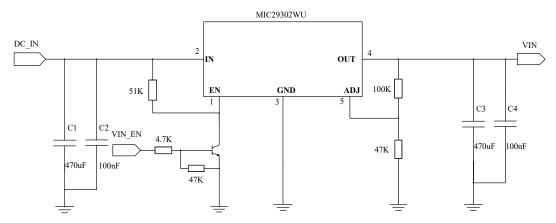

The design of the module power supply is very important because the performance of the module depends largely on the power supply. The power supply can provide at least 2A current. If the voltage difference between input and output is not very large, it is recommended to use LDO power supply module; If the voltage difference between input and output is large, DCDC is preferred as the power source.

The figure below is the reference design of +5V power supply circuit. The design use Micrel LDO, model MIC29302WU. Its typical output voltage is 3.8V and the peak load current reaches 3A.

Figure 3-5 Reference design for power supply input

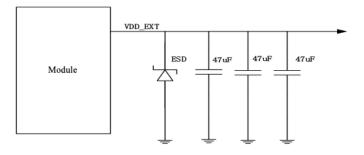

If EXC-N1 module turns on normally, there is a voltage output of 1.8V, current load 80mA in PIN7. You can use the output voltage as an external power supply, for example level reference, and judge if the module is turned on by reading pin level status.

Figure 3-6 VDD\_EXT external capacitor and ESD schematic diagram

The following table shows the recommended ESD models for VDD\_EXT output:

| Table 3-4 VDD | EXT output recom | mends adding ESD models |

|---------------|------------------|-------------------------|

|               |                  | menus adams Lob models  |

| Manufacturers | Model        | Power consumption | Package |

|---------------|--------------|-------------------|---------|

| On semi       | ESD5Z3.3T1G  | 200mW             | SOD523  |

| Prisemi       | PESDNC5D3V3U | 150mW             | SOD523  |