Date: 21 February,2005

Rev: 1.0a

# **Description of Cell Docking System**

### **Introduction**

With the intensively use of Cell phone, the system cost for leasing a fixed line is even lower than those of traditional land line. With this advantage issue, a residential phone and Cell phone integrated product will be outcomed which can provide the advanced features of likes Multi-handset feature. The multi-handset part will use our mature system of DSPG platform. We are now using the 2.4GHz Frequency Hopping System on the multi-handset systems.

#### **System Block Diagram Description**

#### **Cell-Docking Station**

#### (1) Multi-handset Baseband Part

We use the chip DSPG DLH36107 which always used in the 2.4GHz and 5.8GHz multi-handset digital platform. The Cell Docking cradle part will be treated as a separated handset system which is always synchronizing to the base of the multi-handset. With multi-time slots system, a base system can register up to four handsets include the cell docking part. The baseband controller DLH36107 is responsible for burst-mode controller of the system (i.e the system timing for the multi-handsets system such as TDD time control. It also includes the features for the audio part switching and codec functions.

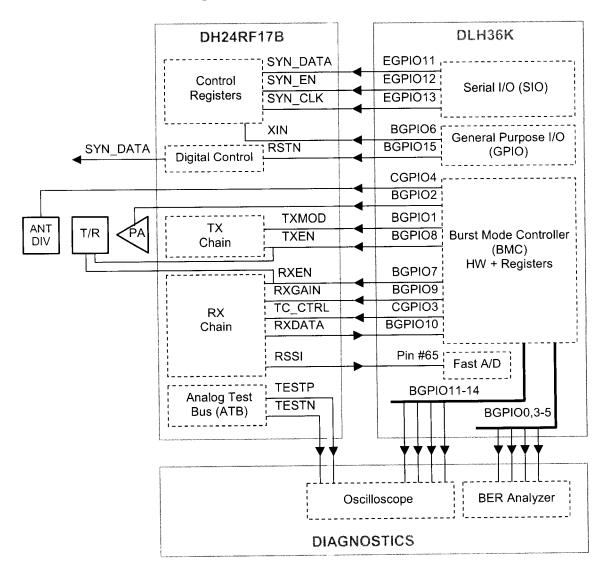

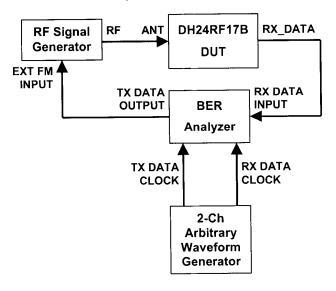

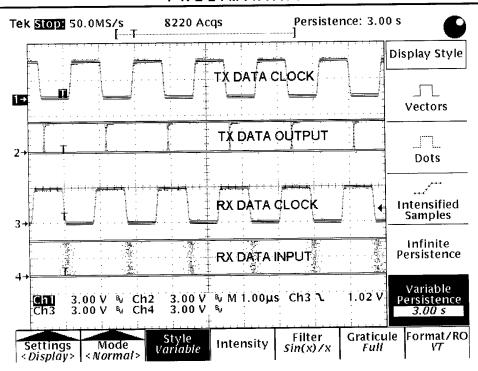

#### (2) RF Transceiver part

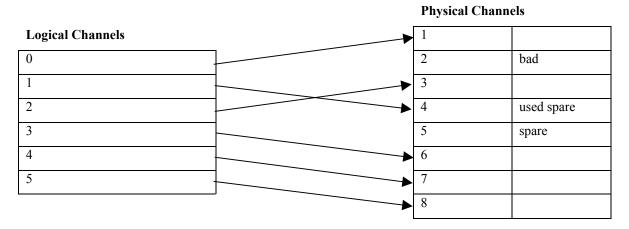

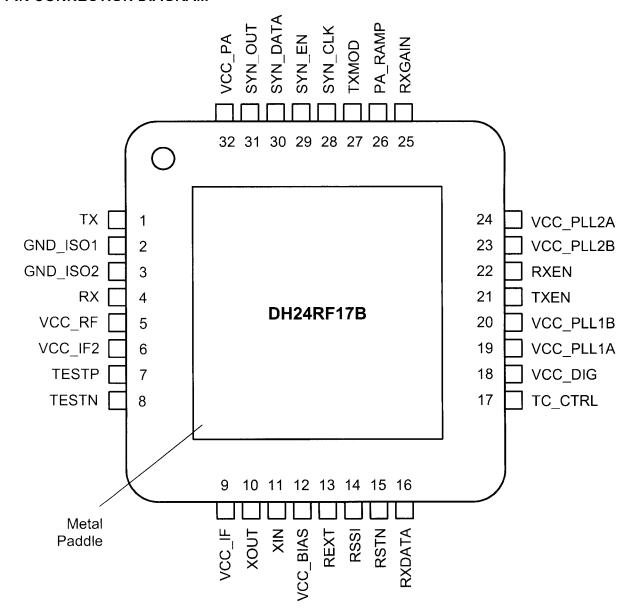

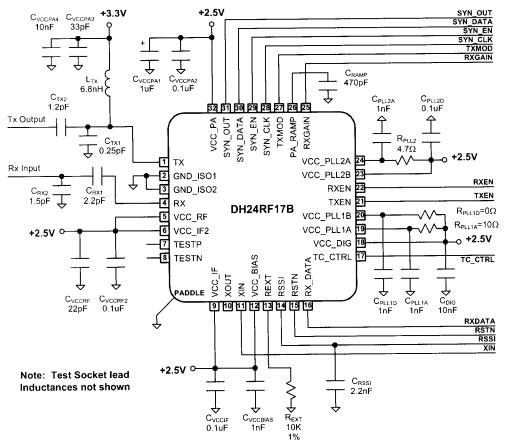

RF signal is picked up by a solid wire antenna, then goes to DH24RF17B transceiver IC which includes LNA, Mixer, Synthesizer, RF power amplifier and TDD switches for 2.4GHz RF part.

The baseband controller DLH36107 is responsible for burst-mode controller of the system (i.e the system timing for the multi-handsets system such as TDD time control. It also includes the features for the audio part switching and codec functions.

The hopping sequence algorithm is same for caller ID and Voice Transmission. Voice and Data can be in same slot. No specific test mode is needed because in frame structure, only data is handled in different field in one frame

#### (3) Cell phone Interface

We have used a MCU TMP92CH21 to act as the interface chip for the cell phone. With this chip, we can preform the software upgradable by using the on-chip USB function. With this software upgradable feature, we can easily upgrade the firmware whenever there have new cellphones introducing to market after the cell docking systems purchased or manufactured. The software upgrade features is used to upgrade the support feature (new phones and/or new features). It won't affect the data rates of the USB.

The cell phone interface based on the concept of the UART and FBUS. Most of the cell phones have integrated with either UART or FBUS configurations. And all these configurations are software re-configurable, the determination of the UART or FBUS will be selected with the cell phone manual selected on the panel of the cell docking and indicated on the LCD.

#### (4) TMP92CH21 to DLH36107 interface

We planned to have a quite a lot of data transfer (CID data, phone book, etc) between the TMP92CH21 and the DLH36107, a software-simulated SPI interface will be used which has comparatively high data rate handling.

#### (5) UART interface for ATE setup

ATE means the Automatic Testing setup which is used for the production setup likes parameters tuning, system parameters updating, ID codes, etc. The cell docking system will interface with Personal Computer (tester) by software UART port.

#### (6) Programming Charger

The charger comprises of a DC-DC convertor. With different cellphones, the input voltage is different. The corresponded information will be stored in Flash ROM inside the Cell Docking System. The voltage output of the DC-DC convertor can be controlled by setting the feedback resistors. The selection is controlled by TMP92CH21 controller.

#### **Handset Unit**

RF signal is picked up by a solid wire antenna, then goes to DH24RF17B transceiver IC which includes LNA, Mixer, Synthesizer, RF power amplifier and TDD switches for 2.4GHz RF part.

The baseband controller DLH36107 is responsible for burst-mode controller of the system (i.e the system timing for the multi-handsets system such as TDD time control. It also includes the features for the audio part switching and codec functions.

Page: 2 of 3

#### **Base Unit**

#### (1) RF Transceiver part

RF signal is picked up by a solid wire antenna, then goes to DH24RF17B transceiver IC which includes LNA, Mixer, Synthesizer, RF power amplifier and TDD switches for 2.4GHz RF part.

The baseband controller DLH36119 is responsible for burst-mode controller of the system (i.e the system timing for the multi-handsets system such as TDD time control. It also includes the features for the audio part switching and codec functions.

#### (2) Antenna Diversity

Antenna diversity is implemented by CR2, CR3 (BAR64-02V) to select alternately the two antennas ANT A, ANT B respectively for TX/RX.

#### (3) Telephone Line interface

The telephone line interface circuit is established by below sections

#### Line seize and isolation

Line isolation is mainly preformed by Q10, Q13 and Q12. Q12 also has a function of controlling Line-seize. Both audio input and output will though Q10 and Q13.

#### Ring detect and CID circuit

The ring and CID signal will input though R113, R114 470K ohm and C43, C44 1nF/500V as DC isolation from telephone line.

Page: 3 of 3

# **EDCT**

# **FCC Submission For 2.4GHz FHSS System**

D30006 Rev 0.2

# **Generation Summary**

| Property  | Value                                             |

|-----------|---------------------------------------------------|

| File Name | D30006 FCC Submission For FHSS System rev 0.2.doc |

| File Type | Microsoft Word 2000                               |

| Author    | Steven Dickinson                                  |

| Revision | Issue Date       | Description                                          |

|----------|------------------|------------------------------------------------------|

| 0.1      | 13 March 2003    | Preliminary                                          |

| 0.2      | 9 Novemeber 2004 | Removed statement about channel 71 (no longer valid) |

| 0.2a     | 23 February 2005 | Channel 71 is valid again                            |

# **Table of Contents**

| D | EFI  | NITIONS, ACRONYMS AND ABBREVIATIONS                              | 5  |

|---|------|------------------------------------------------------------------|----|

| 1 | I    | NTRODUCTION                                                      | 6  |

|   | 1.1  | SCOPE                                                            | 6  |

| 2 | В    | BRIEF SYSTEM DESCRIPTION                                         | 7  |

|   | 2.1  | FREQUENCY CHANNELS                                               | 7  |

|   | 2.2  | TDMA FRAMES STRUCTURE                                            | 8  |

|   | 2.3  | RESIDENTIAL / DOMESTIC SYSTEM                                    | 8  |

|   | 2.4  | BEARERS                                                          | 9  |

| 3 | C    | OVERVIEW OF FREQUENCY HOPPING ALGORITHM                          | 11 |

|   |      | HOPPING RATE                                                     |    |

|   | 3.2  | HOPPING SEQUENCE                                                 | 11 |

|   | 3.   | .2.1 HOPPING PATTERN BASE-TABLE                                  | 11 |

|   | 3.   | .2.2 LCG random number generator                                 | 12 |

|   | 3.   | .2.3 LOGICAL AND PHYSICAL CHANNEL NUMBERS                        | 13 |

|   | 3.3  | IDENTIFYING CHANNEL INTERFERENCE                                 | 14 |

|   | 3.4  | HOP SEQUENCE ADAPTION                                            | 14 |

|   | 3.5  | STARTING A DUMMY BEARER                                          | 14 |

|   | 3.   | .5.1 AVOIDING DUMMY BEARER 'SEQUENCE COLLISION'                  | 15 |

|   | 3.6  | GAINING SYNC WITH A DUMMY BEARER                                 | 15 |

|   | 3    | .6.1 Determining the pattern and HSI from an $N_T$ message       | 15 |

|   | 3.7  | FOLLOWING A DUMMY BEARER                                         | 15 |

|   | 3.8  | STARTING A TRAFFIC BEARER                                        | 16 |

|   | 3.   | .8.1 AVOIDING TRAFFIC BEARER 'SEQUENCE COLLISION'                | 16 |

|   | 3.9  | STARTING A COMBINED DUMMY/TRAFFIC BEARER                         | 16 |

|   | 3.   | .9.1 AVOIDING COMBINED DUMMY/TRAFFIC BEARER 'SEQUENCE COLLISION' | 17 |

|   | 3.10 | O SEAMLESS BEARER HAND-OVER & "MULTI-SLOT MODE"                  | 17 |

|   | 3.11 | 1 Handset-to-handset mode                                        | 17 |

|   | 3.12 | 2 SCANNING FOR NOISE                                             | 17 |

| 4 | C    | CONFORMANCE TO FCC REQUIREMENTS                                  | 18 |

|   |      | SECTION 15.247(A)(1)                                             |    |

|   |      |                                                                  |    |

| 4.3  | SECTION 15.247(G)                          | . 18 |

|------|--------------------------------------------|------|

|      | SECTION 15.247(H)                          |      |

| APPE | NDIX A – CHANNEL CENTRE FREQUENCIES        | . 20 |

| APPE | NDIX B – BASE-TABLE HOPPING SEQUENCE       | . 21 |

| APPE | NDIX C – LCG RANDOM HOPPING SEQUENCE       | . 22 |

| APPE | NDIX D – LOGICAL TO PHYSICAL MAPPING TABLE | . 31 |

# **DEFINITIONS, ACRONYMS AND ABBREVIATIONS**

The simultaneous occupancy of a hopping channel by multiple transmitters. Channel

collision

Preliminary

**DECT** Digital Enhanced Cordless Telecommunications.

**EIRP** Equivalent isotropically Radiated Power.

**ETSI** European Telecommunications Standards Institute.

**FCC** Federal Communications commission (the body in the USA that regulates the use of the

radio spectrum).

FΗ Frequency Hopper: the name of the software component responsible for frequency

hopping.

**FHSS** Frequency Hopping Spread Spectrum.

FP Fixed Part or base-station.

Hand-over A process by which a second traffic bearer is established to carry an existing call. Once

established the first traffic bearer can be released.

**HSI** Hope Sequence Index: used to index into the pattern table.

**ISM** Industrial, Scientific, Medical band: a radio frequency band in the range 2400 – 2483.5

MHz

LCG Linear Congruential Generator: a type of random number generator

LDC Low Duty Cycle: a power saving feature.

**OET** Office of Engineering and Technology, a division of the FCC.

PP Portable Part or handset.

**PSCN** Primary Scan Carrier Number; used in DECT.

**PSPN** Primary Scan Pattern Number; the analogue of the PSCN for frequency hopping.

Radio Cell The area covered by a single FP.

**RFPI** Radio Fixed Part Identity

**RNG** Random Number Generator; more accurately a Pseudo-Random Number Generator or

PRNG.

**RSSI** Received Signal Strength Indication.

Sequence When two transmitters, with overlapping radio cells, are using the same slot, pattern and collision

phase within the pattern. Channel collisions will occur on every frame, until the slot,

pattern or phase is changed.

**TDD** Time Division Duplexing.

**TDMA** Time Division Multiple Access.

## 1 INTRODUCTION

In the US the 2400 - 2483.5 MHz band (henceforth the 2.4 GHz band) is subject to FCC regulations, in particular Part 15 Section 247.

DSP Group has developed a base-band chip, RF solution and protocol stack for the cordless telephony market that uses the 2.4 GHz band. This system is known as EDCT. The EDCT protocol stack is based on a DECT standard protocol stack that has been modified to use frequency hopping spread spectrum (FHSS) techniques in order to meet the FCC requirements.

## 1.1 Scope

This document describes the salient features of the EDCT protocol stack as they relate to the FCC requirements for using the 2.4 GHz band.

### 2 BRIEF SYSTEM DESCRIPTION

The basic system is a cordless telephone system, based on DECT. Because DECT is such a fundamental part of the proposed system, a brief description of this is given first.

DECT is a low-power two-way digital wireless communications system. Whilst DECT is a general digital communications system, it is most commonly used for cordless telephone systems. In particular it is used for residential telephone systems.

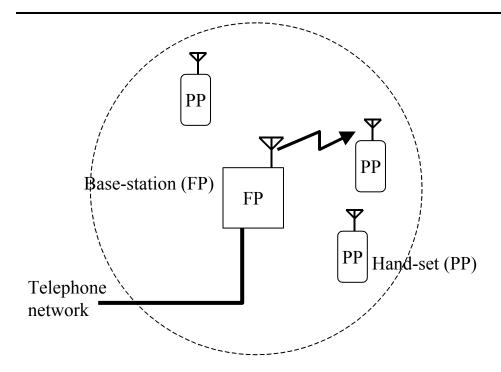

DECT uses TDMA to provide two-way communication between a base-station and multiple hand-sets. In this document the base-station is referred to as the Fixed Part (FP) and the hand-set is referred to as the Portable Part (PP).

Unlike a DECT system, the EDCT system does not have exclusive use of the spectrum. It has to share the spectrum with other users. The EDCT system uses frequency hopping to share the spectrum with other users according to the requirements specified by the FCC.

It is the frequency hopping requirement that creates the biggest difference between a DECT and an EDCT system. The other main difference between the two systems is the TDMA frame structure (EDCT has to use fewer 'slots' in the frame due to a lower bit rate).

## 2.1 Frequency channels

EDCT uses carriers whose centre frequencies are shown in "Appendix A – Channel Centre Frequencies".

This gives <u>87 possible hopping channels</u>, lying between 2401.808203 MHz and 2478.509033 MHz. For the purposes of this document, the channels are numbered 1 ... 87.

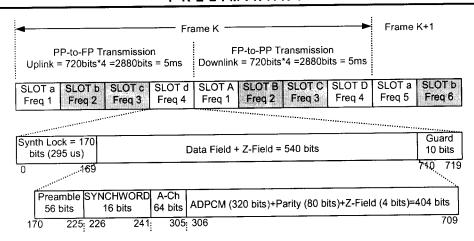

#### 2.2 TDMA frames structure

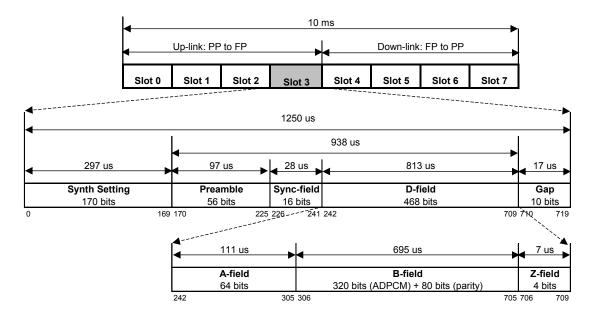

The EDCT TDMA frame structure is shown below:

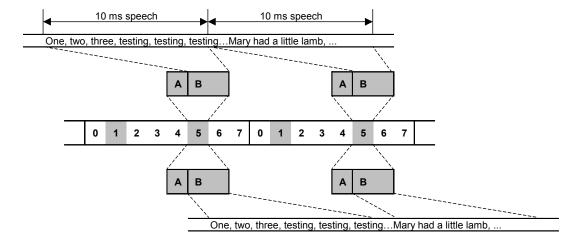

The basic, repeating, frame structure is 10 ms long. It is sub-divided into 8 slots, each 1250  $\mu$ s long. The active transmission time is 937.5  $\mu$ s. The first 4 slots form the 'up-link', when the PPs transmit to the FP. The last 4 slots form the 'down-link', when the FP transmits to the PPs.

EDCT uses TDD to carry a two-way voice communication. This is always by using slot-pairs: 0 and 4, 1 and 5, 2 and 6, 3 and 7. In this way the down-link transmission of the duplex communication is always 5ms after the corresponding up-link transmission.

There is only one transceiver in FP or PP therefore in any single slot, the FP or PP can only ever be receiving or transmitting.

# 2.3 Residential / domestic system

A residential or domestic system is for use in the home. A single FP is used with multiple PPs. There can be any number of PPs, although only 4 simultaneous duplex connections to the FP are allowed; this limit is due to the number of slot-pairs in the TDMA frame structure. The figure illustrates the basic system configuration.

### 2.4 Bearers

An important concept in DECT and EDCT is the notion of a "bearer". A bearer is the medium used for carrying a communication.

In a DECT system a bearer is defined by a combination of channel number and slot number. However, because EDCT is a frequency hopping system, a bearer is defined by a hopping sequence and slot number.

There are two types of bearer in the EDCT system:

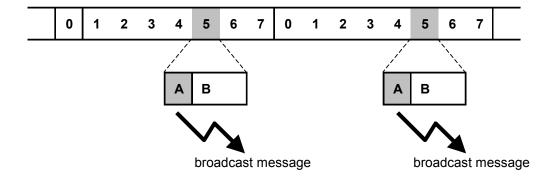

#### **Dummy bearer**

- This is used to carry a 'beacon' and other broadcast information.

- The FP will broadcast a dummy bearer all the time it is powered up and operating.

- Only the FP transmits a dummy bearer.

- As it is a simplex transmission, only a down-link slot is used.

- The broadcast information is contained in the 'A-field' section of the transmission (the 'B-field' section is not required, and is therefore not transmitted).

#### Traffic bearer

- This is used to carry a voice call.

- As it is a duplex transmission both a down-link and up-link slot are used. The slots used are always a slot-pair.

- The 'A-field' section contains the same information as the dummy bearer, with the addition of extra signalling required for the call. The voice data is contained in the 'B-field' section.

In EDCT the dummy bearer is usually separate to the traffic bearers, i.e. they are on different slots. In the case that 4 traffic bearers are required (the maximum number that can be supported by the FP) then one of the traffic bearers will also take over the responsibilities of the dummy bearer. In the remainder of the document this shall be referred to as a 'combined dummy/traffic bearer'.

Since the traffic bearer is already carrying the same information as the dummy bearer, the 'combined dummy/traffic bearer' is the same length as a normal traffic bearer. However, the combined dummy/traffic bearer has some restrictions (compared to a normal traffic bearer) with regards to frequency hopping as detailed later.

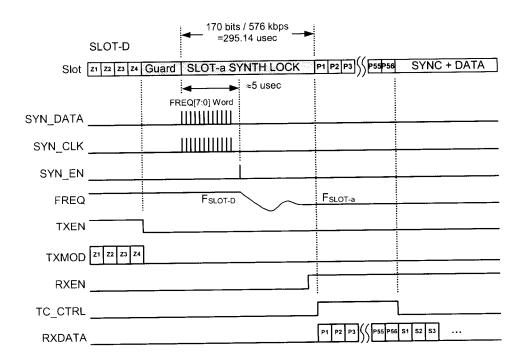

The following diagram shows the down-link transmission of a traffic bearer; the up-link transmission is in slot 1.

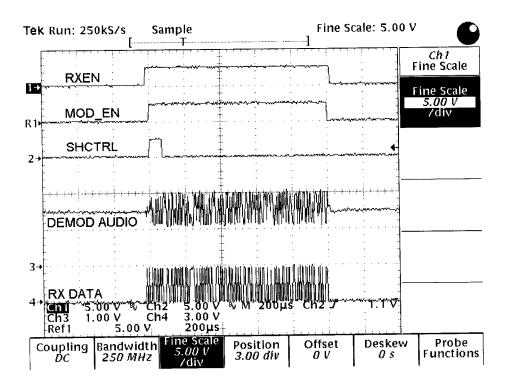

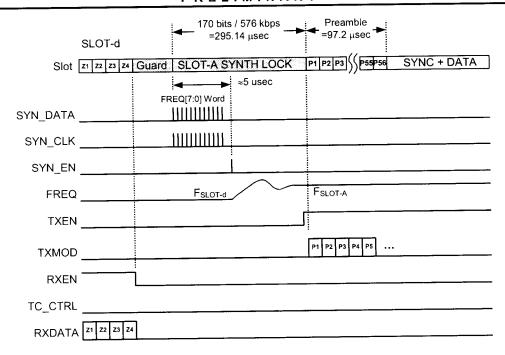

The following diagram shows a dummy bearer transmission. Note, that it uses only a down-link slot and the A-field of the packet.

# 3 OVERVIEW OF FREQUENCY HOPPING ALGORITHM

## 3.1 Hopping rate

Each bearer will change frequency channel, or hop, once per frame, i.e. the bearer hopping rate is 100 hops/second.

In the case of a traffic bearer this means that in a particular frame, both the down-link and up-link slots will use the same frequency channel.

With 4 active traffic bearers, each hopping at 100 hops/sec, there will be 800 frequency changes/second. However, because down-link and up-link use the same channel, this is only actually 400 channels/second.

## 3.2 Hopping Sequence

There are two methods employed for generating the hopping sequences: tables and random number generators (RNGs). Tables are hand-crafted to have specific properties and reverse table-lookup can be used to deduce the position in the table. RNGs generate very long period sequences which are less prone to 'sequence collision'. <u>Both methods are employed in the EDCT system.</u>

### 3.2.1 Hopping pattern base-table

A dummy bearer or combined dummy/traffic bearer uses a table-generated hop sequence.

A single base-table is constructed containing a permutation of the channel numbers 0, 1, 2, ..., 74 (there are no repeats in the sequence). An extract is shown in the following table where 'i' is the index, and 'F<sub>0</sub>' is the base-table sequence.

| i  | F <sub>0</sub> (i) |

|----|--------------------|

| 0  | 0                  |

| 1  | 27                 |

| 2  | 38                 |

| 3  | 14                 |

|    | •••                |

| 74 | 44                 |

(This is only an extract; the full base table is shown in "Appendix B – Base-Table Hopping Sequence").

From this one base-table, additional sequences are generated using the formula:

$$F_x(i) = (F_0(i) + x) \mod 75$$

The sequence index 'i' in the above formula is incremented, modulo 75, each frame. The value 'x' is used to select the required pattern. Due to the modulus there are 75 unique patterns permuted from this single base-table.

The following table shows an extract of the patterns.

| i   | F <sub>0</sub> (i) | F <sub>1</sub> (i) | F <sub>2</sub> (i) | F <sub>3</sub> (i) | •••   | F <sub>74</sub> (i) |

|-----|--------------------|--------------------|--------------------|--------------------|-------|---------------------|

| 0   | 0                  | 1                  | 2                  | 3                  | • • • | 74                  |

| 1   | 27                 | 28                 | 29                 | 30                 | • • • | 26                  |

| 2   | 38                 | 39                 | 40                 | 41                 | • • • | 37                  |

| 3   | 14                 | 15                 | 16                 | 17                 | • • • | 13                  |

| ••• | •••                | •••                | •••                | •••                | •••   | •••                 |

| 8   | 73                 | 74                 | 0                  | 1                  | •••   | 72                  |

|     |                    | •••                | •••                | •••                | •••   | •••                 |

| 74  | 44                 | 45                 | 46                 | 47                 | •••   | 43                  |

The base-table is hand-crafted to meet the following criteria:

- Pseudo-random.

- When any pattern is time-shifted with respect to any other pattern, the number of direct and adjacent channel collisions is minimised. In this context, because of the expected RF performance, adjacent should be taken to mean within 3 channels or less.

- When any pattern is time-shifted with respect to any other pattern, the number of direct or adjacent channel collisions on consecutive hops is minimised. Collisions are minimised for 2, 3 and 4 (or more) consecutive hops.

- Successive channels in the sequence are separated sufficiently to avoid microwave oven interference. In this context, a minimum channel separation of 6 or 8 MHz should be considered sufficient.

#### 3.2.2 LCG random number generator

Traffic bearers use a pseudo-random number generated hop sequence. The random number generator (RNG) is a Linear Congruential Generator (LCG). The general form of an LCG is:

$$R_{n+1} = (a \times R_n + c) \mod m$$

A channel number in the range 0...74 is obtained by applying:

Channel number =  $(75 \times R_n) / m$

In the above formula integer division is used. A particular LCG is denoted by LCG(m, a, c,  $R_0$ ). The proposed RNG for EDCT is LCG(3000,  $(2\times3\times4\times5\times7+1) = 841, 787, R_0$ ):

The modulus (m) is less than  $2^{16}$  so that the 'state' can be stored in a single word (16 bits).

This is a full period generator, with a period of 3000, equivalent to 30 seconds and is also a multiple of 75. As such, all channels are used equally and all channels are used equally over a 30 second period.

The full 3000-long sequence is shown in "Appendix C – LCG Random Hopping Sequence".

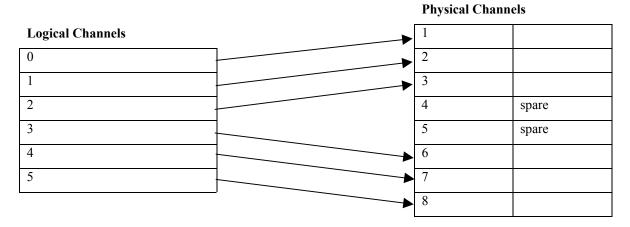

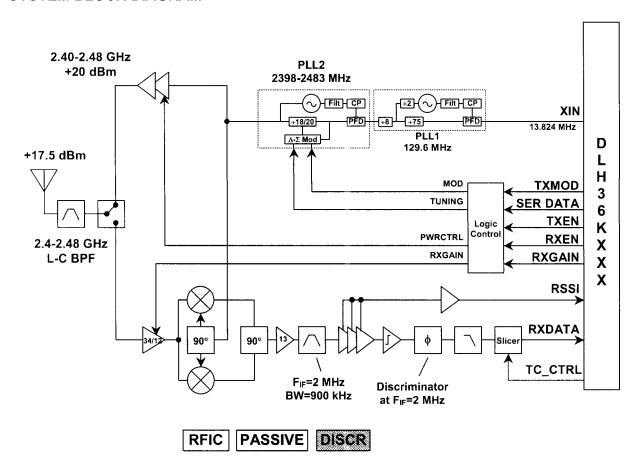

### 3.2.3 Logical and physical channel numbers

The techniques described so far generate channel numbers in the range 0...74. The EDCT system can use a total of 87 hopping channels (numbered from 1... 87). This results in 12 channels that are not part of the normal sequence and these are reserved as 'spare channels'.

The spare channels are used to adapt the hop sequence, which is a method used by EDCT to avoid noisy frequency channels (see later).

A mapping table is used to convert the 'logical channel number' (in the range 0 ... 74) given by the hopping sequence to the 'physical channel number' (in the range 1 ... 87) that is actually used.

An important feature of the mapping table is that it is always a one-to-one mapping, i.e. a physical channel is only ever 'mapped-onto' by one logical channel. In this way the channel usage characteristics of the hop sequence are preserved.

For example, consider the following scenario for a small number of logical and physical channels:

Noisy channels can be adapted out of the sequence by 'channel swapping', i.e. swapping a good spare channel for a noisy channel. For example, swapping physical channels 1 and 3 gives:

Obviously, the above mapping table is an example. The actual mapping table is shown in "Appendix D – Logical To Physical Mapping Table". It satisfies the following criteria:

It maps the 75 logical channels onto 87 physical channels, with a one-to-one mapping. This leaves 12 spare channels that are not used in the unadapted hopping sequence.

The spare channels are only positioned around the 2.45 GHz area. The reason for this is that interference from microwave ovens is most likely<sup>1</sup> to be centred on 2.45 GHz.

To facilitate robust 'sequence adaptation' a requirement is that the basic underlying pattern should be changed as little as possible. This is achieved by always ensuring that the channels are swapped back to their original positions when the channel stops being noisy.

## 3.3 Identifying channel interference

Both the FP and PP can determine channel interference. Interference can be determined by:

- CRC errors on received packets.

- RSSI measurements.

Due to other users of the 2.4 GHz band, the EDCT system has to be tolerant to some interference. EDCT will not be able to avoid the 'random interference' produced by other frequency hopping systems such as Bluetooth or even other EDCT systems. However, it is possible to avoid 'relatively static interference' such as that caused by residential microwave ovens.

In order to distinguish between 'random interference' and 'relatively static interference' it is necessary to detect several successive CRC errors or take several RSSI measurements on a suspect channel. Only then is a channel flagged as being 'bad' – and therefore a candidate for adapting out of the sequence.

## 3.4 Hop sequence adaption

The hopping sequence will be adapted by channel swapping as described already in section 3.2.3.

In this system, there are only 12 spare channels. Therefore, a maximum of 12 channels can be adapted at any one time.

Only traffic bearers and combined dummy/traffic bearers will have their hop sequence adapted.

The FP decides which channels to swap based on information obtained about channel interference (see section 3.3). The FP will send a message to the PP to indicate the swapped channels. When the PP has acknowledged the message both the FP and the PP will adapt their mapping tables and hence their hopping sequences.

# 3.5 Starting a dummy bearer

As already mentioned, a FP will broadcast a dummy bearer all the time it is powered up and operating.

When creating a dummy bearer, the FP will select a slot and initial pattern at random.

In addition the FP will select an initial 'hop sequence index' (HSI) at random. The HSI indexes into the base table to select a logical channel. The HSI is incremented (modulo 75) each frame thereafter.

Once the slot, pattern and initial HSI are selected, a sequence of logical channels can be produced at the bearer hopping rate i.e. one hop *per* frame or 100 hops/sec.

The randomising of slot, pattern and HSI helps to spread out the use of hopping sequences amongst different FPs. However, because each FP will select their own slot, pattern and HSI independently there will be the occasional 'sequence collision'.

\_

<sup>&</sup>lt;sup>1</sup> Actual interference from residential microwave ovens varies greatly with model, loading, environment, time, etc. However, this is a good starting point – the spare channels have to go somewhere!

#### 3.5.1 Avoiding dummy bearer 'sequence collision'

Prior to starting a dummy bearer the FP takes RSSI measurements using the proposed slot and pattern. If these indicate no sequence collision then the dummy bearer is started on the proposed slot and pattern combination. Otherwise, a different slot/pattern pair will be selected, until no sequence collision is detected (or a maximum number of attempts).

Once the dummy bearer has been established, no further action is taken to detect (or correct for) sequence collision on the dummy bearer.

## 3.6 Gaining sync with a dummy bearer

A PP needs to gain sync with a FP's dummy bearer. This involves:

- Synchronising in time, to align the TDMA frame structure.

- 'Locking-on' to the dummy bearer hopping sequence.

In order to align the TDMA frame structure the PP selects an initial channel to start searching. It then waits on that channel until a valid packet is received; this requires the hard-ware to lock onto the 'sync-field' at the start of the packet, which results in the TDMA frame structure being aligned. If a valid packet is not received in a certain time period then the PP will move to another channel and repeat the process.

The most frequently broadcast message on the dummy bearer is the  $N_T$  message. It is transmitted slightly less than every other frame. This message is used to convey the information required for a PP to 'lock-onto' a FP's dummy bearer. However, the PP can only lock-onto a table-generated hopping sequence and so the PP can not use all  $N_T$  messages.

When an  $N_T$  message is received the PP checks he contents to see if it is from a table-generated hopping sequence. If it is then the PP can determine the dummy bearer pattern and the HSI (see section 3.6.1).

Searching continues, with the PP changing slot and/or channel until it receives an  $N_T$  message that it is able to use to 'lock-onto' an FP's dummy bearer.

#### 3.6.1 Determining the pattern and HSI from an N<sub>T</sub> message

A dummy bearer hop sequence is table-generated. The sequence is 75 hops long. Knowing only the pattern number, which is encoded in the  $N_T$  message, and the channel number that the  $N_T$  message was received on, then the HSI can be found directly by reverse table-lookup. Only channels that are in the unadapted sequence are checked, as a PP can not deduce the HSI on an adapted channel.

Once the pattern number and HSI are determined the PP is able to follow the FP's dummy bearer and it is said to be 'locked-onto' the FP.

# 3.7 Following a dummy bearer

Once the PP has locked-onto a FP's dummy bearer it follows the dummy bearer hop sequence and receives broadcast messages from the FP. During this process it collects system information broadcast by the FP, including the dummy bearer slot number and PSPN (see later).

Any number of PPs can be locked-onto a particular FP's dummy bearer.

A PP can enter into Low Duty Cycle (LDC) mode. In this mode the PP saves battery power by only receiving dummy bearer transmissions every 16 or 64 frames. This is sufficiently frequent for the PP to stay synchronised and to pick up 'paging messages' which contain information on incoming calls (and other system status information).

## 3.8 Starting a traffic bearer

In DECT and EDCT it is the PP that initiates the establishment of a traffic bearer. The PP does this by transmitting an ACCESS\_REQUEST message to the FP. The FP constantly listens for ACCESS\_REQUEST messages from PPs on all idle up-link slots, i.e., up-link slots that are not already being used for other traffic bearers.

Successive attempts to establish a traffic bearer use different patterns. This is achieved by the use of the Primary Scan Pattern Number (PSPN). The PSPN determines which pattern is used for a traffic bearer started in the current frame. The FP listens for ACCESS\_REQUESTs on the channel determined by the PSPN pattern and its HSI.

The PSPN is incremented (modulo 75) in each frame whilst the FP is powered up and operating.

The PSPN is known to the PP because it is periodically transmitted on the dummy bearer. Thus once a system's PSPN is known and a FP's HSI is determined, the PP can determine what channel the FP will be listening to during its idle up-link slots.

The PP will select a pattern and slot to use and when the PSPN indicates the selected pattern, the ACCESS\_REQUEST is transmitted on the appropriate channel and slot. To avoid a long latency whilst the selected pattern 'comes around' on the PSPN, the PP selects a pattern that will occur in N frames time. Where N is both small and determined randomly so as to avoid multiple PPs continually colliding whilst trying to establish traffic bearers.

The ACCESS\_REQUEST message contains the identity of the FP to indicate which FP the message is directed at. The requested FP must respond in the next half-frame either with a WAIT or with a BEARER CONFIRM or with a RELEASE.

(This system may seem obscure, but it is a direct consequence of the DECT protocol from which the EDCT protocol was derived.)

In EDCT there are two possible modes of operation:

- The selected pattern is only used for the <u>very first frame</u>. After which both the FP and PP will have synchronised their RNG with the same 'seed' and the random sequence is started and used for the next frame's channel.

- The FP and PP never switch to using a RNG generated hop sequence and instead continue to use the selected table-based pattern.

Traffic bearers normally use a RNG generated hop sequence.

#### 3.8.1 Avoiding traffic bearer 'sequence collision'

Due to the longer period of a RNG-generated hop sequence, the probability of 'sequence collision' on a traffic bearer is much lower than on a table-generated sequence.

Prior to starting a traffic bearer RSSI measurements are taken using the proposed slot and pattern. If these indicate no sequence collision then the traffic bearer is started on the proposed slot and pattern combination. No further action is taken to detect (or correct for) sequence collision.

# 3.9 Starting a combined dummy/traffic bearer

The PP may require to establish a traffic bearer on the slot currently carrying the dummy bearer, usually only when it is the last slot available to it. The PP must use the same pattern that the dummy bearer is currently using.

If the PP has to wait for the dummy bearer pattern to 'come around' on the PSPN this might introduce a long latency. To avoid this, the FP always listens to the channel dictated by the dummy bearer pattern on the slot that is the pair of the dummy bearer transmission.

#### 3.9.1 Avoiding combined dummy/traffic bearer 'sequence collision'

No action is taken to avoid sequence collision.

#### 3.10 Seamless bearer hand-over & "multi-slot mode"

The 2.4 GHz band is prone to interference. In order to improve the robustness of the EDCT system it has the option to operate in a 'multi-slot mode', whereby two traffic bearers are used simultaneously to carry the same voice data. This achieved by operating in a state of permanent 'bearer hand-over'.

To do this the PP establishes a second traffic bearer with the FP, in the manner already described. In doing so, the PP indicates that this bearer is associated with an existing connection, and as a result, the voice data will get routed accordingly. This second traffic bearer uses a different frequency pattern to that of the first traffic bearer.

In a DECT system bearer hand-over normally occurs between a PP and two different FPs and simultaneous traffic bearers are only present for a short period. In EDCT with multi-slot mode enabled the bearer hand-over occurs between a PP and the same FP and the simultaneous traffic bearers are present, in principle, for the duration of the connection.

#### 3.11 Handset-to-handset mode

The EDCT protocol stack supports a 'handset-to-handset' mode in which two handsets can be used to communicate independently of any FP. This is achieved by one of the handsets acting as a FP for the duration of the handset-to-handset call.

All links to the base-station (true FP) are released when a PP is switched to handset-to-handset mode.

The operation of the handset-to-handset mode is as described above for a regular PP / FP system (the part of the FP is effectively played by one of the PPs). The only difference is that a traffic bearer is always started on the dummy bearer slot, i.e. handset-to-handset communications always use a combined dummy/traffic bearer.

# 3.12 Scanning for noise

The PP will occasionally use spare TDMA slots to take RSSI measurements on frequency channels. These channels are not associated with a specific transmitter and therefore do not follow a specific hopping sequence.

## 4 CONFORMANCE TO FCC REQUIREMENTS

The following sections show how the EDCT system conforms to the appropriate FCC requirements:

## 4.1 Section 15.247(a)(1)

The hopping channel carrier frequencies are separated by 891.871 kHz.

Each bearer is independent and hops at a rate of 100 hops/sec.

The hopping sequence is either table generated or RNG generated:

A table-generated hop sequence is 75 hops long, each channel is used exactly once in the sequence. Therefore, in a 30 second period each frequency channel is used exactly 40 times in that sequence.

An RNG-generated hop sequence is 3000 hops long, each channel is used exactly 40 times in the entire sequence. Therefore, in a 30 second period each frequency channel is used exactly 40 times in that sequence.

The hopping sequence contains 75 logical channels these are mapped-onto 75 physical channels using a mapping table (see section 3.2.3 and "Appendix D – Logical To Physical Mapping Table").

The highest channel occupancy occurs when a FP has 4 traffic bearers, i.e. 8 slots utilised, each using the same hopping sequence. As shown previously, for a given sequence, in a 30 second period each frequency channel is used exactly 40 times. The active transmission time in a slot is 937.5µs. Therefore the average time of occupancy on any frequency channel in a 30 second period is:

$$T = 937.5 \mu s \times 40 \times 8 = 300.0 \text{ ms}$$

As a comparison, the lowest channel occupancy occurs when only a single dummy bearer is being transmitted. Because only the A-field is used on a dummy bearer, the transmission is only  $236.1\mu s$  long, therefore the average time of occupancy on any frequency channel in a 30 second period is:

$$T = 236.1 \mu s \times 40 \times 1 = 9.444 \text{ ms}$$

The maximum 20 dB bandwidth of the hopping channel is less than 891.871 kHz.

A packet is sent once *per* frame *per* bearer for the duration of the bearer; packets are not resent.

See section 3.6 for a description of how the receiver gains synchronisation with the transmitter, i.e. a dummy bearer and has a 900kHz bandwidth IF filter matching transmitted signal bandwidth.

# 4.2 Section 15.247(b)(1)

The maximum peak output power of the intentional radiator is 200mW

# 4.3 Section 15.247(g)

In the case of the dummy bearer, which the FP transmits all the time it is powered up and operating, the hopping sequence cycles through the 75 hops in the selected hopping pattern and then repeats.

In the case of a traffic bearer presented with continuous data, which is the normal case --- as this is a voice system, the hopping sequence cycles through either 3000 hops before repeating for a RNG based sequence or cycles through 75 hops before repeating for a table-based sequence.

In the case of a traffic bearer transmitting short bursts, for example, which may happen if a PP has several failed attempts<sup>2</sup> to establish a traffic bearer, then successive traffic bearers will start on different patterns because the PSPN is incremented each frame – see section 3.8.

Note that this system is a voice system and short burst transmissions are not typical.

# 4.4 Section 15.247(h)

There is no coordination between transmitters for the purpose of avoiding the simultaneous occupancy of hopping frequencies by transmitters in multiple EDCT systems.

Communication only ever takes place between one FP and a PP, never between two FPs or two PPs. (In handset-to-handset mode a PP becomes effectively a FP.) It is actually impossible for a FP to receive a FP packet or a PP to receive a PP packet because their respective 'sync-fields' are different.

An FP and a PP that have an active traffic bearer between them share a common hopping sequence and hop sequence adaption information, i.e. swapped channels. However, neither the FP nor the PP transmits this information to a third party, for any purpose whatsoever.

In actual fact, channel collisions between FPs and PPs can and will take place. These may result in reduced voice quality, but this has to be tolerated.

When two transmitters with overlapping radio cells are using the same slot, pattern and phase within the pattern there is sequence collision. This is detected by the occurrence of multiple, consecutive, corrupted packets. If sequence collision happens on a dummy bearer or a combined dummy/traffic bearer then the FP will randomly select a new pattern. If sequence collision happens on a traffic bearer no action is taken.

\_

<sup>&</sup>lt;sup>2</sup> The protocol actually limits the number of re-tries to 11 before giving up on the connection.

# **APPENDIX A – CHANNEL CENTRE FREQUENCIES**

The following table lists the channel centre frequencies as detailed in section 2.1.

| Physical<br>Channel<br>Number | Centre<br>Frequency<br>(MHz) | Physical<br>Channel<br>Number | Centre<br>Frequency<br>(MHz) | Physical<br>Channel<br>Number | Centre<br>Frequency<br>(MHz) |

|-------------------------------|------------------------------|-------------------------------|------------------------------|-------------------------------|------------------------------|

| 1                             | 2401.808203                  | 31                            | 2428.564307                  | 61                            | 2455.320410                  |

| 2                             | 2402.698096                  | 32                            | 2429.454199                  | 62                            | 2456.210303                  |

| 3                             | 2403.591943                  | 33                            | 2430.348047                  | 63                            | 2457.104150                  |

| 4                             | 2404.481836                  | 34                            | 2431.237939                  | 64                            | 2457.994043                  |

| 5                             | 2405.375684                  | 35                            | 2432.131787                  | 65                            | 2458.887891                  |

| 6                             | 2406.265576                  | 36                            | 2433.021680                  | 66                            | 2459.777783                  |

| 7                             | 2407.159424                  | 37                            | 2433.915527                  | 67                            | 2460.671631                  |

| 8                             | 2408.050000                  | 38                            | 2434.805420                  | 68                            | 2461.561523                  |

| 9                             | 2408.943164                  | 39                            | 2435.699268                  | 69                            | 2462.455371                  |

| 10                            | 2409.833057                  | 40                            | 2436.589160                  | 70                            | 2463.345264                  |

| 11                            | 2410.726904                  | 41                            | 2437.483008                  | 71                            | 2464.239111                  |

| 12                            | 2411.616797                  | 42                            | 2438.372900                  | 72                            | 2465.129004                  |

| 13                            | 2412.510645                  | 43                            | 2439.266748                  | 73                            | 2466.022852                  |

| 14                            | 2413.400537                  | 44                            | 2440.156641                  | 74                            | 2466.912744                  |

| 15                            | 2414.294385                  | 45                            | 2441.050488                  | 75                            | 2467.806592                  |

| 16                            | 2415.184277                  | 46                            | 2441.940381                  | 76                            | 2468.696484                  |

| 17                            | 2416.078125                  | 47                            | 2442.834229                  | 77                            | 2469.590332                  |

| 18                            | 2416.968018                  | 48                            | 2443.724121                  | 78                            | 2470.480225                  |

| 19                            | 2417.861865                  | 49                            | 2444.617969                  | 79                            | 2471.374072                  |

| 20                            | 2418.751758                  | 50                            | 2445.507861                  | 80                            | 2472.263965                  |

| 21                            | 2419.645605                  | 51                            | 2446.401709                  | 81                            | 2473.157813                  |

| 22                            | 2420.535498                  | 52                            | 2447.291602                  | 82                            | 2474.047705                  |

| 23                            | 2421.429346                  | 53                            | 2448.185449                  | 83                            | 2474.941553                  |

| 24                            | 2422.319238                  | 54                            | 2449.075342                  | 84                            | 2475.831445                  |

| 25                            | 2423.213086                  | 55                            | 2449.969189                  | 85                            | 2476.725293                  |

| 26                            | 2424.102979                  | 56                            | 2450.859082                  | 86                            | 2477.615186                  |

| 27                            | 2424.996826                  | 57                            | 2451.752930                  | 87                            | 2478.509033                  |

| 28                            | 2425.886719                  | 58                            | 2452.642822                  |                               |                              |

| 29                            | 2426.780566                  | 59                            | 2453.536670                  |                               |                              |

| 30                            | 2427.670459                  | 60                            | 2454.426563                  |                               |                              |

# **APPENDIX B - BASE-TABLE HOPPING SEQUENCE**

The following table, arranged as an  $8 \times 10$  grid, is the base table for the hopping sequence as detailed in section 3.2.1. The sequence is 75 hops long.

|    | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  |

|----|----|----|----|----|----|----|----|----|----|----|

| 0  | 0  | 27 | 38 | 14 | 26 | 49 | 13 | 33 | 73 | 55 |

| 10 | 16 | 1  | 11 | 54 | 8  | 64 | 2  | 48 | 28 | 61 |

| 20 | 4  | 40 | 65 | 6  | 23 | 67 | 57 | 42 | 12 | 29 |

| 30 | 62 | 36 | 47 | 5  | 71 | 43 | 32 | 56 | 21 | 59 |

| 40 | 39 | 15 | 53 | 18 | 45 | 37 | 74 | 63 | 46 | 3  |

| 50 | 51 | 31 | 72 | 58 | 9  | 70 | 35 | 69 | 25 | 34 |

| 60 | 50 | 60 | 68 | 22 | 52 | 24 | 41 | 7  | 17 | 30 |

| 70 | 19 | 10 | 20 | 66 | 44 |    |    |    |    |    |

# APPENDIX C - LCG RANDOM HOPPING SEQUENCE

The following table, is the random channel sequence produced by the LCG random number generator as detailed in section 3.2.2. The sequence is 3000 hops long.

|     | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  |

|-----|----|----|----|----|----|----|----|----|----|----|

| 0   | 0  | 19 | 66 | 20 | 60 | 68 | 73 | 29 | 43 | 69 |

| 10  | 61 | 51 | 68 | 66 | 2  | 55 | 29 | 31 | 15 | 10 |

| 20  | 48 | 8  | 69 | 38 | 19 | 41 | 61 | 33 | 61 | 27 |

| 30  | 35 | 39 | 71 | 10 | 35 | 28 | 18 | 34 | 33 | 44 |

| 40  | 22 | 71 | 73 | 57 | 52 | 15 | 50 | 36 | 5  | 61 |

| 50  | 8  | 28 | 0  | 28 | 69 | 2  | 6  | 38 | 52 | 2  |

| 60  | 70 | 60 | 1  | 0  | 11 | 63 | 38 | 40 | 23 | 19 |

| 70  | 57 | 16 | 3  | 47 | 27 | 50 | 70 | 41 | 70 | 36 |

| 80  | 44 | 48 | 5  | 19 | 44 | 37 | 27 | 43 | 42 | 53 |

| 90  | 30 | 5  | 7  | 65 | 61 | 24 | 58 | 45 | 14 | 69 |

| 100 | 17 | 37 | 8  | 37 | 3  | 10 | 15 | 47 | 60 | 11 |

| 110 | 4  | 68 | 10 | 9  | 19 | 72 | 47 | 48 | 32 | 28 |

| 120 | 66 | 25 | 12 | 56 | 36 | 59 | 4  | 50 | 4  | 45 |

| 130 | 52 | 57 | 14 | 27 | 53 | 46 | 35 | 52 | 51 | 61 |

| 140 | 39 | 14 | 15 | 74 | 70 | 32 | 67 | 54 | 22 | 3  |

| 150 | 26 | 45 | 17 | 46 | 11 | 19 | 24 | 55 | 69 | 20 |

| 160 | 13 | 2  | 19 | 18 | 28 | 6  | 56 | 57 | 41 | 37 |

| 170 | 74 | 34 | 21 | 64 | 45 | 68 | 12 | 59 | 13 | 53 |

| 180 | 61 | 66 | 22 | 36 | 62 | 54 | 44 | 61 | 59 | 70 |

| 190 | 48 | 22 | 24 | 8  | 3  | 41 | 1  | 62 | 31 | 12 |

| 200 | 35 | 54 | 26 | 55 | 20 | 28 | 33 | 64 | 3  | 29 |

| 210 | 21 | 11 | 28 | 26 | 37 | 15 | 64 | 66 | 50 | 45 |

| 220 | 8  | 43 | 29 | 73 | 54 | 1  | 21 | 68 | 21 | 62 |

| 230 | 70 | 74 | 31 | 45 | 70 | 63 | 53 | 69 | 68 | 4  |

| 240 | 57 | 31 | 33 | 17 | 12 | 50 | 10 | 71 | 40 | 21 |

| 250 | 43 | 63 | 35 | 63 | 29 | 37 | 41 | 73 | 12 | 37 |

| 260 | 30 | 20 | 36 | 35 | 46 | 23 | 73 | 0  | 58 | 54 |

| 270 | 17 | 51 | 38 | 7  | 62 | 10 | 30 | 1  | 30 | 71 |

| 280 | 4  | 8  | 40 | 54 | 4  | 72 | 62 | 3  | 2  | 13 |

| 290 | 65 | 40 | 42 | 25 | 21 | 59 | 18 | 5  | 49 | 29 |

| 300 | 52 | 72 | 43 | 72 | 38 | 45 | 50 | 7  | 20 | 46 |

|-----|----|----|----|----|----|----|----|----|----|----|

| 310 | 39 | 28 | 45 | 44 | 54 | 32 | 7  | 8  | 67 | 63 |

| 320 | 26 | 60 | 47 | 16 | 71 | 19 | 39 | 10 | 39 | 5  |

| 330 | 12 | 17 | 49 | 62 | 13 | 6  | 70 | 12 | 11 | 21 |

| 340 | 74 | 49 | 50 | 34 | 30 | 67 | 27 | 14 | 57 | 38 |

| 350 | 61 | 5  | 52 | 6  | 46 | 54 | 59 | 15 | 29 | 55 |

| 360 | 48 | 37 | 54 | 53 | 63 | 41 | 16 | 17 | 1  | 72 |

| 370 | 34 | 69 | 56 | 24 | 5  | 28 | 47 | 19 | 48 | 13 |

| 380 | 21 | 26 | 57 | 71 | 22 | 14 | 4  | 21 | 19 | 30 |

| 390 | 8  | 57 | 59 | 43 | 38 | 1  | 36 | 22 | 66 | 47 |

| 400 | 70 | 14 | 61 | 15 | 55 | 63 | 68 | 24 | 38 | 64 |

| 410 | 56 | 46 | 63 | 61 | 72 | 50 | 24 | 26 | 10 | 5  |

| 420 | 43 | 3  | 64 | 33 | 14 | 36 | 56 | 28 | 56 | 22 |

| 430 | 30 | 34 | 66 | 5  | 30 | 23 | 13 | 29 | 28 | 39 |

| 440 | 17 | 66 | 68 | 52 | 47 | 10 | 45 | 31 | 0  | 56 |

| 450 | 3  | 23 | 70 | 23 | 64 | 72 | 1  | 33 | 47 | 72 |

| 460 | 65 | 55 | 71 | 70 | 6  | 58 | 33 | 35 | 18 | 14 |

| 470 | 52 | 11 | 73 | 42 | 22 | 45 | 65 | 36 | 65 | 31 |

| 480 | 39 | 43 | 0  | 14 | 39 | 32 | 22 | 38 | 37 | 48 |

| 490 | 25 | 0  | 2  | 60 | 56 | 19 | 53 | 40 | 9  | 64 |

| 500 | 12 | 32 | 3  | 32 | 73 | 5  | 10 | 42 | 55 | 6  |

| 510 | 74 | 63 | 5  | 4  | 14 | 67 | 42 | 43 | 27 | 23 |

| 520 | 61 | 20 | 7  | 51 | 31 | 54 | 74 | 45 | 74 | 40 |

| 530 | 47 | 52 | 9  | 22 | 48 | 41 | 30 | 47 | 46 | 56 |

| 540 | 34 | 9  | 10 | 69 | 65 | 27 | 62 | 49 | 17 | 73 |

| 550 | 21 | 40 | 12 | 41 | 6  | 14 | 19 | 50 | 64 | 15 |

| 560 | 8  | 72 | 14 | 13 | 23 | 1  | 51 | 52 | 36 | 32 |

| 570 | 69 | 29 | 16 | 59 | 40 | 63 | 7  | 54 | 8  | 48 |

| 580 | 56 | 61 | 17 | 31 | 57 | 49 | 39 | 56 | 54 | 65 |

| 590 | 43 | 17 | 19 | 3  | 73 | 36 | 71 | 57 | 26 | 7  |

| 600 | 30 | 49 | 21 | 50 | 15 | 23 | 28 | 59 | 73 | 24 |

| 610 | 16 | 6  | 23 | 21 | 32 | 10 | 59 | 61 | 45 | 40 |

| 620 | 3  | 38 | 24 | 68 | 49 | 71 | 16 | 63 | 16 | 57 |

| 630 | 65 | 69 | 26 | 40 | 65 | 58 | 48 | 64 | 63 | 74 |

| 640 | 52 | 26 | 28 | 12 | 7  | 45 | 5  | 66 | 35 | 16 |

| (50 | 20 | 50       | 20 | 50 | 24 | 22 | 26 | <i>(</i> 0 | 1 7      | 22 |

|-----|----|----------|----|----|----|----|----|------------|----------|----|

| 650 | 38 | 58       | 30 | 58 | 24 | 32 | 36 | 68         | 7        | 32 |

| 660 | 25 | 15       | 31 | 30 | 41 | 18 | 68 | 70         | 53       | 49 |

| 670 | 12 | 46       | 33 | 2  | 57 | 5  | 25 | 71         | 25       | 66 |

| 680 | 74 | 3        | 35 | 49 | 74 | 67 | 57 | 73         | 72       | 8  |

| 690 | 60 | 35       | 37 | 20 | 16 | 54 | 13 | 0          | 44       | 24 |

| 700 | 47 | 67       | 38 | 67 | 33 | 40 | 45 | 2          | 15       | 41 |

| 710 | 34 | 23       | 40 | 39 | 49 | 27 | 2  | 3          | 62       | 58 |

| 720 | 21 | 55       | 42 | 11 | 66 | 14 | 34 | 5          | 34       | 0  |

| 730 | 7  | 12       | 44 | 57 | 8  | 1  | 65 | 7          | 6        | 16 |

| 740 | 69 | 44       | 45 | 29 | 25 | 62 | 22 | 9          | 52       | 33 |

| 750 | 56 | 0        | 47 | 1  | 41 | 49 | 54 | 10         | 24       | 50 |

| 760 | 43 | 32       | 49 | 48 | 58 | 36 | 11 | 12         | 71       | 67 |

| 770 | 29 | 64       | 51 | 19 | 0  | 23 | 42 | 14         | 43       | 8  |

| 780 | 16 | 21       | 52 | 66 | 17 | 9  | 74 | 16         | 14       | 25 |

| 790 | 3  | 52       | 54 | 38 | 33 | 71 | 31 | 17         | 61       | 42 |

| 800 | 65 | 9        | 56 | 10 | 50 | 58 | 63 | 19         | 33       | 59 |

| 810 | 51 | 41       | 58 | 56 | 67 | 45 | 19 | 21         | 5        | 0  |

| 820 | 38 | 73       | 59 | 28 | 9  | 31 | 51 | 23         | 51       | 17 |

| 830 | 25 | 29       | 61 | 0  | 25 | 18 | 8  | 24         | 23       | 34 |

| 840 | 12 | 61       | 63 | 47 | 42 | 5  | 40 | 26         | 70       | 51 |

| 850 | 73 | 18       | 65 | 18 | 59 | 67 | 71 | 28         | 42       | 67 |

| 860 | 60 | 50       | 66 | 65 | 1  | 53 | 28 | 30         | 13       | 9  |

| 870 | 47 | 6        | 68 | 37 | 17 | 40 | 60 | 31         | 60       | 26 |

| 880 | 34 | 38       | 70 | 9  | 34 | 27 | 17 | 33         | 32       | 43 |

| 890 | 20 | 70       | 72 | 55 | 51 | 14 | 48 | 35         | 4        | 59 |

| 900 | 7  | 27       | 73 | 27 | 68 | 0  | 5  | 37         | 50       | 1  |

| 910 | 69 | 58       | 0  | 74 | 9  | 62 | 37 | 38         | 22       | 18 |

| 920 | 56 | 15       | 2  | 46 | 26 | 49 | 69 | 40         | 69       | 35 |

| 930 | 42 | 47       | 4  | 17 | 43 | 36 | 25 | 42         | 41       | 51 |

| 940 | 29 | 4        | 5  | 64 | 60 | 22 | 57 | 44         | 12       | 68 |

| 950 | 16 | 35       | 7  | 36 | 1  | 9  | 14 | 45         | 59       | 10 |

| 960 | 3  | 67       | 9  | 8  | 18 | 71 | 46 | 47         | 31       | 27 |

| 970 | 64 | 24       | 11 | 54 | 35 | 58 | 2  | 49         | 3        | 43 |

| 980 | 51 | 56       | 12 | 26 | 52 | 44 | 34 | 51         | 49       | 60 |

| 990 | 38 | 12       | 14 | 73 | 68 | 31 | 66 | 52         | 21       | 2  |

|     | l  | <u> </u> |    |    | L  |    |    |            | <u> </u> |    |

| 1000 | 25 | 44 | 16 | 45 | 10 | 18 | 23 | 54 | 68 | 19 |

|------|----|----|----|----|----|----|----|----|----|----|

| 1010 | 11 | 1  | 18 | 16 | 27 | 5  | 54 | 56 | 40 | 35 |

| 1020 | 73 | 33 | 19 | 63 | 44 | 66 | 11 | 58 | 11 | 52 |

| 1030 | 60 | 64 | 21 | 35 | 60 | 53 | 43 | 59 | 58 | 69 |

| 1040 | 47 | 21 | 23 | 7  | 2  | 40 | 0  | 61 | 30 | 11 |

| 1050 | 33 | 53 | 25 | 53 | 19 | 27 | 31 | 63 | 2  | 27 |

| 1060 | 20 | 10 | 26 | 25 | 36 | 13 | 63 | 65 | 48 | 44 |

| 1070 | 7  | 41 | 28 | 72 | 52 | 0  | 20 | 66 | 20 | 61 |

| 1080 | 69 | 73 | 30 | 44 | 69 | 62 | 52 | 68 | 67 | 3  |

| 1090 | 55 | 30 | 32 | 15 | 11 | 49 | 8  | 70 | 39 | 19 |

| 1100 | 42 | 62 | 33 | 62 | 28 | 35 | 40 | 72 | 10 | 36 |

| 1110 | 29 | 18 | 35 | 34 | 44 | 22 | 72 | 73 | 57 | 53 |

| 1120 | 16 | 50 | 37 | 6  | 61 | 9  | 29 | 0  | 29 | 70 |

| 1130 | 2  | 7  | 39 | 52 | 3  | 71 | 60 | 2  | 1  | 11 |

| 1140 | 64 | 39 | 40 | 24 | 20 | 57 | 17 | 4  | 47 | 28 |

| 1150 | 51 | 70 | 42 | 71 | 36 | 44 | 49 | 5  | 19 | 45 |

| 1160 | 38 | 27 | 44 | 43 | 53 | 31 | 6  | 7  | 66 | 62 |

| 1170 | 24 | 59 | 46 | 14 | 70 | 18 | 37 | 9  | 38 | 3  |

| 1180 | 11 | 16 | 47 | 61 | 12 | 4  | 69 | 11 | 9  | 20 |

| 1190 | 73 | 47 | 49 | 33 | 28 | 66 | 26 | 12 | 56 | 37 |

| 1200 | 60 | 4  | 51 | 5  | 45 | 53 | 58 | 14 | 28 | 54 |

| 1210 | 46 | 36 | 53 | 51 | 62 | 40 | 14 | 16 | 0  | 70 |

| 1220 | 33 | 68 | 54 | 23 | 4  | 26 | 46 | 18 | 46 | 12 |

| 1230 | 20 | 24 | 56 | 70 | 20 | 13 | 3  | 19 | 18 | 29 |

| 1240 | 7  | 56 | 58 | 42 | 37 | 0  | 35 | 21 | 65 | 46 |

| 1250 | 68 | 13 | 60 | 13 | 54 | 62 | 66 | 23 | 37 | 62 |

| 1260 | 55 | 45 | 61 | 60 | 71 | 48 | 23 | 25 | 8  | 4  |

| 1270 | 42 | 1  | 63 | 32 | 12 | 35 | 55 | 26 | 55 | 21 |

| 1280 | 29 | 33 | 65 | 4  | 29 | 22 | 12 | 28 | 27 | 38 |

| 1290 | 15 | 65 | 67 | 50 | 46 | 9  | 43 | 30 | 74 | 54 |

| 1300 | 2  | 22 | 68 | 22 | 63 | 70 | 0  | 32 | 45 | 71 |

| 1310 | 64 | 53 | 70 | 69 | 4  | 57 | 32 | 33 | 17 | 13 |

| 1320 | 51 | 10 | 72 | 41 | 21 | 44 | 64 | 35 | 64 | 30 |

| 1330 | 37 | 42 | 74 | 12 | 38 | 31 | 20 | 37 | 36 | 46 |

| 1340 | 24 | 74 | 0  | 59 | 55 | 17 | 52 | 39 | 7  | 63 |

|      |    |    |    |    |    |    |    |    |    |    |

| 1050 | 1.1 | 2.0 |     | 21       |    | 1 4 |    | 40 | 1 - 4 |    |

|------|-----|-----|-----|----------|----|-----|----|----|-------|----|

| 1350 | 11  | 30  | 2   | 31       | 71 | 4   | 9  | 40 | 54    | 5  |

| 1360 | 73  | 62  | 4   | 3        | 13 | 66  | 41 | 42 | 26    | 22 |

| 1370 | 59  | 19  | 6   | 49       | 30 | 53  | 72 | 44 | 73    | 38 |

| 1380 | 46  | 51  | 7   | 21       | 47 | 39  | 29 | 46 | 44    | 55 |

| 1390 | 33  | 7   | 9   | 68       | 63 | 26  | 61 | 47 | 16    | 72 |

| 1400 | 20  | 39  | 11  | 40       | 5  | 13  | 18 | 49 | 63    | 14 |

| 1410 | 6   | 71  | 13  | 11       | 22 | 0   | 49 | 51 | 35    | 30 |

| 1420 | 68  | 28  | 14  | 58       | 39 | 61  | 6  | 53 | 6     | 47 |

| 1430 | 55  | 59  | 16  | 30       | 55 | 48  | 38 | 54 | 53    | 64 |

| 1440 | 42  | 16  | 18  | 2        | 72 | 35  | 70 | 56 | 25    | 6  |

| 1450 | 28  | 48  | 20  | 48       | 14 | 22  | 26 | 58 | 72    | 22 |

| 1460 | 15  | 5   | 21  | 20       | 31 | 8   | 58 | 60 | 43    | 39 |

| 1470 | 2   | 36  | 23  | 67       | 47 | 70  | 15 | 61 | 15    | 56 |

| 1480 | 64  | 68  | 25  | 39       | 64 | 57  | 47 | 63 | 62    | 73 |

| 1490 | 50  | 25  | 27  | 10       | 6  | 44  | 3  | 65 | 34    | 14 |

| 1500 | 37  | 57  | 28  | 57       | 23 | 30  | 35 | 67 | 5     | 31 |

| 1510 | 24  | 13  | 30  | 29       | 39 | 17  | 67 | 68 | 52    | 48 |

| 1520 | 11  | 45  | 32  | 1        | 56 | 4   | 24 | 70 | 24    | 65 |

| 1530 | 72  | 2   | 34  | 47       | 73 | 66  | 55 | 72 | 71    | 6  |

| 1540 | 59  | 34  | 35  | 19       | 15 | 52  | 12 | 74 | 42    | 23 |

| 1550 | 46  | 65  | 37  | 66       | 31 | 39  | 44 | 0  | 14    | 40 |

| 1560 | 33  | 22  | 39  | 38       | 48 | 26  | 1  | 2  | 61    | 57 |

| 1570 | 19  | 54  | 41  | 9        | 65 | 13  | 32 | 4  | 33    | 73 |

| 1580 | 6   | 11  | 42  | 56       | 7  | 74  | 64 | 6  | 4     | 15 |

| 1590 | 68  | 42  | 44  | 28       | 23 | 61  | 21 | 7  | 51    | 32 |

| 1600 | 55  | 74  | 46  | 0        | 40 | 48  | 53 | 9  | 23    | 49 |

| 1610 | 41  | 31  | 48  | 46       | 57 | 35  | 9  | 11 | 70    | 65 |

| 1620 | 28  | 63  | 49  | 18       | 74 | 21  | 41 | 13 | 41    | 7  |

| 1630 | 15  | 19  | 51  | 65       | 15 | 8   | 73 | 14 | 13    | 24 |

| 1640 | 2   | 51  | 53  | 37       | 32 | 70  | 30 | 16 | 60    | 41 |

| 1650 | 63  | 8   | 55  | 8        | 49 | 57  | 61 | 18 | 32    | 57 |

| 1660 | 50  | 40  | 56  | 55       | 66 | 43  | 18 | 20 | 3     | 74 |

| 1670 | 37  | 71  | 58  | 27       | 7  | 30  | 50 | 21 | 50    | 16 |

| 1680 | 24  | 28  | 60  | 74       | 24 | 17  | 7  | 23 | 22    | 33 |

| 1690 | 10  | 60  | 62  | 45       | 41 | 4   | 38 | 25 | 69    | 49 |

|      |     |     | l . | <u> </u> | L  | l . |    | ]  | L     |    |

| 1700 | 70       | 17       | (2 | 1.7      | <b>50</b> | (5 | 70 | 27 | 40       |    |

|------|----------|----------|----|----------|-----------|----|----|----|----------|----|

| 1700 | 72       | 17       | 63 | 17       | 58        | 65 | 70 | 27 | 40       | 66 |

| 1710 | 59       | 48       | 65 | 64       | 74        | 52 | 27 | 28 | 12       | 8  |

| 1720 | 46       | 5        | 67 | 36       | 16        | 39 | 59 | 30 | 59       | 25 |

| 1730 | 32       | 37       | 69 | 7        | 33        | 26 | 15 | 32 | 31       | 41 |

| 1740 | 19       | 69       | 70 | 54       | 50        | 12 | 47 | 34 | 2        | 58 |

| 1750 | 6        | 25       | 72 | 26       | 66        | 74 | 4  | 35 | 49       | 0  |

| 1760 | 68       | 57       | 74 | 73       | 8         | 61 | 36 | 37 | 21       | 17 |

| 1770 | 54       | 14       | 1  | 44       | 25        | 48 | 67 | 39 | 68       | 33 |

| 1780 | 41       | 46       | 2  | 16       | 42        | 34 | 24 | 41 | 39       | 50 |

| 1790 | 28       | 2        | 4  | 63       | 58        | 21 | 56 | 42 | 11       | 67 |

| 1800 | 15       | 34       | 6  | 35       | 0         | 8  | 13 | 44 | 58       | 9  |

| 1810 | 1        | 66       | 8  | 6        | 17        | 70 | 44 | 46 | 30       | 25 |

| 1820 | 63       | 23       | 9  | 53       | 34        | 56 | 1  | 48 | 1        | 42 |

| 1830 | 50       | 54       | 11 | 25       | 50        | 43 | 33 | 49 | 48       | 59 |

| 1840 | 37       | 11       | 13 | 72       | 67        | 30 | 65 | 51 | 20       | 1  |

| 1850 | 23       | 43       | 15 | 43       | 9         | 17 | 21 | 53 | 67       | 17 |

| 1860 | 10       | 0        | 16 | 15       | 26        | 3  | 53 | 55 | 38       | 34 |

| 1870 | 72       | 31       | 18 | 62       | 42        | 65 | 10 | 56 | 10       | 51 |

| 1880 | 59       | 63       | 20 | 34       | 59        | 52 | 42 | 58 | 57       | 68 |

| 1890 | 45       | 20       | 22 | 5        | 1         | 39 | 73 | 60 | 29       | 9  |

| 1900 | 32       | 52       | 23 | 52       | 18        | 25 | 30 | 62 | 0        | 26 |

| 1910 | 19       | 8        | 25 | 24       | 34        | 12 | 62 | 63 | 47       | 43 |

| 1920 | 6        | 40       | 27 | 71       | 51        | 74 | 19 | 65 | 19       | 60 |

| 1930 | 67       | 72       | 29 | 42       | 68        | 61 | 50 | 67 | 66       | 1  |

| 1940 | 54       | 29       | 30 | 14       | 10        | 47 | 7  | 69 | 37       | 18 |

| 1950 | 41       | 60       | 32 | 61       | 26        | 34 | 39 | 70 | 9        | 35 |

| 1960 | 28       | 17       | 34 | 33       | 43        | 21 | 71 | 72 | 56       | 52 |

| 1970 | 14       | 49       | 36 | 4        | 60        | 8  | 27 | 74 | 28       | 68 |

| 1980 | 1        | 6        | 37 | 51       | 2         | 69 | 59 | 1  | 74       | 10 |

| 1990 | 63       | 37       | 39 | 23       | 18        | 56 | 16 | 2  | 46       | 27 |

| 2000 | 50       | 69       | 41 | 70       | 35        | 43 | 48 | 4  | 18       | 44 |

| 2010 | 36       | 26       | 43 | 41       | 52        | 30 | 4  | 6  | 65       | 60 |

| 2020 | 23       | 58       | 44 | 13       | 69        | 16 | 36 | 8  | 36       | 2  |

| 2030 | 10       | 14       | 46 | 60       | 10        | 3  | 68 | 9  | 8        | 19 |

| 2040 | 72       | 46       | 48 | 32       | 27        | 65 | 25 | 11 | 55       | 36 |

|      | <u> </u> | <u> </u> | I  | <u> </u> | 1         | 1  | 1  | I  | <u> </u> | 1  |

| • • • • |    |    | 1  |    |    |    | 1  | 4.0 |    |    |

|---------|----|----|----|----|----|----|----|-----|----|----|

| 2050    | 58 | 3  | 50 | 3  | 44 | 52 | 56 | 13  | 27 | 52 |

| 2060    | 45 | 35 | 51 | 50 | 61 | 38 | 13 | 15  | 73 | 69 |

| 2070    | 32 | 66 | 53 | 22 | 2  | 25 | 45 | 16  | 45 | 11 |

| 2080    | 19 | 23 | 55 | 69 | 19 | 12 | 2  | 18  | 17 | 28 |

| 2090    | 5  | 55 | 57 | 40 | 36 | 74 | 33 | 20  | 64 | 44 |

| 2100    | 67 | 12 | 58 | 12 | 53 | 60 | 65 | 22  | 35 | 61 |

| 2110    | 54 | 43 | 60 | 59 | 69 | 47 | 22 | 23  | 7  | 3  |

| 2120    | 41 | 0  | 62 | 31 | 11 | 34 | 54 | 25  | 54 | 20 |

| 2130    | 27 | 32 | 64 | 2  | 28 | 21 | 10 | 27  | 26 | 36 |

| 2140    | 14 | 64 | 65 | 49 | 45 | 7  | 42 | 29  | 72 | 53 |

| 2150    | 1  | 20 | 67 | 21 | 61 | 69 | 74 | 30  | 44 | 70 |

| 2160    | 63 | 52 | 69 | 68 | 3  | 56 | 31 | 32  | 16 | 12 |

| 2170    | 49 | 9  | 71 | 39 | 20 | 43 | 62 | 34  | 63 | 28 |

| 2180    | 36 | 41 | 72 | 11 | 37 | 29 | 19 | 36  | 34 | 45 |

| 2190    | 23 | 72 | 74 | 58 | 53 | 16 | 51 | 37  | 6  | 62 |

| 2200    | 10 | 29 | 1  | 30 | 70 | 3  | 8  | 39  | 53 | 4  |

| 2210    | 71 | 61 | 3  | 1  | 12 | 65 | 39 | 41  | 25 | 20 |

| 2220    | 58 | 18 | 4  | 48 | 29 | 51 | 71 | 43  | 71 | 37 |

| 2230    | 45 | 49 | 6  | 20 | 45 | 38 | 28 | 44  | 43 | 54 |

| 2240    | 32 | 6  | 8  | 67 | 62 | 25 | 60 | 46  | 15 | 71 |

| 2250    | 18 | 38 | 10 | 38 | 4  | 12 | 16 | 48  | 62 | 12 |

| 2260    | 5  | 70 | 11 | 10 | 21 | 73 | 48 | 50  | 33 | 29 |

| 2270    | 67 | 26 | 13 | 57 | 37 | 60 | 5  | 51  | 5  | 46 |

| 2280    | 54 | 58 | 15 | 29 | 54 | 47 | 37 | 53  | 52 | 63 |

| 2290    | 40 | 15 | 17 | 0  | 71 | 34 | 68 | 55  | 24 | 4  |

| 2300    | 27 | 47 | 18 | 47 | 13 | 20 | 25 | 57  | 70 | 21 |

| 2310    | 14 | 3  | 20 | 19 | 29 | 7  | 57 | 58  | 42 | 38 |

| 2320    | 1  | 35 | 22 | 66 | 46 | 69 | 14 | 60  | 14 | 55 |

| 2330    | 62 | 67 | 24 | 37 | 63 | 56 | 45 | 62  | 61 | 71 |

| 2340    | 49 | 24 | 25 | 9  | 5  | 42 | 2  | 64  | 32 | 13 |

| 2350    | 36 | 55 | 27 | 56 | 21 | 29 | 34 | 65  | 4  | 30 |

| 2360    | 23 | 12 | 29 | 28 | 38 | 16 | 66 | 67  | 51 | 47 |

| 2370    | 9  | 44 | 31 | 74 | 55 | 3  | 22 | 69  | 23 | 63 |

| 2380    | 71 | 1  | 32 | 46 | 72 | 64 | 54 | 71  | 69 | 5  |

| 2390    | 58 | 32 | 34 | 18 | 13 | 51 | 11 | 72  | 41 | 22 |

|         |    |    | 1  |    | ļ  |    | ļ  |     | l  |    |

| • 100 |    |    | 2.5 |    |    | 20 |    | T = . |    | •  |

|-------|----|----|-----|----|----|----|----|-------|----|----|

| 2400  | 45 | 64 | 36  | 65 | 30 | 38 | 43 | 74    | 13 | 39 |

| 2410  | 31 | 21 | 38  | 36 | 47 | 25 | 74 | 1     | 60 | 55 |

| 2420  | 18 | 53 | 39  | 8  | 64 | 11 | 31 | 3     | 31 | 72 |

| 2430  | 5  | 9  | 41  | 55 | 5  | 73 | 63 | 4     | 3  | 14 |

| 2440  | 67 | 41 | 43  | 27 | 22 | 60 | 20 | 6     | 50 | 31 |

| 2450  | 53 | 73 | 45  | 73 | 39 | 47 | 51 | 8     | 22 | 47 |

| 2460  | 40 | 30 | 46  | 45 | 56 | 33 | 8  | 10    | 68 | 64 |

| 2470  | 27 | 61 | 48  | 17 | 72 | 20 | 40 | 11    | 40 | 6  |

| 2480  | 14 | 18 | 50  | 64 | 14 | 7  | 72 | 13    | 12 | 23 |

| 2490  | 0  | 50 | 52  | 35 | 31 | 69 | 28 | 15    | 59 | 39 |

| 2500  | 62 | 7  | 53  | 7  | 48 | 55 | 60 | 17    | 30 | 56 |

| 2510  | 49 | 38 | 55  | 54 | 64 | 42 | 17 | 18    | 2  | 73 |

| 2520  | 36 | 70 | 57  | 26 | 6  | 29 | 49 | 20    | 49 | 15 |

| 2530  | 22 | 27 | 59  | 72 | 23 | 16 | 5  | 22    | 21 | 31 |

| 2540  | 9  | 59 | 60  | 44 | 40 | 2  | 37 | 24    | 67 | 48 |

| 2550  | 71 | 15 | 62  | 16 | 56 | 64 | 69 | 25    | 39 | 65 |

| 2560  | 58 | 47 | 64  | 63 | 73 | 51 | 26 | 27    | 11 | 7  |

| 2570  | 44 | 4  | 66  | 34 | 15 | 38 | 57 | 29    | 58 | 23 |

| 2580  | 31 | 36 | 67  | 6  | 32 | 24 | 14 | 31    | 29 | 40 |

| 2590  | 18 | 67 | 69  | 53 | 48 | 11 | 46 | 32    | 1  | 57 |

| 2600  | 5  | 24 | 71  | 25 | 65 | 73 | 3  | 34    | 48 | 74 |

| 2610  | 66 | 56 | 73  | 71 | 7  | 60 | 34 | 36    | 20 | 15 |

| 2620  | 53 | 13 | 74  | 43 | 24 | 46 | 66 | 38    | 66 | 32 |

| 2630  | 40 | 44 | 1   | 15 | 40 | 33 | 23 | 39    | 38 | 49 |

| 2640  | 27 | 1  | 3   | 62 | 57 | 20 | 55 | 41    | 10 | 66 |

| 2650  | 13 | 33 | 5   | 33 | 74 | 7  | 11 | 43    | 57 | 7  |

| 2660  | 0  | 65 | 6   | 5  | 16 | 68 | 43 | 45    | 28 | 24 |

| 2670  | 62 | 21 | 8   | 52 | 32 | 55 | 0  | 46    | 0  | 41 |

| 2680  | 49 | 53 | 10  | 24 | 49 | 42 | 32 | 48    | 47 | 58 |

| 2690  | 35 | 10 | 12  | 70 | 66 | 29 | 63 | 50    | 19 | 74 |

| 2700  | 22 | 42 | 13  | 42 | 8  | 15 | 20 | 52    | 65 | 16 |

| 2710  | 9  | 73 | 15  | 14 | 24 | 2  | 52 | 53    | 37 | 33 |

| 2720  | 71 | 30 | 17  | 61 | 41 | 64 | 9  | 55    | 9  | 50 |

| 2730  | 57 | 62 | 19  | 32 | 58 | 51 | 40 | 57    | 56 | 66 |

| 2740  | 44 | 19 | 20  | 4  | 0  | 37 | 72 | 59    | 27 | 8  |

| 2750 | 31 | 50 | 22 | 51 | 16 | 24 | 29 | 60 | 74 | 25 |

|------|----|----|----|----|----|----|----|----|----|----|

| 2760 | 18 | 7  | 24 | 23 | 33 | 11 | 61 | 62 | 46 | 42 |

| 2770 | 4  | 39 | 26 | 69 | 50 | 73 | 17 | 64 | 18 | 58 |

| 2780 | 66 | 71 | 27 | 41 | 67 | 59 | 49 | 66 | 64 | 0  |

| 2790 | 53 | 27 | 29 | 13 | 8  | 46 | 6  | 67 | 36 | 17 |

| 2800 | 40 | 59 | 31 | 60 | 25 | 33 | 38 | 69 | 8  | 34 |

| 2810 | 26 | 16 | 33 | 31 | 42 | 20 | 69 | 71 | 55 | 50 |

| 2820 | 13 | 48 | 34 | 3  | 59 | 6  | 26 | 73 | 26 | 67 |

| 2830 | 0  | 4  | 36 | 50 | 0  | 68 | 58 | 74 | 73 | 9  |

| 2840 | 62 | 36 | 38 | 22 | 17 | 55 | 15 | 1  | 45 | 26 |

| 2850 | 48 | 68 | 40 | 68 | 34 | 42 | 46 | 3  | 17 | 42 |

| 2860 | 35 | 25 | 41 | 40 | 51 | 28 | 3  | 5  | 63 | 59 |

| 2870 | 22 | 56 | 43 | 12 | 67 | 15 | 35 | 6  | 35 | 1  |

| 2880 | 9  | 13 | 45 | 59 | 9  | 2  | 67 | 8  | 7  | 18 |

| 2890 | 70 | 45 | 47 | 30 | 26 | 64 | 23 | 10 | 54 | 34 |

| 2900 | 57 | 2  | 48 | 2  | 43 | 50 | 55 | 12 | 25 | 51 |

| 2910 | 44 | 33 | 50 | 49 | 59 | 37 | 12 | 13 | 72 | 68 |

| 2920 | 31 | 65 | 52 | 21 | 1  | 24 | 44 | 15 | 44 | 10 |

| 2930 | 17 | 22 | 54 | 67 | 18 | 11 | 0  | 17 | 16 | 26 |

| 2940 | 4  | 54 | 55 | 39 | 35 | 72 | 32 | 19 | 62 | 43 |

| 2950 | 66 | 10 | 57 | 11 | 51 | 59 | 64 | 20 | 34 | 60 |

| 2960 | 53 | 42 | 59 | 58 | 68 | 46 | 21 | 22 | 6  | 2  |

| 2970 | 39 | 74 | 61 | 29 | 10 | 33 | 52 | 24 | 53 | 18 |

| 2980 | 26 | 31 | 62 | 1  | 27 | 19 | 9  | 26 | 24 | 35 |

| 2990 | 13 | 62 | 64 | 48 | 43 | 6  | 41 | 27 | 71 | 52 |

|      |    |    |    |    |    |    |    |    |    |    |

# APPENDIX D - LOGICAL TO PHYSICAL MAPPING TABLE

The following table, is the logical to physical mapping table, as detailed in section 3.2.3.

|    | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  |

|----|----|----|----|----|----|----|----|----|----|----|

| 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 |

| 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 |

| 30 | 31 | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 |

| 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 50 |

| 50 | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58 | 72 | 73 |

| 60 | 74 | 75 | 76 | 77 | 78 | 79 | 80 | 81 | 82 | 83 |

| 70 | 84 | 85 | 86 | 87 |    |    |    |    |    |    |

# DH24RF17B

# Digital FHSS RFIC for 2.4GHz ISM Band supporting Multi-Handset Applications

#### **DISTINCTIVE CHARACTERISTICS:**

- 0.25µ CMOS Technology

- Integrated Rx Channel Filters

- FM Discriminator and Data Slicer

- Integrated PLL Synthesizer, including VCO and PLL Loop Filter

- +20 dBm Tx Output Power

- On-Board "Trimmable" XTAL Oscillator

- EDCT Protocol is DSPG Proprietary

#### **GENERAL DESCRIPTION**

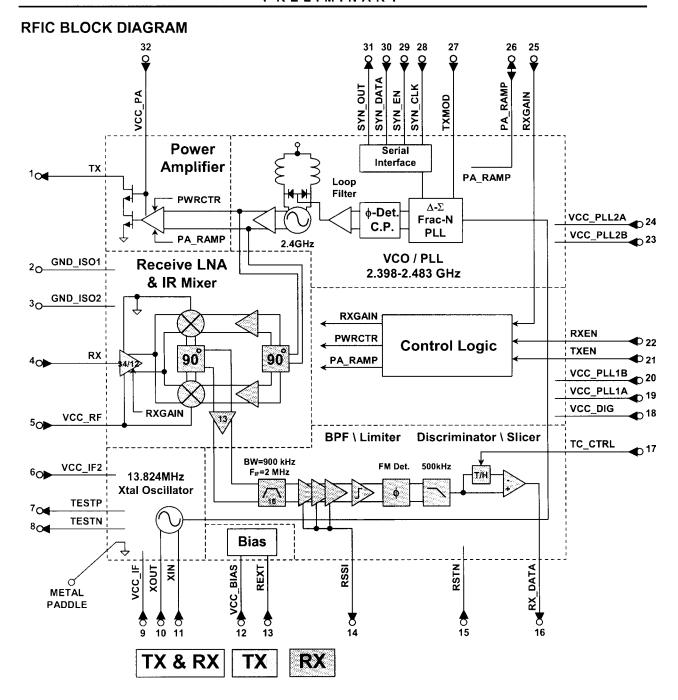

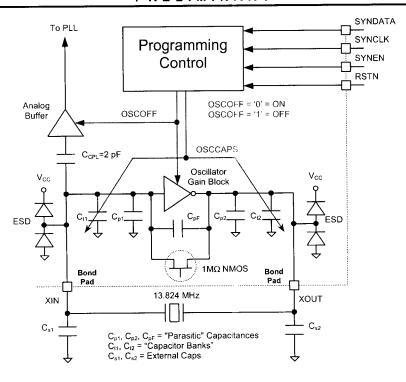

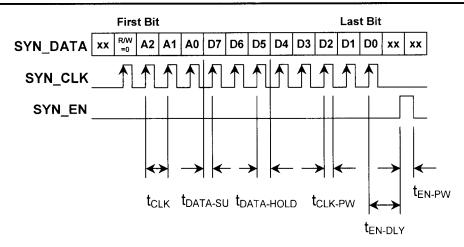

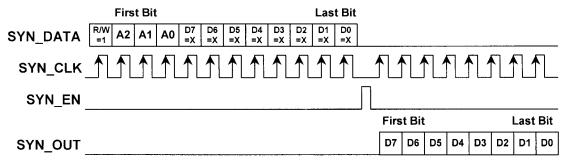

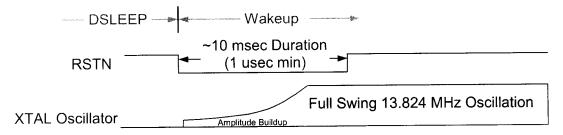

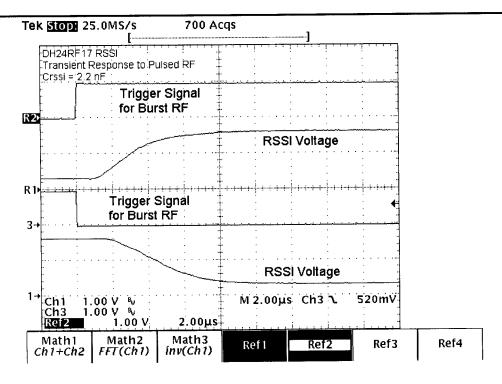

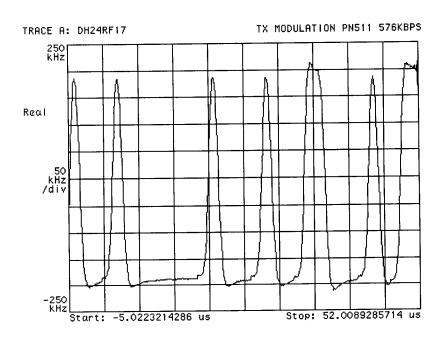

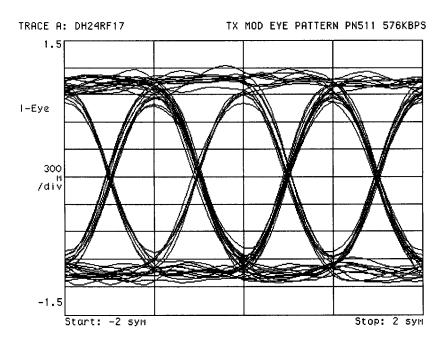

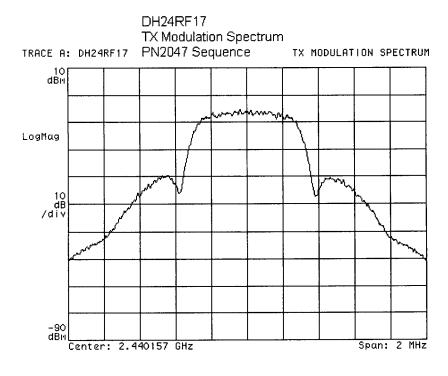

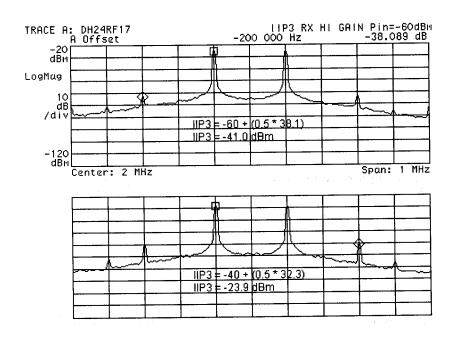

The DH24RF17B Digital FHSS RFIC for 2.4GHz ISM Band supporting Multi-Handset Applications is a member of DSPG's EDCT™ family, which also contains the DLH36K Baseband Processor. This two-chip solution provides a complete solution for a 2.4 GHz cordless telephone chip set. The DH24RF17B is a CMOS Radio Frequency Integrated Circuit (RFIC) that incorporates all of the transmit and receive functions required for a Frequency Hopping Spread Spectrum (FHSS) Digital Cordless transceiver architecture, operating in the 2.4-2.5 GHz Industrial, Scientific, and Medical (ISM) band. The FHSS protocol used by the system utilizes Time Division Duplexing (TDD), in which the transceiver alternately transmits and receives in a burst-like nature.

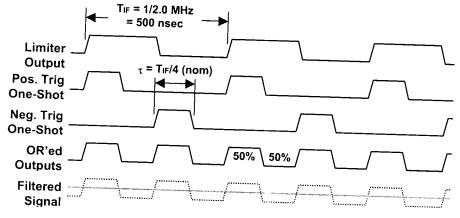

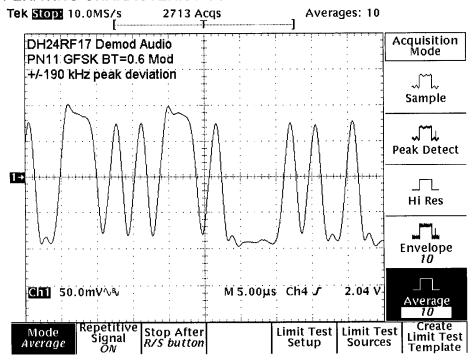

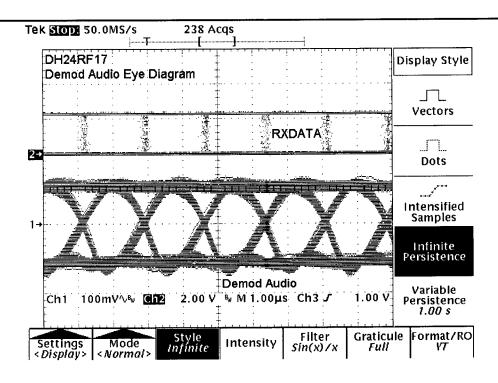

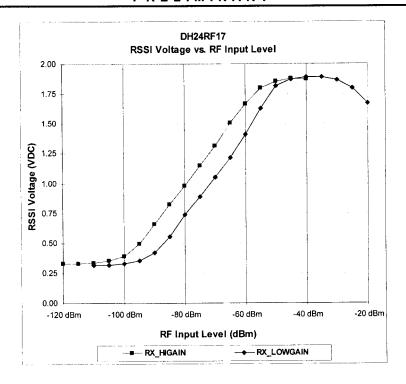

The receive path uses a single-conversion architecture which image-reject mixes the 2-level FSK-modulated receive signal to a low IF frequency of 2 MHz. Integrated bandpass filters provide rejection of unwanted signals. The IF signal is amplified and limited prior to demodulation by an integrated FM discriminator that requires no external components or adjustment. The resulting demodulated audio signal is then filtered, sliced, and output to the baseband chip for further processing.

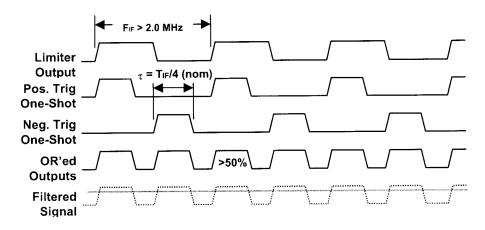

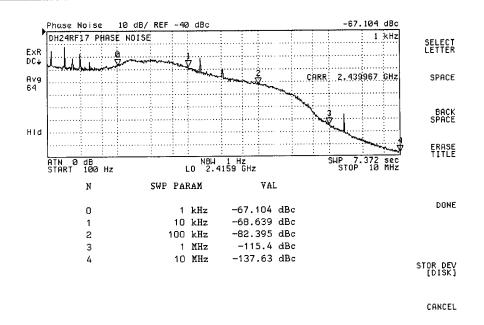

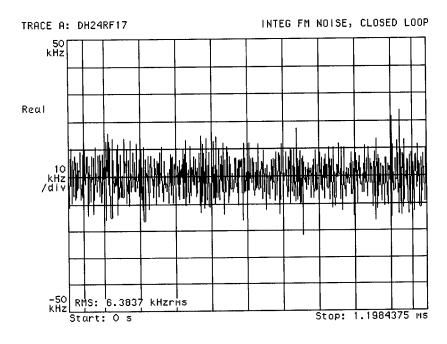

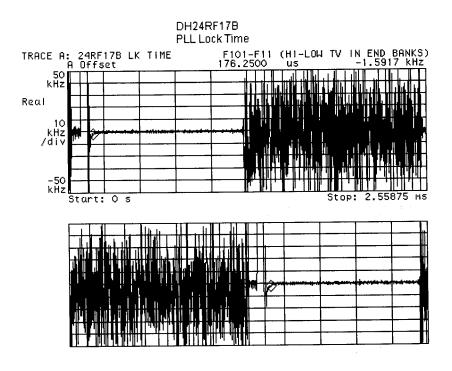

Because the transmitter and receiver are never on at the same time, it is possible to use a single local oscillator (LO) for both transmit and receive modes. This is done by quickly shifting the LO frequency in the gap time between the transmit and receive bursts. The LO is generated by an integrated VCO and  $\Delta$ - $\Sigma$  Fractional-N PLL synthesizer. The transmit FSK data is shaped by a Gaussian low-pass filter and modulated directly into the  $\Delta$ - $\Sigma$  data stream. The transmit path contains an integrated power amplifier capable of delivering +20 dBm in CW mode. The power amplifier is adjustable in output level to minimize current consumption under strong signal conditions. Ramping of the rising and falling edges of the burst signal prevents unwanted spectral splatter.

The TDD architecture of the system makes it possible to integrate both transmit and receive functions in a single chip. The chip is well suited for building digital communication links when used with baseband integrated circuits such as the DLH36K from DSPG.

### PRELIMINARY

# **TABLE OF CONTENTS**

| Distinctive Characteristics:                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                            |

| Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                                                                                            |

| Table of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                                                                            |

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                                                                            |

| Revision Log                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5                                                                                            |