## **Table of Contents for Spec Sheets**

| Assembly / Board | PDF Pages |

|------------------|-----------|

| ADC-26-52        | 2         |

| HMC199           | 3 - 10    |

| HMC8021          | 11 - 16   |

| LET9045          | 17 - 26   |

| MGA-30689        | 27 - 42   |

| OSC-075P2        | 43        |

| PGA-103+         | 44 - 48   |

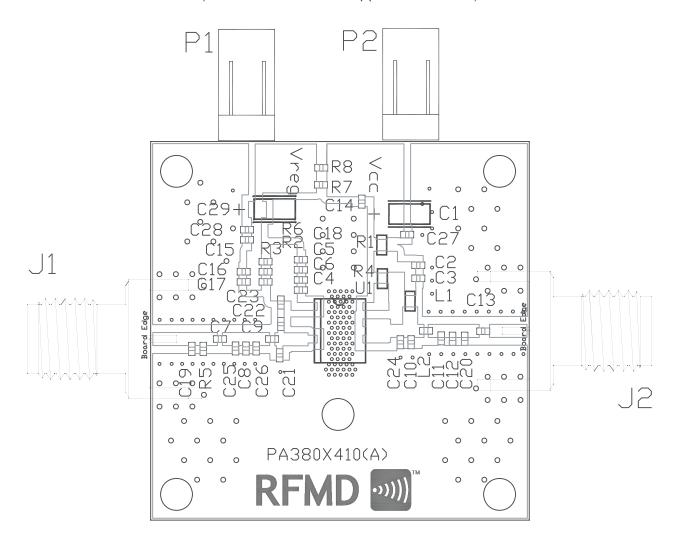

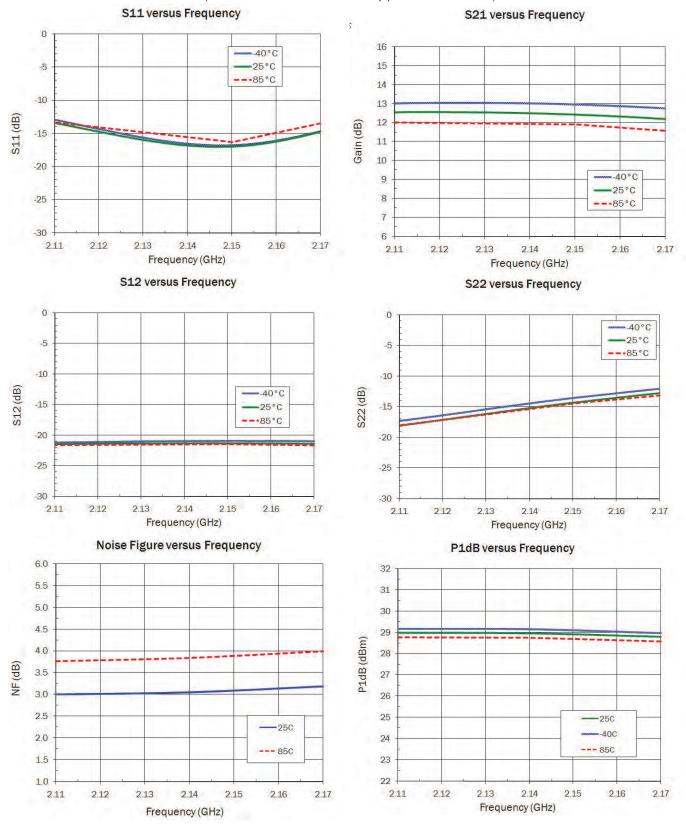

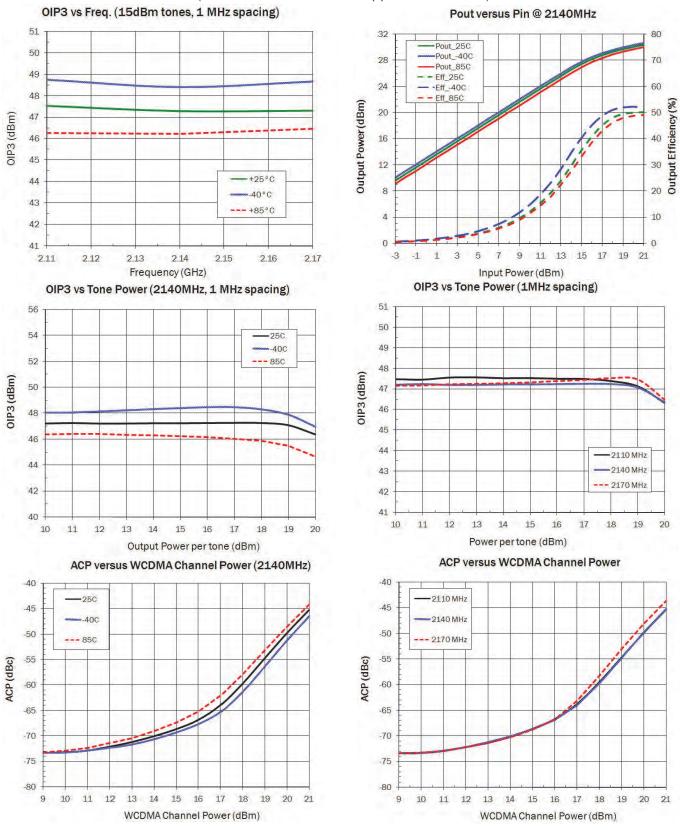

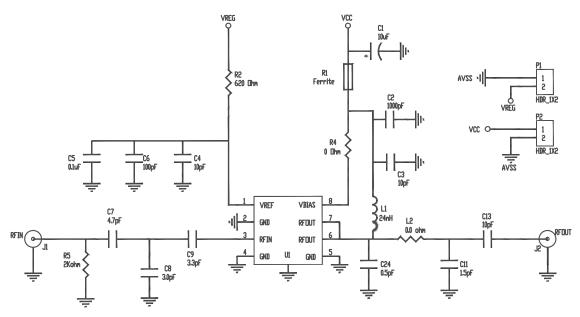

| RFPA3809         | 49 - 59   |

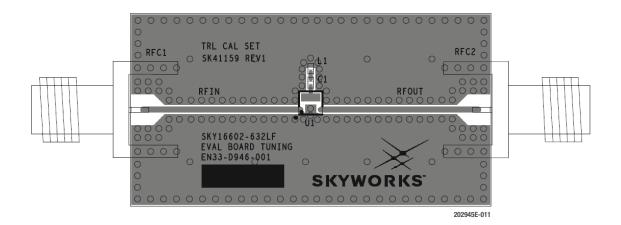

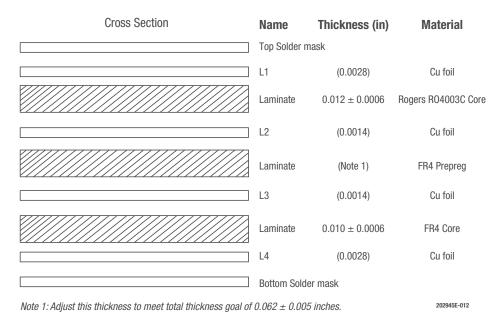

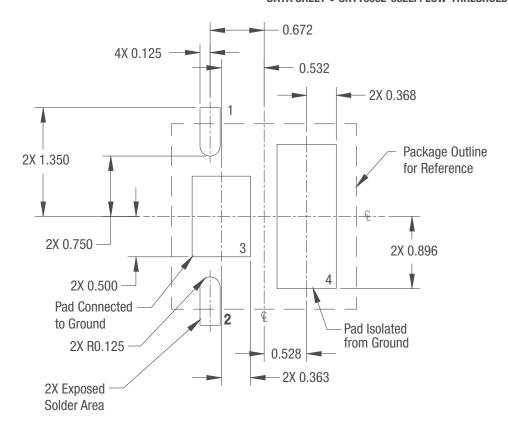

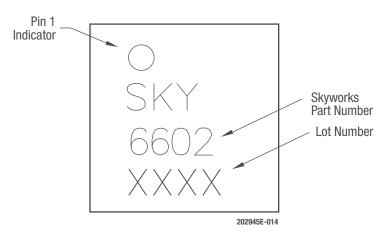

| SKY16602         | 60 - 70   |

| TQL9042          | 71 - 80   |

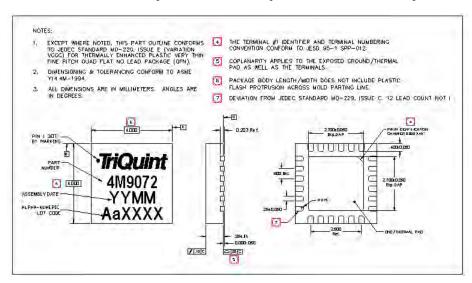

| TQP4M9072        | 81 - 94   |

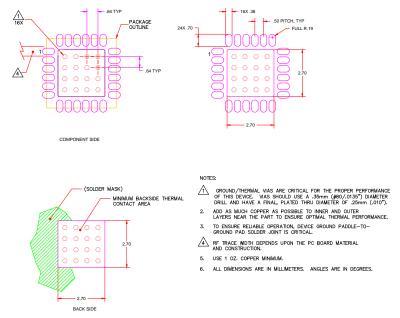

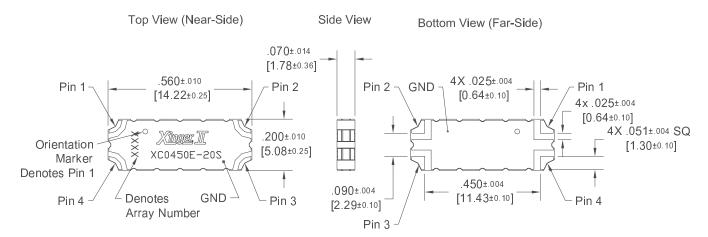

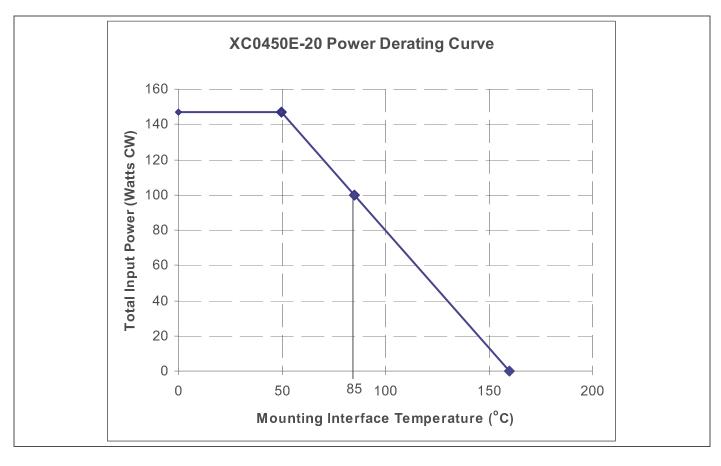

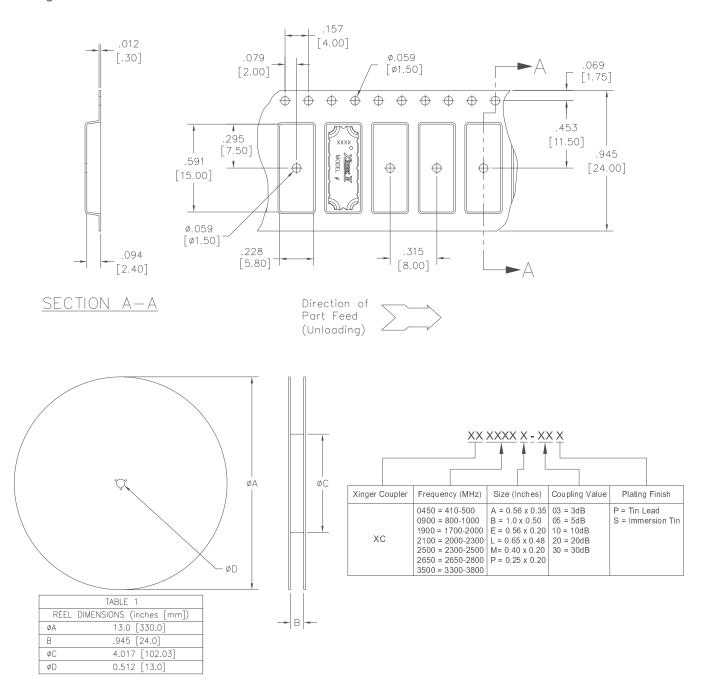

| XC0450E-20       | 95 - 116  |

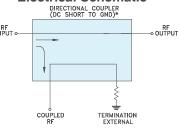

# **Directional Coupler**

## ADC-26-52+

### 10 to 500 MHz

### **Maximum Ratings**

| Operating Temperature             | -40°C to 85°C                |

|-----------------------------------|------------------------------|

| Storage Temperature               | -55°C to 100°C               |

| Permanent damage may occur if any | of these limits are exceeded |

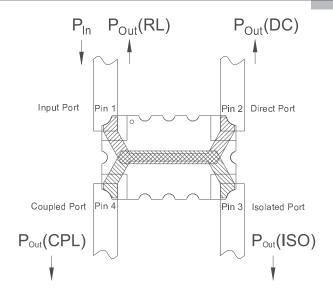

### **Pin Connections**

| INPUT                | 1_ |

|----------------------|----|

| OUTPUT               | 6  |

| COUPLED              | 3  |

| GROUND               | 2  |

| 50Ω TERM EXTERNAL    | 4  |

| ISOLATE (DO NOT USE) | 5  |

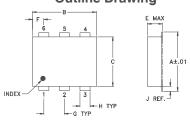

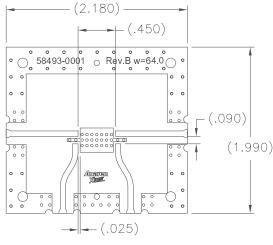

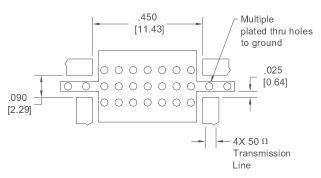

### **Outline Drawing**

### Outline Dimensions (inch)

| A            | B                         | <b>C</b>                         | D            | E            | F    | G                   |

|--------------|---------------------------|----------------------------------|--------------|--------------|------|---------------------|

| . <b>272</b> | .310                      | . <b>220</b>                     | .100         | . <b>162</b> | .055 | .100                |

| 6.91         | 7.87                      | 5.59                             | 2.54         | 4.11         | 1.40 | 2.54                |

| H<br>.030    | J<br>. <b>026</b><br>0.66 | <b>K</b><br>. <b>065</b><br>1.65 | .300<br>7.62 |              |      | wt<br>grams<br>0.25 |

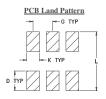

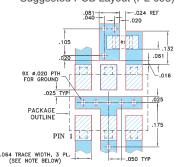

### Demo Board MCL P/N: TB-05 Suggested PCB Layout (PL-095)

RESISTOR R1: 49.9 Ohm, 0805 SIZE. NOTES: 1. TRACE WIDTH IS SHOWN FOR ROGERS RO4350B WITH DIELECTRIC THICKNESS .030" ± .002"; COPPER: 1/2 0Z. EACH SIDE. FOR OTHER MATERIALS TRACE WIDTH MAY NEED TO BE MODIFIED. 2. BOTTOM SIDE OF THE PCB IS CONTINUOUS GROUND PLANE.

DENOTES PCB COPPER LAYOUT WITH SMOBC (SOLDER MASK OVER BARE COPPER)

DENOTES COPPER LAND PATTERN FREE OF SOLDER MASK

#### **Features**

- wideband, 10-500 MHz

- low insertion loss, 0.2 dB typ.

- high directivity, 21 dB typ.

- aqueous washable

- protected by U.S Patents 6,133,525 & 6,140,887

### **Applications**

- VHF/UHF

- reflective power measurements

- communications

- · signal sampling

### CASE STYLE: CD636

+RoHS Compliant The +Suffix identifies RoHS Compliance. See our web site for RoHS Compliance methodologies and qualifications

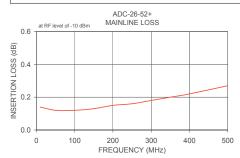

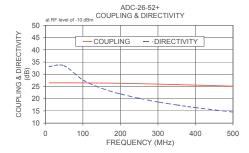

### **Directional Coupler Electrical Specifications**

| FREQ. COUPLING<br>RANGE (dB)   |          | MAINLINE LOSS <sup>1</sup> (dB) |           | DIRECTIVITY (dB) |           |           | VSWR<br>(:1) | POV<br>INP<br>(V | UT <sup>2</sup> |      |      |

|--------------------------------|----------|---------------------------------|-----------|------------------|-----------|-----------|--------------|------------------|-----------------|------|------|

|                                |          | Тур.                            | L         | M                | U         | L         | M            | U                |                 | LM   | U    |

| f <sub>L</sub> -f <sub>U</sub> | Nom.     | Flatness                        | Тур. Мах. | Тур. Мах.        | Тур. Мах. | Typ. Min. | Typ. Min.    | Typ. Min.        | Тур.            | Max. | Max. |

| 10-500                         | 26.0±0.5 | ±0.9                            | 0.15 0.35 | 0.2 0.3          | 0.3 0.5   | 35 22     | 25 16        | 18 11            | 1.1             | 2.0  | 5    |

- L= 10-100 MHz

- M= 100-250 MHz

- U= 250-500 MHz

- 1. Mainline loss includes theoretical power loss at coupled port. 2. Derate linearly to 0.5 Watt for "L, M" band and 1 Watt for "U" band at 85°C.

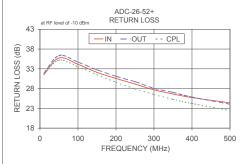

### **Typical Performance Data**

| Frequency<br>(MHz) | Mainline Loss (dB) | Coupling<br>(dB) | Directivity<br>(dB) | Return Loss<br>(dB) |       |       |

|--------------------|--------------------|------------------|---------------------|---------------------|-------|-------|

|                    | In-Out             | In-CpI           |                     | In                  | Out   | СрІ   |

| 10.00              | 0.14               | 26.49            | 33.14               | 31.50               | 31.90 | 31.60 |

| 50.00              | 0.12               | 26.51            | 33.50               | 35.75               | 36.35 | 35.18 |

| 100.00             | 0.12               | 26.48            | 27.68               | 34.14               | 34.71 | 33.55 |

| 150.00             | 0.13               | 26.41            | 24.27               | 32.10               | 32.76 | 31.53 |

| 200.00             | 0.15               | 26.29            | 21.96               | 30.57               | 31.12 | 29.61 |

| 250.00             | 0.16               | 26.14            | 20.19               | 29.15               | 29.75 | 27.93 |

| 300.00             | 0.18               | 25.97            | 18.67               | 27.68               | 28.08 | 26.51 |

| 350.00             | 0.20               | 25.77            | 17.46               | 26.65               | 27.05 | 25.29 |

| 400.00             | 0.22               | 25.56            | 16.37               | 25.73               | 25.86 | 24.24 |

| 500.00             | 0.27               | 25.14            | 14.54               | 24.41               | 24.06 | 22.45 |

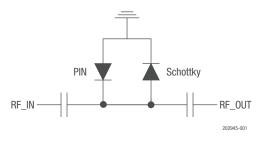

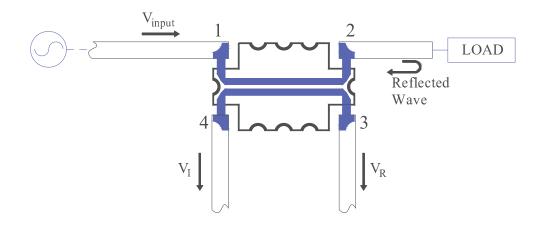

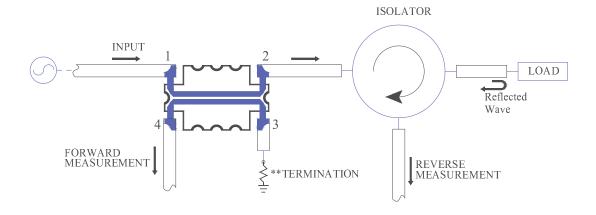

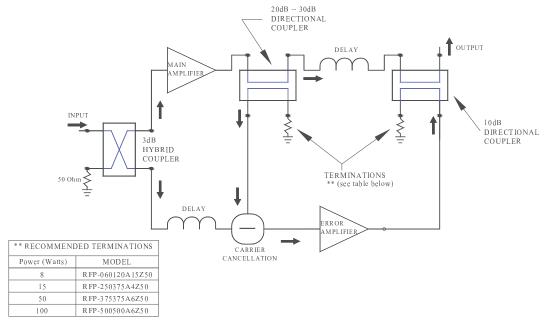

### **Electrical Schematic**

A. Performance and quality attributes and conditions not expressly stated in this specification document are intended to be excluded and do not form a part of this specification document.

B. Electrical specifications and performance data contained in this specification document are based on Mini-Circuit's applicable established test performance criteria and measurement instructions.

C. The parts covered by this specification document are subject to Mini-Circuits standard limited warranty and terms and conditions (collectively, "Standard Terms"). Purchasers of this part are entitled to the rights and benefits contained therein. For a full statement of the Standard Terms and the exclusive rights and remedies thereunder, please visit Mini-Circuits website at www.minicircuits.com/MCLStore/terms.jsp

# Analog Devices Welcomes Hittite Microwave Corporation

NO CONTENT ON THE ATTACHED DOCUMENT HAS CHANGED

/00 0814

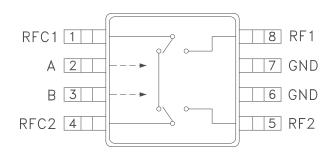

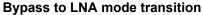

DUAL SPDT SWITCH DC - 2.5 GHz

### Typical Applications

The HMC199AMS8 / 199AMS8E is ideal for:

- Cellular

- ISM Basestations

- PCS

### **Features**

RoHS-Compliant Product

Integrated Dual SPDTs

Low Insertion Loss: <0.5 dB @ 2 GHz

Positive Control: 0/+5V, 0/+3V

Ultra Small MSOP8 Package: 14.8 mm<sup>2</sup>

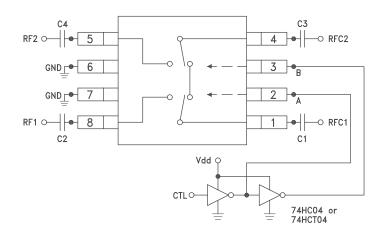

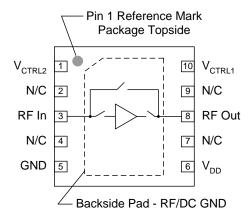

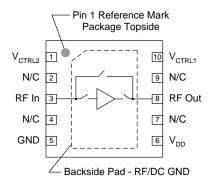

### **Functional Diagram**

### **General Description**

The HMC199AMS8 & HMC199AMS8E are low-cost general purpose dual SPDT GaAs "bypass" switches in 8-lead MSOP packages covering DC to 2.5 GHz. These four-RF-port components integrate two SPDT switches and a through line onto a single IC. The designs provide low insertion loss of less than 0.5 dB while switching passive or active external circuit components in and out of the signal path. Port to port isolations are typically 25 to 30 dB. On-chip circuitry enables positive voltage control operation at very low DC currents with control inputs compatible with CMOS and most TTL logic families. Applications include LNA or filter bypass switching and single bit attenuator switching. The HMC199AMS8E is a RoHS-compliant product.

### Electrical Specifications, $T_A = +25^{\circ}$ C, Vctl = 0/+5 Vdc, 50 Ohm System

| Parameter                                                                | Frequency                                    | Min.     | Тур.              | Max.              | Units          |

|--------------------------------------------------------------------------|----------------------------------------------|----------|-------------------|-------------------|----------------|

| Insertion Loss                                                           | DC - 1.0 GHz<br>DC - 2.0 GHz<br>DC - 2.5 GHz |          | 0.3<br>0.4<br>0.6 | 0.6<br>0.8<br>1.0 | dB<br>dB<br>dB |

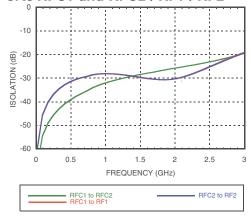

| Isolation (Between Ports RFC1 and RFC2 / RF1 / RF2)                      | DC - 2.0 GHz<br>DC - 2.5 GHz                 | 22<br>17 | 25<br>22          |                   | dB<br>dB       |

| Return Loss (On State, Any Port)                                         | DC - 2.0 GHz<br>DC - 2.5 GHz                 | 20<br>20 | 30<br>30          |                   | dB<br>dB       |

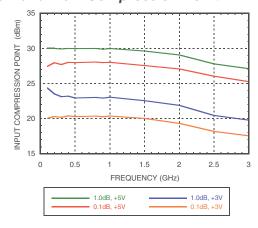

| Input Power for 1 dB Compression                                         | 0.5 - 2.0 GHz                                | 25       | 28                |                   | dBm            |

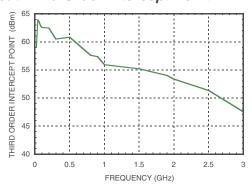

| Input Third Order Intercept<br>(Two-tone Input Power = 13 dBm Each Tone) | 0.5 - 2.0 GHz                                | 40       | 55                |                   | dBm            |

| Switching Characteristics                                                | DC - 2.5 GHz                                 |          |                   |                   |                |

| tRISE, tFALL (10/90% RF)<br>tON, tOFF (50% CTL to 10/90% RF)             |                                              |          | 20<br>40          |                   | ns<br>ns       |

## V00.081

### DUAL SPDT SWITCH DC - 2.5 GHz

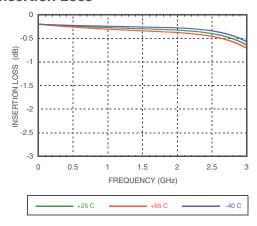

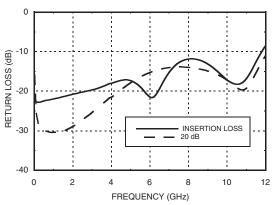

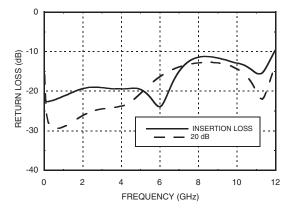

### **Insertion Loss**

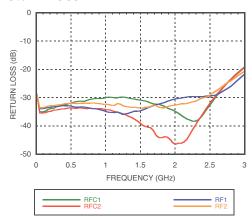

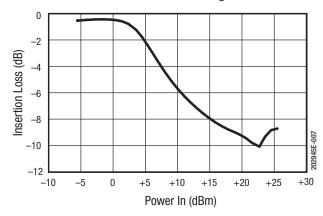

### **Return Loss**

# Isolation Between Ports RFC1 and RFC2 / RF1 / RF2

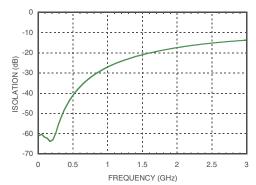

### Isolation Between Ports RF1 and RF2

Note: RFC1 - RFC2 is in insertion loss state

### 0.1 and 1 dB Compression Point

### Input Third Order Intercept Point

00 0814

### **Absolute Maximum Ratings**

| RF Input Power V <sub>CTL</sub> = 0/+5V                         | +29.3 dBm        |  |  |

|-----------------------------------------------------------------|------------------|--|--|

| Control Voltage Range (A & B)                                   | -0.5 to +7.5 Vdc |  |  |

| Channel Temperature                                             | 150 °C           |  |  |

| Continuous Pdiss (T = 85 °C)<br>(derate 5.85 mW/°C above 85 °C) | 0.38 W           |  |  |

| Thermal Resistance                                              | 171 °C/W         |  |  |

| Storage Temperature                                             | -65 to +150 °C   |  |  |

| Operating Temperature                                           | -40 to +85 °C    |  |  |

| ESD Sensitivity (HBM)                                           | Class 1A         |  |  |

### Distortion vs. Frequency

| Control Input | Input Third Order Intercept (dBm)<br>0 dBm Each Tone |          |  |

|---------------|------------------------------------------------------|----------|--|

| (Vdc)         | 900 MHz                                              | 1900 MHz |  |

| +5            | 56                                                   | 52       |  |

| +3            | 52                                                   | 47       |  |

# ELECTROSTATIC SENSITIVE DEVICE OBSERVE HANDLING PRECAUTIONS

### **Truth Table**

\*Control Input Tolerances are ± 0.5 Vdc

| Cor       | Control Input* |            | Control Current<br>(Typical) |            | Signal Path        |                   |                   |

|-----------|----------------|------------|------------------------------|------------|--------------------|-------------------|-------------------|

| A<br>(Vdd | c)             | B<br>(Vdc) | la<br>(µA)                   | lb<br>(μA) | RFC1<br>to<br>RFC2 | RFC1<br>to<br>RF1 | RFC2<br>to<br>RF2 |

| 0         |                | +5         | -1                           | 1          | ON                 | OFF               | OFF               |

| +5        |                | 0          | 1                            | -1         | OFF                | ON                | ON                |

| 0         |                | +3         | -0.1                         | 0.1        | ON                 | OFF               | OFF               |

| +3        |                | 0          | 0.1                          | -0.1       | OFF                | ON                | ON                |

DC blocking capacitors are required at ports RFC1, RFC2, RF1, RF2. Choose value for lowest frequency of operation.

### Compression vs. Frequency

|              | Carrier a                                | t 900MHz                                 | Carrier at 1900MHz                       |                                          |  |

|--------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|--|

| CTL<br>Input | Input Power<br>for 0.1 dB<br>Compression | Input Power<br>for 1.0 dB<br>Compression | Input Power for<br>0.1 dB<br>Compression | Input Power<br>for 1.0 dB<br>Compression |  |

| (Vdc)        | (dBm)                                    | (dBm)                                    | (dBm)                                    | (dBm)                                    |  |

| +5           | 28                                       | 30                                       | 27                                       | 29                                       |  |

| +3           | 20                                       | 23                                       | 20                                       | 22                                       |  |

Caution: Do not operate continuously at RF power input greater than 1 dB compression and do not "hot switch" power levels greater than +22 dBm (Control = 0/+5Vdc).

DUAL SPDT SWITCH DC - 2.5 GHz

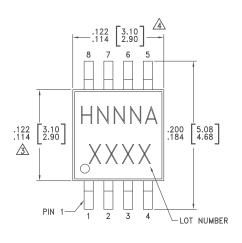

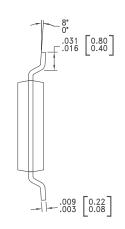

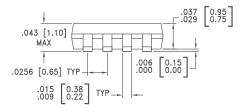

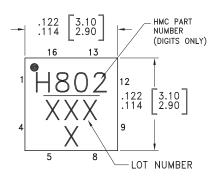

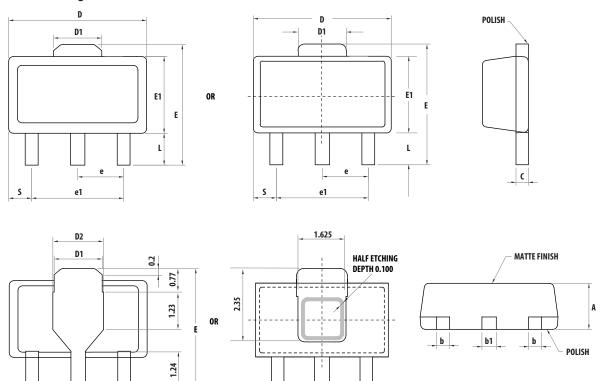

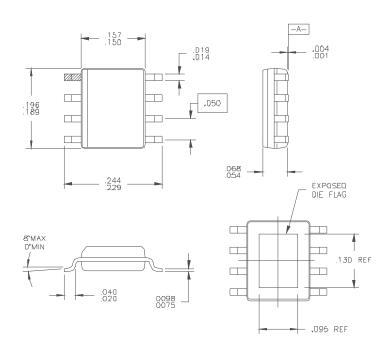

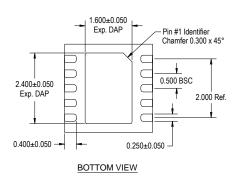

### **Outline Drawing**

#### NOTES:

- 1. LEADFRAME MATERIAL: COPPER ALLOY

- 2. DIMENSIONS ARE IN INCHES [MILLIMETERS].

- DIMENSION DOES NOT INCLUDE MOLDFLASH OF 0.15mm PER SIDE.

- DIMENSION DOES NOT INCLUDE MOLDFLASH OF 0.25mm PER SIDE.

- 5. ALL GROUND LEADS MUST BE SOLDERED TO PCB RF GROUND.

### **Package Information**

| Part Number | Package Body Material                              | Lead Finish   | MSL Rating | Package Marking [3] |

|-------------|----------------------------------------------------|---------------|------------|---------------------|

| HMC199AMS8  | Low Stress Injection Molded Plastic                | Sn/Pb Solder  | MSL1 [1]   | H199A<br>XXXX       |

| HMC199AMS8E | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn | MSL1 [2]   | H199A<br>XXXX       |

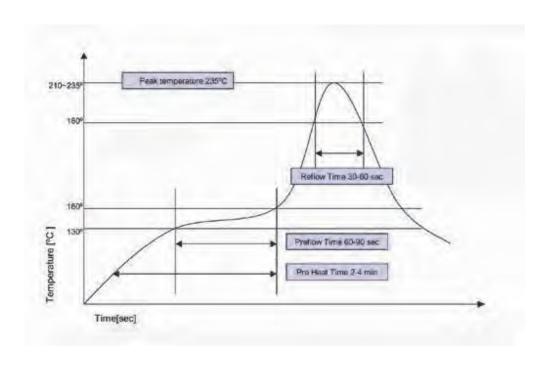

- [1] Max peak reflow temperature of 235 °C

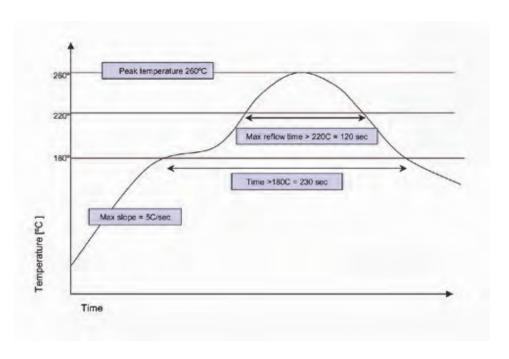

- [2] Max peak reflow temperature of 260  $^{\circ}\text{C}$

- [3] 4-Digit lot number XXXX

00 0814

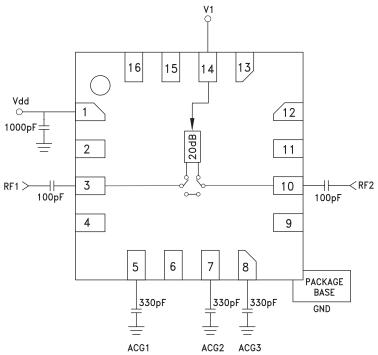

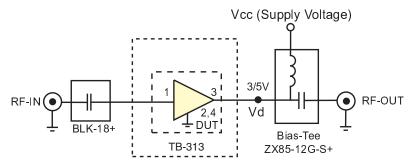

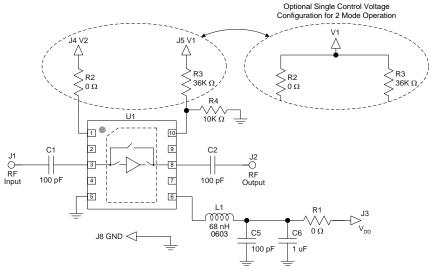

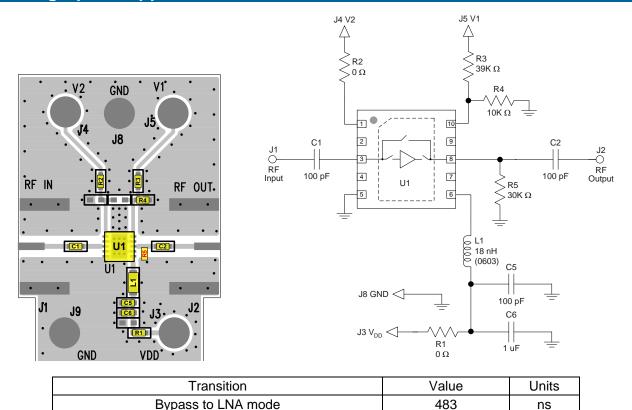

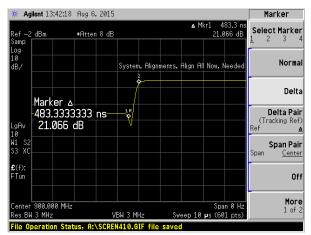

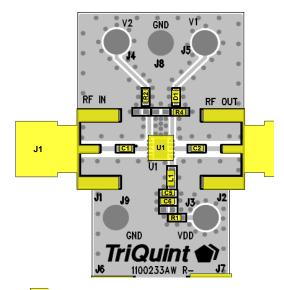

### **Typical Application Circuit**

#### Notes:

- 1. Set A/B control to 0/+5V, Vdd = +5V and use HCT series logic to provide a TTL driver interface.

- 2. Control inputs A/B can be driven directly with CMOS logic (HC) with Vdd = 5 to 7 Volts applied to the CMOS logic gates.

- 3. DC Blocking capacitors are required for each RF port as shown. Capacitor value determines lowest frequency of operation.

- 4. Highest RF signal power capability is achieved with Vdd = +7V and A/B set to 0/+7V.

### DUAL SPDT SWITCH DC - 2.5 GHz

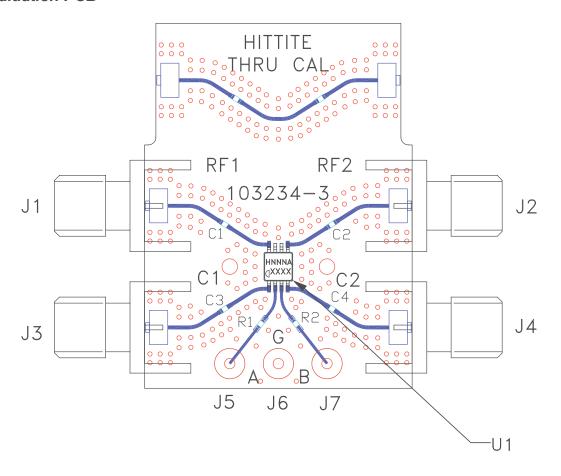

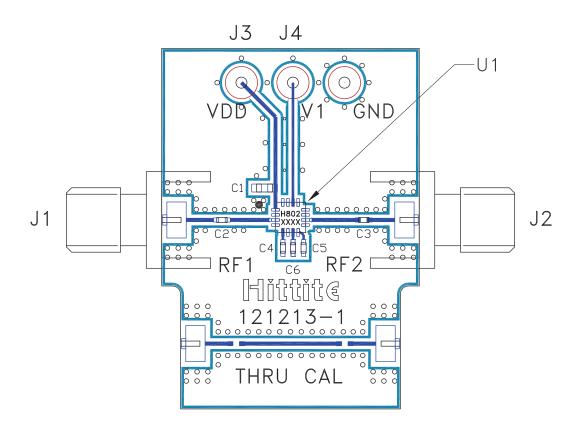

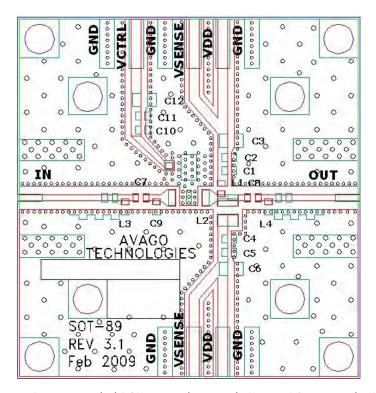

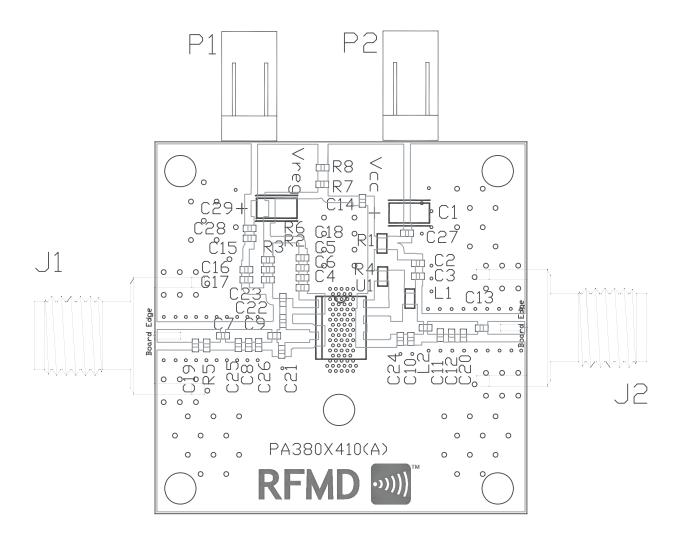

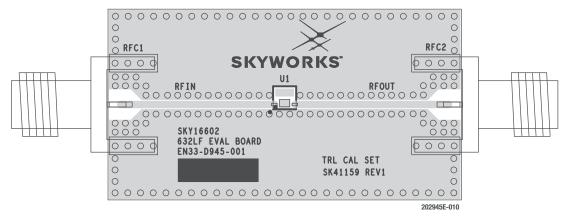

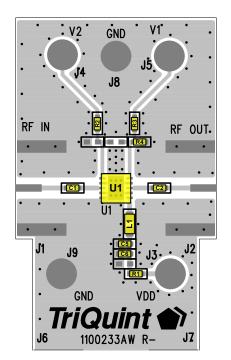

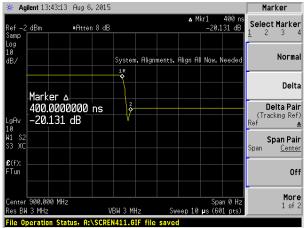

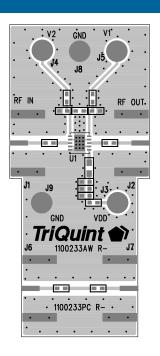

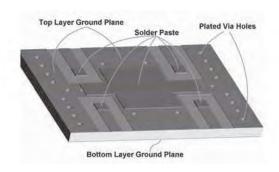

### **Evaluation PCB**

# List of Materials for Evaluation PCB EV1HMC199AMS8 [1]

| Item    | Description                                                                                          |

|---------|------------------------------------------------------------------------------------------------------|

| J1 - J4 | PCB Mount SMA RF Connector                                                                           |

| J5 - J7 | DC Pin                                                                                               |

| C1 - C4 | Chip Capacitor, 0402 Pkg. Choose value for lowest frequency of operation. 330 pF is provided on PCB. |

| R1 - R2 | 100 Ohm Resistor, 0402 Pkg.                                                                          |

| U1      | HMC199AMS8 / 199AMS8E Bypass Switch                                                                  |

| PCB [2] | 103234 Evaluation PCB 1.5" x 1.5"                                                                    |

<sup>[1]</sup> Reference this number when ordering complete evaluation PCB

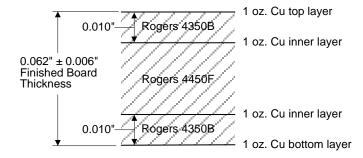

The circuit board used in the application should be generated with proper RF circuit design techniques. Signal lines at the RF ports should have 50 ohm impedance. The evaluation circuit board shown above is available from Hittite Microwave Corporation upon request.

\*R1 & R2 = 100 Ohm.

These optional resistors will provide more RF path to control circuit isolation.

<sup>[2]</sup> Circuit Board Material: Rogers 4350

oHS√

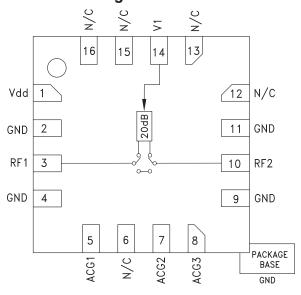

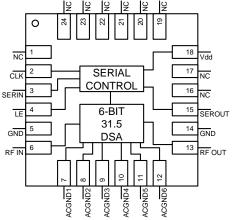

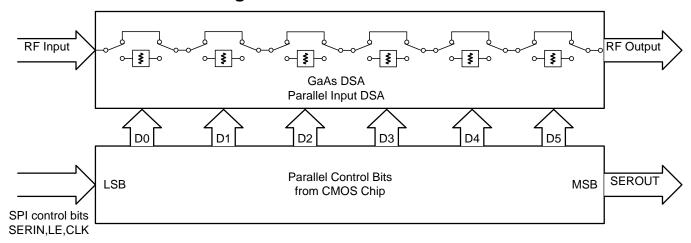

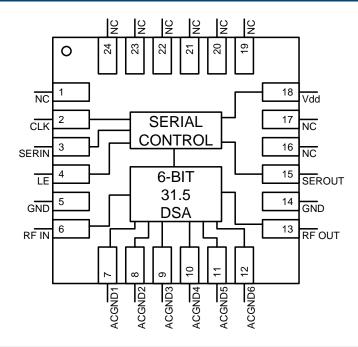

# 20 dB GaAs MMIC 1-BIT DIGITAL POSITIVE CONTROL ATTENUATOR, DC - 10 GHz

### Typical Applications

The HMC802LP3E is ideal for both RF and IF applications:

- Test Equipment and Sensors

- ISM, MMDS, WLAN, WiMAX, WiBro

- Microwave Radio & VSAT

- Cellular Infrastructure

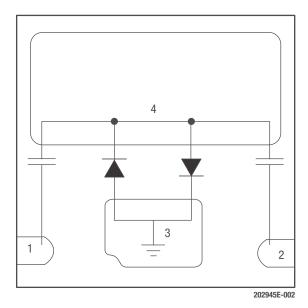

### **Functional Diagram**

### **Features**

± 0.6 dB Typical Step Error Low Insertion Loss: 3 dB

High IP3: +55 dBm Single Control Line

TTL/CMOS Compatible Control

Single +5V Supply

16 Lead 3x3mm SMT Package: 9mm<sup>2</sup>

### **General Description**

The HMC802LP3E is a broadband bidirectional 1-bit GaAs IC digital attenuator in a low cost leadless surface mount package. This single positive control line digital attenuator utilizes off chip AC ground capacitors for near DC operation, making it suitable for a wide variety of RF and IF applications. Covering DC to 10 GHz, the insertion loss is less than 3 dB typical and attenuation accuracy is excellent at  $\pm 0.6$  dB typical. The attenuator also features a high IIP3 of  $\pm 50$  dBm. One TTL/CMOS control input is used to select the attenuation state and a single Vdd bias of  $\pm 50$  is required.

### Electrical Specifications, $T_A = +25^{\circ}$ C, With Vdd = +5V & VctI = 0/+5V

| Parameter                                                                    | Frequency (GHz)                       | Min. | Тур.              | Max.              | Units          |

|------------------------------------------------------------------------------|---------------------------------------|------|-------------------|-------------------|----------------|

| Insertion Loss                                                               | DC - 4 GHz<br>4 - 8 GHz<br>8 - 10 GHz |      | 1.5<br>3.0<br>3.5 | 2.5<br>4.0<br>4.5 | dB<br>dB<br>dB |

| Attenuation Range                                                            | DC - 10 GHz                           |      | 20                |                   | dB             |

| Return Loss (RF1 & RF2, Both States)                                         | DC - 6 GHz<br>6 - 10 GHz              |      | 18<br>12          |                   | dB<br>dB       |

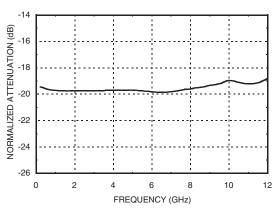

| Attenuation Accuracy: (Referenced to Insertion Loss)                         | DC - 8 GHz<br>8 - 10 GHz              |      | ± 0.4<br>± 0.8    | ± 0.6<br>± 1.2    | dB<br>dB       |

| Input Power for 0.1 dB Compression                                           | DC - 0.4 GHz<br>0.4 - 10 GHz          |      | 20<br>30*         |                   | dBm<br>dBm     |

| Input Third Order Intercept Point<br>(Two-Tone Input Power= 0 dBm Each Tone) | DC - 0.4 GHz<br>0.4 - 10 GHz          |      | 45<br>55          |                   | dBm            |

| Switching Characteristics                                                    |                                       |      |                   |                   |                |

| tRISE, tFALL (10/90% RF)<br>tON, tOFF (50% CTL to 10/90% RF)                 | DC - 10 GHz                           |      | 120<br>150        |                   | ns<br>ns       |

<sup>\*</sup> For frequencies greater than 0.4 GHz, the 0.1 dB compression point is greater than the absolute maximum RF input power of 30 dBm.

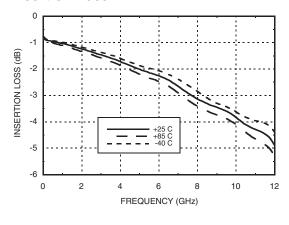

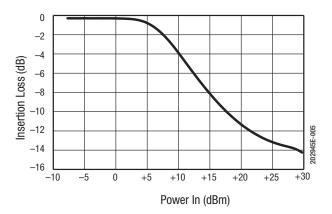

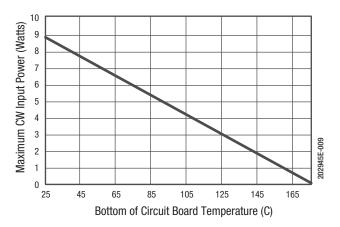

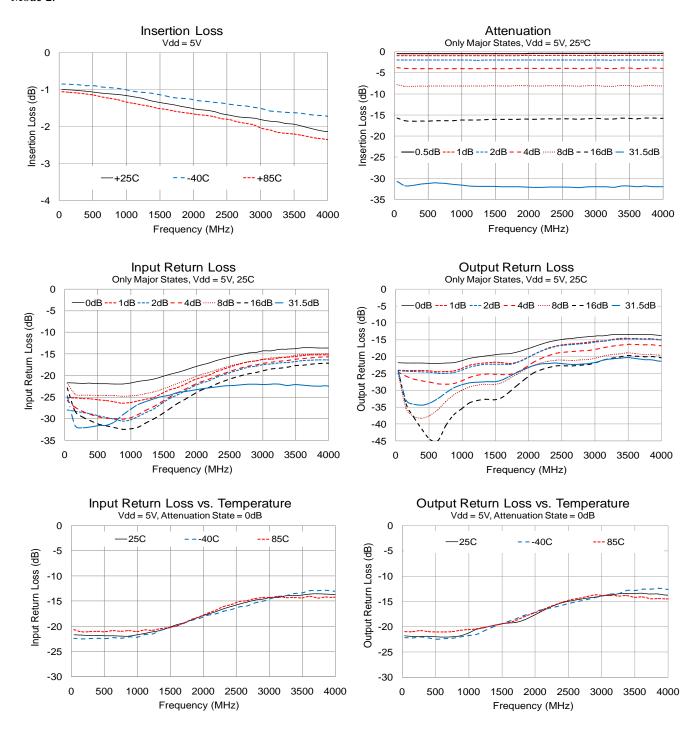

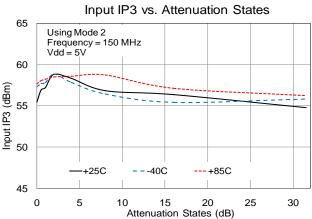

### **Insertion Loss**

### **Input Return Loss**

### **Output Return Loss**

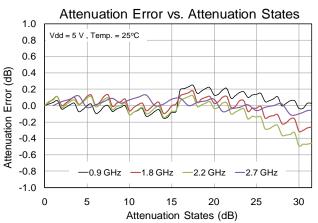

### Relative Attenuation

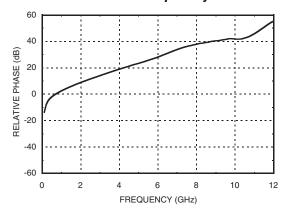

### Relative Phase vs. Frequency

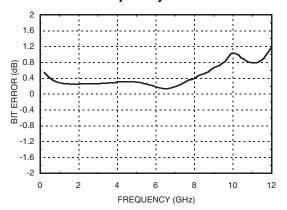

### Bit Error vs. Frequency

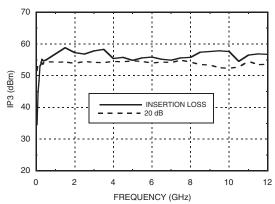

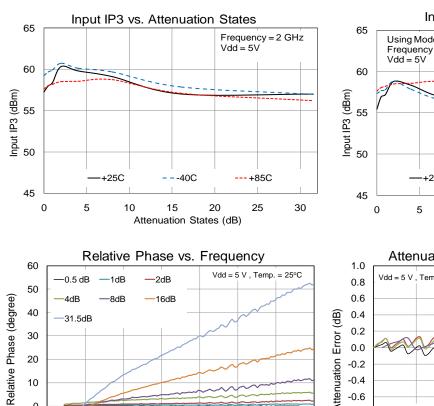

### Input IP3 vs. Frequency

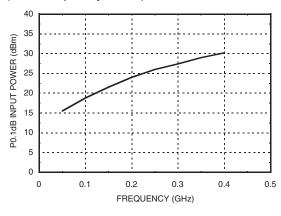

# Input Power for 0.1 dB Compression\* (Low Frequency Detail)

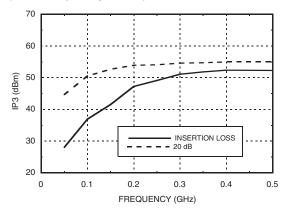

### Input IP3 vs. Frequency

(Low Frequency Detail)

### **Truth Table**

| Control Voltage Input | Attenuation State        |

|-----------------------|--------------------------|

| V1                    | RF1 - RF2                |

| High                  | Reference Insertion Loss |

| Low                   | 20 dB                    |

### **Bias Voltage & Current**

| $Vdd = +5 Vdc \pm 10\%$ |                    |  |

|-------------------------|--------------------|--|

| Vdd<br>(Vdc)            | ldd (Typ.)<br>(mA) |  |

| 4.5                     | 0.21               |  |

| 5.0                     | 0.23               |  |

| 5.5                     | 0.25               |  |

### **Control Voltage**

| State           | Bias Condition          |  |

|-----------------|-------------------------|--|

| Low             | 0 to +0.8V @ -1 μA Typ. |  |

| High            | +2 to +5V @ 30 μA Typ.  |  |

| Note: Vdd = +5V |                         |  |

<sup>\*</sup> For frequencies greater than 0.4 GHz, the 0.1 dB compression point is greater than the absolute maximum RF input power of 30 dBm.

### **Absolute Maximum Ratings**

| RF Input Power (DC - 10 GHz)                                  | +30 dBm        |

|---------------------------------------------------------------|----------------|

| Control Voltage Range (V1)                                    | -1 to Vdd + 1V |

| Bias Voltage (Vdd)                                            | +7 Vdc         |

| Channel Temperature                                           | 150 °C         |

| Continuous Pdiss (T = 85 °C)<br>(derate 12 mW/°C above 85 °C) | 0.783 W        |

| Thermal Resistance (channel to ground paddle)                 | 83 °C/W        |

| Storage Temperature                                           | -65 to +150 °C |

| Operating Temperature                                         | -40 to +85 °C  |

| ESD Sensitivity (HBM)                                         | Class 1A       |

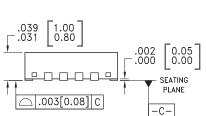

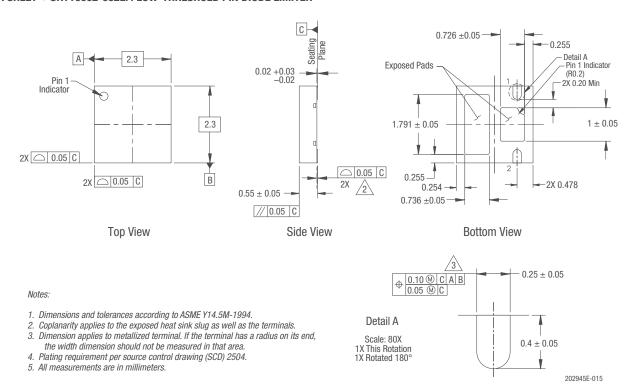

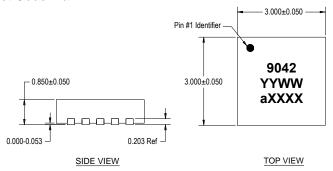

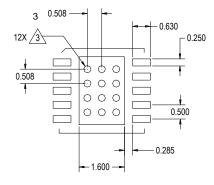

### **Outline Drawing**

#

BOTTOM VIEW

#### NOTES

SQUARE

- 1. LEADFRAME MATERIAL: COPPER ALLOY

- 2. DIMENSIONS ARE IN INCHES [MILLIMETERS]

- 3. LEAD SPACING TOLERANCE IS NON-CUMULATIVE

**PADDLE**

- PAD BURR LENGTH SHALL BE 0.15mm MAXIMUM.

PAD BURR HEIGHT SHALL BE 0.05mm MAXIMUM.

- 5. PACKAGE WARP SHALL NOT EXCEED 0.05mm.

- 6. ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.

- 7. REFER TO HITTITE APPLICATION NOTE FOR SUGGESTED LAND PATTERN.

### Package Information

| Part Number | Package Body Material                              | Lead Finish   | MSL Rating | Package Marking [2] |

|-------------|----------------------------------------------------|---------------|------------|---------------------|

| HMC802LP3E  | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn | MSL1 [1]   | <u>H802</u><br>XXXX |

<sup>[1]</sup> Max peak reflow temperature of 260 °C

<sup>[2] 4-</sup>Digit lot number XXXX

### **Pin Descriptions**

| Pin Number           | Function         | Description                                                                                                                              | Interface Schematic |

|----------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1                    | Vdd              | Supply Voltage.                                                                                                                          |                     |

| 2, 4, 9, 11          | GND              | These pins and the exposed ground paddle must be connected to RF/DC ground.                                                              | ○ GND<br>=          |

| 3, 10                | RF1, RF2         | These pins are DC coupled and matched to 50 Ohms. Blocking capacitors are required. Select value based on lowest frequency of operation. | RF1 RF2             |

| 5, 7, 8              | ACG1, ACG2, ACG3 | External capacitor to ground is required. Select value for lowest frequency of operation. Place capacitor as close to pins as possible.  |                     |

| 6, 12, 13,<br>15, 16 | N/C              | The pins are not connected internally; however, all data shown herein was measured with these pins connected to RF/DC ground externally. |                     |

| 14                   | V1               | See truth table and control voltage table.                                                                                               | V1 0 180K           |

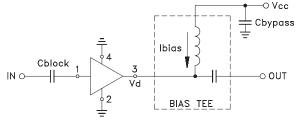

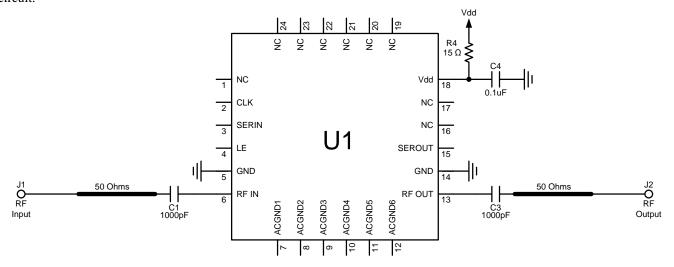

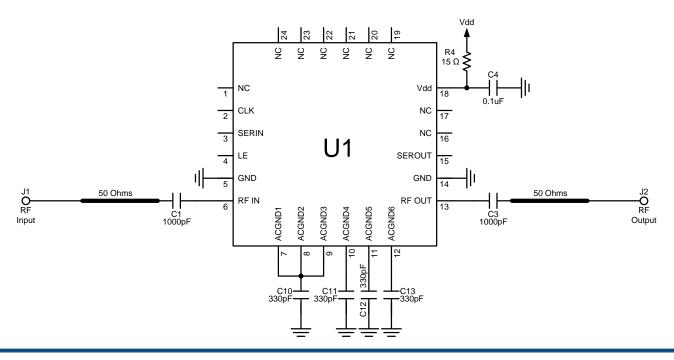

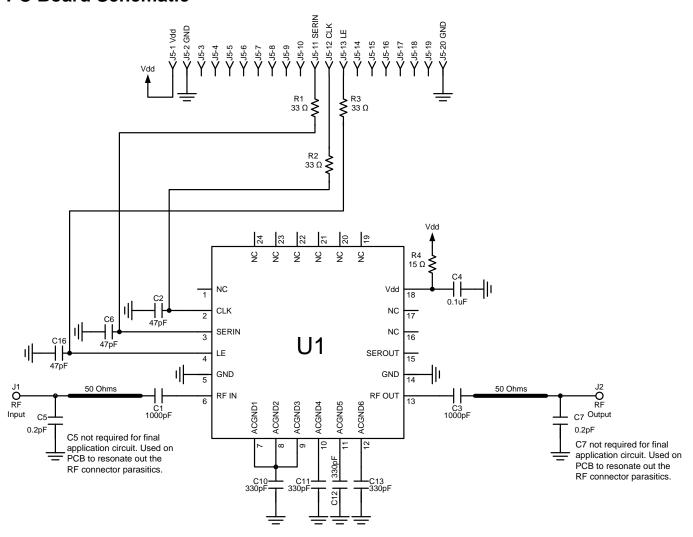

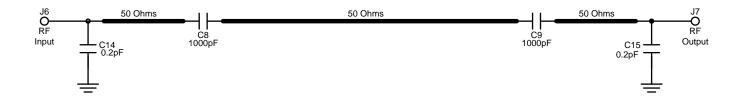

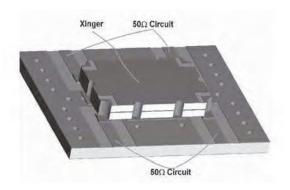

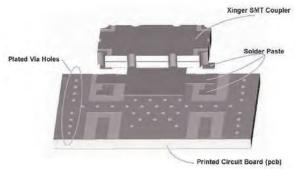

### **Application Circuit**

### **Evaluation PCB**

### List of Materials for Evaluation PCB 127103 [1]

| Item    | Description                   |

|---------|-------------------------------|

| J1, J2  | PCB Mount SMA Connector       |

| J3, J4  | DC Connector                  |

| C1      | 1000 pF Capacitor, 0603 Pkg.  |

| C2, C3  | 100 pF Capacitor, 0402 Pkg.   |

| C4 - C6 | 330 pF Capacitor, 0402 Pkg.   |

| U1      | HMC802LP3E Digital Attenuator |

| PCB [2] | 121213 Evaluation PCB         |

<sup>[1]</sup> Reference this number when ordering complete evaluation PCB

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 Ohm impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.

<sup>[2]</sup> Circuit Board Material: Rogers 4350

### **LET9045C**

# RF power transistor from the LdmoST family of n-channel enhancement-mode lateral MOSFETs

### **Features**

- Excellent thermal stability

- Common source configuration

- P<sub>OUT</sub> (@28 V) = 45 W with 18.5 dB gain @ 960 MHz

- P<sub>OUT</sub> (@36V) = 70 W with 18.5 dB gain @ 960 MHz

- BeO free package

- In compliance with the 2002/95/EC European directive

The LET9045C is a common source N-channel enhancement-mode lateral field-effect RF power transistor designed for broadband commercial and industrial applications at frequencies up to 1.0 GHz. The LET9045C is designed for high gain and broadband performance operating in common source mode at 28 V. It is ideal for base station applications requiring high linearity.

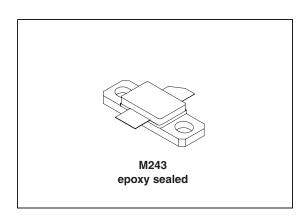

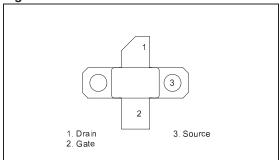

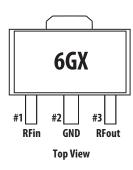

Figure 1. Pin out

Table 1. Device summary

| Order code | Package | Branding |

|------------|---------|----------|

| LET9045C   | M243    | LET9045C |

Maximum ratings LET9045C

# 1 Maximum ratings

Table 2. Absolute maximum ratings ( $T_{CASE} = 25 \, ^{\circ}C$ )

| Symbol               | Parameter                                    | Value       | Unit |

|----------------------|----------------------------------------------|-------------|------|

| V <sub>(BR)DSS</sub> | Drain-source voltage                         | 80          | V    |

| $V_{GS}$             | Gate-source voltage                          | -0.5 to +15 | V    |

| I <sub>D</sub>       | Drain current                                | 9           | Α    |

| P <sub>DISS</sub>    | Power dissipation (@ T <sub>C</sub> = 70 °C) | 108         | W    |

| TJ                   | Max. operating junction temperature          | 200         | °C   |

| T <sub>STG</sub>     | Storage temperature                          | -65 to +150 | °C   |

Table 3. Thermal data

| Symbol              | Parameter                        | Value | Unit |

|---------------------|----------------------------------|-------|------|

| R <sub>th(JC)</sub> | Junction-case thermal resistance | 1.2   | °C/W |

## 2 Electrical characteristics

$T_C = 25$  °C

Table 4. Static

| Symbol               | Test conditions                                          | Min. | Тур. | Max. | Unit |

|----------------------|----------------------------------------------------------|------|------|------|------|

| V <sub>(BR)DSS</sub> | $V_{GS} = 0 \text{ V}; I_{DS} = 10 \text{ mA}$           | 80   |      |      | V    |

| I <sub>DSS</sub>     | V <sub>GS</sub> = 0 V; V <sub>DS</sub> = 28 V            |      |      | 1    | μΑ   |

| I <sub>GSS</sub>     | $V_{GS} = 20 \text{ V}; V_{DS} = 0 \text{ V}$            |      |      | 1    | μΑ   |

| V <sub>GS(Q)</sub>   | $V_{DS} = 28 \text{ V}; I_D = 300 \text{ mA}$            | 2.0  |      | 5.0  | V    |

| V <sub>DS(ON)</sub>  | $V_{GS} = 10 \text{ V}; I_D = 3 \text{ A}$               |      | 0.9  | 1.2  | V    |

| G <sub>FS</sub>      | $V_{DS} = 10 \text{ V}; I_D = 3 \text{ A}$               | 2.5  |      |      | mho  |

| C <sub>ISS</sub>     | V <sub>GS</sub> = 0 V; V <sub>DS</sub> = 28 V; f = 1 MHz |      | 58   |      | рF   |

| C <sub>OSS</sub>     | V <sub>GS</sub> = 0 V; V <sub>DS</sub> = 28 V; f = 1 MHz |      | 29   |      | pF   |

| C <sub>RSS</sub>     | V <sub>GS</sub> = 0 V; V <sub>DS</sub> = 28 V; f = 1 MHz |      | 0.8  |      | pF   |

Table 5. Dynamic

| Symbol           | Test conditions                                                                      | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------------------------------------------------------------|------|------|------|------|

| P <sub>OUT</sub> | V <sub>DD</sub> = 28 V; I <sub>DQ</sub> = 300 mA; P <sub>IN</sub> = 1 W; f = 960 MHz | 45   | 59   |      | W    |

| G <sub>PS</sub>  | V <sub>DD</sub> = 28 V; I <sub>DQ</sub> = 300 mA; P <sub>IN</sub> = 1 W; f = 960 MHz | 16.5 | 17.7 |      | dB   |

| h <sub>D</sub>   | V <sub>DD</sub> = 28 V; I <sub>DQ</sub> = 300 mA; P <sub>IN</sub> = 1 W; f = 960 MHz | 60   | 65   |      | %    |

| Load<br>mismatch | $V_{DD}$ = 28 V; $I_{DQ}$ = 300 mA; $P_{IN}$ = 1 W; f = 960 MHz All phase angles     | 10:1 |      |      | VSWR |

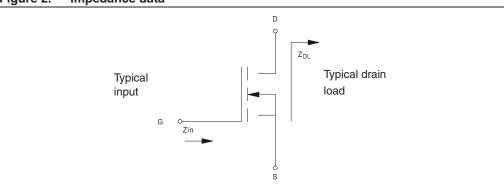

Impedance data LET9045C

## 3 Impedance data

Figure 2. Impedance data

Table 6. Impedance data

| Frequency | <b>Z</b> <sub>IN</sub> (Ω) | Z <sub>DL</sub> (Ω) |

|-----------|----------------------------|---------------------|

| 920       | 0.8 - j 0.08               | 5.3 + j 0.63        |

| 945       | 0.7 - j 0.4                | 5 + j 1.5           |

| 960       | 0.6 - j 0.6                | 4.7 + j 2           |

## 4 Typical performances

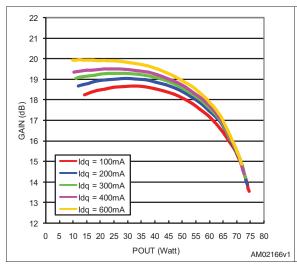

Figure 3. Gain vs output power and bias current, freq = 960 MHz, Vdd = 28 V

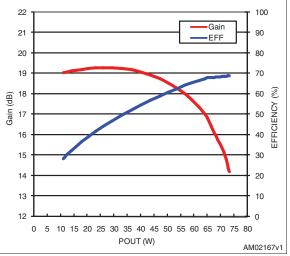

Figure 4. Gain and efficiency vs output power, freq = 960 MHz, Vdd = 28 V, ldq = 300 mA

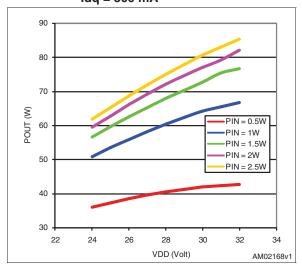

Table 7. Output power vs supply voltage freq = 960 MHz, Vdd = 28 V, Idq = 300 mA

Test circuit LET9045C

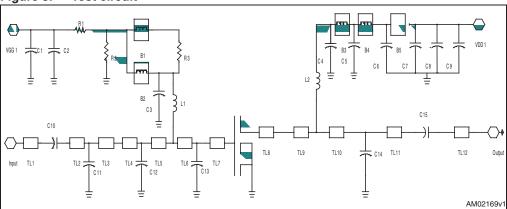

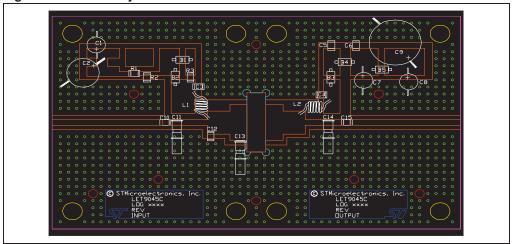

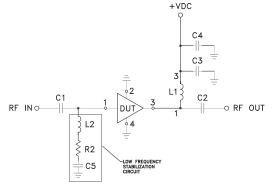

## 5 Test circuit

Figure 5. Test circuit

Table 8. LET9045C components list

| Table 0.               | -   | .L 130430 compon | Citto iiot        |                                                                           |

|------------------------|-----|------------------|-------------------|---------------------------------------------------------------------------|

| Item                   | Qty | Part number      | Vendor            | Description                                                               |

| R1, R2                 | 2   | CR1206-8W-112JB  | VENKEL            | 1.1 kΩ1/8W surface mount chip resistor                                    |

| R3                     | 1   | CR1206-8W-100JB  | VENKEL            | 10 Ω1/8W surface mount chip resistor                                      |

| Coil                   | 2   |                  | BELDEN            | Inductor 5 turns<br>air WOUND#20AWG ID =0.130 in (3.3 mm) bylon<br>coated |

| B1,B2,B<br>3,B4,B5     | 5   | 2743021447       | FAIR-RITE<br>CORP | Surface mount EMI sheild bead                                             |

| C1,C7,<br>C8           | 3   | T491D106K035AT   | Kemet             | 10 μF 35 V tantalum capacitors                                            |

| C2                     | 1   |                  |                   | 100 μF 63 V electrolytic capacitor                                        |

| C3, C4,<br>C10,<br>C15 | 4   | ATC100B470XXXX   | ATC               | 47 pF chip capacitor                                                      |

| C5, C6                 | 2   | ATC200B393MW     | ATC               | 39000 pF chip capacitor                                                   |

| C9                     | 1   |                  |                   | 330 uF 50 V electrolytic capacitor                                        |

| C11,<br>C13,<br>C14    | 3   | 27291PC          | Johanson          | 0.8-8 pF giga trim variable capacitor                                     |

| C12                    | 1   | ATC100B110XXXX   | ATC               | 11 pF chip capacitor                                                      |

| TL1                    |     |                  |                   | L = 1.350in [34.29 mm] W = 0.082in [02.08 mm]                             |

| TL2                    |     |                  |                   | L = 0.144in [3.65 mm] W = 0.082in [02.08 mm]                              |

| TL3                    |     |                  |                   | L = 0.311in [7.91 mm] W = 0.082in [02.08 mm]                              |

| TL4                    |     |                  |                   | L = 00.82in [2.09 mm] W = 0.323in [08.21 mm]                              |

| TL5                    |     |                  |                   | L = 0.194 in [4.94 mm] W = 0.323in [08.21 mm]                             |

LET9045C Test circuit

Table 8. LET9045C components list (continued)

| Item         | Qty | Part number | Vendor      | Description                                   |

|--------------|-----|-------------|-------------|-----------------------------------------------|

| TL6          |     |             |             | L = 0.059in [1.49 mm] W= 0.506in [12.85 mm]   |

| TL7          |     |             |             | L = 0.144in [3.65 mm] W = 0.506in [12.85 mm]  |

| TL8          |     |             |             | L = 0.208in [5.28 mm] W = 0.506in [12.85 mm]  |

| TL9          |     |             |             | L = 0.275in [6.98 mm] W = 0.323in [08.21 mm]  |

| TL10         |     |             |             | L = 0.210in [5.33 mm] W = 0.082in [02.08 mm]  |

| TL11         |     |             |             | L = 0.260in [6.60 mm] W = 0.082in [02.08 mm]  |

| TL12         |     |             |             | L = 1.350in [34.29 mm] W = 0.082in [02.08 mm] |

| Board<br>3X5 | 1   |             | Rogers corp | Er=2.55 t=0.0026in h=0.030in                  |

Figure 6. Circuit layout

### Package mechanical data 6

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK<sup>®</sup> is an ST trademark.

Table 9. M243 (.230 x .360 2L N/HERM W/FLG) mechanical data

| Dim.   |       | mm    |       | inch  |       |       |

|--------|-------|-------|-------|-------|-------|-------|

| Dilli. | Min.  | Тур   | Max.  | Min.  | Тур   | Max.  |

| А      | 5.21  |       | 5.72  | 0.205 |       | 0.225 |

| В      | 5.46  |       | 6.48  | 0.215 |       | 0.255 |

| С      | 5.59  |       | 6.1   | 0.22  |       | 0.24  |

| D      |       | 14.27 |       |       | 0.562 |       |

| Е      | 20.07 |       | 20.57 | 0.79  |       | 0.81  |

| F      | 8.89  |       | 9.4   | 0.35  |       | 0.37  |

| G      | 0.1   |       | 0.15  | 0.004 |       | 0.006 |

| Н      | 3.18  |       | 4.45  | 0.125 |       | 0.175 |

| I      | 1.83  |       | 2.24  | 0.072 |       | 0.088 |

| J      | 1.27  |       | 1.78  | 0.05  |       | 0.07  |

.107/2,72X45\* 2×B (2X).130/3,30 DIA 4× 45° 2X.045/1,14 MAX. OPTIONAL Ð

Figure 7. M243 package dimensions

LET9045C Revision history

# 7 Revision history

Table 10. Document revision history

| Date        | Revision | Changes                                                                     |

|-------------|----------|-----------------------------------------------------------------------------|

| 02-Mar-2009 | 1        | Initial release.                                                            |

| 02-Nov-2009 | 2        | Udated Figure 4.                                                            |

| 11-Feb-2010 | 3        | Changed test condition for V <sub>(BR)DSS</sub> in <i>Table 4: Static</i> . |

| 15-Apr-2011 | 4        | Updated features in cover page.                                             |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2011 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

10/10 Doc ID 15443 Rev 4

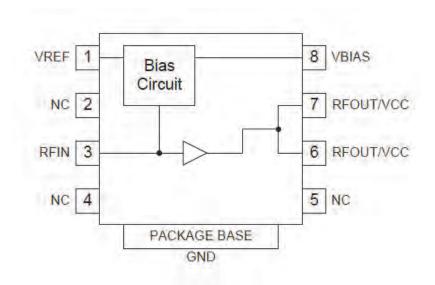

### MGA-30689

40MHz - 3000MHz Flat Gain High Linearity Gain Block

# Data Sheet

### **Description**

Avago Technologies' MGA-30689 is a flat gain, high linearity, low noise, 22dBm Gain Block with good OIP3 achieved through the use of Avago Technologies' proprietary 0.25um GaAs Enhancement-mode pHEMT process.

The device required simple dc biasing components to achieve wide bandwidth performance. The temperature compensated internal bias circuit provides stable current over temperature and process threshold voltage variation.

The MGA-30689 is housed inside a standard SOT89 package (4.5 x 4.1 x 1.5 mm).

### **Applications**

- IF amplifier, RF driver amplifier

- General purpose gain block

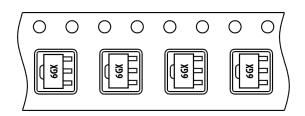

### **Component Image**

#### Notes:

Package marking provides orientation and identification "6G" = Device Code"

"X" = Month of manufacture

### **Features**

- Flat Gain 14dB +/-0.5dB, 40MHz to 2600MHz

- High linearity

- Built in temperature compensated internal bias circuitry

- No RF matching components required

- GaAs E-pHEMT Technology<sup>[1]</sup>

- Standard SOT89 package

- Single, Fixed 5V supply

- Excellent uniformity in product specifications

- MSL-2 and Lead-free halogen free

- High MTTF for base station application

### **Specifications**

- 900MHz; 5V, 104mA (typical)

- 14.3 dB Gain

- 43 dBm Output IP3

- 3.0 dB Noise Figure

- 22.3 dBm Output Power at 1dB gain compression

- 1950MHz, 5V, 104mA (typical)

- 14.6 dB Gain

- 40 dBm Output IP3

- 3.3 dB Noise Figure

- 22.5 dBm Output Power at 1dB gain compression

#### Note:

Enhancement mode technology employs positive gate voltage, thereby eliminating the need of negative gate voltage associated with conventional depletion mode devices.

Attention: Observe precautions for handling electrostatic sensitive devices.

ESD Machine Model = 75 V ESD Human Body Model = 450 V Refer to Avago Application Note A004R: Electrostatic Discharge, Damage and Control.

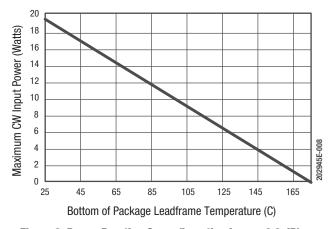

### Absolute Maximum Rating [2] $T_A=25$ °C

| Symbol              | Parameter                           | Units | Absolute Max. |

|---------------------|-------------------------------------|-------|---------------|

| V <sub>dd,max</sub> | Device Voltage, RF output to ground | V     | 5.5           |

| P <sub>in,max</sub> | CW RF Input Power                   | dBm   | 20            |

| P <sub>diss</sub>   | Total Power Dissipation [4]         | W     | 0.75          |

| T <sub>j, max</sub> | Junction Temperature                | °C    | 150           |

| T <sub>STG</sub>    | Storage Temperature                 | °C    | -65 to 150    |

# Thermal Resistance $^{[3]}$ $\theta_{jc}$ = 53.5°C/W (Vdd = 5V, Ids = 100mA, Tc = 85°C)

#### Note

- Operation of this device in excess of any of these limits may cause permanent damage.

- 3. Thermal resistance measured using Infrared measurement technique.

- 4. This is limited by maximum Vdd and lds. Derate 18.7 mW/°C for Tc>110°C.

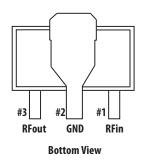

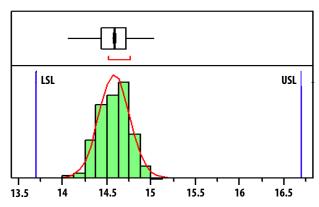

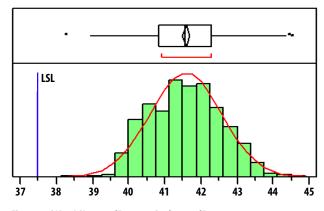

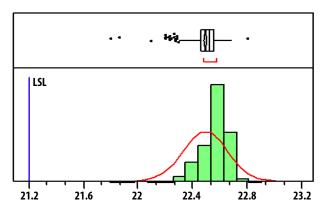

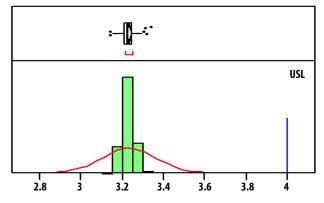

### **Product Consistency Distribution Charts**<sup>[5, 6]</sup>

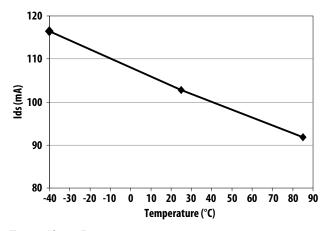

Figure 1. Ids, LSL=80mA, nominal=104mA, USL=125mA

Figure 2. Gain, LSL=13.7dB, nominal=14.6dB, USL=16.7dB

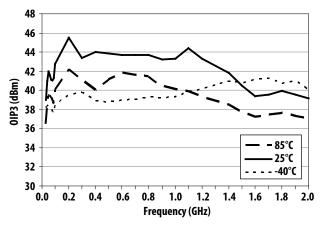

Figure 3. OIP3, LSL=37.5dBm, nominal=41.5dBm

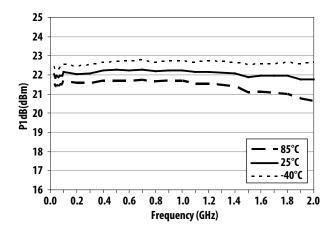

Figure 4. P1dB, LSL=21.2dBm, nominal=22.5dBm

Figure 5. NF, nominal=3.23dB, USL=4dB

#### Notes

- Distribution data sample size is 500 samples taken from 3 different wafer lots and 6 different wafers. Future wafers allocated to this product may have nominal values anywhere between the upper and lower limits.

- Measurements were made on a characterization test board, which represents a trade-off between optimal OIP3, gain and P1dB. Circuit trace losses have not been de-embedded from measurements above.

### Electrical Specifications [7]

$T_A = 25$ °C, Vdd = 5V

| Symbol   | Parameter and Test Condition         | Frequency | Units | Min.  | Тур. | Max. |

|----------|--------------------------------------|-----------|-------|-------|------|------|

| lds      | Quiescent current                    | N/A       | mA    | 80    | 104  | 125  |

| Gain     | Gain                                 | 40MHz     | dB    |       | 14.8 |      |

|          |                                      | 900MHz    |       |       | 14.3 |      |

|          |                                      | 1950MHz   |       | 13.7  | 14.6 | 16.7 |

| OIP3 [8] | Output Third Order Intercept Point   | 40MHz     | dBm   |       | 40   |      |

|          |                                      | 900MHz    |       |       | 43   |      |

|          |                                      | 1950MHz   |       | 37.5  | 40   | -    |

| NF       | Noise Figure                         | 40MHz     | dB    |       | 2.9  |      |

|          |                                      | 900MHz    |       |       | 3.0  |      |

|          |                                      | 1950MHz   |       | - 3.3 | 4    |      |

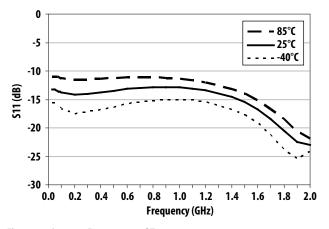

| S11      | Input Return Loss, $50\Omega$ source | 40MHz     | dB    |       | -13  |      |

|          |                                      | 900MHz    |       |       | -12  |      |

|          |                                      | 1950MHz   |       |       | -15  |      |

| S22      | Output Return Loss, 50Ω load         | 40MHz     | dB    |       | -18  |      |

|          |                                      | 900MHz    |       |       | -15  |      |

|          |                                      | 1950MHz   |       |       | -12  |      |

| S12      | Reverse Isolation                    | 40MHz     | dB    |       | -20  |      |

|          |                                      | 900MHz    |       |       | -22  |      |

|          |                                      | 1950MHz   |       |       | -25  |      |

| OP1dB    | Output Power at 1dB Gain Compression | 40MHz     | dBm   |       | 21.8 |      |

|          |                                      | 900MHz    |       |       | 22.4 |      |

|          |                                      | 1950MHz   |       | 21.2  | 22.5 | _    |

#### Notes:

<sup>7.</sup> Measurements obtained using demo board described in Figure 30 and 31. 40MHz data was taken with 40MHz – 2GHz Application Test Circuit, 900MHz data with 0.2GHz – 3GHz Application Test Circuit and 1.95GHz data with 1.5GHz – 2.6GHz Application Test Circuit respectively.

<sup>8.</sup> OIP3 test condition:  $F_{RF1} - F_{RF2} = 10 MHz$  with input power of -15dBm per tone measured at worse side band.

<sup>9.</sup> Use proper bias, heat sink and de-rating to ensure maximum channel temperature is not exceeded. See absolute maximum ratings and application note (if applicable) for more details.

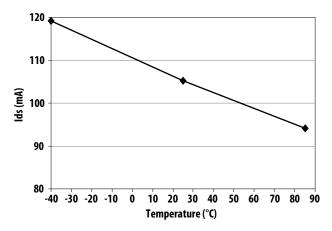

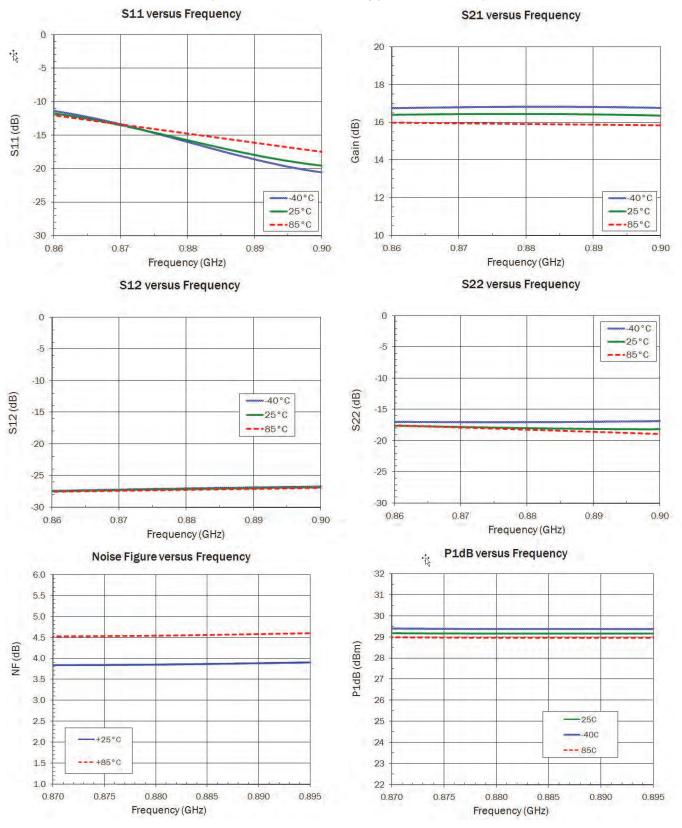

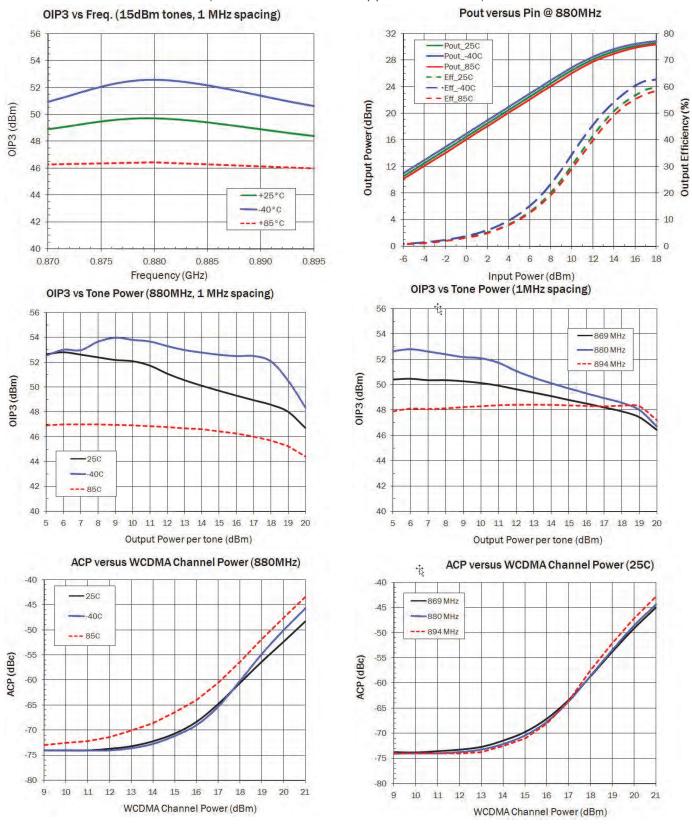

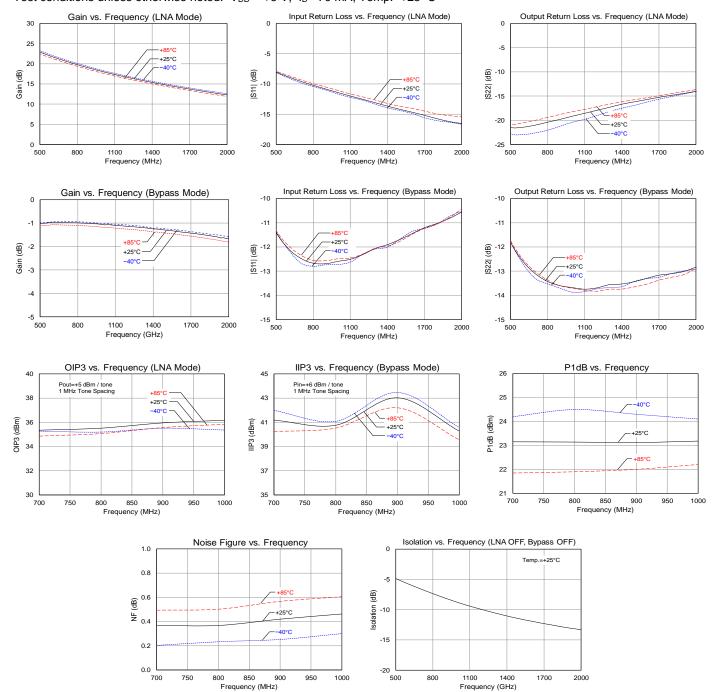

### Typical Performance (40MHz – 2GHz)

TA = +25°C, Vdd = 5V, Input Signal = CW. Application Test Circuit is shown in Figure 30 and Table 1.

16 15.5 15 14.5 Gain (dB) 14 13.5 13 − 85°C 12.5 - -40°C 12 0.0 0.2 0.4 1.0 1.2 1.4 1.6 1.8 Frequency (GHz)

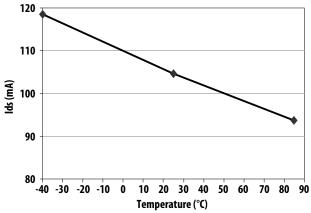

Figure 6. Ids over Temperature

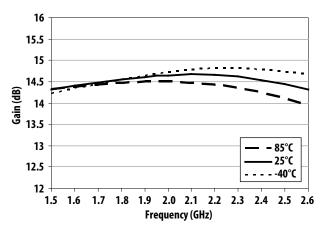

Figure 7. Gain over Frequency and Temperature

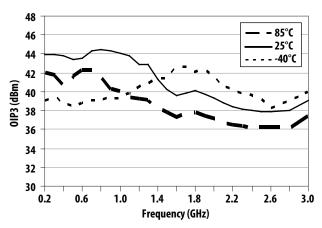

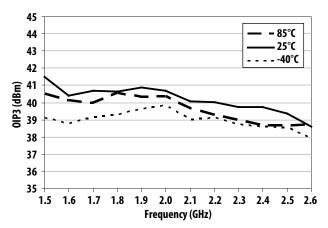

Figure 8. OIP3 over Frequency and Temperature

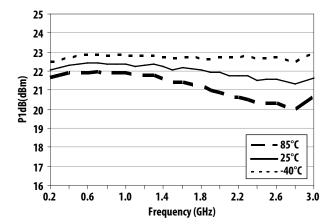

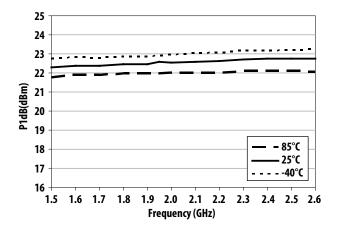

Figure 9. P1dB over Frequency and Temperature

### Typical Performance (40MHz - 2GHz)

TA = +25°C, Vdd = 5V, Input Signal = CW. Application Test Circuit is shown in Figure 30 and Table 1.

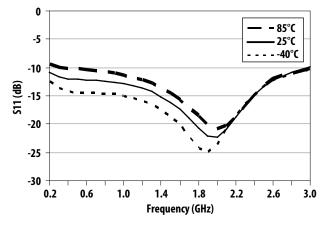

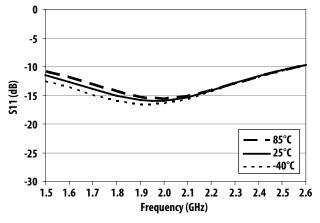

Figure 10. S11 over Frequency and Temperature

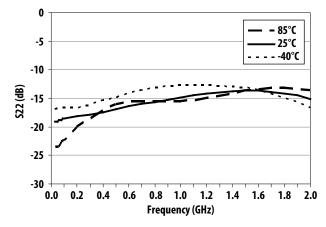

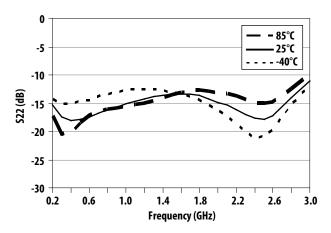

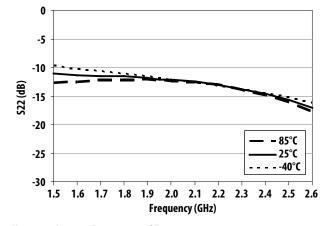

Figure 11. S22 over Frequency and Temperature

6.0

– 85°C 5.5 25°C 5.0 - - - - -40°C 4.5 NF(dB) 4.0 3.5 3.0 2.5 2.0 0.0 0.2 0.4 0.6 0.8 1.0 1.6 1.8 2.0 1.2 Frequency (GHz)

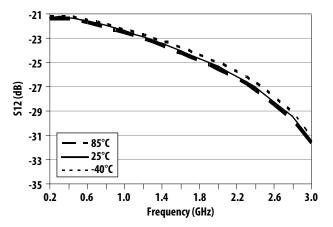

Figure 12. S12 over Frequency and Temperature

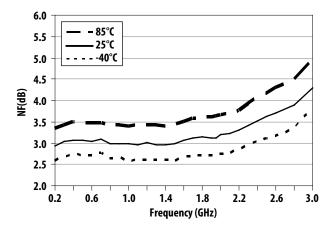

Figure 13. Noise Figure over Frequency and Temperature

### Typical Performance (0.2GHz - 3GHz)

TA = +25°C, Vdd = 5V, Input Signal = CW. Application Test Circuit is shown in Figure 30 and Table 2.

Figure 14. lds over Temperature

Figure 15. Gain over Frequency and Temperature

Figure 16. OIP3 over Frequency and Temperature

Figure 17. P1dB over Frequency and Temperature

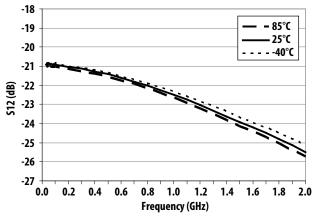

### Typical Performance (0.2GHz - 3GHz)

TA = +25°C, Vdd = 5V, Input Signal = CW. Application Test Circuit is shown in Figure 30 and Table 2.

Figure 18. S11 over Frequency and Temperature

Figure 19. S22 over Frequency and Temperature

Figure 20. S12 over Frequency and Temperature

Figure 21. Noise Figure over Frequency and Temperature

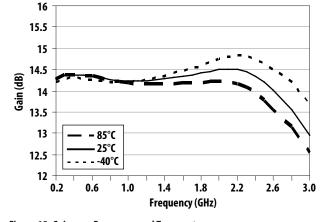

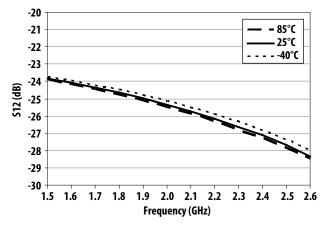

### Typical Performance (1.5GHz – 2.6GHz)

TA = +25°C, Vdd = 5V, Input Signal = CW. Application Test Circuit is shown in Figure 30 and Table 3.

Figure 22. Ids over Temperature

Figure 23. Gain over Frequency and Temperature

Figure 24. OIP3 over Frequency and Temperature

Figure 25. P1dB over Frequency and Temperature

### Typical Performance (1.5GHz – 2.6GHz)

TA = +25°C, Vdd = 5V, Input Signal = CW. Application Test Circuit is shown in Figure 30 and Table 3.

Figure 26. S11 over Frequency and Temperature

Figure 27. S22 over Frequency and Temperature

6.0

5.5

5.0

4.5

4.0

3.5

3.0

2.5

1.5 1.6 1.7 1.8 1.9 2.0 2.1 2.2 2.3 2.4 2.5 2.6

Frequency (GHz)

Figure 28. S12 over Frequency and Temperature

Figure 29. Noise Figure over Frequency and Temperature

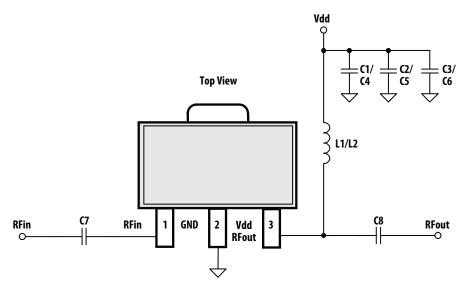

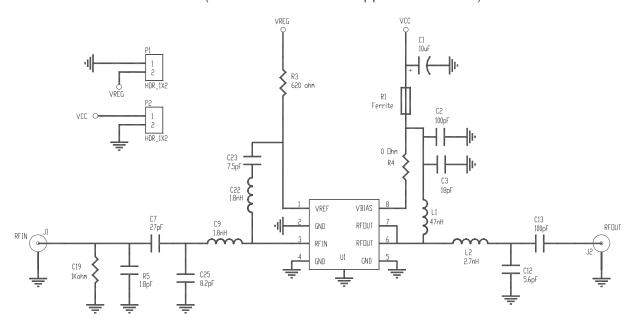

### **Application Schematic Components Table and Demo Board**

Figure 30. Application Schematic

- Recommended PCB material is 10 mils Rogers RO4350, with FR4 backing for mechanical strength.

- Suggested component values may vary according to layout and PCB material.

Figure 31. Demo board Layout

## **Demo board Part List**

Table 1. 40 MHz – 2 GHz Application Schematic Components

| Circuit Symbol | Size | Value | Part Number                 | Description              |

|----------------|------|-------|-----------------------------|--------------------------|

| L2             | 0805 | 820nH | LLQ2012-series (Toko)       | Wire Wound Chip Inductor |

| C4             | 0402 | 100pF | GRM1555C1H101JZ01B (Murata) | Ceramic Chip Capacitor   |

| C5             | 0402 | 0.1uF | GRM155R71C104KA88D (Murata) | Ceramic Chip Capacitor   |

| C6             | 0805 | 2.2uF | GRM21BR61E225KA12L (Murata) | Ceramic Chip Capacitor   |

| C7             | 0402 | 0.1uF | GRM155R71C104KA88D (Murata) | Ceramic Chip Capacitor   |

| C8             | 0402 | 0.1uF | GRM155R71C104KA88D (Murata) | Ceramic Chip Capacitor   |

Table 2. 0.2 GHz – 3 GHz Application Schematic Components

| Circuit Symbol | Size | Value | Part Number                 | Description            |

|----------------|------|-------|-----------------------------|------------------------|

| L1             | 0402 | 100nH | LL1005-FHLR10J (Toko)       | MLC Inductor           |

| C1             | 0402 | 10pF  | GRM1555C1H100JZ01B (Murata) | Ceramic Chip Capacitor |

| C2             | 0402 | 0.1uF | GRM155R71C104KA88D (Murata) | Ceramic Chip Capacitor |

| C3             | 0805 | 2.2uF | GRM21BR61E225KA12L (Murata) | Ceramic Chip Capacitor |

| C7             | 0402 | 100pF | GRM1555C1H101JZ01B (Murata) | Ceramic Chip Capacitor |

| C8             | 0402 | 100pF | GRM1555C1H101JZ01B (Murata) | Ceramic Chip Capacitor |

Table 3. 1.5 GHz – 2.6 GHz Application Schematic Components

| Circuit Symbol | Size | Value | Part Number                 | Description            |

|----------------|------|-------|-----------------------------|------------------------|

| L1             | 0402 | 5.6nH | LL1005-FHL5N6S (Toko)       | MLC Inductor           |

| C1             | 0402 | 100pF | GRM1555C1H101JZ01B (Murata) | Ceramic Chip Capacitor |

| C2             | 0402 | 0.1uF | GRM155R71C104KA88D (Murata) | Ceramic Chip Capacitor |

| C3             | 0805 | 2.2uF | GRM21BR61E225KA12L (Murata) | Ceramic Chip Capacitor |

| C7             | 0402 | 20pF  | GRM1555C1H200JZ01B (Murata) | Ceramic Chip Capacitor |

| C8             | 0402 | 20pF  | GRM1555C1H200JZ01B (Murata) | Ceramic Chip Capacitor |

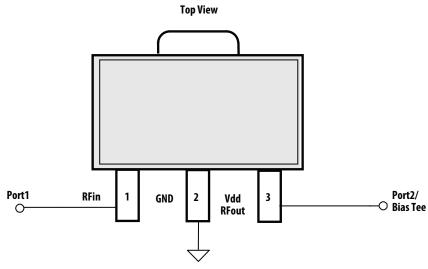

# **Test Circuit for S-Parameter and Noise Parameter**

Figure 32. S-parameter and Noise parameter test circuit

Typical S-Parameter (Vdd=5V, T=25°C, 50 ohm)

| Freq<br>(GHz) | S11<br>(dB) | S11<br>(ang) | S21<br>(dB) | S21<br>(ang) | S12<br>(dB) | S12<br>(ang) | S22<br>(dB) | S22<br>(ang) |

|---------------|-------------|--------------|-------------|--------------|-------------|--------------|-------------|--------------|

| 0.04          | -12.99      | -32.00       | 15.06       | 168.04       | -20.92      | 5.28         | -16.84      | -127.51      |

| 0.1           | -14.08      | -27.40       | 14.79       | 169.90       | -20.96      | -2.48        | -19.24      | -154.22      |

| 0.2           | -14.01      | -38.85       | 14.76       | 165.35       | -21.03      | -8.75        | -19.58      | -162.15      |

| 0.3           | -13.91      | -53.66       | 14.74       | 159.56       | -21.12      | -14.11       | -19.26      | -164.02      |

| 0.4           | -13.77      | -68.63       | 14.73       | 153.53       | -21.22      | -19.09       | -18.74      | -163.03      |

| 0.5           | -13.35      | -83.56       | 14.73       | 147.37       | -21.33      | -23.96       | -18.11      | -160.98      |

| 0.6           | -13.00      | -97.71       | 14.73       | 141.14       | -21.47      | -28.71       | -17.39      | -160.35      |

| 0.7           | -12.72      | -111.41      | 14.73       | 134.86       | -21.62      | -33.44       | -16.68      | -161.36      |

| 0.8           | -12.52      | -124.63      | 14.74       | 128.51       | -21.80      | -38.09       | -16.06      | -163.41      |

| 0.9           | -12.39      | -137.62      | 14.76       | 122.08       | -22.00      | -42.67       | -15.52      | -166.34      |

| 1             | -12.34      | -150.05      | 14.78       | 115.62       | -22.22      | -47.13       | -15.24      | -169.82      |

| 1.1           | -12.41      | -161.87      | 14.82       | 109.17       | -22.44      | -51.53       | -15.28      | -173.97      |

| 1.2           | -12.54      | -175.41      | 14.84       | 102.50       | -22.70      | -55.82       | -14.89      | -179.03      |

| 1.3           | -12.69      | 170.65       | 14.85       | 95.82        | -22.99      | -60.06       | -14.57      | 175.40       |

| 1.4           | -12.82      | 156.26       | 14.87       | 89.03        | -23.31      | -64.12       | -14.31      | 169.62       |

| 1.5           | -12.93      | 141.66       | 14.88       | 82.19        | -23.64      | -68.01       | -14.12      | 163.81       |

| 1.6           | -13.01      | 126.78       | 14.89       | 75.26        | -23.99      | -71.72       | -14.00      | 157.96       |

| 1.7           | -13.03      | 111.68       | 14.90       | 68.25        | -24.35      | -75.22       | -13.93      | 152.01       |

| 1.8           | -13.01      | 96.50        | 14.90       | 61.16        | -24.71      | -78.44       | -13.94      | 146.11       |

| 1.9           | -12.95      | 81.20        | 14.90       | 53.95        | -25.07      | -81.61       | -14.00      | 140.34       |

| 2             | -12.88      | 65.77        | 14.90       | 46.65        | -25.43      | -84.49       | -14.15      | 134.63       |

| 2.1           | -12.81      | 50.14        | 14.89       | 39.20        | -25.77      | -87.34       | -14.40      | 129.04       |

| 2.2           | -12.70      | 34.17        | 14.87       | 31.61        | -26.12      | -90.10       | -14.76      | 123.74       |

| 2.3           | -12.58      | 17.76        | 14.83       | 23.90        | -26.47      | -92.75       | -15.29      | 118.58       |

| 2.4           | -12.41      | 0.95         | 14.78       | 16.00        | -26.81      | -95.33       | -16.00      | 113.77       |

| 2.5           | -12.16      | -16.14       | 14.71       | 7.96         | -27.17      | -98.00       | -16.96      | 109.37       |

| 2.6           | -11.80      | -33.20       | 14.61       | -0.24        | -27.55      | -100.74      | -18.30      | 105.50       |

| 2.7           | -11.33      | -49.82       | 14.49       | -8.55        | -28.00      | -103.33      | -20.25      | 102.35       |

| 2.8           | -10.76      | -65.59       | 14.34       | -17.05       | -28.53      | -105.61      | -23.31      | 101.97       |

| 2.9           | -10.13      | -80.17       | 14.15       | -25.68       | -29.14      | -107.36      | -28.97      | 113.12       |

| 3             | -9.48       | -93.20       | 13.93       | -34.41       | -29.83      | -107.91      | -32.62      | -162.21      |

| 4             | -4.21       | -168.28      | 7.93        | -120.56      | -27.04      | -106.92      | -5.05       | 172.01       |

| 5             | -3.59       | 147.25       | 0.81        | -166.87      | -26.54      | -152.31      | -5.03       | 119.44       |

| 5             | -3.85       | 96.49        | -4.08       | 149.56       | -27.32      | 163.02       | -5.99       | 64.27        |

| 7             | -2.69       | 44.14        | -9.83       | 107.31       | -29.75      | 120.51       | -4.59       | 18.14        |

| 3             | -1.77       | 16.03        | -14.96      | 78.14        | -31.67      | 91.43        | -3.79       | -4.64        |

| 9             | -1.75       | -9.43        | -17.88      | 50.07        | -31.40      | 63.78        | -4.06       | -28.88       |

| 10            | -1.78       | -50.02       | -20.61      | 13.00        | -31.03      | 27.56        | -3.96       | -68.59       |

| 11            | -1.13       | -83.66       | -24.77      | -17.84       | -32.33      | -2.54        | -2.84       | -99.28       |

| 12            | -0.68       | -93.53       | -27.85      | -31.54       | -32.97      | -16.55       | -2.41       | -112.27      |

| 13            | -0.60       | -96.96       | -28.26      | -42.20       | -31.56      | -29.12       | -3.06       | -124.68      |

| 14            | -0.75       | -111.43      | -27.18      | -66.26       | -29.27      | -55.40       | -5.12       | -151.90      |

| 15            | -0.78       | -137.85      | -27.02      | -107.10      | -28.39      | -98.30       | -10.11      | 172.41       |

| 16            | -0.60       | -158.35      | -29.80      | -158.40      | -30.72      | -150.20      | -13.09      | -114.20      |

| 17            | -0.46       | -169.66      | -36.11      | 159.22       | -36.78      | 166.86       | -4.23       | -127.84      |

| 18            | -0.46       | -177.82      | -41.41      | 126.91       | -42.05      | 133.28       | -4.23       | -147.29      |

|               | -0.46       |              | -41.41      | 81.20        | -42.03      | 83.71        | -2.40       |              |

| 19            |             | 173.41       |             |              |             |              |             | -162.89      |

| 20            | -0.76       | 158.69       | -40.61      | 50.84        | -41.28      | 51.14        | -2.26       | -173.39      |

# Typical Noise Parameters (Vdd=5V, T=25°C, 50 ohm)

| Freq (GHz) | Fmin (dB) | $\Gamma_{opt}$ Mag | $\Gamma_{ m opt}$ Ang | Rn/Z0 |

|------------|-----------|--------------------|-----------------------|-------|

| 0.4        | 3.04      | 0.203              | 13.20                 | 0.522 |

| 0.9        | 2.80      | 0.205              | 14.50                 | 0.466 |

| 1.0        | 2.87      | 0.208              | 16.30                 | 0.468 |

| 1.7        | 2.82      | 0.211              | 19.80                 | 0.496 |

| 1.85       | 2.81      | 0.214              | 20.80                 | 0.512 |

| 2.0        | 2.83      | 0.217              | 26.10                 | 0.526 |

| 2.5        | 3.05      | 0.280              | 51.60                 | 0.59  |

| 3.0        | 3.84      | 0.356              | 95.30                 | 0.596 |

| 3.5        | 4.27      | 0.468              | 142.00                | 0.362 |

| 4.0        | 5.18      | 0.537              | 174.50                | 0.234 |

| 4.5        | 5.20      | 0.522              | -163.90               | 0.29  |

| 5.0        | 6.16      | 0.534              | -142.24               | 0.618 |

|            |           |                    |                       |       |

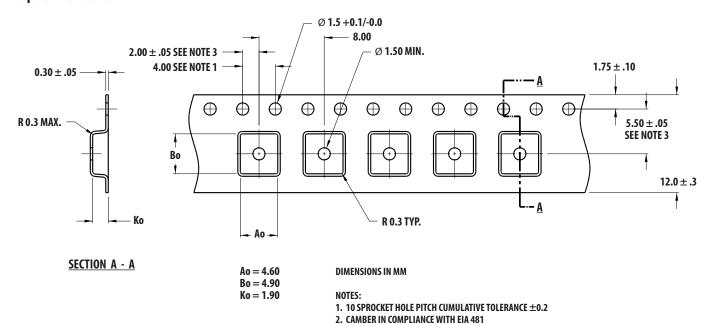

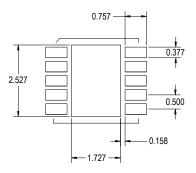

# **SOT89 Package Dimensions**

b1

|         | Di      | mensions in n | nm      | Dim     | nensions in inc | thes    |

|---------|---------|---------------|---------|---------|-----------------|---------|

| Symbols | Minimum | Nominal       | Maximum | Minimum | Nominal         | Maximum |

| A       | 1.40    | 1.50          | 1.60    | 0.055   | 0.059           | 0.063   |

| L       | 0.89    | 1.04          | 1.20    | 0.0350  | 0.041           | 0.047   |

| b       | 0.36    | 0.42          | 0.48    | 0.014   | 0.016           | 0.018   |

| b1      | 0.41    | 0.47          | 0.53    | 0.016   | 0.018           | 0.030   |

| С       | 0.38    | 0.40          | 0.43    | 0.014   | 0.015           | 0.017   |

| D       | 4.40    | 4.50          | 4.60    | 0.173   | 0.177           | 0.181   |

| D1      | 1.40    | 1.60          | 1.75    | 0.055   | 0.062           | 0.069   |

| D2      | 1.45    | 1.65          | 1.80    | 0.055   | 0.062           | 0.069   |

| Е       | 3.94    | -             | 4.25    | 0.155   | -               | 0.167   |

| E1      | 2.40    | 2.50          | 2.60    | 0.094   | 0.098           | 0.102   |

| e1      | 2.90    | 3.00          | 3.10    | 0.114   | 0.118           | 0.122   |

| S       | 0.65    | 0.75          | 0.85    | 0.026   | 0.030           | 0.034   |

| е       | 1.40    | 1.50          | 1.60    | 0.054   | 0.059           | 0.063   |

## **Part Number Ordering Information**

| Part Number    | No. of Devices | Container     |  |

|----------------|----------------|---------------|--|

| MGA-30689-BLKG | 100            | 7" Tape/Reel  |  |

| MGA-30689-TR1G | 3000           | 13" Tape/Reel |  |

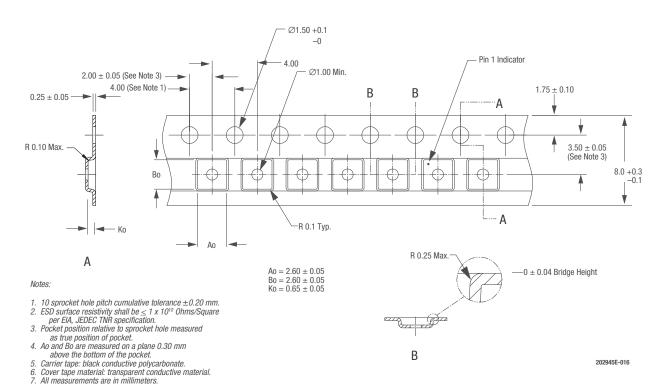

## **Device Orientation**

3. POCKET POSITION RELATIVE TO SPROCKET HOLE MEASURED AS TRUE POSITION OF POCKET, NOT POCKET HOLE

# **Tape Dimensions**

15

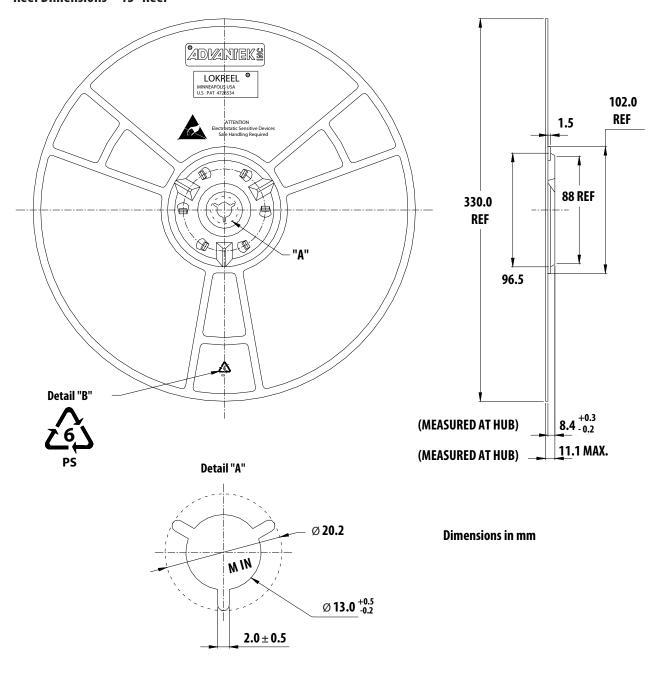

## Reel Dimensions - 13" Reel

For product information and a complete list of distributors, please go to our web site: **www.avagotech.com**

WHEN TIMING IS OF THE ESSENCE

#### **Features**

Operational Voltage: 2.5, 3.3V ±5%

0.6pS Jitter (max.)

Voltage Controlled

Enable/Disable function

CMOS, LVDS, LVPECL Output

RoHS Compliant Product

# Programmable Crystal Oscillator CMOS, LVDS, LVPECL Output

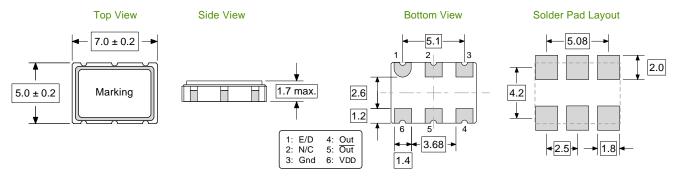

$5.0\,x\,7.0\,x\,1.7mm$  Ceramic (6 pad) SMD

10MHz ~ 1.5GHz

# **Outlines & Dimensions (mm)**

# **Electrical Specifications**

| Waveform Output                     | HCMOS                 | LVDS                                                   | LVPECL   |  |  |  |

|-------------------------------------|-----------------------|--------------------------------------------------------|----------|--|--|--|

| Frequency                           | 10MHz to 250MHz       | 10MHz to 1.5GHz                                        |          |  |  |  |

| Mode of Oscillation                 |                       | Fundamental                                            |          |  |  |  |

| Supply Voltage                      |                       | 2.5V, 3.3V                                             |          |  |  |  |

| Frequency Stability vs. Temp. Range |                       | ±50ppm                                                 |          |  |  |  |

| Input Current                       | 40mA                  | 30mA                                                   | 70mA     |  |  |  |

| Rise/Fall Time                      | 4nS                   | 600pS                                                  |          |  |  |  |

| Phase Jitter                        |                       | 0.6pS (max.)                                           |          |  |  |  |

| Duty Cycle                          |                       | 45/55%                                                 |          |  |  |  |

| Start-up Time                       |                       | 10mS (Max.)                                            |          |  |  |  |

| Enable/Disable Input Voltage        | V <sub>IH</sub> ≥ 0.7 | <sub>DD</sub> or No Connect, $V_{IL} \le 0.3 V_{DD}$ o | r Ground |  |  |  |

| Output Load                         | 15pF                  | 100Ω                                                   | 50Ω      |  |  |  |

| Aging/year                          | ±3.0ppm (Max.)        |                                                        |          |  |  |  |

| Operating Temp. Range               | 0 ~ +70°C             |                                                        |          |  |  |  |

| Storage Temp. Range                 |                       | -40 ~ +125°C                                           |          |  |  |  |

# **Numbering Guide**

Example: O75P2-622.0000M3T2MAE

| Series | Frequency                          | Supply Voltage              | Tri-state                                  | Freq. Stability                                | Oper. Temp.                                                | Waveform                            |

|--------|------------------------------------|-----------------------------|--------------------------------------------|------------------------------------------------|------------------------------------------------------------|-------------------------------------|

| O75P2  | xxx.xxxxM = MHz<br>xxx.xxxxG = GHz | 2 = 2.5V<br><b>3</b> = 3.3V | T1 = Pin 1<br>T2 = Pin 2<br>N = No Connect | L = ±25ppm<br><b>M</b> = ±50ppm<br>N = ±100ppm | <b>A</b> = -40 ~ +85°C<br>B = -20 ~ +70°C<br>C = 0 ~ +70°C | C = HCMOS<br>D = LVDS<br>E = LVPECL |

# **Monolithic Amplifier**

**PGA-103+**

**50**Ω 0.05 to 4 GHz

# **The Big Deal**

- Ultra High IP3

- · Broadband High Dynamic Range

- May be used as a replacement for RFMD SPF-5189Z<sup>a,b</sup>

# **Product Overview**

PGA-103+ (RoHS compliant) is an advanced wideband amplifier fabricated using E-PHEMT technology and offers extremely high dynamic range over a broad frequency range and with low noise figure. In addition, the PGA-103+ has good input and output return loss over a broad frequency range without the need for external matching components and has demonstrated excellent reliability. Lead finish is SnAgNi. It has repeatable performance from lot to lot and is enclosed in a SOT-89 package for very good thermal performance.

# **Key Features**

| Feature                                                                                                            | Advantages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Broad Band: 0.05 to 4.0 GHz                                                                                        | Broadband covering primary wireless communications bands:<br>Cellular, PCS, LTE, WiMAX                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Ultra High IP3<br>Versus DC power Consumption:<br>45 dBm typical at 2 GHz at +5.0V<br>Supply Voltage and only 97mA | The PGA-103+ provides excellent IP3 performance relative to device size and power consumption. The combination of the design and E-PHEMT Structure provides enhanced linearity over a broad frequency range as evidence in the IP3 being typically 20 dB above the P 1dB point. This feature makes this amplifier ideal for use in:  • Driver amplifiers for complex waveform up converter paths  • Drivers in linearized transmit systems  • Secondary amplifiers in ultra High Dynamic range receivers |

| Low Noise Figure:<br>0.6 dB up to 1.0 GHz                                                                          | A unique feature of the PGA-103+ which separates this design from all competitors is the low noise figure performance in combination with the high dynamic range.                                                                                                                                                                                                                                                                                                                                        |

#### Notes

a. Suitability for model replacement within a particular system must be determined by and is solely the responsibility of the customer based on, among other things, electrical performance criteria, stimulus conditions, application, compatibility with other components and environmental conditions and stresses.

b. The RFMD SPF-5189Z part number is used for identification and comparison purposes only.

A. Performance and quality attributes and conditions not expressly stated in this specification document are intended to be excluded and do not form a part of this specification document.

B. Electrical specifications and performance data contained in this specification document are based on Mini-Circuit's applicable established test performance criteria and measurement instructions.

C. The parts covered by this specification document are subject to Mini-Circuits standard limited warranty and terms and conditions (collectively, "Standard Terms"); Purchasers of this part are entitled to the rights and benefits contained therein. For a full statement of the Standard Terms and the exclusive rights and remedies thereunder, please visit Mini-Circuits' website at www.minicircuits.com/MCLStore/terms.jsp

# **Monolithic Amplifier**

0.05-4 GHz

#### **Product Features**

- 5V/3V operation

- High IP3, 45 dBm typ. at 2 GHz, Vd=5V

- Low Noise Figure, 0.6 at 1 GHz; 0.9 dB at 2 GHz

- Gain, 11.0 dB typ. at 2 GHz

- P1dB 22.5 dBm typ. at 2 GHz at Vd=5V

- Protected under US Patent 8,803,612

CASE STYLE: DE782

+RoHS Compliant The +Suffix identifies RoHS Compliance. See our web site for RoHS Compliance methodologies and qualifications

# **Typical Applications**

- Base station infrastructure

- Portable Wireless

- CATV & DBS

- MMDS & Wireless LAN

- LTE

# **General Description**

PGA-103+ (RoHS compliant) is an advanced wideband amplifier fabricated using E-PHEMT technology and offers extremely high dynamic range over a broad frequency range and with low noise figure. In addition, the PGA-103+ has good input and output return loss over a broad frequency range without the need for external matching components. Lead finish is SnAqNi. It has repeatable performance from lot to lot and is enclosed in a SOT-89 package for very good thermal performance.

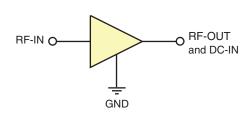

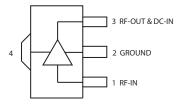

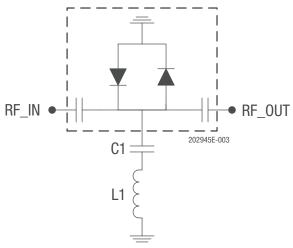

#### simplified schematic and pin description

| Function         | Pin Number | Description                                                                                                                                                                                                                                                                       |

|------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RF IN            | 1          | RF input pin. This pin requires the use of an external DC blocking capacitor chosen for the frequency of operation.                                                                                                                                                               |

| RF-OUT and DC-IN | 3          | RF output and bias pin. DC voltage is present on this pin; therefore a DC blocking capacitor is necessary for proper operation. An RF choke is needed to feed DC bias without loss of RF signal due to the bias connection, as shown in "Recommended Application Circuit", Fig. 2 |

| GND              | 2,4        | Connections to ground. Use via holes as shown in "Suggested Layout for PCB Design" to reduce ground path inductance for best performance.                                                                                                                                         |

a. Suitability for model replacement within a particular system must be determined by and is solely the responsibility of the customer based on, among other things, electrical performance criteria, stimulus conditions, application, compatibility with other components and environmental conditions and stresses. b. The RFMD SPF-5189Z part number is used for identification and comparison purposes only.

Notes

A. Performance and quality attributes and conditions not expressly stated in this specification document are intended to be excluded and do not form a part of this specification document.

B. Electrical specifications and performance data contained in this specification document are based on Mini-Circuit's applicable established test performance criteria and measurement instructions.

C. The parts covered by this specification document are subject to Mini-Circuits standard limited warranty and terms and conditions (collectively, "Standard Terms"); Purchasers of this part are entitled to the rights and benefits contained therein. For a full statement of the Standard Terms and the exclusive rights and remedies thereunder, please visit Mini-Circuits' website at www.minicircuits.com/MCLStore/terms.jsp

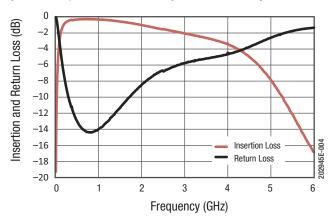

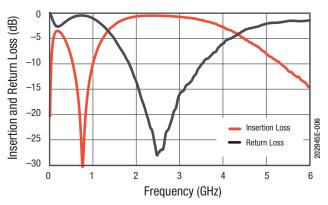

Electrical Specifications<sup>(1)</sup> at 25°C, 50Ω, unless noted

| Parameter                                     | Condition |      | Vd=5V |      | Vd=3V |       |

|-----------------------------------------------|-----------|------|-------|------|-------|-------|

|                                               | (GHz)     | Min. | Тур.  | Max. | Тур.  | Units |

| Frequency Range                               |           | 0.05 |       | 4.0  |       | GHz   |

| Gain                                          | 0.05      | _    | 26.5  | _    | 25.9  | dB    |

|                                               | 0.4       | _    | 22.1  | _    | 21.6  |       |

|                                               | 1.0       | 14.7 | 16.2  | 18.0 | 15.8  |       |

|                                               | 2.0       | _    | 11.0  | _    | 10.6  |       |

|                                               | 3.0       | _    | 8.1   | _    | 7.7   |       |

|                                               | 4.0       | _    | 6.2   | _    | 5.9   |       |

| Noise Figure                                  | 0.05      |      | 0.5   |      | 0.5   | dB    |

|                                               | 0.4       |      | 0.5   |      | 0.5   |       |

|                                               | 1.0       |      | 0.6   |      | 0.6   |       |

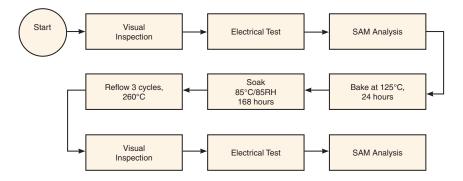

|                                               | 2.0       |      | 0.9   |      | 0.9   |       |