## TECHNICAL BULLETIN MODEL 192S

ELECTRONIC SYSTEMS TECHNOLOGY 415 N. QUAY STREET KENNEWICK, WA 99336 509-735-9092 (O) 509-783-5475 (FAX)

## **192S TECHNICAL AND OPERATIONAL DESCRIPTION**

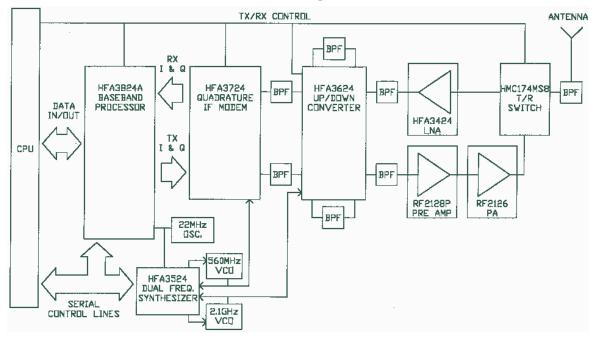

The ESTeem 192S is a Spread Spectrum Wireless Modem transceiver designed to receive and transmit RS-232 or RS-485 data (Figure 1). The data is formatted into RF packets and transmitted and received using a direct sequence modulation technique.

## Transmitter

The CPU receives data from the attached communication device, formats it into a packet and sends it to the baseband processor where a preamble and header are added to the data. The data is then scrambled and differentially encoded before being differential binary phase shift keying (DBPSK) modulated with a 11 chip barker sequence. The baseband processor outputs the signal to the Quadrature IF Modulator using DC coupled to fifth order Butterworth low pass filters, to provide shaping of the phase shift keyed (PSK) signal. After the signal is modulated on to the 280 MHz IF it passes through a SAW bandpass filter and into the up-converter where the 280 MHz is mixed with 2.12 GHz first LO to make the 2.4 GHz signal. The 2.4 GHz RF output passes through a two poll filter before being applied to the pre-amplifier and output amplifier. The 2.4 GHz RF signal then passes through the T/R switch and two pole bandpass filters before arriving at the antenna port. The maximum output power is +30 dBm.

## Receiver

The received signal passes through two, two pole bandpass filters and the T\R switch before being down converted from 2.4 GHz to 280 MHz. It then passes through a SAW band pass filter and enters the Quadrature IF Demodulator. The Demodulator provides two baseband low pass filters and a one pole LC differential filter. The demodulated signal is then sent to the base band processor. The base band processor correlates the PN (pseudo-noise) spreading to remove it and uncover the differential DBPSK. The DBPSK signal is then differential decoded and descrambled before being sent to the CPU. The CPU then sends the data out the communications port

Figure 1: 192S Block Diagram