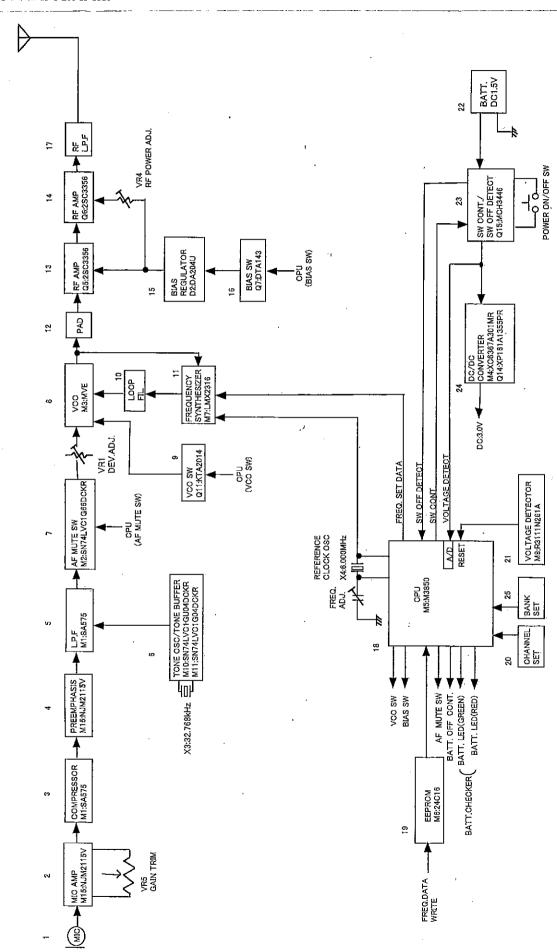

# 1. BLOCK DIAGRAM

# 2. CIRCUIT EXPLANATION

#### HOW EACH SECTION WORKS

We will explain operations of each section based on the block diagram.

### (1) MICROPHONE (Block diagram No. 1)

The microphone is a lavaliere microphone having an internal microphone of omnidirectional, electret condenser type.

Impedance: 1.5 kΩ

Sensitivity: -44 dB (1 kHz, 0 dB = 1 V/1 pa)

#### (2) MICROPHONE AMPLIFIER (2)

The microphone amplifier uses an OP amp (M15) and amplifies the signal from the microphone capsule to the level necessary for the compressor circuit. By changing the feedback amount, this microphone amplifier permits gain control of 15 dB.

### (3) COMPRESSOR (3)

The compander IC is SA575 (M1), and has a compressor circuitry and 2 OP amps. The compression ratio is 1/2 (logarithmic compression).

## (4) PRE-EMPHASIS (4)

Pre-emphasis is carried out to improve the system's S/N ratio. Amplifier (M15) is used as an OP amp. A time constant is 50 µsec.

# (5) LPF (5)

The third Butterworth type low-pass filter is constructed using the OP amp built in M1 to attenuate the audio signal components of over 15 kHz. Also, the harmonic components of the tone signal to be superimposed in the LPF circuit are attenuated by the low-pass filter.

### (6) MUTE SW (7)

Using the analog switch (M2), this circuit mutes both the audio and tone signals during the periods of from the power switch-on to the commencement of signal transmission and from power switch-off to transmission termination to operate the receiver tone squelch.

### (7) TONE OSC (6)

Consists of a quarts oscillator (X3) and an inverter (M10) and oscillates a signal for tone squelch (tone signal). The oscillation frequency is 32.768 kHz, and the output signal is taken out through a buffer (M11).

# (8) PLL FREQUENCY SYNTHESIZER (8, 10, 11)

VCO (M3), PLL IC (M7) and LOOP FILTER make up a phase locked loop. The VCO oscillates the transmission frequency directly and divides the output. It then compares the frequency phase by means of the 25 kHz comparison frequency, and outputs a pulse corresponding to the phase difference. The pulse is applied to the VCO as a control voltage after integrated at a loop filter, and then is locked to the set transmission frequency. Both the audio and tone signals are input from the VCO's modulation terminal, and then are frequency-modulated. The modulation method is a reactance modulation system using a variable capacitance diode.

### (9) RF AMP, RF POWER AMP (12,13, 14)

By amplifying the VCO's oscillation output with a transistor, these amplifiers not only make up for losses in a pad or RF LPF, but also gain the antenna power. The two-stage construction method is employed for the amplifiers to obtain sufficient buffer effects for the VCO, and about 6 dB pad is installed in the amplifier input. The output is less than 50 mW, and is adjusted by changing Q6's bias current using VR4 to change operation points.

### (10) BIAS REGULATOR, BIAS SWITCH (15, 16)

By compensating for the temperature by means of a diode (D2), the bias circuit suppresses the changes of operation points due to temperature variations. When the VCO's transmission frequency becomes stable after PLL lockup completion, the switch (Q7) turns on and the bias is applied for radio signal transmission.

### (11) RF LPF (17)

A 3-stage  $\pi$  type low-pass filter is used for the RF section's band limiting filter to suppress the spurious-radiated signals with frequencies much different from the transmission frequency.

### (12) CPU and its peripheral parts (18, 20, 21, 25)

This section is comprised of the CPU (M5), voltage detector (M8) and crystal-controlled reference oscillator (X4). The reference oscillator is 6.0 MHz in frequency, and is oscillated by the CPU's internal inverter to operate the CPU as a clock. At the same time, the 6 MHz signal is supplied to the PLL IC as the PLL reference oscillation frequency. The oscillation frequency is adjusted by TCI so that its deviation stays within ±1 kHz. After its power switch is set to the ON position, the CPU controls the transmission frequency setting, the start of transmission, actions till voice transmission, and actions when the system is switched off. The operating procedures are stored in the CPU's mask ROM, and the control contents are as follows:

- (A) The CPU reads transmission frequency setting data from both the Bank and Channel setting switches, and transmits data to PLL IC for the division ratio setting.

- (B) The CPU controls the bias circuitry and Q7 so that the radio signal is not transmitted until the transmission frequency becomes stable.

- (C) The CPU controls AF MUTE SW, VCO SW, BIAS SW, and BATT.CHECKER.

When the circuit voltage drops below 2.6 V, the voltage detector transmits a reset signal to the CPU to stop the CPU's operation so that no radio signal is transmitted.

#### (13) SW CONT./SW OFF DETECT (23)

Setting the power switch (SW2) to ON turns the FET (Q15) on, thereby activating the circuit. Then, the CPU starts up and controls Q15 to keep it active.

When the power switch is set to OFF, the CPU detects it, turns off the AF MUTE SW and then stops transmitting audio and tone signals. This causes the tone squelch of the receiver to operate. Subsequently, the VCO SW and BIAS SW are turned off, which then stops transmitting the radio signal. Finally, Q15 is turned off, deactivating all circuits.

# (14) DC/DC CONVERTER (24)

Consists of the oscillation control IC (M4), FET (Q14), and diode. This circuit raises the battery voltage to 3.0 V, and supplies the power to each circuit section.

### (15) BATT. CHECKER

Permits the state of battery consumption to indicate by means of red and green LEDs (D8, D9) to inform whether the battery needs to be replaced.

When the battery is full, only the green LED lights. As the battery voltage decreases due to the battery drain, the green LED dims gradually and in turn the red LED starts to light. Further voltage drop causes only the red LED to light, then to extinguish with the control CPU halt.

The recommended time of battery replacement is when the red LED starts lighting; the battery voltage is 1.05 V

An additional function is that the LED flashes when an incorrect bank or channel is set.

# (16) Frequency registration (19)

Transmission frequencies and their banks and channels are written in the EEPROM (M16), and the contents can be changed as required.