## Typical Applications

- Wireless Meter Reading

- Keyless Entry Systems

- 433/868/915MHz ISM Band Systems

- Wireless Data Transceiver

- Wireless Security Systems

- Battery Powered Portable Devices

## Product Description

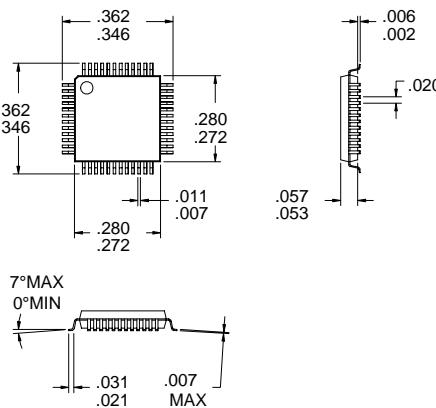

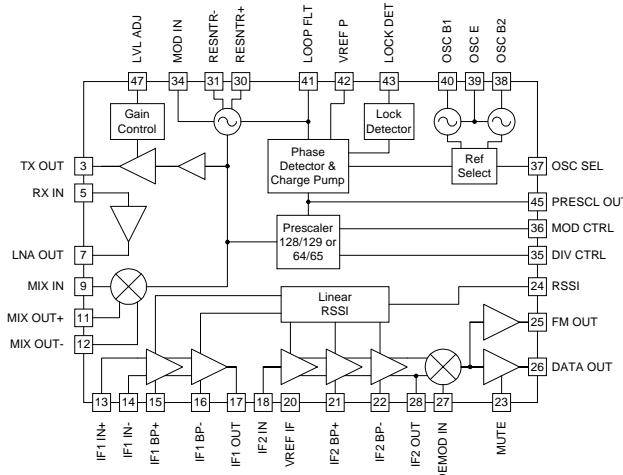

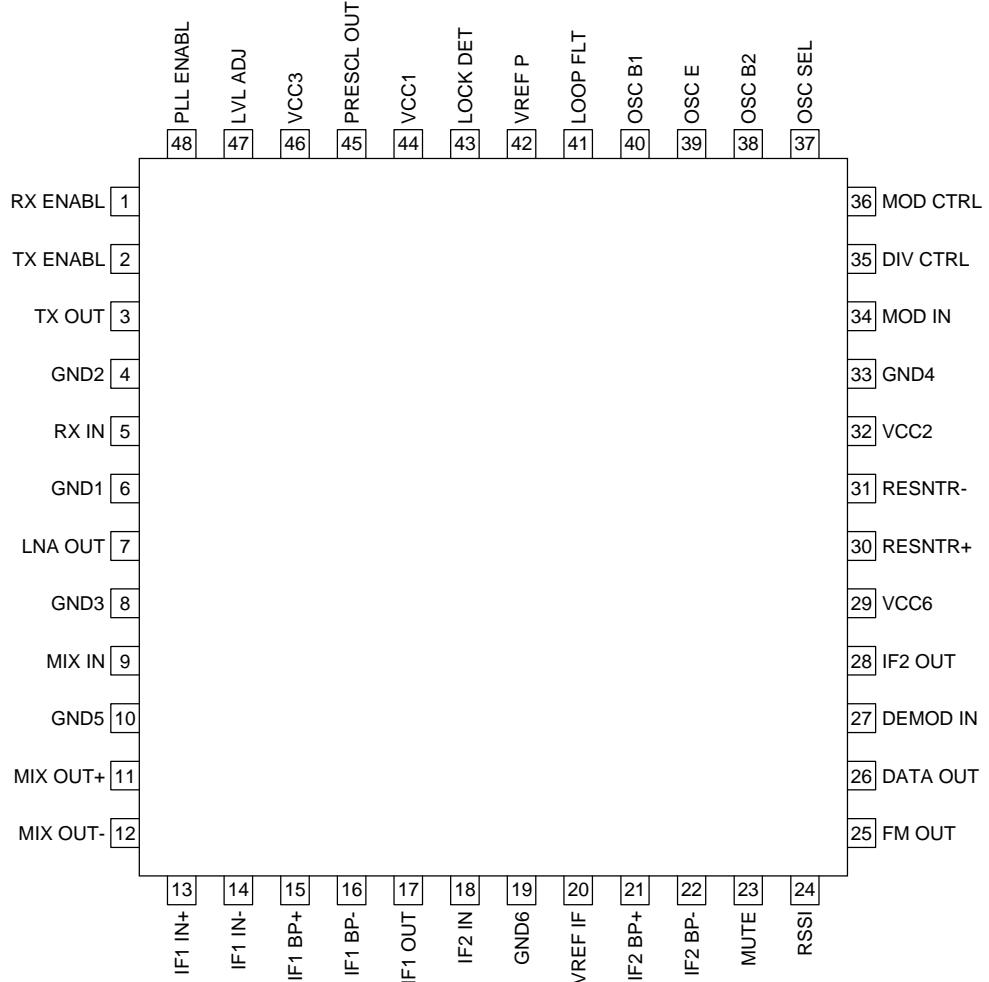

The RF2905 is a monolithic integrated circuit intended for use as a low cost FM transceiver. The device is provided in 48-lead plastic LQFP packaging and is designed to provide a fully functional FM transceiver. The chip is intended for linear (AM, FM) or digital (ASK, FSK, OOK) applications in the North American 915MHz ISM band and European 433MHz and 868MHz ISM bands. The integrated VCO, dual modulus/dual divide (128/129 or 64/65) prescaler, and reference oscillator require only the addition of an external crystal to provide a complete phase-locked oscillator.

## **Optimum Technology Matching® Applied**

Si BJT       GaAs HBT       GaAs MESFET

Si Bi-CMOS

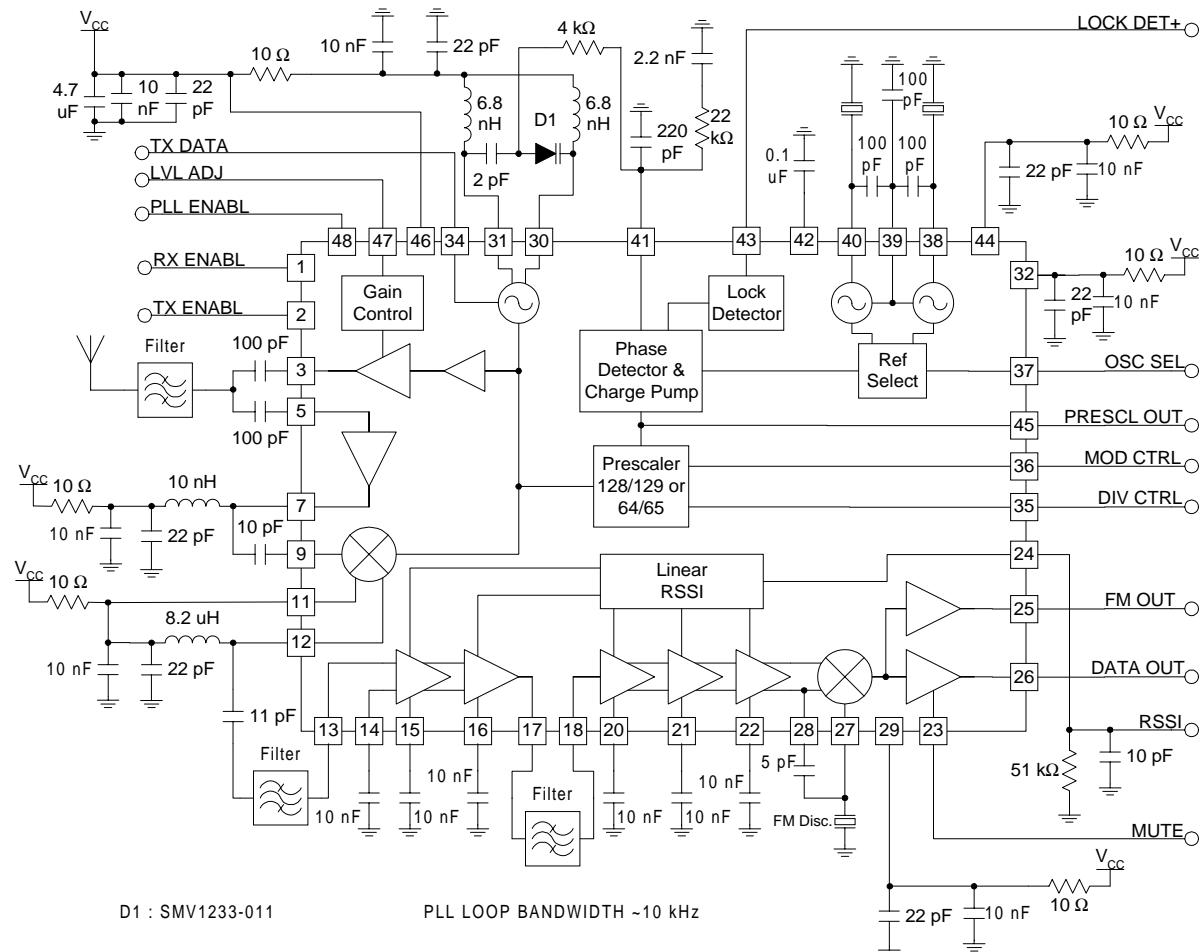

## Functional Block Diagram

#### **Package Style: LQFP-48**

## Features

- Fully Monolithic Integrated Transceiver

- 2.7V to 5.0V Supply Voltage

- Narrow Band and Wide Band FM/FSK

- 300MHz to 1000MHz Frequency Range

- 10dB Cascaded Noise Figure

- 10mW Output Power at 433MHz

## **Ordering Information**

|               |                                           |

|---------------|-------------------------------------------|

| RF2905        | 433/868/915MHz FM/FSK/ASK/OOK Transceiver |

| RF2905 PCBA-L | Fully Assembled Evaluation Board (433MHz) |

| RF2905 PCBA-M | Fully Assembled Evaluation Board (868MHz) |

| RF2905 PCBA-H | Fully Assembled Evaluation Board (915MHz) |

RF Micro Devices, Inc.

7625 Thorndike Road

Greensboro, NC 27409, USA

Tel (910) 664 1233

Fax (910) 664 0454

<http://www.rfmd.com>

## Absolute Maximum Ratings

| Parameter                     | Ratings      | Unit            |

|-------------------------------|--------------|-----------------|

| Supply Voltage                | -0.5 to +5.5 | V <sub>DC</sub> |

| Control Voltages              | -0.5 to +5.0 | V <sub>DC</sub> |

| Input RF Level                | +10          | dBm             |

| Output Load VSWR              | 50:1         |                 |

| Operating Ambient Temperature | -40 to +85   | °C              |

| Storage Temperature           | -40 to +150  | °C              |

Caution! ESD sensitive device.

RF Micro Devices believes the furnished information is correct and accurate at the time of this printing. However, RF Micro Devices reserves the right to make changes to its products without notice. RF Micro Devices does not assume responsibility for the use of the described product(s).

| Parameter                      | Specification    |                              |       | Unit   | Condition                                   |

|--------------------------------|------------------|------------------------------|-------|--------|---------------------------------------------|

|                                | Min.             | Typ.                         | Max.  |        |                                             |

| <b>Overall</b>                 |                  | 300 to 1000                  |       | MHz    | T=25 °C, V <sub>CC</sub> =3.6V, Freq=433MHz |

| RF Frequency Range             |                  |                              |       |        |                                             |

| <b>VCO and PLL Section</b>     |                  |                              |       |        |                                             |

| VCO Frequency Range            | 300 to 1000      |                              |       | MHz    |                                             |

| Prescaler divide ratio         | 64/65 or 128/129 |                              |       |        |                                             |

| Prescaler Output Impedance     | 50               |                              |       | Ω      |                                             |

| PLL Lock Time                  | 10               |                              |       | ms     |                                             |

| PLL Phase Noise                | -80              |                              |       | dBc/Hz |                                             |

| Reference Frequency            | TBD              | -100                         |       | dBc/Hz |                                             |

| Crystal R <sub>S</sub>         | 50               |                              | 17    | MHz    |                                             |

| Charge Pump Current            | -40              | 100                          | +40   | Ω      |                                             |

|                                |                  |                              |       | μA     |                                             |

| <b>Transmit Section</b>        |                  |                              |       |        |                                             |

| Max Modulation Frequency       | 2                |                              |       | MHz    |                                             |

| Min Modulation Frequency       |                  | Set by loop filter bandwidth |       |        |                                             |

| Maximum Power Level            | +7               | +10                          |       | dBm    |                                             |

|                                |                  | +3                           |       | dBm    |                                             |

| Power Control Range            | 12               | 10                           |       | dB     |                                             |

| Power Control Sensitivity      | 200              |                              |       | dB/V   |                                             |

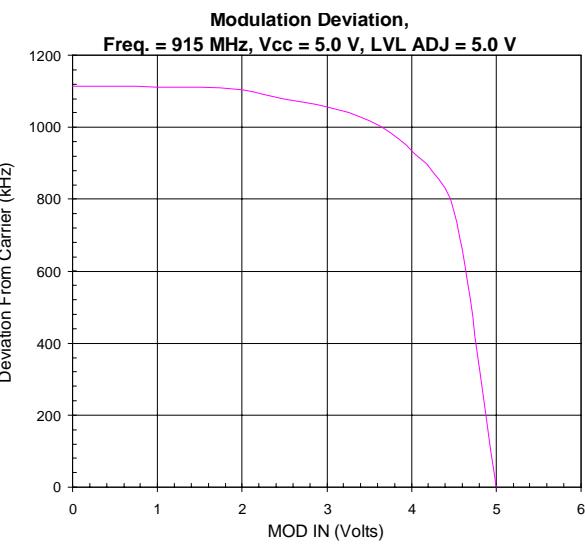

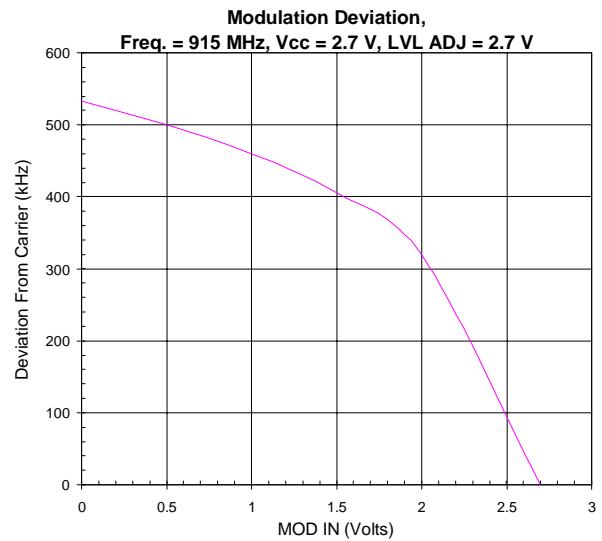

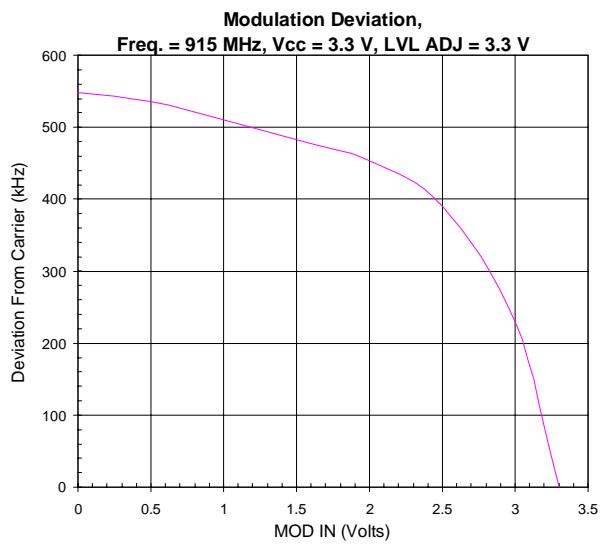

| Max FM Deviation               |                  |                              |       | kHz    |                                             |

| Antenna Port Impedance         |                  | 50                           |       | Ω      |                                             |

| Antenna Port Impedance         |                  | TBD                          |       | Ω      |                                             |

| Antenna Port VSWR              |                  |                              |       |        |                                             |

| Modulation Input Impedance     |                  |                              | 1.5:1 |        |                                             |

| Harmonics                      |                  | -23                          |       | κΩ     |                                             |

| Spurious                       |                  |                              |       | dBc    |                                             |

|                                |                  |                              |       | dBc    |                                             |

| <b>Overall Receive Section</b> |                  |                              |       |        |                                             |

| Frequency Range                | 300 to 1000      |                              |       | MHz    |                                             |

| Cascaded Voltage Gain          | 35               |                              |       | dB     |                                             |

|                                | 23               |                              |       | dB     |                                             |

| Cascaded Noise Figure          | 10               |                              |       | dB     |                                             |

| Cascaded Input IP <sub>3</sub> | -31              |                              |       | dBm    |                                             |

|                                | -26              |                              |       | dBm    |                                             |

| RX Sensitivity                 | -101             |                              |       | dBm    |                                             |

| LO Leakage                     |                  |                              |       | dBm    |                                             |

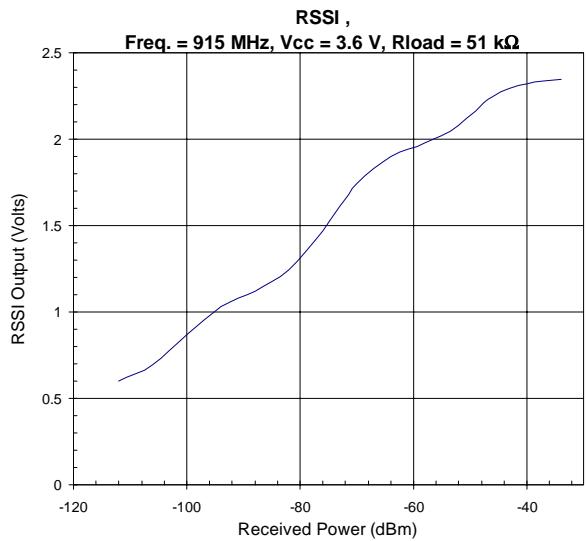

| RSSI DC Output Range           | 0.5 to 2.5       |                              |       | V      |                                             |

| RSSI Sensitivity               | 25               |                              |       | mV/dB  |                                             |

| RSSI Dynamic Range             | 70               | 80                           |       | dB     |                                             |

| <b>LNA</b>               |                |      |                      |                  |                                                                                                           |

|--------------------------|----------------|------|----------------------|------------------|-----------------------------------------------------------------------------------------------------------|

| Voltage Gain             |                | 23   |                      | dB               | 433MHz                                                                                                    |

|                          |                | 16   |                      | dB               | 915MHz                                                                                                    |

| Noise Figure             |                | 4.8  |                      | dB               | 433MHz                                                                                                    |

|                          |                | 5.5  |                      | dB               | 915MHz                                                                                                    |

| Input IP <sub>3</sub>    |                | -27  |                      | dBm              | 433MHz                                                                                                    |

|                          |                | -20  |                      | dBm              | 915MHz                                                                                                    |

| Input P <sub>1dB</sub>   |                | -37  |                      | dBm              | 433MHz                                                                                                    |

|                          |                | -30  |                      | dBm              | 915MHz                                                                                                    |

| Antenna Port Impedance   |                | 50   |                      | Ω                | RX ENABL="1"                                                                                              |

|                          | TBD            |      |                      | Ω                | RX ENABL="0"                                                                                              |

| Antenna Port VSWR        |                |      | 1.5:1                |                  | Freq=433MHz, RX Mode                                                                                      |

| Output Impedance         | Open Collector |      |                      | Ω                | 433MHz                                                                                                    |

|                          | Open Collector |      |                      | Ω                | 915MHz                                                                                                    |

| <b>Mixer</b>             |                |      |                      |                  |                                                                                                           |

| Conversion Voltage Gain  |                | 8    |                      | dB               | Single-ended configuration                                                                                |

|                          |                | 7    |                      | dB               | 433MHz                                                                                                    |

| Noise Figure (SSB)       |                | TBD  |                      | dB               | 915MHz                                                                                                    |

|                          |                | 17   |                      | dB               | 433MHz                                                                                                    |

| Input IP <sub>3</sub>    |                | -21  |                      | dBm              | 915MHz                                                                                                    |

|                          |                | -17  |                      | dBm              | 433MHz                                                                                                    |

| Input P <sub>1dB</sub>   |                | -31  |                      | dBm              | 915MHz                                                                                                    |

|                          |                | -28  |                      | dBm              | 433MHz                                                                                                    |

| Maximum Output Voltage   |                |      |                      | V <sub>PP</sub>  | Balanced                                                                                                  |

| <b>First IF Section</b>  |                |      |                      |                  |                                                                                                           |

| IF Frequency Range       | 0.1            | 10.7 | 25                   | MHz              |                                                                                                           |

| Voltage Gain             |                | 40   |                      | dB               | IF=10.7MHz                                                                                                |

| Noise Figure             |                | 13   |                      | dB               |                                                                                                           |

| Input IP <sub>3</sub>    |                | TBD  |                      | mV <sub>PP</sub> |                                                                                                           |

| IF1 Input Impedance      |                | 330  |                      | Ω                |                                                                                                           |

| IF1 Output Impedance     |                | 330  |                      | Ω                |                                                                                                           |

| <b>Second IF Section</b> |                |      |                      |                  |                                                                                                           |

| IF Frequency Range       | 0.1            | 10.7 | 25                   | MHz              |                                                                                                           |

| Voltage Gain             |                | 60   |                      | dB               | IF=10.7MHz                                                                                                |

| IF2 Input Impedance      |                | 330  |                      | Ω                |                                                                                                           |

| IF2 Output Impedance     |                | 1    |                      | κΩ               | At IF2 OUT- pin                                                                                           |

| Demod Input Impedance    |                | 10   |                      | κΩ               |                                                                                                           |

| FM Output Impedance      |                | 500  |                      | Ω                |                                                                                                           |

| Data Output Impedance    |                | >1   |                      | MΩ               |                                                                                                           |

| FM Output Bandwidth      | 2              |      |                      | MHz              |                                                                                                           |

| Data Output Bandwidth    | 2              |      |                      | MHz              |                                                                                                           |

| Data Output Level        | 0.3            |      | V <sub>CC</sub> -0.3 | V                | Z <sub>LOAD</sub> =1MΩ    3pF; Output voltage is proportional with the instantaneous frequency deviation. |

| FM Output DC Level       |                | 2.6  |                      | V                | Z <sub>LOAD</sub> >10kΩ                                                                                   |

| FM Output AC Level       |                | 200  |                      | mV <sub>PP</sub> | Z <sub>LOAD</sub> >10kΩ                                                                                   |

|                            |     |            |     |          |                                          |

|----------------------------|-----|------------|-----|----------|------------------------------------------|

| <b>Power Down Control</b>  |     |            |     |          |                                          |

| Logical Controls "ON"      | 2.0 |            | 1.0 | V        | Voltage supplied to the input            |

| Logical Controls "OFF"     | 25k |            |     | V        | Voltage supplied to the input            |

| Control Input Impedance    |     |            |     | $\Omega$ |                                          |

| Turn On Time               |     | 4          |     | ms       | Reference Crystal=7.075MHz               |

| Turn Off Time              |     | 4          |     | ms       | Dependent upon reference crystal. Higher |

| RX to TX and TX to RX Time |     | 4          |     | ms       | frequencies reduce turn on/off times     |

| <b>Power Supply</b>        |     |            |     |          |                                          |

| Voltage                    |     | 3.6        |     | V        | Specifications                           |

|                            |     | 2.7 to 5.0 |     | V        | Operating limits                         |

| Current Consumption        |     | 25         |     | mA       | TX Mode, LVL ADJ=3.6V                    |

|                            |     | 10         |     | mA       | TX Mode, LVL ADJ=0V                      |

|                            |     | 9          |     | mA       | RX Mode                                  |

|                            |     | 8          | 1   | $\mu$ A  | Power Down Mode                          |

|                            |     |            |     | mA       | PLL Only Mode                            |

| Pin | Function        | Description                                                                                                                                                                                                                                                                                                                                                                                                        | Interface Schematic                                                                   |

|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

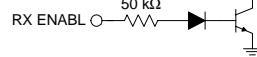

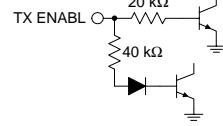

| 1   | <b>RX ENABL</b> | Enable pin for the receiver circuits. RX ENABL>2.0V powers up all receiver functions. RX ENABL<1.0V turns off all receiver functions except the PLL functions and the RF mixer.                                                                                                                                                                                                                                    |    |

| 2   | <b>TX ENABL</b> | Enables the transmitter circuits. TX ENABL>2.0V powers up all transmitter functions. TX ENABL<1.0V turns off all transmitter functions except the PLL functions.                                                                                                                                                                                                                                                   |    |

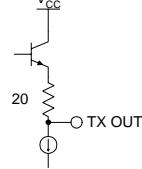

| 3   | <b>TX OUT</b>   | RF output pin for the transmitter electronics. TX OUT output impedance is a low impedance (see output impedance plot in Figure TBD) when the transmitter is enabled. TX OUT is a high impedance when the transmitter is disabled.                                                                                                                                                                                  |    |

| 4   | <b>GND2</b>     | Ground connection for the 40 dB IF limiting amplifier and Tx PA functions. Keep traces physically short and connect immediately to ground plane for best performance.                                                                                                                                                                                                                                              |                                                                                       |

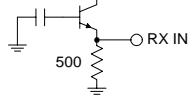

| 5   | <b>RX IN</b>    | RF input pin for the receiver electronics. RX IN input impedance is a low impedance (see input impedance plot in Figure TBD) when the transmitter is enabled. RX IN is a high impedance when the receiver is disabled.                                                                                                                                                                                             |   |

| 6   | <b>GND1</b>     | Ground connection for RF receiver functions. Keep traces physically short and connect immediately to ground plane for best performance.                                                                                                                                                                                                                                                                            |                                                                                       |

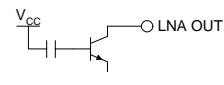

| 7   | <b>LNA OUT</b>  | Output pin for the receiver RF low noise amplifier. This pin is an open collector output and requires an external pull up coil to provide bias and tune the LNA output. A capacitor in series with this output can be used to match the LNA to 50Ω impedance image filters.                                                                                                                                        |  |

| 8   | <b>GND3</b>     | Same as pin 4.                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                       |

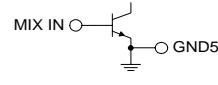

| 9   | <b>MIX IN</b>   | RF input to the RF Mixer. An LC matching network between LNA OUT and MIX IN can be used to connect the LNA output to the RF mixer input in applications where an image filter is not needed or desired.                                                                                                                                                                                                            |  |

| 10  | <b>GND5</b>     | GND5 is the ground connection shared by the input stage of the transmit power amplifier and the receiver RF mixer.                                                                                                                                                                                                                                                                                                 |                                                                                       |

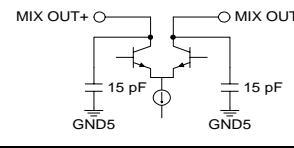

| 11  | <b>MIX OUT+</b> | Complementary (with respect to pin 12) IF output from the RF mixer. Interfaces directly to 10.7MHz ceramic IF filters as shown in the application schematic. A pull-up inductor and series matching capacitor should be used to present a 330Ω termination impedance to the ceramic filter. Alternately, an IF tank can be used to tailor the IF frequency and bandwidth to meet the needs of a given application. |  |

| 12  | <b>MIX OUT-</b> | IF output from the RF mixer. For a balanced mixer output, pull-up inductors from pin 11 and 12 to Vcc and a capacitor between the pins should be used. The sum of the total pull-up inductance should be used to resonate the capacitor between pins 11 and 12. DC blocking capacitors of 10nF can then be used to connect the balanced output to IF1 IN+ (pin 13) and IF1 IN- (pin 14).                           | See pin 11.                                                                           |

|    |           |                 |                                                                                                                                                                                                                                                           |                                                                                       |

|----|-----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

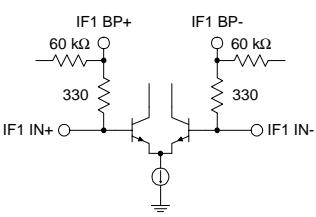

| 11 | <b>13</b> | <b>IF1 IN+</b>  | Balanced IF input to the 40dB limiting amplifier strip. A 10nF DC blocking capacitor is required on this input.                                                                                                                                           |    |

|    | <b>14</b> | <b>IF1 IN-</b>  | Functionally the same as pin 13 except inverting node amplifier input. In single-ended applications, this input should be bypassed directly to ground through a 10nF capacitor.                                                                           | See pin 13.                                                                           |

|    | <b>15</b> | <b>IF1 BP+</b>  | DC feedback node for the 40dB limiting amplifier strip. A 10nF bypass capacitor from this pin to ground is required.                                                                                                                                      | See pin 13.                                                                           |

|    | <b>16</b> | <b>IF1 BP-</b>  | Same as pin 15.                                                                                                                                                                                                                                           | See pin 13.                                                                           |

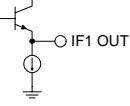

|    | <b>17</b> | <b>IF1 OUT</b>  | IF output from the 40dB limiting amplifier. The IF1 OUT output presents a nominal 330 Ω output resistance and interfaces directly to 10.7MHz ceramic filters.                                                                                             |    |

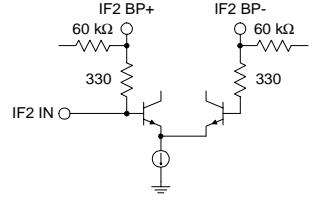

|    | <b>18</b> | <b>IF2 IN</b>   | Balanced IF input to the 60dB limiting amplifier strip. A 10nF DC blocking capacitor is required on this input. The IF2 IN input presents a nominal 330 Ω input resistance and interfaces directly to 10.7MHz ceramic filters.                            |   |

|    | <b>19</b> | <b>GND6</b>     | Ground connection for 60dB IF limiting amplifier. Keep traces physically short and connect immediately to ground plane for best performance.                                                                                                              |                                                                                       |

|    | <b>20</b> | <b>VREF IF</b>  | DC voltage reference for the IF limiting amplifiers. A 10nF capacitor from this pin to ground is required.                                                                                                                                                |                                                                                       |

|    | <b>21</b> | <b>IF2 BP+</b>  | DC feedback node for the 60dB limiting amplifier strip. A 10nF bypass capacitor from this pin to ground is required.                                                                                                                                      | See pin 18.                                                                           |

|    | <b>22</b> | <b>IF2 BP-</b>  | Same as pin 21.                                                                                                                                                                                                                                           | See pin 18.                                                                           |

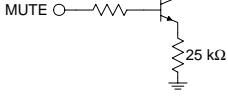

|    | <b>23</b> | <b>MUTE</b>     | This pin is used to mute the data output (DATA OUT). MUTE>2.0V turns the DATA OUT signal on. MUTE<1.0V turns the DATA OUT signal off. The MUTE signal should be logic low in the Sleep Mode.                                                              |  |

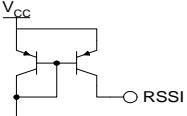

|    | <b>24</b> | <b>RSSI</b>     | A DC voltage proportional to the received signal strength is output from this pin. The output voltage range is 0.5V to 2.5V and increases with increasing signal strength.                                                                                |  |

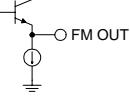

|    | <b>25</b> | <b>FM OUT</b>   | Linear output from the FM demodulator. This pin is used in analog applications when signal fidelity is important.                                                                                                                                         |  |

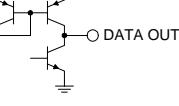

|    | <b>26</b> | <b>DATA OUT</b> | Demodulated data output from the demodulator. Output levels on this are TTL/CMOS compatible. The magnitude of the load impedance is intended to be 1MΩ or greater. When using a RF2905 transmitter and receiver back to back a data inversion will occur. |  |

|    |                 |                                                                                                                                                                                                                                                                                                                                                        |                                                                                       |

|----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

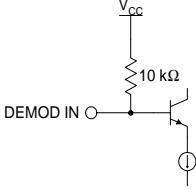

| 27 | <b>DEMOD IN</b> | This pin is the input to the FM demodulator. This pin is NOT AC coupled. Therefore, a DC blocking capacitor is required on this pin to avoid shorting the demodulator input with the LC tank. A ceramic discriminator or DC blocked LC tank resonant at the IF should be connected to this pin.                                                        |    |

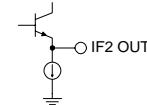

| 28 | <b>IF2 OUT</b>  | Balanced IF output from the 60dB limiting amplifier strip. This pin is intended to be connected to pin 27 through a 5pF capacitor and an FM discriminator circuit.                                                                                                                                                                                     |    |

| 29 | <b>VCC6</b>     | This pin is used is supply DC bias to the 60dB IF limiting amplifier. An IF bypass capacitor should be connected directly to this pin and returned to ground. A 10nF capacitor is recommended for 10.7MHz IF applications.                                                                                                                             |                                                                                       |

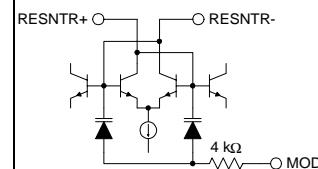

| 30 | <b>RESNTR+</b>  | This port is used to supply DC voltage to the VCO as well as to tune the center frequency of the VCO. Equal value inductors should be connected to this pin and pin 31 although a small imbalance can be used to tune in the proper frequency range.                                                                                                   |    |

| 31 | <b>RESNTR-</b>  | See RESNTR+ description.                                                                                                                                                                                                                                                                                                                               | See pin 30.                                                                           |

| 32 | <b>VCC2</b>     | This pin is used is supply DC bias to the VCO, prescaler, and PLL. An IF bypass capacitor should be connected directly to this pin and returned to ground. A 10nF capacitor is recommended for 10.7MHz IF applications.                                                                                                                                |                                                                                       |

| 33 | <b>GND4</b>     | GND4 is the ground shared on chip by the VCO, prescaler, and PLL electronics.                                                                                                                                                                                                                                                                          |                                                                                       |

| 34 | <b>MOD IN</b>   | FM analog or digital modulation can be imparted to the VCO through this pin. The VCO varies in accordance to the voltage level presented to this pin. To set the deviation to a desired level, a voltage divider referenced to Vcc is the recommended. This deviation is also dependent upon the overall capacitance of the external resonant circuit. | See pin 30.                                                                           |

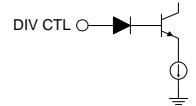

| 35 | <b>DIV CTRL</b> | This pin is used to select the desired prescaler divisor. A logic high (DIV CTRL>2.0V) selects the 64/65 divisor. A logic low (DIV CTRL<1.0V) selects the 128/129 divisor.                                                                                                                                                                             |  |

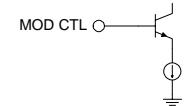

| 36 | <b>MOD CTRL</b> | This pin is used to select the prescaler modulus. A logic high (MOD CTRL>2.0V) selects 64 or 128 for the prescaler divisor. A logic low (MOD CTRL<1.0V) selects 65 or 129 for the prescaler divisor.                                                                                                                                                   |  |

| 37 | <b>OSC SEL</b>  | A logic high (OSC SEL>2.0V) applied to this pin powers on reference oscillator 2 and powers down reference oscillator 1. A logic low (OSC SEL<1.0V) applied to this pin powers on reference oscillator 1 and powers down reference oscillator 2.                                                                                                       |                                                                                       |

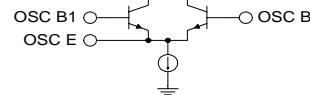

| 38 | <b>OSC B2</b>   | This pin is connected directly to the reference oscillator 2 transistor base. The intended reference oscillator configuration is a modified Colpitts. A 100pF capacitor should be connected between pin 38 and pin 39.                                                                                                                                 |  |

| 39 | <b>OSC E</b>    | This pin is connected directly to the emitter of the reference oscillator transistors. A 100pF capacitor should be connected from this pin to ground.                                                                                                                                                                                                  | See pin 38.                                                                           |

|    |                   |                                                                                                                                                                                                                                                                                                     |             |

|----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 40 | <b>OSC B1</b>     | This pin is connected directly to the reference oscillator 1 transistor base. The intended reference oscillator configuration is a modified Colpitts. A 100pF capacitor should be connected between pin 39 and pin 40.                                                                              | See pin 38. |

| 41 | <b>LOOP FLT</b>   | Output of the charge pump, and input to the VCO control. An RC network from this pin to ground is used to establish the PLL bandwidth.                                                                                                                                                              |             |

| 42 | <b>VREF P</b>     | Bypass pin for the prescaler reference voltage. A 33nF capacitor to ground is needed to suppress reference spurs in the device. This value may be different for different PCB arrangements.                                                                                                         |             |

| 43 | <b>LOCK DET</b>   | This pin provides an analog output indicating the lock status of the PLL. The amplitude of this signal is typically 200mV <sub>pp</sub> around a DC level of V <sub>CC</sub> -0.1 V.                                                                                                                |             |

| 44 | <b>VCC1</b>       | This pin is used to supply DC bias to the receiver RF electronics. A RF bypass capacitor should be connected directly to this pin and returned to ground. A 100pF capacitor is recommended for 915MHz applications. A 220pF capacitor is recommended for 433MHz applications.                       |             |

| 45 | <b>PRESCL OUT</b> | Dual-modulus/Dual-divide prescaler output. The output can be interfaced to an external PLL IC for additional flexibility in frequency programming.                                                                                                                                                  |             |

| 46 | <b>VCC3</b>       | This pin is used to supply DC bias to the transmitter PA. A RF bypass capacitor should be connected directly to this pin and returned to ground. A 100pF capacitor is recommended for 915MHz applications. A 220pF capacitor is recommended for 433MHz applications.                                |             |

| 47 | <b>LVL ADJ</b>    | This pin is used to vary the transmitter output power. An output level adjustment range greater than 12dB is provided through analog voltage control of this pin. DC current of the transmitter power amp is also reduced with output power. This pin MUST be low when the transmitter is disabled. |             |

| 48 | <b>PLL ENABL</b>  | This pin is used to power up or down the VCO and PLL. A logic high (PLL ENABL>2.0V) powers up the VCO and PLL electronics. A logic low (PLL ENABL<1.0V) powers down the PLL and VCO.                                                                                                                |             |

## Pin Out

## 915 MHz Application Schematic