## NFC wireless charging transmitter controller

Rev. 3.0 — 11 January 2021 655130

Product short data sheet COMPANY PUBLIC

## 1 General description

This 32-bit Arm Cortex-M0-based, all in one NFC wireless charging transmitter IC is designed to follow the NFC Forum Standard for Wireless Charging. This product is part of a solution offering from NXP for wireless charging and wireless power transfer for low-power application and small form factor devices.

NFC wireless charging solutions enable customers to remove plugs and cords from their product. This facilitates new design flexibility, can make products smaller and more compact in combination with completely new design options. The removal of plugs and pins is an important step to make a product waterproof and seal it hermetically, which in turn offers an unmatched level of quality and robustness.

In many customer applications, it is the combination of wireless charging with a fast, bidirectional data channel that makes the solution exciting.

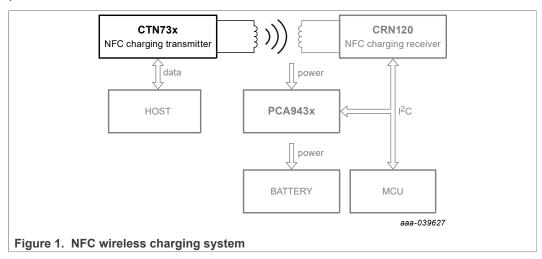

In the figure below a typical NFC charging system is illustrated including <u>CRN120</u> as communication and <u>PCA9430</u> or <u>PCA9431</u> as power receiver. A detailed system view can be found in the <u>AN12639</u>. <u>AN12641</u> provides all needed system information from RF point of view.

#### 2 Features and benefits

### 2.1 Integrated NFC charging frontend

- 1.25 W output power frontend

- Supports reading and writing of NFC Forum tag types 2, 3, 4A, 4B and 5

- CTN730 Supports type 4A card emulation mode up to and including 848 kbit/s

- Low-power NFC charging RX device detection

Table 1. NFC transfer speed in [kbit/s]

| NFC charging controller | Type 2 Tag | Type 3 Tag | Type 4A Tag | Type 4B Tag | Type 5 Tag |

|-------------------------|------------|------------|-------------|-------------|------------|

| CTN730                  | 106        | 212        | up to 848   | 106         | 26         |

| CTN732                  | 106        | 212        | 106         | 106         | 26         |

#### 2.2 Cortex-M0 microcontroller

- · Processor core

- Arm Cortex: 32-bit M0 processor

- Built-in Nested Vectored Interrupt Controller (NVIC)

- Non-maskable interrupt

- 24-bit system tick timer

- Running frequency of up to 20 MHz

- Clock management to enable low power consumption

- Memory

- Flash: 160 kBSRAM: 12 kBEEPROM: 4 kB

- 40 kB boot ROM included, including USB mass storage primary boot loader for code download

- · Debug option

- Serial Wire Debug (SWD) interface

- · Peripherals

- Host interface:

- USB 2.0 full speed with USB 3.0 hub connection capability

- HSUART for serial communication, supporting standards speeds from 9600 bauds to 115200 bauds, and faster speed up to 1.288 Mbit/s

- SPI with half-duplex and full duplex capability with speeds up to 7 Mbit/s

- <u>I<sup>2</sup>C</u> supporting standard mode, fast mode, and high-speed mode with multiple address supports

- Master interface:

- SPI with half-duplex capability from 1 Mbit/s to 6.78 Mbit/s

- 1<sup>2</sup>C supporting standard mode, fast mode plus, and clock stretching

- Up to 21 General-Purpose I/O (GPIO) with configurable pull-up/pull-down resistors

- GPIO1 to GPIO12 can be used as edge and level sensitive interrupt sources

CTN730

- Power

- Two reduced power modes: standby mode and hard power-down mode

- Supports suspend mode for USB host interface

- Processor wake-up from hard power-down mode, standby mode, suspend mode via host interface, GPIOs, NFC field detection

- Integrated PMU to adjust internal regulators automatically, to minimize the power consumption during all possible power modes

- Power-on reset

- NFC supply: external, or using an integrated LDO (TX LDO, configurable with 3 V, 3.3 V, 3.6 V, 4.5 V, and 4.75 V)

- Pad voltage supply: external 3.3 V or 1.8 V, or using an integrated LDO (3.3 V supply)

- Timers

- Four general-purpose timers

- Programmable Watchdog Timer (WDT)

- · CRC coprocessor

- · Random number generator

- Clocks

- Crystal oscillator at 27.12 MHz

- Dedicated PLL at 48 MHz for the USB

- Integrated HFO 20 MHz and LFO 365 kHz

- General

- VFBGA64 package

- HVQFN64 package (CTN730 only)

- Temperature range: -40 °C to +85 °C

## 3 Applications

Designed to follow the NFC Forum Standard for wireless charging, this product is part of a solution offering from NXP for wireless charging and wireless power transfer for low-power application and small form factor devices.

The solution supports wireless charging and power transfer of

- small battery powered devices with small form factors with a power level <1 W

- hearable and audio devices (earbuds, hearing aids)

- computer accessories (stylus pen)

- wearable devices (wrist bands, fitness trackers, rings, smart watches)

- industrial devices (wireless connectors, sensors)

- medical devices (sensor, waterproof small devices)

## 4 Quick reference data

Table 2. Quick reference data

Operating range: -40 °C to +85 °C unless specified; NFC interface: internal LDO not used

| Symbol                 | Parameter                        | Conditions                                                                                   | Min  | Тур | Max  | Unit |

|------------------------|----------------------------------|----------------------------------------------------------------------------------------------|------|-----|------|------|

| V <sub>DDP(VBUS)</sub> | power supply voltage             | CTN730 card emulation mode                                                                   | 2.3  | -   | 5.5  | V    |

|                        | on pin VBUS                      | reader/writer charging mode                                                                  | 2.7  | -   | 5.5  | V    |

| V <sub>DD(PVDD)</sub>  | PVDD supply voltage              | 1.8 V                                                                                        | 1.65 | 1.8 | 1.95 | V    |

|                        |                                  | 3.3 V <sup>[1]</sup>                                                                         | 3    | 3.3 | 3.6  | V    |

| I <sub>DDP(VBUS)</sub> | power supply current on pin VBUS | in hard power-down mode; T = 25 °C; V <sub>DDP(VBUS)</sub> = 5.5 V; RST_N = 0                | -    | 12  | 18   | μA   |

|                        |                                  | stand by mode; T = 25 °C;<br>V <sub>DDP(VBUS)</sub> = 3.3 V; external<br>PVDD LDO used       | -    | 18  | -    | μA   |

|                        |                                  | stand by mode; T = 25 °C;<br>V <sub>DDP(VBUS)</sub> = 5.5 V; internal<br>PVDD LDO used       | -    | 55  | -    | μА   |

|                        |                                  | suspend mode, USB interface; V <sub>DDP(VBUS)</sub> = 5.5 V; external PVDD supply; T = 25 °C | -    | 120 | 250  | μА   |

| I <sub>DD(TVDD)</sub>  | TVDD supply current              | on pin TVDD_IN; maximum supported operating current by the NFC interface                     | -    | -   | 250  | mA   |

| P <sub>max</sub>       | maximum power dissipation        |                                                                                              | -    | -   | 1050 | mW   |

| T <sub>amb</sub>       | ambient temperature              | JEDEC PCB                                                                                    | -40  | -   | +85  | °C   |

<sup>[1]</sup> If the USB interface is used, PVDD\_IN voltage must be between 3.0 V and 3.6 V, according to the USB specification.

## 5 Ordering information

The table below lists the ordering information of CTN73x.

Table 3. Ordering information

| Orderable part number | Package |                                                                                                                      |           |  |  |  |  |

|-----------------------|---------|----------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|

|                       | Name    | Description                                                                                                          | Version   |  |  |  |  |

| CTN730EV/C101Y        | VFBGA64 | plastic very thin fine-pitch ball grid array package; 64 balls; 4.5 mm x 4.5 mm x 0.80 mm; 4000 pcs. on 13" reel     | SOT1307-2 |  |  |  |  |

| CTN730EV/C101E        | VFBGA64 | plastic very thin fine-pitch ball grid array package; 64 balls; 4.5 mm x 4.5 mm x 0.80 mm; 490 pcs. on tray          | SOT1307-2 |  |  |  |  |

| CTN730HN/C101Y        | HVQFN64 | plastic thermal enhanced very thin quad flat package; no leads; 64 terminals; 9 × 9 × 0.85 mm; 1000 pcs. on 13" reel | SOT804-4  |  |  |  |  |

| CTN732EV/C101Y        | VFBGA64 | plastic very thin fine-pitch ball grid array package; 64 balls; 4.5 mm x 4.5 mm x 0.80 mm; 4000 pcs. on 13" reel     | SOT1307-2 |  |  |  |  |

## 6 Block diagram

### 6.1 Block diagram CTN73x

## 7 Limiting values

#### Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol              | Parameter                       | Conditions                                  |   | Min | Max  | Unit |

|---------------------|---------------------------------|---------------------------------------------|---|-----|------|------|

| V <sub>ESD</sub>    | electrostatic discharge voltage | human body model (HBM) <sup>[1]</sup>       |   |     |      |      |

|                     |                                 | on all pins                                 |   | -2  | +2   | kV   |

|                     |                                 | charged device model (CDM) <sup>[2]</sup>   | 1 |     |      |      |

|                     |                                 | on all pins                                 |   | -1  | +1   | kV   |

| T <sub>stg</sub>    | storage temperature             | non-operating                               |   | -55 | +150 | °C   |

| T <sub>j(max)</sub> | maximum junction temperature    |                                             |   | -   | +125 | °C   |

| P <sub>tot</sub>    | total power dissipation         | reader mode; V <sub>DDP(VBUS)</sub> = 5.5 V |   | -   | 1050 | mW   |

<sup>[1]</sup> According to ANSI/ESDA/JEDEC JS-001.

#### Table 5. Limiting values for GPIO1 to GPIO12

| Symbol | Parameter     | Conditions | Min  | Max | Unit |

|--------|---------------|------------|------|-----|------|

| Vi     | input voltage |            | -0.3 | 4.2 | V    |

## Table 6. Limiting values for I<sup>2</sup>C master pins (i2cm\_sda, i2cm\_scl)

| Symbol | Parameter     | Conditions | Min  | Max | Unit |

|--------|---------------|------------|------|-----|------|

| Vi     | input voltage |            | -0.3 | 4.2 | V    |

## Table 7. Limiting values for SPI master pins (spim\_nss, spim\_miso, spim\_mosi and spi\_clk)

| S | ymbol | Parameter     | Conditions | Min  | Max | Unit |

|---|-------|---------------|------------|------|-----|------|

| ٧ | 'i    | input voltage |            | -0.3 | 4.2 | V    |

# Table 8. Limiting values for host interfaces atx\_a, atx\_b, atx\_c, atx\_d in all configurations (USB, HSUART, SPI and $I^2C$ )

| Symbol | Parameter     | Conditions | Min  | Max | Unit |

|--------|---------------|------------|------|-----|------|

| Vi     | input voltage |            | -0.3 | 4.2 | V    |

#### Table 9. Limiting values for crystal oscillator

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol   | Parameter                | Conditions   | Min | Max | Unit |

|----------|--------------------------|--------------|-----|-----|------|

| $V_{IH}$ | high-level input voltage | XTAL1, XTAL2 | 0   | 2.2 | V    |

CTN730

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

<sup>[2]</sup> According to ANSI/ESDA/JEDEC JS-002.

Table 10. Limiting values for power supply

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Parameter                              | Conditions                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                           | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| power supply voltage on pin VBUS       |                                                                                                                                                                                                                                                  | [1]                                                                                                                                                                                                                                                                                                                                                                                                                       | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| power supply voltage on pin VBUSP      |                                                                                                                                                                                                                                                  | [1]                                                                                                                                                                                                                                                                                                                                                                                                                       | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| oltage for host interface and GPIOs    | (on pin PVDD_IN)                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PVDD supply voltage                    | on pin PVDD_IN; power supply for host interfaces and GPIOs                                                                                                                                                                                       | [1]                                                                                                                                                                                                                                                                                                                                                                                                                       | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| oltage for master interfaces (on pin l | PVDD_M_IN)                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PVDD supply voltage                    | on pin PVDD_M_IN; power supply for master interfaces                                                                                                                                                                                             | [1]                                                                                                                                                                                                                                                                                                                                                                                                                       | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ce LDO (pin VUP_TX)                    | 1                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LDO input voltage                      | for NFC interface LDO                                                                                                                                                                                                                            | [1]                                                                                                                                                                                                                                                                                                                                                                                                                       | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| itter (pin TVDD_IN)                    |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TVDD supply voltage                    | for NFC interface transmitter                                                                                                                                                                                                                    | [1]                                                                                                                                                                                                                                                                                                                                                                                                                       | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ,                                      | power supply voltage on pin VBUS power supply voltage on pin VBUSP roltage for host interface and GPIOs PVDD supply voltage roltage for master interfaces (on pin PVDD supply voltage see LDO (pin VUP_TX) LDO input voltage itter (pin TVDD_IN) | power supply voltage on pin VBUS  power supply voltage on pin VBUSP  roltage for host interface and GPIOs (on pin PVDD_IN)  PVDD supply voltage on pin PVDD_IN; power supply for host interfaces and GPIOs  roltage for master interfaces (on pin PVDD_M_IN)  PVDD supply voltage on pin PVDD_M_IN; power supply for master interfaces  re LDO (pin VUP_TX)  LDO input voltage for NFC interface LDO  itter (pin TVDD_IN) | power supply voltage on pin VBUS  power supply voltage on pin VBUSP  roltage for host interface and GPIOs (on pin PVDD_IN)  PVDD supply voltage  on pin PVDD_IN; power supply for host interfaces and GPIOs  roltage for master interfaces (on pin PVDD_M_IN)  PVDD supply voltage  on pin PVDD_M_IN; power supply for host interfaces and GPIOs  roltage for master interfaces (on pin PVDD_M_IN)  [1]  PVDD supply voltage  on pin PVDD_M_IN; power supply for master interfaces  re LDO (pin VUP_TX)  LDO input voltage  for NFC interface LDO  [1]  itter (pin TVDD_IN) | power supply voltage on pin VBUS  power supply voltage on pin VBUSP  roltage for host interface and GPIOs (on pin PVDD_IN)  PVDD supply voltage  on pin PVDD_IN; power supply for host interfaces and GPIOs  roltage for master interfaces (on pin PVDD_M_IN)  PVDD supply voltage  on pin PVDD_M_IN; power supply for host interfaces and GPIOs  roltage for master interfaces (on pin PVDD_M_IN)  PVDD supply voltage  on pin PVDD_M_IN; power supply for master interfaces  re LDO (pin VUP_TX)  LDO input voltage  for NFC interface LDO  [1] -0.3  itter (pin TVDD_IN) | power supply voltage on pin VBUS  power supply voltage on pin VBUSP  roltage for host interface and GPIOs (on pin PVDD_IN)  PVDD supply voltage  on pin PVDD_IN; power supply for host interfaces and GPIOs  roltage for master interfaces (on pin PVDD_M_IN)  PVDD supply voltage  on pin PVDD_M_IN; power supply for host interfaces and GPIOs  roltage for master interfaces (on pin PVDD_M_IN)  PVDD supply voltage  on pin PVDD_M_IN; power supply for master interfaces  supply for master interfaces  re LDO (pin VUP_TX)  LDO input voltage  for NFC interface LDO  [1] -0.3 |

<sup>[1]</sup> Maximum/minimum voltage above the maximum operating range and below ground that can be applied for a short time (< 10 ms) to a device without leading to irrecoverable failure. Failure includes the loss of reliability and shorter life time of the device.

#### Table 11. Limiting values for NFC interface

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol | Parameter     | Conditions          |     | Min | Max | Unit |

|--------|---------------|---------------------|-----|-----|-----|------|

| Vi     | input voltage | on pins RXN and RXP | [1] | 0   | 2.2 | V    |

<sup>[1]</sup> Maximum/minimum voltage above the maximum operating range and below ground that can be applied for a short time (< 10 ms) to a device without leading to irrecoverable failure. Failure includes the loss of reliability and shorter life time of the device.

### Table 12. Limiting values for USB interface

| Symbol                     | Parameter               | Conditions |     | Min  | Max | Unit |

|----------------------------|-------------------------|------------|-----|------|-----|------|

| V <sub>DDP(USB_VBUS)</sub> | Voltage on pin USB_VBUS |            | [1] | -0.3 | 7   | V    |

<sup>[1]</sup> Maximum/minimum voltage above the maximum operating range and below ground that can be applied for a short time (< 10 ms) to a device without leading to irrecoverable failure. Failure includes the loss of reliability and shorter life time of the device.

## 8 Handling information

#### **CAUTION**

This device is sensitive to ElectroStatic Discharge (ESD). Observe precautions for handling electrostatic sensitive devices. Such precautions are described in the ANSI/ESD S20.20, IEC/ST 61340-5, JESD625-A or equivalent standards.

For assembly guidelines refer to AN1902.

## 9 References

- [1] NFC Forum Wireless Charging Technical Specification https://nfc-forum.org/product-category/specification/

- UM10204 I<sup>2</sup>C-bus specification and user manual https://www.nxp.com/docs/en/user-guide/UM10204.pdf

- [3] VFBGA64 SOT1307-2 package and soldering information https://www.nxp.com/docs/en/package-information/SOT1307-2.pdf

- [4] HVQFN64 SOT804-4 package and soldering information https://www.nxp.com/docs/en/package-information/SOT804-4.pdf

- [5] AN1902 Assembly guidelines for QFN and SON packages https://www.nxp.com/docs/en/application-note/AN1902.pdf

- [6] AN12639 NFC wireless charging system guide https://www.docstore.nxp.com/products

- [7] AN12641 NFC wireless charging hardware development and RF configuration <a href="https://www.docstore.nxp.com/products">https://www.docstore.nxp.com/products</a>

- [8] PCA9430 NFC wireless charging power receiver data sheet <a href="https://www.docstore.nxp.com/products">https://www.docstore.nxp.com/products</a>

- [9] PCA9431 NFC wireless charging power receiver data sheet <a href="https://www.docstore.nxp.com/products">https://www.docstore.nxp.com/products</a>

- [10] CRN120 NFC wireless charging communication receiver frontend <a href="https://www.docstore.nxp.com/products">https://www.docstore.nxp.com/products</a>

NFC wireless charging transmitter controller

## 10 Revision history

### Table 13. Revision history

| Document ID       | Release date                              | Data sheet status        | Supersedes |

|-------------------|-------------------------------------------|--------------------------|------------|

| CTN730_SDS v. 3.0 | 20210112                                  | Product short data sheet | -          |

| Modifications:    | First released "Product short data sheet" |                          |            |

## 11 Legal information

#### 11.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 11.2 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 11.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

$\ensuremath{\mathbf{Applications}}$  — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

CTN730

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications. In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

#### 11.4 Licenses

#### Purchase of NXP ICs with ISO/IEC 14443 type B functionality

This NXP Semiconductors IC is ISO/IEC 14443 Type B software enabled and is licensed under Innovatron's Contactless Card patents license for ISO/IEC 14443 B.

RATP/Innovatron Technology

The license includes the right to use the IC in systems and/or end-user equipment.

#### Purchase of NXP ICs with NFC technology

Purchase of an NXP Semiconductors IC that complies with one of the Near Field Communication (NFC) standards ISO/IEC 18092 and ISO/IEC 21481 does not convey an implied license under any patent right infringed by implementation of any of those standards. Purchase of NXP Semiconductors IC does not include a license to any NXP patent (or other IP right) covering combinations of those products with other products, whether hardware or software.

#### 11.5 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

MIFARE — is a trademark of NXP B.V.

ICODE and I-CODE — are trademarks of NXP B.V.

MIFARE Classic — is a trademark of NXP B.V.

NXP — wordmark and logo are trademarks of NXP B.V.

AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile—are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved.

FeliCa — is a trademark of Sony Corporation.

## NFC wireless charging transmitter controller

## **Tables**

| <b>-</b> | NEO (                                      | <b>T</b> |                                            |    |

|----------|--------------------------------------------|----------|--------------------------------------------|----|

| Tab. 1.  | NFC transfer speed in [kbit/s]2            | 1ab. 8.  | Limiting values for host interfaces atx_a, |    |

| Tab. 2.  | Quick reference data5                      |          | atx_b, atx_c, atx_d in all configurations  |    |

| Tab. 3.  | Ordering information6                      |          | (USB, HSUART, SPI and I2C)                 | 8  |

| Tab. 4.  | Limiting values 8                          | Tab. 9.  | Limiting values for crystal oscillator     | 8  |

| Tab. 5.  | Limiting values for GPIO1 to GPIO128       | Tab. 10. | Limiting values for power supply           | 9  |

| Tab. 6.  | Limiting values for I2C master pins (i2cm_ | Tab. 11. | Limiting values for NFC interface          | 9  |

|          | sda, i2cm_scl) 8                           | Tab. 12. | Limiting values for USB interface          | 9  |

| Tab. 7.  |                                            | Tab. 13. | Revision history                           | 12 |

|          | nss, spim_miso, spim_mosi and spi_clk) 8   |          |                                            |    |

## **NXP Semiconductors**

# CTN730/CTN732

NFC wireless charging transmitter controller

| Figures |                               |         |                |  |

|---------|-------------------------------|---------|----------------|--|

| Fig. 1. | NFC wireless charging system1 | Fig. 2. | Block diagram7 |  |

### NFC wireless charging transmitter controller

## **Contents**

| 1   | General description              | 1 |

|-----|----------------------------------|---|

| 2   | Features and benefits            |   |

| 2.1 | Integrated NFC charging frontend | 2 |

| 2.2 | Cortex-M0 microcontroller        |   |

| 3   | Applications                     |   |

| 4   | Quick reference data             | 5 |

| 5   | Ordering information             | 6 |

| 6   | Block diagram                    |   |

| 6.1 | Block diagram CTN73x             |   |

| 7   | Limiting values                  |   |

| 8   | Handling information             |   |

| 9   | References                       |   |

| 10  | Revision history                 |   |

| 11  | Legal information                |   |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.