- 1. As stated in Exhibit I, we use a ASIC chip from Microelectronics. The chip is designed with the clock settings listed below.

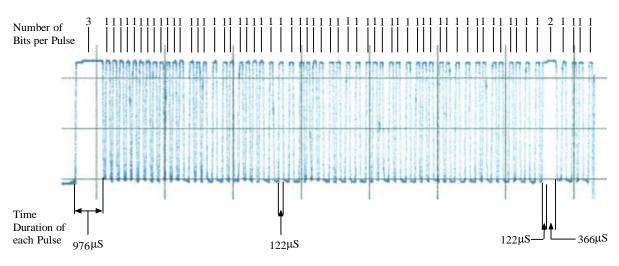

- 2. A pulse can contain more than one bit time. There are a total of 63 bits sent per packet. Three bits are latched with a total "ON" time of 976μS. Another bit has a "ON" time of 366μS. The other 59 bits have a "ON" time of 122μS.

The total "ON" time of a single packet is:

$$59 * 122\mu S + 366\mu S + 976\mu S = 8540\mu S$$

or  $8.54mS$

Duty Cycle correction factor is:

$$20 * LOG (8.54 / 100) = -21.37 dB$$

The plot below, from page 11 in test report, illustrates this:

Number of Pulses = 60 Number of bits = 63

ITI 2266 SECOND STREET NORTH NORTH SAINT PAUL, MN 55109

PH 651-777-2690 VM 800-777-1415 FX 651-779-4890

3. If you have any questions E-Mail me at <a href="Melson@Interlogixinc.com">KenL\_Nelson@Interlogixinc.com</a>

Thank you,

Ken Nelson FCC Compliance Coordinator Interlogix Security & Life Safety Group