#### CIRCUIT DESCRIPTION SECTION 2

### 2-1 RECEIVER CIRCUITS

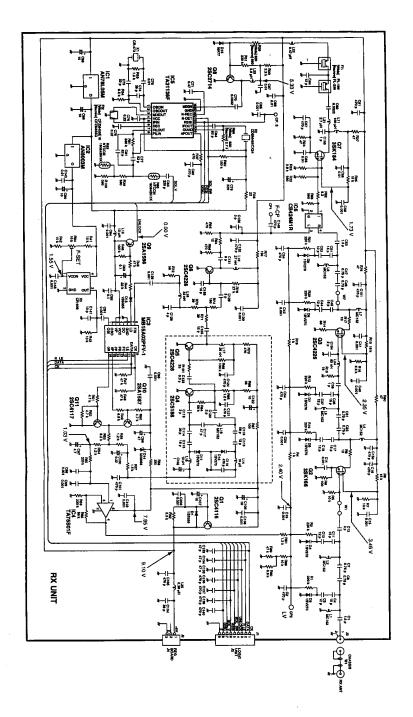

#### 2-1-1 RF CIRCUIT (RX UNIT)

Received signals enter the antenna connector (J3) and pass through a band-pass filter (C4-C7, C11-C13, D3, D4, L1, L2). The filtered signals are applied to an pre-amplifier (Q2). The pre-amplified signals are applied to a band-pass filter (C17, C18, C23, C31, C36-C38, D5, D7, L6, L24), and applied to an RF-amplifier (Q3). The RF-amplified signal passes through a band-pass filter (C44-C47, C51-C53, D8, D9, L7, L9), and then applied to the 1st mixer circuit.

### 2-1-2 1ST MIXER AND 1ST IF CIRCUITS (RX UNIT)

The 1st mixer circuit converts the received signals to a fixed frequency of the 1st IF signal with a PLL output frequency. By changing a PLL frequency, only the desired frequency can be passed through a pair of crystal filters at the next stage of the 1st mixer.

The filtered signals are applied to a 1st mixer (IC6, pin 4) and are then mixed with a 1st LO signal from the PLL circuit to produce a 30.875 MHz 1st IF signal.

The 30.875 MHz 1st IF signal is applied to crystal band-pass filter (FI1). FI1 is an MCF (Monolithic Crystal Filter) which suppresses out-of-band signal. The 1st IF signal is applied to the 2nd mixer circuit (IC5, pin 16) via the buffer amplifier (Q8)

### 2-1-3 2ND IF AND DEMODULATOR CIRCUITS (RX UNIT)

The 2nd mixer circuit converts the 1st IF signal to a 2nd IF signal. A double superheterodyne system (which converts receive signals twice improves the image rejection ratio and obtains stable receiver gain.

The 1st IF signal is applied to a 2nd mixer (IC5, pin 16) and is then mixed with a 2nd LO signal to produce a 455 kHz 2nd IF signal.

The 455 kHz 2nd IF signal is applied to a ceramic band-pass filter (FI2) where unwanted signals are suppressed and then to a limiter amplifier section in system IC (IC5, pin 5).

IC5 contains the local oscillator circuit, quadrature detector circuit, noise filter circuit, IF amplifier, limiter amplifier, noise amplifier, and so on. The local oscillator section and X1 generate 30.42 MHz for the 2nd LO signal.

The 2nd LO signal from the limiter amplifier (IC5, pin 5) is applied to the quadrature detector section (IC5, pin 11 and ceramic discriminator X2) to demodulate the 2nd IF signal into an AF signal. The AF signal is output from pin 9 of IC5.

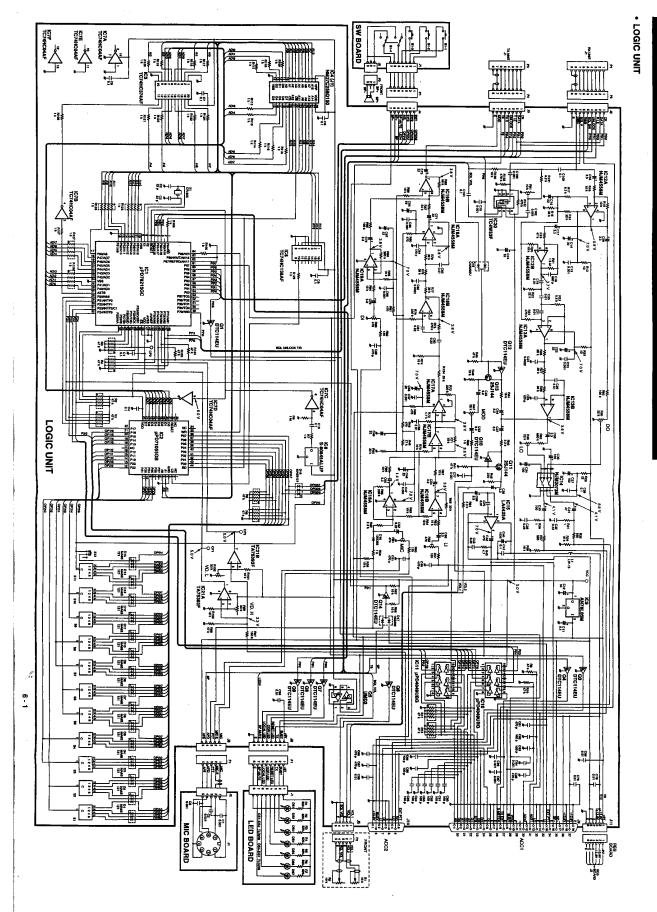

### 2-1-4 SQUELCH CIRCUIT (RX AND LOGIC UNITS)

A squeich circuit cuts out AF signals when no RF signal is received. By detecting noise components in the AF signals, the squelch circuit switches the AF mute switches.

The squelch switching signal from IC5, pin 13 is applied to the [SQL] select switch (LOGIC unit; IC20, pin1) via the "SQL.V" signal. IC20 selects the squelch switch of R2 (on FRONT unit) or R91 (on LOGIC unit). When the [LOCAL INHIBIT] switch is "OFF", the squelch switch selects R2 (on FRONT unit). When the [LOCAL INHIBIT] switch is "ON", the squelch switch selects R91 (on LOGIC unit).

#### 2-1-5 AF AMPLIFIER CIRCUIT (RX AND LOGIC UNITS)

The AF signal outputs from pin 9 of IC5 (RX unit) is applied to pin 2 of IC12 (LOGIC unit), and then applied to pin 3 of IC13 (LOGIC unit) which functions as a high-pass and lowpass filter via a de-emphasis circuit. The filtered signal is output from pin 7 of IC13 (LOGIC unit) and is the applied to the [VOLUME] control (R1) on the FRONT PANEL through an AF mute switch (LOGIC unit; Q10 and Q11). When the squelch is closed, Q10 and Q11 cuts off the AF signal as an AF mute switch. The AF signal is power-amplified at an AF power amplifier (LOGIC unit; IC15) to drive a speaker.

> "RSSI" signal to the J9, pin 26 (Logic unit)

#### 2nd IF AND DEMODULATOR CIRCUITS 2nd IF filter 455 kHz **C81** : C77 FI2 X1 3 **R81** 5 R39 **₹** R85 **≶** 8 Active 2nd Noise limiter filter Mixe amp. amp C83 R100≸ R83≸ QUAD. detector Noise "SQL.V" signal to the IC20, pin 1 (LOGIC unit) RSSI IC5 TA31136F comp. 116 12 13 10 1st IF signal (30.875 MHz) 9 **C84** from Q8 **R37** "SQL.SW" signal to the IC1, pin 49 (Logic unit) "DISC" signal to the IC12, pin 2 (LOGIC unit) X2 **R83** C80

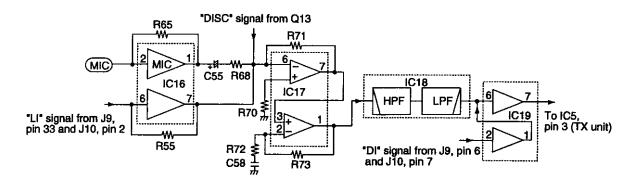

### 2-2 TRANSMITTER CIRCUITS 2-2-1 MICROPHON AMPLIFIER CIRCUIT

(LOGIC UNIT)

The microphone amplifier circuit (IC16) amplifies the audio signals from the microphone. The amplified signal is mixed with the "LI" signal from IC16 (on the LOGIC unit) and "MOD-MUTE" signal from Q12 and Q13 (on the LOGIC unit) at the mixer amplifier (IC17). The mixed signal passes through the high-pass and low-pass filter (IC18) via the preemphasis circuit (IC17), within +6 dB/octave pre-emphasis characteristics (300 Hz-3 kHz), to a level needed for the modulation circuit.

The filtered signal is applied to the mixer amplifier, and is then mixed with the "DI" signal from IC19. The mixed signal is applied to the limiter amplifier (TX unit; IC5, pin 3).

#### 2-2-2 MODULATION CIRCUIT (TX UNIT)

The modulation circuit modulates the VCO oscillating signal (RF signal) using the microphone AF signals.

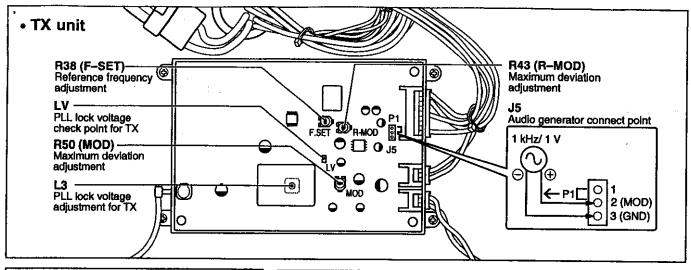

The "MOD" signal from pin 7, J1 is applied to the limiteramplifier (IC5, pin 3) via the pin 1, J5. The limiter-amplified signal passes through the modulating controller (Q13) and low-pass filter (IC5). The filtered signal is adjusted the input level by the R50, and is then applied to the VCO circuit (D2, D3, Q2).

#### 2-2-3 YGR-AMPLIFIER CIRCUIT (TX UNIT)

The YGR-amplifier circuit includes the buffer-amplifier (Q4). pre-driver (Q5) and YGR-amplifier (Q6). The buffer-amplified signal from the VCO circuit is amplified at the YGRamplifier circuit. The YGR-amplified signal is applied to the power amplifier (PA unit; IC1, pin 1).

The "APCV" signal from the APC control circuit (PA unit) is applied to the YGR-amplifier (Q6) to stable RF output power.

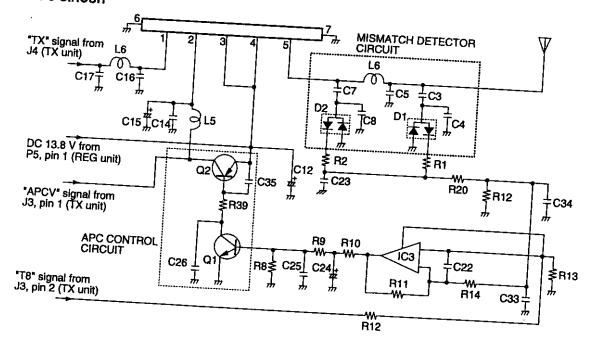

#### 2-2-4 RF POWER AMPLIFIER CIRCUIT (PA UNIT)

IC1 is a power module which provides a stable 45 W of output power.

The amplified signal from the TX unit passes through the low-pass filter (C16, C17, L6), and is then applied to power -amplifier (IC1, pin 1). The power-amplified signal is applied to the RF detector circuit (D1, D2) to control APC circuit, and passes through the low-pass filter (L1-L4, C1, C2, C5, C6, C9. C10). Then, the filtered signal is applied to the TX antenna connector.

#### 2-2-5 APC CIRCUIT (PA UNIT)

APC circuit controls a current of the power module's first stage and a current of the driver amplifier to obtain stable RF output power.

The APC mismatch detector circuit consists of C3, C7, D1. D2, L3. When the antenna impedance is matched at 50  $\Omega$ . the detected voltage by D1 and D2 is at its minimum. The detected voltage is applied to a differential amplifier (IC3, pin 3). The APC reference voltage is applied to pin 1,of IC3.

When the antenna impedance is mismatched, the voltage of IC3 (pin 3) exceeds the reference voltage of IC3 (pin 1). The output level from IC3 (pin 4) decreases. Q1 amplifies the current from the differential amplifier (IC3) which controls Q2. Q2 changes the supply voltage to IC1.

This decreases the output power from the power amplifier (IC1) until the input voltage of IC3 (pin 6) reaches the same level as pin 5 of IC2.

#### MICROPHONE AMPLIFIER CIRCUITS

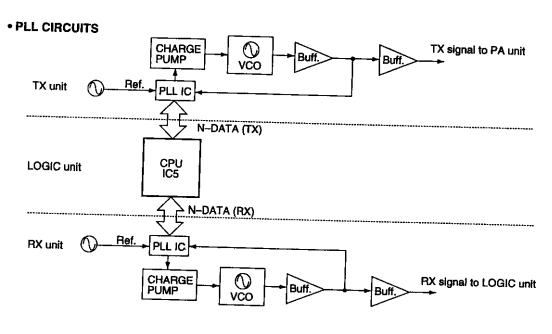

### 2-3 PLL CIRCUITS

#### 2-3-1 GENERAL

Each receiver and transmitter circuit has an independent PLL circuit for controlling frequencies. All PLL circuits are shielded and installed on the RX and TX Units.

PLL circuits steadily oscillate the transmit frequency and the receive local frequency. The PLL output frequency is controlled by the divided ratio (N-data) of the program mable

## 2-3-2 RECEIVER PLL CIRCUIT (RX UNIT)

The PLL IC (IC3) which includes the prescaler, the programmable counter and the phase comparator generates the 1st LO frequency with a Colpitts VCO (D10, D11, Q4). The PLL IC sets the dividing ratio based on N-data from the CPU (LOGIC unit; IC1) to control the programmable counter. The PLL IC compares the phases of a VCO signal with the reference oscillator frequency, and is then applied to VCO circuit (D10, D11, Q4) via the charge pump circuit (D14,

### 2-3-3 RECEIVER REFERENCE OSCILLATOR **CIRCUIT (RX UNIT)**

A 12.8 MHz reference frequency is produced by the oscillator (X3). The frequency is adjusted with R84. The reference frequency is applied to the PLL IC (IC3, pin 1).

## 2-3-4 RECEIVER VCO CIRCUIT (RX UNIT)

The VCO circuit (D10, D11, Q4) generates the receive frequency. D10, D11, L14 and L15 provide oscillate frequency control. The controlled signal is applied to the buffer-amplifier (Q5) to amplify the VCO oscillation. The buffer-amplified signal is applied to PLL IC (IC3, pin 8) and the buffer-amplifier (Q6). The buffer-amplified signal is applied to the mixer circuit (IC6, pin 3).

## 2-3-5 TRANSMITTER PLL CIRCUIT (TX UNIT)

The PLL IC (IC3) which includes the prescaler, the programmable counter and the phase comparator generates the 1st LO frequency with a Colpitts VCO (D2, D3, Q2). The PLL IC sets the dividing ratio based on N-data from the CPU (LOGIC unit; IC1) to control the programmable counter. The PLL IC compares the phases of a VCO signal with the reference oscillator frequency, and is then applied to VCO circuit (D2, D3, Q2) via the charge pump circuit (D6, Q10,

### 2-3-6 TRANSMITTER REFERENCE OSCILLATOR CIRCUIT (TX UNIT)

A 12.8 MHz reference frequency is produced by the oscillator (X1). The frequency is adjusted with R38. The reference frequency is applied to the PLL IC (IC3, pin 1).

## 2-3-7 TRANSMITTER VCO CIRCUIT (TX UNIT)

The VCO circuit (D2, D3, Q2) generates the transmit frequency. D2, D3, L1 and L2 provide oscillate frequency control. The controlled signal is applied to the buffer-amplifier (Q3) to amplify the VCO oscillation. The buffer-amplified signal is applied to PLL IC (IC3, pin 8) and the YGR-amplifier circuit (Q4, Q5, Q6).

#### APC CIRCUIT

# 2-4 POWER SUPPLY CIRCUIT 2-4-1 VOLTAGE LINES

| LINE     | DECODIDATION                                                                                                                                                                                                                       |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u> </u> | DESCRIPTION                                                                                                                                                                                                                        |

| 13.8 V   | The voltage from the connected DC power supply. The output voltage is applied to the CPU (LOGIC unit; IC1, pin 45) via the V.DET circuit (LOGIC unit; IC21, pin 3 and 5).                                                          |

| S13.8 V  | The same voltage as the 13.8 V line which is controlled by the power switch (FRONT unit; S1). The output voltage is applied to the AF amplifier (LOGIC unit; IC15, pin 5) via the "V13" line.                                      |

| + 9 V    | Common 9 V converted from the DC power supply by the + 9 V regulator circuit (REG unit; IC1). The output voltage is applied to TX switch, + 5 V regulator, ripple filter on TX unit and + 5 V regulator, ripple filter on RX unit. |

| + 5 V    | Common 5 V converted from the + 9 V regulator circuit (REG unit; IC1) by the + 5 V regulator circuit (LOGIC unit; IC9).  The output voltage is applied to RESET circuit (LOGIC unit).                                              |

### 2-5 PORT ALLOCATIONS 2-5-1 CPU (LOGIC UNIT IC1)

| number name Description  3 P62 / A18 Outputs LOCAL INHIBIT LED control signal .  4 P61 / A17 Outputs COR SIMURATE LED control singal.  5 P60 / A16 Outputs RESET LED control signal.  1 Input port for the transmitting mode from the outside signal.  30 P22 / INTP0 Input port for the STB signal to switch the outside frequency.  31 P23 / INTP2   Input port for the LOCAL mode from the outside signal.  32 P24 / INTP3 Input port for the RESET signal from the outside signal.  45 P74 / AN4 Input port for the VD, H signal from the DC power supply voltage detecting circuit.  46 P73 / AN3 Input port for the VD, L signal from the DC power supply voltage detecting circuit.  47 P72 / AN2 Input port for the TX unlock signal.  48 P71 / AN1 Input port for the RX unlock signal.  49 P70 / AN0 Input port for the squelch signal.  54 P00 Outputs clock signal to TX and RX PLL IC.  Outputs data signal to TX and RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 011          |                 |                                                                |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|----------------------------------------------------------------|--|--|--|--|--|

| 961 / A17 Outputs COR SIMURATE LED control singal.  1 P60 / A16 Outputs RESET LED control signal.  1 P21 / INTPO Input port for the transmitting mode from the outside signal.  1 P22 / INTP1 Input port for the STB signal to switch the outside frequency.  1 P23 / INTP2 / C1 Input port for the LOCAL mode from the outside signal.  1 P24 / INTP3 Input port for the RESET signal from the outside signal.  1 P74 / AN4 Input port for the VD, H signal from the DC power supply voltage detecting circuit.  1 P72 / AN2 Input port for the VD, L signal from the DC power supply voltage detecting circuit.  1 P72 / AN2 Input port for the TX unlock signal.  1 P70 / AN0 Input port for the RX unlock signal.  1 P00 Outputs clock signal to TX and RX PLL IC.  1 Outputs data signal to TX and RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pin<br>numbe | Port<br>er name | Description                                                    |  |  |  |  |  |

| singal.  P60 / A16 Outputs RESET LED control signal.  P21 / INTP0 Input port for the transmitting mode from the outside signal.  P22 / INTP1 Input port for the STB signal to switch the outside frequency.  Input port for the LOCAL mode from the outside signal.  P23 / INTP2 / C1 Input port for the RESET signal from the outside signal.  P24 / INTP3 Input port for the VD, H signal from the DC power supply voltage detecting circuit.  Input port for the VD, L signal from the DC power supply voltage detecting circuit.  P72 / AN2 Input port for the TX unlock signal.  P71 / AN1 Input port for the RX unlock signal.  P70 / AN0 Input port for the squelch signal.  Outputs clock signal to TX and RX PLL IC.  Outputs data signal to TX and RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3            | P62 / A1        | Outputs LOCAL INHIBIT LED control signal .                     |  |  |  |  |  |

| P21 / INTPO Input port for the transmitting mode from the outside signal.  P22 / INTP1 Input port for the STB signal to switch the outside frequency.  Input port for the LOCAL mode from the outside signal.  P23 / INTP2 / C1 Input port for the RESET signal from the outside signal.  P24 / INTP3 Input port for the VD, H signal from the DC power supply voltage detecting circuit.  P74 / AN4 Input port for the VD, L signal from the DC power supply voltage detecting circuit.  P72 / AN2 Input port for the TX unlock signal.  P71 / AN1 Input port for the RX unlock signal.  P70 / AN0 Input port for the squelch signal.  Outputs clock signal to TX and RX PLL IC.  Outputs data signal to TX and RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4            | P61 / A1        | Outputs COR SIMURATE LED control singal.                       |  |  |  |  |  |

| P21 / INTPO Input port for the transmitting mode from the outside signal.  P22 / INTP1 Input port for the STB signal to switch the outside frequency.  Input port for the LOCAL mode from the outside signal.  P23 / INTP2 / C1 Input port for the RESET signal from the outside signal.  P24 / INTP3 Input port for the VD, H signal from the DC power supply voltage detecting circuit.  P74 / AN4 Input port for the VD, L signal from the DC power supply voltage detecting circuit.  P72 / AN2 Input port for the TX unlock signal.  P71 / AN1 Input port for the RX unlock signal.  P70 / AN0 Input port for the squelch signal.  Outputs clock signal to TX and RX PLL IC.  Outputs data signal to TX and RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5            | P60 / A1        | Outputs RESET LED control signal.                              |  |  |  |  |  |

| 1 INTP1 the outside frequency.  1 P23 / INTP2 / C1 the outside signal.  1 P24 / INTP3 Input port for the LOCAL mode from the outside signal.  1 P24 / INTP3 Input port for the RESET signal from the outside signal.  1 P74 / AN4 Input port for the VD, H signal from the DC power supply voltage detecting circuit.  1 P73 / AN3 Input port for the VD, L signal from the DC power supply voltage detecting circuit.  1 P72 / AN2 Input port for the TX unlock signal.  1 P71 / AN1 Input port for the RX unlock signal.  1 P70 / AN0 Input port for the squelch signal.  2 P00 Outputs clock signal to TX and RX PLL IC.  2 Outputs data signal to TX and RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29           |                 | Input port for the transmitting mode                           |  |  |  |  |  |

| 1NTP2 / C1 the outside signal.  P24 / INTP3 Input port for the RESET signal from the outside signal.  Input port for the VD, H signal from the DC power supply voltage detecting circuit.  Input port for the VD, L signal from the DC power supply voltage detecting circuit.  P73 / AN3 Input port for the TX unlock signal.  P72 / AN2 Input port for the RX unlock signal.  P71 / AN1 Input port for the RX unlock signal.  P70 / AN0 Input port for the squelch signal.  Outputs clock signal to TX and RX PLL IC.  Outputs data signal to TX and RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30           | 1               | Input port for the STB signal to switch the outside frequency. |  |  |  |  |  |

| the outside signal.  P74 / AN4 Input port for the VD, H signal from the DC power supply voltage detecting circuit.  Input port for the VD, L signal from the DC power supply voltage detecting circuit.  P73 / AN3 Input port for the TX unlock signal.  P71 / AN1 Input port for the RX unlock signal.  P70 / AN0 Input port for the squelch signal.  Outputs clock signal to TX and RX PLL IC.  Outputs data signal to TX and RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31           |                 | Input port for the LOCAL mode from the outside signal.         |  |  |  |  |  |

| P73 / AN3 DC power supply voltage detecting circuit.  Input port for the VD, L signal from the DC power supply voltage detecting circuit.  P72 / AN2 Input port for the TX unlock signal.  P71 / AN1 Input port for the RX unlock signal.  P70 / AN0 Input port for the squelch signal.  Outputs clock signal to TX and RX PLL IC.  Outputs data signal to TX and RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32           |                 | Input port for the RESET signal from the outside signal.       |  |  |  |  |  |

| P73 / AN3 DC power supply voltage detecting circuit.  47 P72 / AN2 Input port for the TX unlock signal.  48 P71 / AN1 Input port for the RX unlock signal.  49 P70 / AN0 Input port for the squelch signal.  54 P00 Outputs clock signal to TX and RX PLL IC.  55 P01 Outputs data signal to TX and RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45           | P74 / AN4       | DC power supply voltage detection                              |  |  |  |  |  |

| 48 P71 / AN1 Input port for the RX unlock signal. 49 P70 / AN0 Input port for the squeich signal. 54 P00 Outputs clock signal to TX and RX PLL IC. 55 P01 Outputs data signal to TX and RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46           | P73 / AN3       | DC power supply voltage detecting                              |  |  |  |  |  |

| 48 P71 / AN1 Input port for the RX unlock signal. 49 P70 / AN0 Input port for the squelch signal. 54 P00 Outputs clock signal to TX and RX PLL IC. 55 P01 Outputs data signal to TX and RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 47           | P72 / AN2       | Input port for the TX unlock signal.                           |  |  |  |  |  |

| 49 P70 / ANO Input port for the squeich signal.  54 P00 Outputs clock signal to TX and RX PLL IC.  55 P01 Outputs data signal to TX and RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48           | P71 / AN1       |                                                                |  |  |  |  |  |

| 55 P01 Outputs data signal to TX and RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49           | P70 / AN0       |                                                                |  |  |  |  |  |

| IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54           | P00             | Outputs clock signal to TX and RX PLL IC.                      |  |  |  |  |  |

| 56 P02 Outputs I F signal to TX PULIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55           | P01             | Outputs data signal to TX and RX PLL IC.                       |  |  |  |  |  |

| THE PLANT OF THE PARTY OF THE P | 56           | P02             | Outputs LE signal to TX PLL IC.                                |  |  |  |  |  |

| 57 P03 Outputs LE signal to RX PLL IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57           | P03             |                                                                |  |  |  |  |  |

| 58 P04 Outputs control signal for transmitting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58           | P04             |                                                                |  |  |  |  |  |

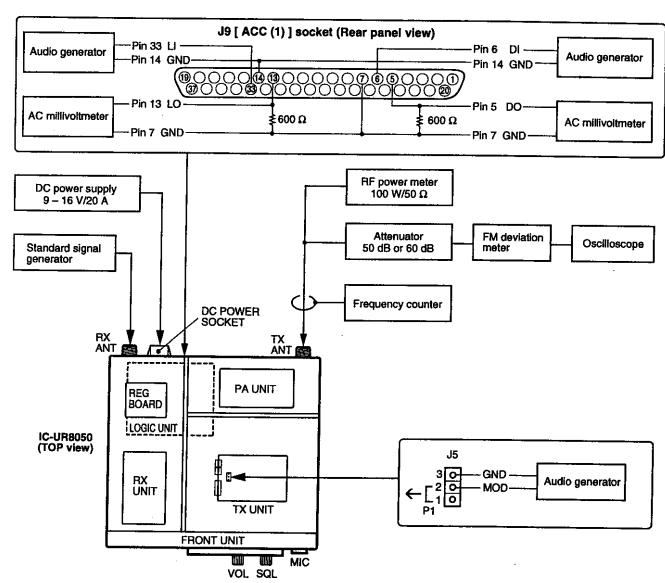

## SECTION 3 ADJUSTMENT PROCEDURES

#### **3-1 PREPARATION**

#### ■ REQUIRED TEST EQUIPMENT

| EQUIPMENT                        | GRADE AND RANGE                                        |                                                             | EQUIPMENT                       | GRADE AND RANGE                    |                                                      |  |

|----------------------------------|--------------------------------------------------------|-------------------------------------------------------------|---------------------------------|------------------------------------|------------------------------------------------------|--|

| DC power supply                  | Output voltage<br>Current capacity                     | : 9-16 V DC<br>: 20 A or more                               | Standard signal generator (SSG) | Frequency range<br>Output level    | : 300–600 MHz<br>: 0.1 µV~32 mV<br>(–127 to –17 dBm) |  |

| RF power meter (terminated type) | Measuring range<br>Frequency range<br>Impedance<br>SWR | : 1-100 W<br>: 300-600 MHz<br>: 50 Ω<br>: Less than 1.2 : 1 | Oscilloscope                    | Frequency range<br>Measuring range | : DC-20 MHz<br>: 0.01-20 V                           |  |

|                                  |                                                        |                                                             | DC voltmeter                    | Input impedance                    | : 50 kΩ/V DC or better                               |  |

| Frequency counter                | Frequency accuracy: ±1                                 | : 0.1-600 MHz<br>: ±1 ppm or better<br>: 100 mV or better   | AC millivoltmeter               | Measuring range                    | : 10 mV-10 V                                         |  |

|                                  |                                                        |                                                             | Digital multimeter              | Input Impedance                    | : 10 MΩ/V DC or better                               |  |

| FM deviation meter               | Frequency range                                        | : 30–600 MHz                                                | Attenuator                      | Power attenuation<br>Capacity      | : 50 or 60 dB<br>: 100 W or more                     |  |

|                                  | Measuring range                                        | : 0 to 10 kHz                                               |                                 | Impedance                          | : 50 Ω                                               |  |

| Audio generator (AG)             |                                                        | : 300-3000 Hz<br>: 1-500 mV                                 | Terminator                      | Capacity                           | : 100 W or more                                      |  |

|                                  |                                                        |                                                             |                                 | Impedance                          | : 600 Ω dummy                                        |  |

CW: Clockwise CCW: Counterclockwise

#### **ECONNECTION**

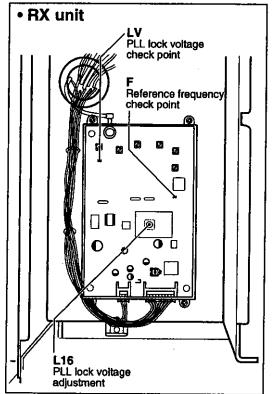

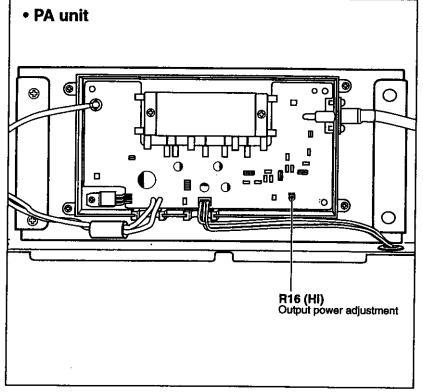

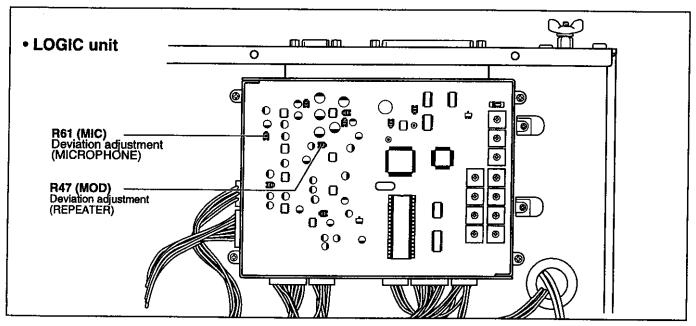

### 3-2 PLL AND TRANSMITTER ADJUSTMENTS

| ADJUSTMENT             |   | ADJUSTMENT CONDITIONS                                                                                                                                                                                                                                                             |               | MEASUREMENT                                                                       | VALUE                                                                                     | ADJUSTMENT |                |

|------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------|----------------|

|                        |   | ADJUSTMENT CONDITIONS                                                                                                                                                                                                                                                             | UNIT LOCATION |                                                                                   | VALUE                                                                                     | UNIT       | ADJUST         |

| PLL LOCK<br>VOLTAGE    | 1 | Operating freq.: 415.000 MHz Apply DC voltage: 13.8 V [VOLUME]: Max. CCW [SQUELCH]: Max. CW Connect an RF power meter or terminator to the [TX ANT] connector. Transmitting:                                                                                                      | TX            | Connect a digital multi-<br>meter or an oscillo-<br>scope to check point<br>[LV]. |                                                                                           | ТХ         | L3             |

|                        | 2 | [LOCAL INHIBIT] switch : ON     Receiving freq. : 415.050 MHz     [VOLUME] : "11 o'clock" position     Receiving                                                                                                                                                                  | RX            | Connect a digital multi-<br>meter or an oscillo-<br>scope to check point<br>[LV]. |                                                                                           | RX         | L16            |

| REFERENCE<br>FREQUENCY |   | Operating freq. :415.000 MHz     Transmitting                                                                                                                                                                                                                                     | Rear<br>panel | Loosely couple a frequency counter to the [TX ANT] connector.                     |                                                                                           | ТХ         | R38<br>(F-SET) |

| OUTPUT<br>POWER        | 1 | [LOCAL INHIBIT] switch : ON     Operating freq. : 415.000 MHz     Apply DC voltage : 13.8 V     [VOLUME] : Max. CCW     [SQUELCH] : Max. CW      Transmitting                                                                                                                     | Rear<br>panel | Connect an RF power meter or a terminator to the [TX ANT] connector.              |                                                                                           | PA         | R16<br>(Hi)    |

| DEVIATION<br>(MAXIMUM) | 1 | [LOCAL INHIBIT] switch: ON     Set an FM deviation meter as:         HPF : OFF         LPF : 20 kHz         De-emphasis: OFF         Detector: (P-P)/2     Disconnect P1 from J5 on the TX     unit, connect an audio generator to J5     and set as: 1 kHz/ 1 V     Transmitting | Rear<br>panel | Connect an FM deviation meter to the [TX ANT] connector through an attenuator.    | [Wide]                                                                                    | TX         | R50<br>(MOD)   |

|                        | 2 | Set an AG as : 50 Hz/ 1 V     Transmitting                                                                                                                                                                                                                                        |               |                                                                                   | Minimum deviation, and a connected oscilloscope to the FM deviation meter as shown below. |            | R43<br>(R-MOD) |

|                        | 3 | After adjustment, connect P1 to J5 on th                                                                                                                                                                                                                                          | e TX un       | it.                                                                               |                                                                                           | <u></u> i  |                |

| (MICROPHONE)           | 4 | Connect an AG to [MIC] connector<br>and set as : 1 kHz/ 4 mV     Transmitting                                                                                                                                                                                                     | Rear<br>panel | Connect an FM deviation meter to the [TX ANT] connector through an attenuator.    | [Wide]                                                                                    | LOGIC      | R61<br>(MIC)   |

| (REPEATER)             | 5 | • [LOCAL INHIBIT] switch : OFF • Connect an SSG to the [RX ANT] connector and set as:  Level :1 mV*  (60 dBµ)  Deviation :± 3 kHz  Modulation :1 kHz • Receiving                                                                                                                  |               | -                                                                                 |                                                                                           |            | R47<br>(MOD)   |

| ļ                      |   | Set an SSG as  Deviation : ± 5.0 kHz [Wide] : ± 2.5 kHz [Narrow]  Receiving                                                                                                                                                                                                       |               |                                                                                   | ± 3.0–5.0 kHz<br>[Wide]<br>± 1.5–2.5 kHz<br>[Narrow]                                      |            | Verify         |

<sup>\*</sup>This output level of the standard signal generator (SSG) is indicated as the SSG's open circuit.

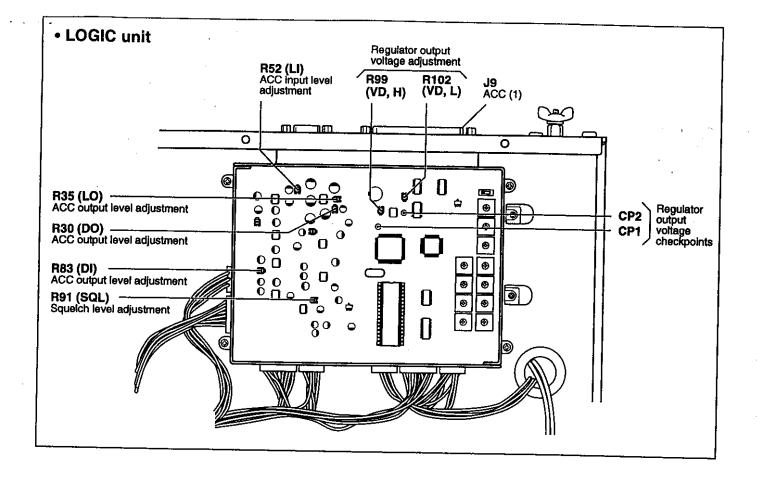

### 3-3 ACC LEVELS, REGULATOR OUTPUT AND RECEIVER ADJUSTMENTS

| ADJUSTMENT                     |   | AD HISTMENT CONDITIONS                                                                                                                                                                                                         |               | MEASUREMENT                                                                         | 3/41.15                                                    | ADJUSTMENT |                                                                |

|--------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------|------------------------------------------------------------|------------|----------------------------------------------------------------|

|                                |   | ADJUSTMENT CONDITIONS                                                                                                                                                                                                          |               | LOCATION                                                                            | VALUE                                                      | UNIT       | ADJUST                                                         |

| ACC OUPUT<br>LEVEL (DO)        | 1 | • [LOCAL INHIBIT] switch : ON • Connect an SSG to the [RX ANT] connector and set as : Level : 1 mV* (-60 dBµ) Deviation : ±3.0 kHz [Wide] ±1.5 kHz[Narrow] Modulation : 1 kHz                                                  | Rear<br>panel |                                                                                     |                                                            | LOGIC      | R30<br>(DO)                                                    |

| ACC OUPUT<br>LEVEL (LO)        | 2 | Receiving                                                                                                                                                                                                                      | <u></u>       | (J9 pin 13, 7)                                                                      | 0 dBm                                                      |            | R35<br>(LO)                                                    |

| ACC INPUT<br>LEVEL (LI)        | 1 | [LOCAL INHIBIT] switch : ON     Set an FM deviation meter as:         HPF : OFF         LPF : 20 kHz         De-emphasis : OFF         Detector : (P-P)/2     Connect an AG to [ACC1] socket (J9 pin 33, 14) and set as        | Rear<br>panel | Connect an FM deviation meter to the [TX ANT] connector through an attenuator.      | [Wide]<br>± 1.5 kHz                                        | LOGIC      | R52<br>(LI)                                                    |

| ACC INPUT<br>LEVEL (DI)        | 2 | Connect an AG to [ACC1] socket (J9 pin 6, 14) and set as     Level : 1 kHz/100 mV     Transmitting                                                                                                                             |               |                                                                                     | ±3 kHz                                                     |            | R83<br>(DI)                                                    |

| REGULATOR<br>OUTPUT<br>VOLTAGE | 1 | Connect an RF power meter or a terminator to the [TX ANT] connector.     R99, R102 (LOGIC unit)     : Max. CCW     Apply DC voltage: 11 V                                                                                      | LOGIC         | Connect a digital multi-<br>meter to check point<br>CP1.                            |                                                            | LOGIC      | R99<br>(VD, H)                                                 |

|                                | 2 | Apply DC voltage : 10 V                                                                                                                                                                                                        |               | Connect a digital multi-<br>meter to check point<br>CP2.                            |                                                            |            | R102<br>(VD, L)                                                |

|                                | 3 | Decrease applied DC voltage 13.8 V to 9 V.     Transmitting                                                                                                                                                                    | Rear          | Connect a DC volt-<br>meter between the +<br>and – terminals at DC<br>power socket. | LED at 10 V.                                               | Front      | Verify                                                         |

| - 1047                         | 4 | <ul> <li>Increase applied DC voltage 9 V to<br/>13.8 V.</li> <li>Transmitting</li> </ul>                                                                                                                                       |               |                                                                                     | Turns on [TX]<br>LED at 11 V.<br>(start transmit-<br>ting) |            |                                                                |

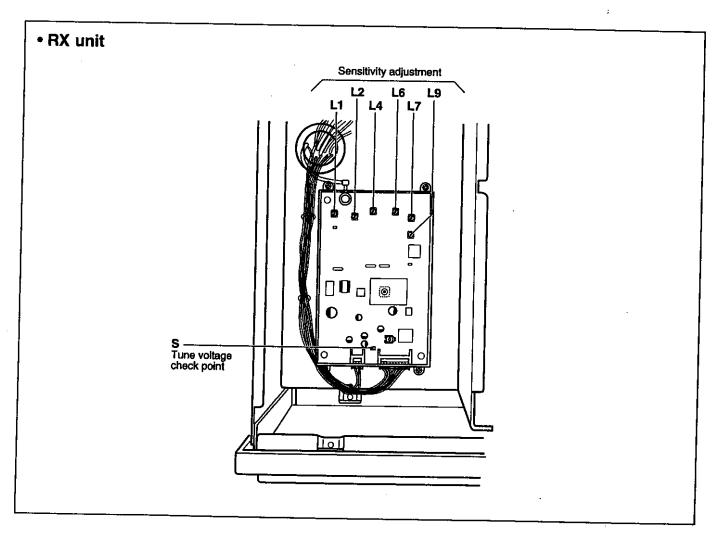

| SENSITIVITY                    | 1 | • [LOCAL INHIBIT] switch : ON • Receiving freq. : 415.000 MHz • Connect an SSG to the [RX ANT] connector and set as : Level : 3.2 µV* (-97 dBm) Deviation : ±3.0 kHz [Wide] : ±1.5 kHz [Narrow] Modulation : 1 kHz • Receiving | RX            | Connect a digital multi-<br>meter to check point<br>CP.S.                           | Maximum volt-<br>age                                       | RX         | Adjust in<br>sequence<br>L1,<br>L2,<br>L4,<br>L6,<br>L7,<br>L9 |

| SQUELCH<br>LEVEL               |   | • [LOCAL INHIBIT] switch : ON • Receiving freq : 415.000 MHz • Connect an SSG to the [RX ANT] connector and set as : Level : 0.32 μV* (–10 dBμ) Modulation : OFF • Receiving                                                   | FRONT         | [BUSY] LED                                                                          | At the point where<br>the [BUSY] LED just<br>turns on.     | FRONT      | [SQUELCH]<br>control                                           |

|                                |   | • [LOCAL INHIBIT] switch : OFF<br>• R91 (LOGIC unit): Max. CW<br>• Set an SSG as:<br>Level : 0.22 µV* (-13 dBµ)<br>• Receiving                                                                                                 | ļ             |                                                                                     | At the point where the audio signal just appears.          | LOGIC      | R91<br>(SQL)                                                   |

.

i,

6-