# **Technical Description**

The Equipment Under Test (EUT) is a Kitchen Radio with Bluetooth audio feature. The Bluetooth portion is operating between 2402MHz and 2480MHz (79 channels with 1MHz channel spacing). When the EUT is switched ON in Bluetooth mode, the display will show "BT" and a LED flashing. The Bluetooth enabled device would be searched and connected the EUT before playing audio. After pairing, the "BT" LED will stay lit. The audio signal will be amplified and fed to internal stereo loudspeaker. The EUT also have FM radio and timer clock function. A LED display acts as the visual interface. The EUT is powered by 5V DC from an AC/DC adaptor. The AC/DC adaptor can accept 100-240VAC.

# 2.4GHz Bluetooth Module: Modulation Type: GFSK

Antenna Type: Integral, Internal

Frequency Range: 2402MHz - 2480MHz, 1MHz channel spacing, 79 channels

Nominal field strength is 98.6dBµV/m @ 3m Production Tolerance of field strength is +/- 3dB Antenna gain is 0dBi

The functions of main ICs are mentioned below.

## 1. BlueTooth module CMD2022B (BT1):

- 1) IC3 (CW6638M) acts as the 2.4GHz radio core of Bluetooth module

- 2) IC2 (AX2225) is MCU integrating with audio DSP and CODEC.

- 3) IC4 (24C08) is 8k serial EEPROM for parameter storage.

- 4) Y2 (26MHz) crystal provides system clock for IC3.

- 5) X302 (32.768kHz) crystal provides system clock for IC2.

#### 2. AM/FM Radio Portion:

1) U3 (BK1080) acts as digital FM radio demodulator.

#### 3. MCU module:

- 1) U2 (HC180230A) acts as MCU core for the product.

- 2) Y202 (32.768kHz) acts as clock for the MCU core (U2).

### 4. Audio portion:

1) U1 (MC4863) is stereo 2W power amplifiers driving built-in loudspeakers.

### 5. Power Supply portion:

1) IC1 (JZ6206) is 3.3V voltage regulator.

# Channel Frequency Table of Bluetooth Module

| CH. NO. | FRE.     | Hex Value | CH. NO. | FRE.    | Hex Value  | CH. NO | FRE.     | Hex Value | CH. NO                                  | FRE.    | Hex Value |

|---------|----------|-----------|---------|---------|------------|--------|----------|-----------|-----------------------------------------|---------|-----------|

| CH0     | 2402MHz  | 0         | CH26    | 2428MHz | 1A         | CH52   | 2454MHz  | 34        | CH78                                    | 2480MHz | 4E        |

| CH1     | 2403MHz  | î î       | CH27    | 2429MHz | 1B         | CH53   | 2455MHz  | 35        | - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 |         |           |

| CH2     | 2404MHz  | 2         | CH28    | 2430MHz | 1C         | CH54   | 2456MHz  | 36        |                                         |         |           |

| CH3     | 2405MHz  | 3         | CH29    | 2431MHz | 1D         | CH55   | 2457MHz  | 37        |                                         |         | 3         |

| CH4     | 2406MHz  | 4         | CH30    | 2432MHz | 1E         | CH56   | 2458MHz  | 38        |                                         |         |           |

| CH5     | 2407MHz  | 5         | CH31    | 2433MHz | 1F         | CH57   | 2459MHz  | 39        |                                         |         |           |

| СН6     | 2408MHz  | 6         | CH32    | 2434MHz | 20         | CH58   | 2460MHz  | 3A        |                                         |         |           |

| CH7     | 2409MHz  | 7         | CH33    | 2435MHz | 21         | CH59   | 2461 MHz | 3B        |                                         |         |           |

| CH8     | 2410MHz  | 8         | CH34    | 2436MHz | 22         | CH60   | 2462MHz  | 3C        |                                         |         |           |

| CH9     | 2411MHz  | 9         | CH35    | 2437MHz | 23         | CH61   | 2463MHz  | 3D        |                                         |         |           |

| CH10    | 2412MHz  | A         | CH36    | 2438MHz | 24         | CH62   | 2464MHz  | 3E        |                                         |         |           |

| CH11    | 2413MHz  | В         | CH37    | 2439MHz | 25         | CH63   | 2465MHz  | 3F        |                                         |         |           |

| CH12    | 2414MHz  | C         | CH38    | 2440MHz | 26         | CH64   | 2466MHz  | 40        |                                         |         |           |

| CH13    | 2415MHz  | D         | CH39    | 2441MHz | 27         | CH65   | 2467MHz  | 41        |                                         |         |           |

| CH14    | 2416MHz  | E         | CH40    | 2442MHz | 28         | CH66   | 2468MHz  | 42        |                                         |         |           |

| CH15    | 2417MHz  | F         | CH41    | 2443MHz | 29         | CH67   | 2469MHz  | 43        |                                         |         |           |

| CH16    | 2418MHz  | 10        | CH42    | 2444MHz | 2A         | CH68   | 2470MHz  | 44        |                                         |         |           |

| CH17    | 2419MHz  | 11        | CH43    | 2445MHz | 2B         | CH69   | 2471MHz  | 45        |                                         |         |           |

| CH18    | 2420MHz  | 12        | CH44    | 2446MHz | 2C         | CH70   | 2472MHz  | 46        |                                         |         |           |

| CH19    | 2421 MHz | 13        | CH45    | 2447MHz | 2D         | CH71   | 2473MHz  | 47        |                                         |         |           |

| CH20    | 2422MHz  | 14        | CH46    | 2448MHz | 2E         | CH72   | 2474MHz  | 48        |                                         |         |           |

| CH21    | 2423MHz  | 15        | CH47    | 2449MHz | 2 <b>F</b> | CH73   | 2475MHz  | 49        |                                         |         |           |

| CH22    | 2424MHz  | 16        | CH48    | 2450MHz | 30         | CH74   | 2476MHz  | 4A        |                                         |         | (-        |

| CH23    | 2425MHz  | 17        | CH49    | 2451MHz | 31         | CH75   | 2477MHz  | 4B        |                                         |         | 7         |

| CH24    | 2426MHz  | 18        | CH50    | 2452MHz | 32         | CH76   | 2478MHz  | 4C        |                                         |         |           |

| CH25    | 2427MHz  | 19        | CH51    | 2453MHz | 33         | CH77   | 2479MHz  | 4D        |                                         |         |           |

# CMD2022B CW6638M

# Bluetooth Module

Rev 1.0 Mar 2013

# **Table of Contents**

| Chapter | 1   | Description                                   | 1 |

|---------|-----|-----------------------------------------------|---|

| Chapter | 2   | CMD2022B CW6638+AX2225A Features              | 1 |

| Chapter | 3   | Deminsion                                     | 2 |

| Chapter | 4   | Pin Assignment                                | 3 |

|         | 4.1 | CMD2022B CW6638+AX2225A Pin Assignment        | 4 |

| Chapter | 5   | Application                                   | 4 |

| Chapter | 6   | Application Schematic                         | 5 |

|         | 6.1 | CMD2022B CW6638+AX2225A Application Schematic |   |

# Module Description

CW6638+AX2225A is robust Bluetooth Audio Module which has rich functions targeted to small size portable Audio Boombox market. Incorporated with Appotech MP3 decode IC, CW6638+AX2225A is a highly competitive solution. CW6638M is Bluetooth 2.1 + EDR and also Bluetooth 3.0 compatible.

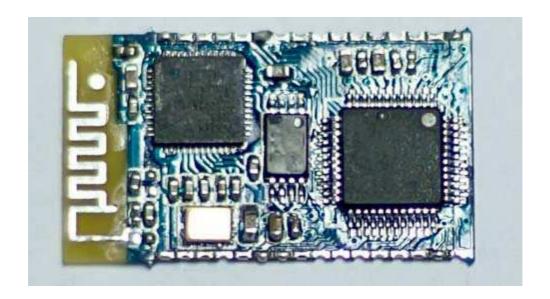

CMD2022B CW6638+AX2225A Module Photograph

CM**D2022B** CW6638 Module

# CMD2022 B-CW6638+AX2225A Module Characteristics

- **Support** USB, SD/TF card;

- Aux in with Volume Control; (three AUX\_IN Channels)

- Support external FM radio chip;

- Support IR remote function;

- Support buzz tone;

- Support USB card reader function, access SD, TF audio files;

- Support power ON/OFF function;

- Support AUDIO EQUALIZATION;

- Support USB Host;

- Support L2CAP/A2DP (AVCTP/AVDTP/AVRCP)

Audio files

- Support MCU, UART;

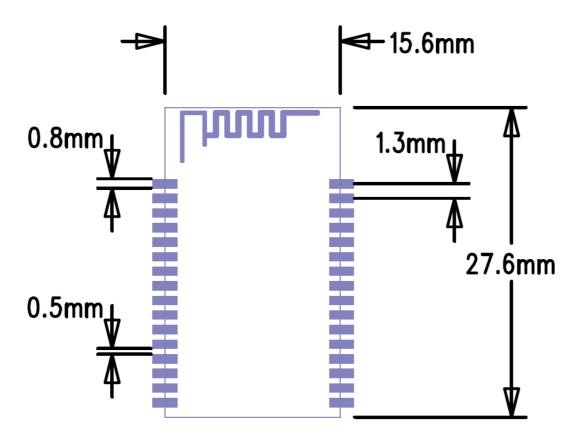

# Module Deminsion

| Module          | Demainsion                                                                      |

|-----------------|---------------------------------------------------------------------------------|

| CMD2022B CW6638 | $L \times W \times H = 27.6 \text{mm} \times 15.6 \text{mm} \times 2 \text{mm}$ |

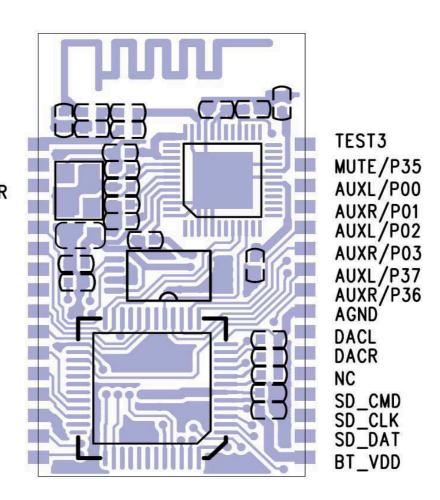

Pin Assignment CMD2022B- CW6638 Pin Assignment

ANT/RF

3V3

PLAY/PAUSE/PAIR

LED\_PLAY

TEST1

TEST2

12\_SDA

12\_SCL

NEXT

PREV

RTC

OSCI

OSCO

GND

USBDP

USBDM

| Pin | Name       | Function      | Description                                                |

|-----|------------|---------------|------------------------------------------------------------|

| 1   | RF_ANT     | RF_ANT        | External Antenna Port, NC if internal PCB antenna is used; |

| 2   | 3. 3V      | POWER         | 3. 3V output                                               |

| 3   | PLAY/PAUSE | Digital Input | PLAY/PAUSE                                                 |

| 4   | BT_LED     | Digital Input | Power On Indicator (Active High)                           |

| 5   | TEST1      | Digital I/O   | NC                                                         |

| 6   | TEST2      | Digital I/O   | NC                                                         |

| 7   | IIC_SDA    | Digital I/O   | IIC_SDA                                                    |

| 8   | IIC_SCL    | Digital I/O   | IIC_SCL                                                    |

| 9   | NEXT       | Digital I/O   | Next Track                                                 |

| 10  | PREV       | Digital I/O   | Previous Track                                             |

| 1.1 | DWG      | DOWED         | D 1 M; OI 1 (DOWND)                       |

|-----|----------|---------------|-------------------------------------------|

| 11  | RTC      | POWER         | Real Time Clock; (POWER)                  |

| 12  | 32KIN    | Digital Input | 32.768kH clock;                           |

| 13  | 32KOUT   | Digital out   | 32.768kHz clock output                    |

| 14  | GND      | POWER         | Power Ground;                             |

| 15  | USBDP    | Digital I/O   | USB DP                                    |

| 16  | USBDM    | Digital I/O   | USB DM                                    |

| 17  | BT_VDD   | POWER         | Module Power Input                        |

| 18  | SD_DAT   | Digital I/O   | SD/TF data;                               |

| 19  | SD_CLK   | Digital I/O   | SD/TF Clock;                              |

| 20  | SD_CMD   | Digital I/O   | SD/TF CMD;                                |

| 21  | NC       | Digital I/O   | NC                                        |

| 22  | DACR     | Digital OUT   | DAC Audio out R;                          |

| 23  | DACL     | Digital OUT   | DAC Audio out L;                          |

| 24  | AGND     | POWER         | Analog Ground;                            |

| 25  | AUXR/P37 | Digital Input | AUX1 R_input; or MCU UART (programmable); |

| 26  | AUXL/P36 | Digital Input | AUX1 L_input; or MCU UART (programmable); |

| 27  | AUXR/P03 | Digital Input | AUX2 R_input; or IO (programmable);       |

| 28  | AUXL/P02 | Digital Input | AUX2 L_input; or IO (programmable);       |

| 29  | AUXR/P01 | Digital Input | AUX3 R_input; or IO (programmable);       |

| 30  | AUXL/P00 | Digital Input | AUX3 L_input; or IO (programmable);       |

| 31  | MUTE/P35 | Digital OUT   | MUTE or IO (programmable)                 |

| 32  | TESR3    | Digital I/O   | test port                                 |

|     |          |               |                                           |

|     |          |               |                                           |

Note: Module IO is for 3.3V system,  $\,{\rm Don'}\,{\rm t}\,$  exceed 3.3V in application to avoid damage.

# Application

- Portable luetooth Audio

- Bluetooth MP3 Boombox

- Bluetooth Speaker

- Bluetooth Home Audio

- Hi-Fi Bluetooth Stereo

# Bluetooth Car Audio

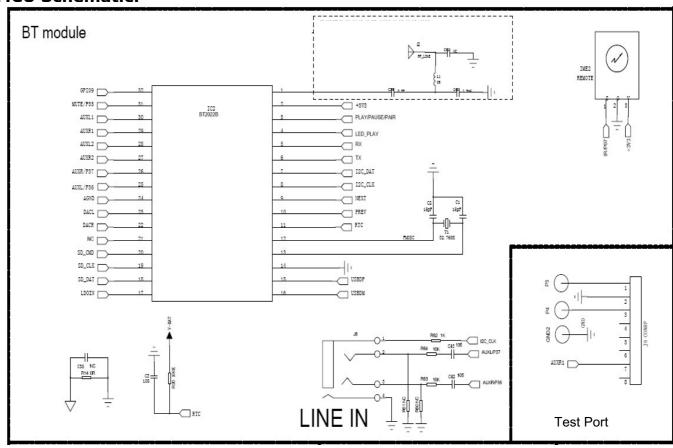

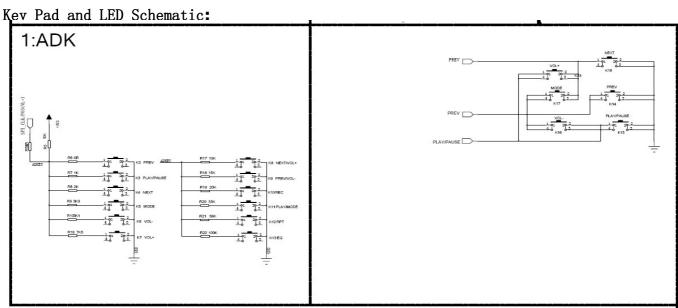

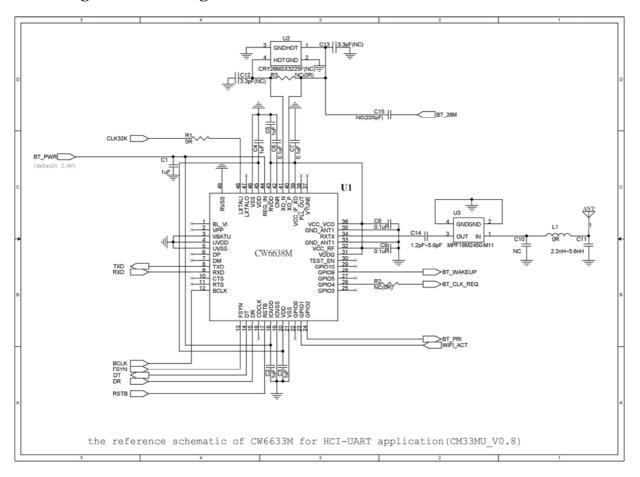

# CMD2022B CW6638 Application Schematic

# **MCU Schematic:**

(—): CMD2022B CW6638 Application Schematic

Ver. 1.0 June/28/2012

Page: 1 / 16

# Bluetooth 3.0 Single Chip for A2DP/AVRCP Solution

# **General Description**

The CONWISE CW6638M is a monolithic, single-chip, stand-alone baseband process with an integrated 2.4GHz transceiver including EDR to 3Mbits/s for Bluetooth v2.1+EDR and v3.0 applications. The CW6638M is also completely backward-compatible with Bluetooth 1.1/1.2/2.0 specification. It eliminates the need for external flash memories and active components into the device. Thus minimizing the footprint and system cost of implementing a Bluetooth system.

The CW6638M has been designed in CMOS RF technology, the most cost-performance effective silicon process today. This use of the advanced process enables the CW6638M to achieve the lowest cost total solution and maintain the possible lower current consumption in all modes of operation.

The CW6638M is the optimal solution for A2DP/AVRCP applications that requires the audio bitstream payload and remote control commands/ events via UART interface.

# **Features**

- Bluetooth specification version 3.0 compatible.

- Support ACL multi-slot packets for Data/Audio stream application.

- Support SCO/eSCO link with external PCM digital audio interface.

- Support high-speed UART baud rate of up to 3Mbps and USB2.0 full-speed compliant for HCI transport

- Support AFH for WiFi coexistence.

- Optimal 2-wire coexistence with WLAN.

- On-chip ROM eliminates dedicated flash memory chip, significantly lowering system BOM.

- Integrated 8-bit 8051 microprocessor core instead of ARM/MIPS such high cost processors.

- External Clock/Crystal 16, 26MHz system clocks are available to apply for system requirements.

- Optional external 32.768KHz crystal/clock for deep-low power mode using.

- Wide operation voltage: 2.2V~5.5V.

- Package types available

CW6638M: 48pin QFN package (6mm x 6mm)

# **Applications**

- Bluetooth speaker utilizing A2DP/AVRCP

- Audio system require audio source via Bluetooth from cellphone, PC

Doc.NO:DS6638M Page: 2 / 16 Ver. 1.0 June/28/2012

# **Revision History**

| Revision | Date       | Originator | Change Description             |

|----------|------------|------------|--------------------------------|

| V1.0     | 2012/06/28 | Jamic      | Draft version initial released |

Tel: 886-3-5719960

Fax: 886-3-5719969

Doc.NO:DS6638M

Ver. 1.0 June/28/2012

## 1. Overview

The CW6638M is Bluetooth Core Specification version 3.0 compliant and designed for used for Bluetooth Audio application. The combination of the Radio Transceiver, BBC and the 8051-based microcontroller-BLM, BIM with on-chip ROM provide a complete lower layer Bluetooth protocol stock including the link controller (LC), link manger (LM), A2DP sink and AVRCP. The major features of CW6638M are listed in section 1.1 and the usage models- Bluetooth Audio is described in following section 1.2.

#### 1.1. Features

Major features of the CW6638M include:

- Fully supports Bluetooth 3.0 features

- Adaptive Frequency Hopping (AFH)

- Scatter Mode

- QoS

- eSCO

- Fast Connect

- LMP improvements

- Synchronization

- Built-in regulators

- Built-in TR switch

- Maximum UART baud rates of 3 Mbps

- Support maximum Bluetooth data rates over UART interfaces

- HCI USB transport support with USB version 2.0 full-speed compliant interface

- High speed HCI UART transport support

- Channel quality driven data rate and package type selection

- Extended radio and production test mode features

- Full support for power saving modes

- Built-in LPO clock using external 32.768KHz crystal/clock

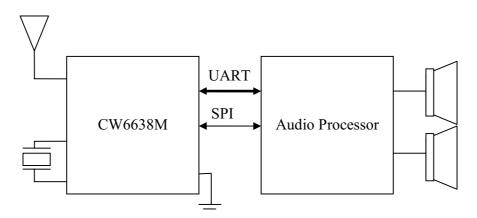

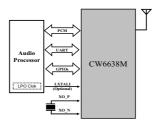

## 1.2. Bluetooth Audio Usage Model

The CW6638M is designed to provide direct interface to provide audio processor with audio bitstream transported via Bluetooth as show in figure 1. The CW6638M has very flexible PCM and UART interface enabling it to transparently connect with existing circuits. In addition, the low-cost crystal and external LPO (Low Power Oscillator) inputs allows to further minimizing the size, power and cost of the integration.

The CW6638M incorporates a number of unique features to accommodate the integration into audio playback platforms.

- The PCM interface provides multiple modes of operation to support both master and slave as well as interfacing to single external codec devices.

- The UART interface supports hardware flow control with tight integration to power control side band signalling to support the lowest power operation.

Doc.NO:DS6638M

Page: 4 / 16

Ver. 1.0 June/28/2012

- The XTAL oscillation circuit provides a dedicated 26MHz to accommodate the typical reference frequency used by mobile phone.

- A programmable XTAL power-up or power-down signal allows the device to indicate when the clock supplied to the CW6638M may be disabled for added power saving during sleep mode.

- Both the XTAL and external LPO inputs are high impedance inputs that have minimal loading on the driving source.

- The highly linear design of the radio transceiver ensures that the device has the lowest output spurious emissions regardless of the stat of operation and has been fully characterized in the global cellular bands.

- The transceiver design has excellent blocking (eliminating desensitization of the Bluetooth receiver) and inter-modulation performance (distortion of the transmitted signal caused by the mixing of the cellular and Bluetooth transmissions) in the presence of a any cellular transmission (GSM, GPRS, CDMA, WCDMA or TD-SCDMA). Minimal external filtering is required for integration inside the handset.

- Minimal external components are required for integration and very compact packaging is available.

Figure 1 Bluetooth Audio Model

Doc.NO:DS6638M Page: 5 / 16 Ver. 1.0 June/28/2012

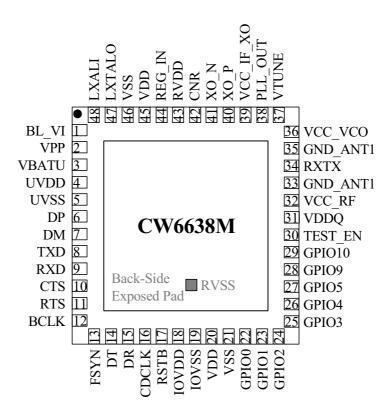

# 2. Pin Assignments

Figure 2 CW6638M 48-pin QFN6x6 Pin Diagram(Top-View)

**Table 1: Pin Description**

| Pin Number                        | Pin Name | I/O  | Power<br>Domain                                                                 | Description                          |

|-----------------------------------|----------|------|---------------------------------------------------------------------------------|--------------------------------------|

| Clock/Crystal Interface and Reset |          |      |                                                                                 |                                      |

| 40                                | XO_P     | I    | RVDD                                                                            | Crystal or frequency reference input |

| 41 XO_N O R                       |          | RVDD | Crystal Oscillator output. Connect with XO_P if the reference clock is supplied |                                      |

Page: 6 / 16 Ver. 1.0 June/28/2012

| 48                  | LXTALI           | I   | IOVDD | Low clock rate crystal driver input pin for 32.768KHz crystal or external clock input. Connect to IOVSS if no low clock is applied.                                                       |

|---------------------|------------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47                  | LXTALO           | О   | IOVDD | Low clock rate crystal driver output pin for 32.768KHz crystal driving. Leave unconnected if low clock is supplied.                                                                       |

| 17                  | RSTB             | I   | IOVDD | Active low system reset. This pin contains a weak pull-up.                                                                                                                                |

| Digital I/O and Cor | e Power Supplies |     |       |                                                                                                                                                                                           |

| 18                  | IOVDD            | I   | NA    | Power supply for GPIOs.                                                                                                                                                                   |

| 19                  | IOGND            | -   | NA    | Ground connection of GPIOs                                                                                                                                                                |

| 44                  | REG_IN           | I   | NA    | This pin serves as an input of the on-chip VDD and RVDD LDO regulators.                                                                                                                   |

| 20, 45              | VDD              | -   | NA    | On-chip 1.8V LDO output for digital core, this pin output typical voltage is 1.8V.                                                                                                        |

| 21, 46              | VSS              | -   | NA    | Ground connection of on-chip 1.8 VDD LDO                                                                                                                                                  |

| 2                   | VPP              | -   | VDD   | Internal OTP ROM power supply. This pin should be left unconnected in field application.                                                                                                  |

| RF Power Supplies   |                  |     |       |                                                                                                                                                                                           |

| 43                  | RVDD             | -   | NA    | On-chip 1.8V RVDD LDO output to supply internal RF                                                                                                                                        |

|                     |                  |     |       | circuits, this pin output typical voltage is 1.8V.                                                                                                                                        |

| Exposed Pad         | RVSS             | -   | NA    | Ground connection of on-chip 1.8V RVDD LDO                                                                                                                                                |

| 31                  | VDDQ             | I   | RVDD  | Digital block of RF circuit power supply. This pin must connect to RVDD.                                                                                                                  |

| 32                  | VCC_RF           | I   | RVDD  | RF circuit power supply. This pin must connect to RVDD.                                                                                                                                   |

| 36                  | VCC_VCO          | I   | RVDD  | VCO circuit power supply. This pin must connect to RVDD.                                                                                                                                  |

| 39                  | VCC_IF_XO        | I   | RVDD  | IF and internal Crystal Oscillator circuit power supply. This pin must connect to RVDD                                                                                                    |

| 42                  | CNR              | О   | RVDD  | On-Chip RVDD LDO external decoupling capacitor pir                                                                                                                                        |

| USB Power Supplie   |                  |     |       |                                                                                                                                                                                           |

| 3                   | VBATU            | -   | NA    | This pin serves as an input of the on-chip UVDD LOD regulators. Connect to UVSS if the USB interface is not used.                                                                         |

| 4                   | UVDD             | -   | NA    | On-chip 3.3V UVDD LDO output to supply USB transceiver.                                                                                                                                   |

| 5                   | UVSS             | -   | NA    | Ground connection of on-chip 3.3V UVDD LDO                                                                                                                                                |

| USB Interface       |                  |     |       |                                                                                                                                                                                           |

| 6                   | DP               | I/O | UVDD  | USB data plus pin for the HCI USB interface. This pin should be connected to UVSS if USB is not used.                                                                                     |

| 7                   | DM               | I/O | UVDD  | USB data minus pin for the HCI USB interface. This pin should be connected to UVSS if USB is not used.                                                                                    |

| UART Interface      |                  |     |       |                                                                                                                                                                                           |

| 8                   | TXD              | O   | IOVDD | UART Serial data output port for the HCI UART interface. This pin should be left unconnected if UART is not used or can be configured to the GPIO Pin 14.                                 |

| 9                   | RXD              | I   | IOVDD | UART Serial data input port for the HCI UART interface. This pin should be left unconnected if UART is not used or can be configured to the GPIO Pin 15                                   |

| 10                  | CTS              | I   | IOVDD | UART Clear to Send-active low for HCI UART interface when the hardware flow control feature enable This pin is used to set the system clock rate if the flow control feature is disabled. |

Tel: 886-3-5719960

Fax: 886-3-5719969

Page: 7 / 16 Ver. 1.0 June/28/2012

| 11                                | RTS              | O   | IOVDD | UART Request to Send-active low for HCI UART interface when the hardware flow control feature enable. This pin is used to set the system clock rate if the flow control feature is disabled. |

|-----------------------------------|------------------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Audio PCM Interfa                 | ace              |     |       |                                                                                                                                                                                              |

| 12                                | BCLK             | I/O | IOVDD | PCM serial data clock pin. In master mode, this is the clock output into the external HOST/CODEC. In clock slave mode, this is an input pin.                                                 |

| 13                                | FSYN             | О   | IOVDD | PCM serial data synchronization pin. In master mode, this is an 8Khz sync signal to synchronize the input and output serial data streams.                                                    |

| 14                                | DT               | О   | IOVDD | PCM serial data output pin. This data is clocked with BLCK, and first serial bit is synchronized by FSYN                                                                                     |

| 15                                | DR               | I   | IOVDD | PCM serial data input pin. This data is clocked with BLCK, and first serial bit is synchronized by FSYN                                                                                      |

| 16                                | CDCLK            | О   | IOVDD | External CODEC system clock. It can enable/disable to output the system clock to drive an external CODEC.                                                                                    |

| GPIO                              |                  |     |       |                                                                                                                                                                                              |

| 22, 23, 24, 25, 26,<br>27, 28, 29 | GPIO0~GPIO<br>10 | I/O | IOVDD | 3.3V tolerant GPIO pin with programmable pull-up.                                                                                                                                            |

| Radio                             |                  |     |       |                                                                                                                                                                                              |

| 33, 35                            | GND_ANT1         | -   | RVDD  | Ground connection of RF I/O antenna. These pins must connect to RVSS.                                                                                                                        |

| 34                                | RXTX             | -   | RVDD  | RF I/O antenna pin.                                                                                                                                                                          |

| 37                                | VTUNE            | I   | RVDD  | VCO tune input pin.                                                                                                                                                                          |

| 38                                | PLL_OUT          | О   | RVDD  | Charge Pump output                                                                                                                                                                           |

| <b>Battery-Low Detect</b>         | etor             |     |       |                                                                                                                                                                                              |

| 1                                 | BL_VI            | I   | VDD   | The input detection pin of Battery-Low Detector                                                                                                                                              |

| Reserved Pins                     |                  |     |       |                                                                                                                                                                                              |

| 30                                | TEST_EN          | I   | IOVDD | The test mode enable pin. This pin should be left unconnected for field application.                                                                                                         |

Doc.NO:DS6638M

Ver. 1.0 June/28/2012

# 3. Electrical Characteristics

# 3.1. Absolute Maximum Ratings

**Table 2: Maximum Electrical Rating**

| Rating                                      | Minimum   | Maximum   | Unit |

|---------------------------------------------|-----------|-----------|------|

| Storage temperature                         | -40       | +150      | °C   |

| Supply voltage of REG_IN                    | -0.4      | 5.5       | V    |

| Supply voltage of VBATU                     | -0.4      | 5.5       | V    |

| Supply voltage of UVDD                      | -0.4      | 4.0       | V    |

| Supply voltage of IOVDD                     | -0.4      | 4.0       | V    |

| Supply voltage of input/output Pin          | IOVSS-0.4 | IOVDD+0.4 | V    |

| Supply voltage of VDD                       | -0.4      | 3.0       | V    |

| Supply voltage of RVDD, VCC_RF, VCC_IF_VCO, | -0.4      | 3.0       | V    |

| VCC XO                                      |           |           |      |

# 3.2. Recommended Operating Conditions

**Table 3: Recommended Operating Conditions**

| Rating                                      | Minimum | Typical | Maximum |

|---------------------------------------------|---------|---------|---------|

| Operation temperature                       | 0 °C    | +25°C   | +70 °C  |

| Supply voltage of REG_IN                    | 2.2V    | 3.3V    | 5.5V    |

| Supply voltage of VBATU                     | 3.7V    | 5.0V    | 5.5V    |

| Supply voltage of UVDD                      | 2.8V    | 3.3V    | 3.6V    |

| Supply voltage of IOVDD                     | 1.7V    | 3.3V    | 3.6V    |

| Supply voltage of VDD                       | 1.7V    | 1.8V    | 2.0V    |

| Supply voltage of RVDD, VCC_RF, VCC_IF_VCO, | 1.7V    | 1.8V    | 2.0V    |

| VCC XO                                      |         |         |         |

# 3.3. Clocks

Table 4: Signal Specification of XO P/XO N Pin

| Crystal Oscillator                  | Minimum | Typical | Maximum |

|-------------------------------------|---------|---------|---------|

| Crystal frequency                   | -       | 26MHz   | -       |

| Crystal load capacitance            | 8pF     | 10pF    | 12pF    |

| Frequency tolerance                 |         |         | ±20ppm  |

| Digital trim range                  | 0pF     | -       | 3.1pF   |

| Digital trim step                   | -       | 100fF   | -       |

| External clock of XO_P <sup>1</sup> | Minimum | Typical | Maximum |

| Input frequency                     | -       | 26MHz   | -       |

| Clock input level                   | 0.8Vp-p | -       | RVDD    |

| XO_P input impedance                | 100ΚΩ   | -       | -       |

| XO_P input impedance                | -       | -       | 4pF     |

<sup>1.</sup> Connect XO\_N and XO\_P together when use external reference clock instead of crystal.

Table 5: Signal Specification of LXTALI/LXTALO Pin

| Crystal Oscillator | Minimum | Typical | Maximum |

|--------------------|---------|---------|---------|

|--------------------|---------|---------|---------|

Doc.NO:DS6638M

Page: 9 / 16

Ver. 1.0 June/28/2012

| Crystal frequency                     | -            | 32.768KHz                | -                 |

|---------------------------------------|--------------|--------------------------|-------------------|

| Crystal load capacitance              | =            | 20pF                     | -                 |

| Frequency tolerance                   |              |                          | ±200ppm           |

| E . III CIVIAII                       | 17           | T . 1                    | 3.6               |

| External clock of LXTALI <sup>1</sup> | Minimum      | Typical                  | Maximum           |

| Input frequency                       | Minimum<br>- | <i>Typical</i> 32.768KHz | Maximum<br>-      |

|                                       | - 0.8 x VDD  | V A                      | Maximum<br>-<br>- |

<sup>1.</sup> Leave LXTALO unconnected when use external reference clock instead of crystal.

# 3.4. Linear Regulator

## **Table 6: UVDD LDO**

| UVDD Liner Regulator                      | Minimum | Typical | Maximum |

|-------------------------------------------|---------|---------|---------|

| Input voltage                             | 3.7V    | -       | 5.5V    |

| Dropout voltage (I <sub>load</sub> =70mA) | -       | -       | 0.2V    |

| Output voltage (I <sub>load</sub> =70mA)  | -       | 3.3V    | -       |

| Temperature coefficient                   | -       | -       | -       |

| Output noise                              | -       | =       | -       |

| Load regulation (I <sub>load</sub> <70mA) | -       | -       | 200mV/A |

| Maximum output current                    | -       | -       | 70mA    |

| Quiescent current                         | -       | 7uA     | -       |

## **Table 7: VDD LDO**

| VDD Liner Regulator                       | Minimum | Typical | Maximum |

|-------------------------------------------|---------|---------|---------|

| Input voltage                             | 2.2V    | -       | 5.5V    |

| Dropout voltage (I <sub>load</sub> =70mA) | -       | -       | 0.2V    |

| Output voltage (I <sub>load</sub> =70mA)  | -       | 1.8V    | -       |

| Temperature coefficient                   | -       | -       | -       |

| Output noise                              | -       | =       | -       |

| Load regulation (I <sub>load</sub> <70mA) | -       | =       | 200mV/A |

| Maximum output current                    | -       | -       | 70mA    |

| Quiescent current                         | -       | 7uA     | -       |

# **Table 8: RVDD LDO**

| RVDD Liner Regulator                      | Minimum | Typical | Maximum |

|-------------------------------------------|---------|---------|---------|

| Input voltage                             | 2.2V    | -       | 5.5V    |

| Dropout voltage (I <sub>load</sub> =70mA) | -       | -       | 0.2V    |

| Output voltage (I <sub>load</sub> =70mA)  | -       | 1.8V    | -       |

| Temperature coefficient                   | -       | -       | -       |

| Output noise                              | -       | -       | -       |

| Load regulation (I <sub>load</sub> <70mA) | -       | -       | 200mV/A |

| Maximum output current                    | -       | -       | 80mA    |

| Quiescent current                         | -       | 20uA    | _       |

Tel: 886-3-5719960 Fax: 886-3-5719969 Doc.NO:DS6638M

Page: 10 / 16

Ver. 1.0 June/28/2012

# 3.5. Power Consumption

Table 9 shows the current consumption for (IOVDD/REG\_IN=2.8V, RVDD=1.8V, VDD=1.8V) (T<sub>A</sub>=25°C) (XO\_P=26MHz, LXTALI=GND) (UART HCI=921.6Kbps)

**Table 9: Typical Current Consumption**

| Operational Mode               | Minimum | Typical | Maximum |

|--------------------------------|---------|---------|---------|

| Page scan, time internal 1.28s | -       | 1mA     | -       |

| Inquiry                        | =       | 55mA    |         |

| Page scan and Inquiry          | =       | 1.6mA   | -       |

| ACL no traffic                 | -       | 26mA    | -       |

| ACL with file transfer         | -       | 47mA    | -       |

| SCO HV3                        | -       | 52mA    | -       |

| Sleep                          | -       | 80uA    | -       |

# 3.6. RF Specifications

**Table 10: Receiver RF specifications**

| Parameter                     |                                   | Minimum | Typical <sup>2</sup> | Maximum |

|-------------------------------|-----------------------------------|---------|----------------------|---------|

| Receiver Selection            |                                   |         |                      |         |

| Frequency range               |                                   | 2402MHz | -                    | 2480MHz |

| Rx sensitivity <sup>1</sup>   | GFSK, 0.1% BER                    | -88dBm  | -86dBm               | -84dBm  |

|                               | $\pi$ /4-DQPSK, 0.01% BER         | -       | -86dBm               | -       |

|                               | 8-DPSK, 0.01% BER                 | -       | -78dBm               | -       |

| Input IP3                     |                                   | -21dBm  | -                    | =       |

|                               | GFSK, 0.1% BER                    | -       | 0dBm                 | =       |

| Maximum input                 | $\pi$ /4-DQPSK, 0.1% BER          | -       | 0dBm                 | -       |

|                               | 8-DPSK, 0.1% BER                  | -       | -10dBm               | -       |

| Interference Performan        | ce                                |         |                      |         |

| C/I co-channel (GFSK, 0.      | 1%BER)                            | 11dB    | 10dB                 | -       |

| C/I 1 MHz adjacent chann      | nel (GFSK, 0.1% BER)              | -       | -1dB                 | 0dB     |

| C/I 2 MHz adjacent chann      | nel (GFSK, 0.1% BER)              | -       | -36dB                | -30dB   |

| C/I >= 3 MHz adjacent cha     | annel (GFSK, 0.1% BER)            | -       | -43dB                | -40dB   |

| C/I Image channel (GFSK       | <del>/ /</del>                    | -       | -15dB                | -9dB    |

| C/I co-channel (π/4-DQPS      | SK, 0.1% BER)                     | -       | 12dB                 | 13dB    |

|                               | nel (π/4-DQPSK, 0.1% BER)         | -       | -7dB                 | 0dB     |

| C/I 2 MHz adjacent chann      | nel (π/4-DQPSK, 0.1% BER)         | -       | -32dB                | -30dB   |

| C/I >= 3 MHz adjacent cha     | annel ( $\pi/4$ -DQPSK, 0.1% BER) | -       | -43dB                | -40dB   |

| C/I Image channel (π/4-D      | QPSK, 0.1%BER)                    | -       | -19dB                | -7dB    |

| C/I co-channel (8-DPSK,       | 0.1%BER)                          | -       | 20dB                 | 21dB    |

| C/I 1 MHz adjacent chann      | nel (8-DPSK, 0.1% BER)            | -       | 0dB                  | 5dB     |

| C/I 2 MHz adjacent chann      | nel (8-DPSK, 0.1% BER)            | -       | -27dB                | -25dB   |

| C/I >= 3 MHz adjacent cha     | annel (8-DPSK, 0.1% BER)          | _       | -35dB                | -33dB   |

| C/I Image channel (8-DPS      | SK, 0.1%BER)                      | -       | -13dB                | 0dB     |

| Intermodulation Perform       | nance                             |         |                      |         |

| Frequency range +3MHz~        | +6MHz offset (0.1% BER)           | -39dBm  | -                    | -       |

| <b>Out-of-Band Blocking P</b> | erformance (CW)                   |         |                      |         |

Doc.NO:DS6638M

Ver. 1.0 June/28/2012

| 30 MHz - 2000 MHz, 0.1% BER   | -10dBm | -3dBm  | _ |

|-------------------------------|--------|--------|---|

| 2000 MHz – 2399 MHz, 01% BER  | -27dBm | -13dBm |   |

| 2498 MHz – 3000 MHz, 0.1% BER | -27dBm | -14dBm | _ |

| 3000 MHz – 12.75GMz, 0.1% BER | -10dBm | -6dBm  | - |

| Spurious Emissions            |        |        |   |

| 30 MHz – 1 GHz                | -      | -      | - |

| 1 GHz -12.75 GHz              | -      | -      | - |

- 1. The receiver sensitivity is measured on the device interface.

- 2. Typical operating conditions are RVDD=1.8V operation voltage and 25°C ambient temperature.

- 3. The maximum value represents the actual Bluetooth specification required for Bluetooth qualification as defined in the version 3.0 specification.

**Table 11: Transmitter RF specifications**

| Parameter                      | Minimum      | Typical <sup>1</sup> | Maximum |

|--------------------------------|--------------|----------------------|---------|

| Transmitter Selection          |              |                      |         |

| Frequency range                | 2402MHz      | -                    | 2480MHz |

| Output power                   | -3dBm        | +1dBm                | +4dBm   |

| Output power level control     | 2dB          | 4dB                  | 8dB     |

| 20dB bandwidth output spectrum | -            | 780KHz               | 1000KHz |

| Frequency drift                |              |                      |         |

| DH1 packet                     | -            | 13KHz                | ±25KHz  |

| DH3 packet                     | -            | 15KHz                | ±40KHz  |

| DH5 packet                     | -            | 15KHz                | ±40KHz  |

| Modulation Index               | 0.28         | 0.32                 | 0.35    |

| Out-Band Spurious Emission     |              |                      |         |

| 30 MHz – 1 GHz idle mode       | -            | -                    | -57dBm  |

| 1 GHz -12.75 GHz idle mode     | <del>-</del> | -                    | -47dBm  |

| 1.8 GHz - 1.9 GHz              | -            | -                    | -57dBm  |

| 5.15 GHz -5.3 GHz              | -            | -                    | -47dBm  |

1. Typical operating conditions are RVDD=1.8V operation voltage and 25°C ambient temperature.

Tel: 886-3-5719960

Fax: 886-3-5719969

- 2. The maximum value represents the actual Bluetooth specification required for Bluetooth qualification as defined in the version 3.0 specification.

- 3. the RF characteristics are measured at the chip interface.

Doc.NO:DS6638M

Page: 12 / 16

Ver. 1.0 June/28/2012

# 4. Application Circuits

# 4.1. Usage Model through UART

Figure 3 The Application Circuit for Usage Model-UART

Doc.NO:DS6638M Page: 13 / 16 Ver. 1.0 June/28/2012

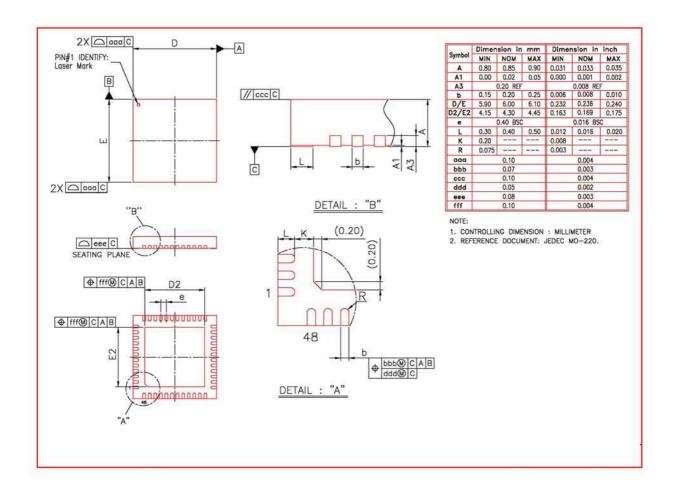

# 5. Mechanical Information

# 5.1. QFN6x6 48-pin Package Information

Figure 4 CW6638M 48-pin, 6 x 6 x 0.85mm, 0.4mm-pitch QFN Package Dimension

Page: 14 / 16 Ver. 1.0 June/28/2012

C: Firmware version code(ROM)

Tel: 886-3-5719960

Fax: 886-3-5719969

D: Date code

P: Package vendor code V: Hardware version code

L: Lot number

Figure 5 CW6638M Product Marking

Doc.NO:DS6638M

Page: 15 / 16

Ver. 1.0 June/28/2012

# 6. Ordering Information

|                      | Package        |                 | 0.1.37.1     |

|----------------------|----------------|-----------------|--------------|

| Type                 | Size           | Shipment Method | Order Number |

| 48-Pin QFN (Pb free) | 6 x 6 x 0.85mm | Tape&Reel       | CW6638M      |

# **Minimum Order Quantity**

Tape & Reel: 3Kpcs/reel

Tel: 886-3-5719960

Fax: 886-3-5719969

Doc.NO:DS6638M Page: 16 / 16 Ver. 1.0 June/28/2012

# **Contact Information**

**CONWISE Technology, Ltd.**

8F, No.47, Lane 2, Kwang-Fu Rd. Sec. 2, Hsin-Chu City,

Taiwan 30071

Tel: +886 3 5719960 Fax: +886 3 5719969

e-mail: sales@conwise.com.tw

Information given in this document is believed to be accurate and reliable at the time of printing; however, CONWISE reserves the right to make changes to products and specifications without notice.

CONWISE makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does CONWISE assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental dmange.

Tel: 886-3-5719960

Fax: 886-3-5719969