# FSC-BT906

# 4.2 Dual Mode Bluetooth Module Data Sheet

Document Type: FSC-BT906

Document Version: V1.8

Release Date: April.30. 2019

| Version Number | Release Date | Comments                               |

|----------------|--------------|----------------------------------------|

| Revision 1.0   | 2016-08-27   | First Release                          |

| Revision 1.1   | 2016-09-21   | Update the circuit diagram             |

| Revision 1.2   | 2016-12-08   | 1, modify the pin definition and       |

|                |              | application circuit diagram            |

|                |              | 2, increase the electric performance   |

|                |              | parameters                             |

| Revision 1.3   | 2018-02-26   | Modify the 9,10,14,27,28,31 pin        |

|                |              | description                            |

| Revision 1.4   | 2018-05-05   | Modify Bluetooth Version: Upgrade from |

|                |              | BT4.0 to BT4.2                         |

| Revision 1.5   | 2019-02-22   | Clarify HID/SPP profiles.              |

| Revision 1.6   | 2019-08-29   | Add certificate picture                |

| Revision 1.7   | 2019-10-18   | Feature update                         |

| Revision 1.8   | 2020-04-30   | Increase power consumption parameters  |

# **Release Record**

# 1. INTRODUCTION

FSC-BT906 is a bluetooth 4.2 Smart Ready device (with BR/EDR & LE support simultaneou sly). It is a small form factor, highly power and highly economic Bluetooth radio module that allows OEM to add wireless capability to their products. The module supports multiple interfaces that make it simple to integrate into fully certified embedded Bluetooth solutions.

With AT programming interfaces, designers can easily customize their applications to support different Bluetooth profiles, such HS/HF, A2DP, AVRCP, OPP, DUN, SPP, and etc. The module supports Bluetooth® Enhanced Data Rate (EDR) and delivers up to 3 Mbps data rate for distances to 10M.

The module is an appropriate product for designers who want to add wireless capability to their products. The supported remote devices' OS are iOS, Android, and Windows.

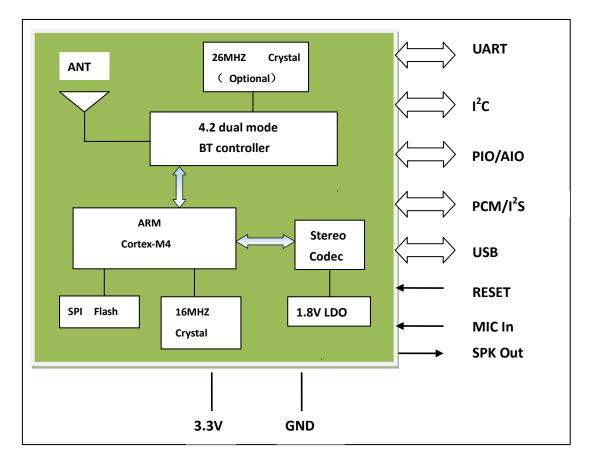

# 1.1 Block Diagram

# 1.2 Feature

- Fully qualified Bluetooth 4.2/3.0/2.1/2.0/1.2/1.1

- Postage stamp sized form factor,

- Low power

- Class 1.5 support(high output power)

- The default UART Baud rate is 115.2Kbps and can support from 1200bps up to 921Kbps,.

- ◆ UART, I<sup>2</sup>C, PCM/I<sup>2</sup>S data connection interfaces.

- Profiles including HS/HF, A2DP, AVRCP, OPP, DUN, SPP, HID, BLE

- USB 2.0 full-speed device/host/OTG controller

- RoHS compliant

- KC Certified

- Power Consumption In Sleep Mode (VDD\_3V3 at 3.3 V)

- Discoverable: 1.73mA

- BR/EDR Connection: 11.12mA

- LE Connection: 2.46mA

- Power Consumption In Working Mode (VDD\_3V3 at 3.3 V)

- Discoverable: 11.56mA

- BR/EDR Connection: 20.95mA

- LE Connection: 12.08mA

# 1.3 Application

- Portable Multimedia players

- High quality stereo headsets

- High quality mono headsets

- Hands-free car kits

- Wireless speakers

- Bluetooth-Enable Automotive Dashboards

- VOIP handsets

- Analogue and USB Multimedia Dongles

- Medical devices

- Barcode and RFID scanners

# 2. GENERAL SPECIFICATION

| General Specification   |                                                       |  |  |

|-------------------------|-------------------------------------------------------|--|--|

| ChipSet                 | BT4.2 Dual Mode                                       |  |  |

| Product ID              | FSC-BT906                                             |  |  |

| Dimension               | 13mm(W) x 26.9mm(L) x 2.4mm(H)<br>(Tolerance: ±0.1mm) |  |  |

| Bluetooth Specification | Bluetooth V4.2 (Dual Mode)                            |  |  |

| Power Supply            | 3.3 Volt DC                                           |  |  |

| Output Power            | 8.5 dBm (Class 1.5)                                   |  |  |

| Sensitivity             | -88dBm@0.1%BER                                        |  |  |

| Frequency Band          | 2.402GHz -2.480GHz ISM band                           |  |  |

| Modulation           | 8DPSK,DQPSK,GFSK                        |  |

|----------------------|-----------------------------------------|--|

| Baseband Crystal OSC | 16MHz                                   |  |

|                      | 1600hops/sec, 1MHz channel space,79     |  |

| Hopping & channels   | Channels(BT 4.2 to 2MHz channel space)  |  |

| RF Input Impedance   | 50 ohms                                 |  |

| Antenna              | FPC Antenna                             |  |

|                      | Data: UART (Standard), I <sup>2</sup> C |  |

|                      | Audio: MIC In/SPK Out (Standard),       |  |

| Interface            | PCM/I <sup>2</sup> S                    |  |

|                      | Others: PIO, AIO, Touch sensor, PWM.    |  |

|                      | USB 2.0                                 |  |

|                      | SPP, GATT(BLE Standard)                 |  |

| Profile              | MFI, Airsync, ANCS, iBeacon, HID        |  |

|                      | HS/HF, A2DP, AVRCP                      |  |

| Temperature          | -40°C to +85°C                          |  |

| Humidity             | 10%~95% Non-Condensing                  |  |

| Environmental        | RoHS Compliant                          |  |

| MSL grade:           | MSL 3                                   |  |

|                      | Human Body Model: Class-2               |  |

| ESD grade            | Machine Model: Class-B                  |  |

Table 1

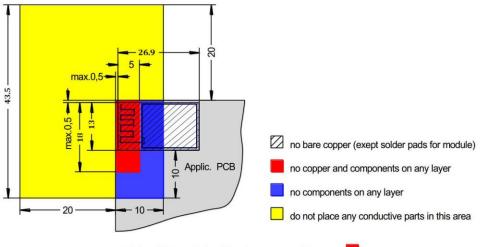

# 3. PHYSICAL CHARACTERISTIC

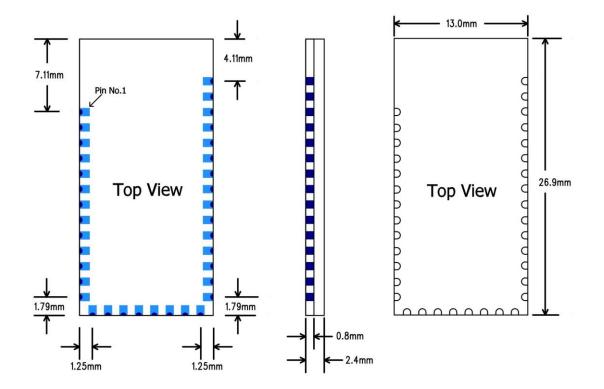

- Dimension: 13mm(W) x 26.9mm(L) x 2.4mm(H) Tolerance: ±0.1mm

- Module size: 13mm X 26.9mm Tolerance: ±0.2mm

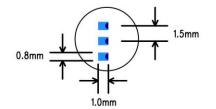

- Pad size: 1mmX0.8mm Tolerance: ±0.2mm

- Pad pitch: 1.5mm Tolerance:  $\pm$ 0.1mm

Figure 2

# 4. PIN DEFINITION DESCRIPTIONS

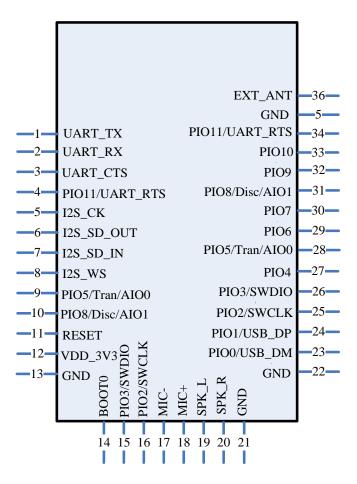

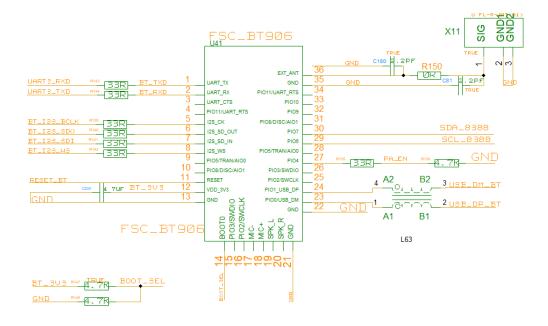

Figure 3: FSC-BT906 PIN Diagram

| Pin NO. | Pin Name                             | Туре                  | Pin Descriptions                                              |  |

|---------|--------------------------------------|-----------------------|---------------------------------------------------------------|--|

| 1       | UART_TX                              | CMOS output           | UART data output                                              |  |

| 2       | UART_RX                              | CMOS input            | UART data input                                               |  |

| 2       |                                      | CMOS input            | UART clear to send active low                                 |  |

| 3       | 3 UART_CTS CMOS input Alternative Fu |                       | Alternative Function: Programmable input/output line          |  |

|         | PIO11/UART_                          | CMOS output/          | UART request to send active low                               |  |

| 4       | 4 RTS Bi-                            |                       | Alternative Function: Programmable input/output line          |  |

| 5       | I2S_CK                               | <b>Bi-directional</b> | I <sup>2</sup> S CLK (BCLK)                                   |  |

| 6       | I2S_SD_OUT                           | <b>Bi-directional</b> | I <sup>2</sup> S Data Output                                  |  |

| 7       | I2S_SD_IN                            | <b>Bi-directional</b> | I <sup>2</sup> S Data Input                                   |  |

| 8       | I2S_WS                               | <b>Bi-directional</b> | I <sup>2</sup> S Chip Select For Synchronous Serial Interface |  |

| 9         PIOS/Tran/AIO<br>0         I/O         Alternative Function 1: Analogue programmable i/O line.<br>Alternative Function 2: Host MCU change UART<br>transmission mode.           10         PIO8/Disc/AIO<br>1         I/O         Programmable input/output line<br>Alternative Function 2: Host MCU disconnect bluetooth.<br>Alternative Function 2: Host MCU disconnect bluetooth.           11         RESET         CMOS input         Reset If low. Input debounced so must be low for >5ms to<br>cause a reset.           12         VDD_3V3         VDD         Power supply voltage 3.3V           13         GND         VSS         Power Ground           14         BOOT0         CMOS input         The default is low. (internal 10K resistance drop)           14         BOOT0         CMOS input         UART DFU Mode, Enabled at startup when set to high<br>level, Disabled by default           15         PIO3/SWDI0         Bi-directional         The default is low. (internal 10K resistance drop)           16         PIO2/SWCLK         Bi-directional         Debugging through the data line(Default)           17         MIC-         Analogue Input         MIC- Input           18         MIC+         Analogue Output         Left Output (Line or Headphone )           20         SPK_R         Analogue Output         Left Output (Line or Headphone )           21         GND         VSS <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |               |                       |                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|-----------------------|---------------------------------------------------------|

| 9         PLOS frait/NO         I/O         Alternative Function 2: Host MCU change UART transmission mode.           10         PIO8/Disc/AIO         I/O         Alternative Function 1: Analogue programmable i/O line. Alternative Function 2: Host MCU disconnect bluetooth. Alternative Function 2: Host MCU disconnect bluetooth.           11         RESET         CMOS input         Reset if Iow. Input debounced so must be Iow for >5ms to cause a reset.           12         VDD_3V3         VDD         Power supply voltage 3.3V           13         GND         VSS         Power Ground           14         BOOT0         CMOS input         The default is Iow. (internal 10K resistance drop)           14         BOOT0         CMOS input         UART DFU Mode, Enabled at startup when set to high Ievel, Disabled by default           15         PIO3/SWDIO         Bi-directional         Debugging through the data line(Default) Alternative Function: Programmable input/output line           17         MIC-         Analogue Output         MIC- Input           18         MIC+         Analogue Output         Right Output (Line or Headphone )           20         SPK_L         Analogue Output         Right Output (Line or Headphone )           21         GND         VSS         Power Ground           22         GND         VSS         Power Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |               |                       |                                                         |

| 0         Alternative Function 2: Host MCU charge UAR1           10         PIO8/Disc/AIO           10         1           11         RESET           12         VDD_3V3           13         GND           13         GND           14         BOOTO           15         PIO3/SWDIO           16         PIO2/SWCLK           17         MIC-           18         MIC-           19         SPK_L           10         PIO2/SWCLK           11         Rest if Iow. Input           12         VDD_3V3           VDD         Power supply voltage 3.3V           13         GND           14         BOOTO           CMOS input         UART DFU Mode, Enabled at startup when set to high<br>level, Disabled by default           15         PIO3/SWDIO           Bi-directional         Debugging through the data line(Default)           Atternative Function: Programmable input/output line           17         MIC-           18         MIC+           MIC-         Analogue Input           MIC-         Analogue Output           19         SPK_L           Analogue Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ٥          | PIO5/Tran/AIO |                       |                                                         |

| PIO8/Disc/AIO         I/O         Programmable input/output line<br>Atternative Function 1: Analogue programmable I/O line.<br>Atternative Function 2: Host MCU disconnect bluetooth.           11         RESET         CMOS input         Reset if Iow. Input debounced so must be low for >5ms to<br>cause a reset.           12         VDD_3V3         VDD         Power supply voltage 3.3V           13         GND         VSS         Power Ground           14         BOOTO         CMOS input         UART DFU Mode, Enabled at startup when set to high<br>level, Disabled by default           15         PIO3/SWDIO         Bi-directional         Debugging through the data line(Default)<br>Atternative Function: Programmable input/output line           16         PIO2/SWCLK         Bi-directional         MIC- Input           18         MIC+         Analogue Input         MIC- Input           19         SPK_L         Analogue Output         Right Output (Line or Headphone )           20         SPK_R         Analogue Output         Right Output (Line or Headphone )           21         GND         VSS         Power Ground           22         GND         VSS         Power Ground           23         PIO0/USB_D         Bi-directional         Reset Function: USB_D DM           24         PIO1/USB_DP         Bi-directional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3          | 0             | 1/0                   | Alternative Function 2: Host MCU change UART            |

| 10         PIO8/Disc/AIO         I/O         Alternative Function 1: Analogue programmable I/O line.<br>Alternative Function 2: Host MCU disconnect bluetooth.           11         RESET         CMOS input         Reset if low. Input debounced so must be low for >5ms to<br>cause a reset.           12         VDD_3V3         VDD         Power supply voltage 3.3V           13         GND         VSS         Power Ground           14         BOOT0         CMOS input         UART DFU Mode, Enabled at starup when set to high<br>level, Disabled by default           15         PIO3/SWDIO         Bi-directional         Debugging through the data line/Default)<br>Alternative Function: Programmable input/output line           16         PIO2/SWCLK         Bi-directional         MIC- Input           18         MIC+         Analogue Input         MIC- Input           19         SPK_L         Analogue Output         Right Output (Line or Headphone )           20         SPK_R         Analogue Output         Right Output (Line or Headphone )           21         GND         VSS         Power Ground           22         GND         VSS         Power Ground           23         PIO0/USB_D         Bi-directional         Alternative Function: USB_DM           24         PIO1/USB_DP         Bi-directional         Alte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |               |                       |                                                         |

| 1         Atternative Function 2: Host MCU disconnect bluetooth.           11         RESET         CMOS input         Reset if low. Input debounced so must be low for >5ms to cause a reset.           12         VDD_3V3         VDD         Power supply voltage 3.3V           13         GND         VSS         Power Ground           14         BOOTO         CMOS input         UART DFU Mode, Enabled at startup when set to high level, Disabled by default           15         PIO3/SWDIO         Bi-directional         The default is low. (internal 10K resistance drop)           16         PIO2/SWCLK         Bi-directional         Debugging through the data line(Default)           17         MIC-         Analogue Input         MIC- Input           18         MIC+         Analogue Input         MIC+ Input           19         SPK_L         Analogue Output         Right Output (Line or Headphone )           20         SPK_R         Analogue Output         Right Output (Line or Headphone )           21         GND         VSS         Power Ground           22         GND         VSS         Power Ground           23         PIO0/USB_D         Bi-directional         Programmable input/output line           24         PIO1/USB_DP         Bi-directional         Pr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            | PIO8/Disc/AIO |                       |                                                         |

| 11         RESET         CMOS input         Reset if low. Input debounced so must be low for >5ms to cause a reset.           12         VDD_3V3         VDD         Power supply voltage 3.3V           13         GND         VSS         Power Ground           14         BOOT0         CMOS input         UART DFU Mode, Enabled at startup when set to high level, Disabled by default           15         PIO3/SWDIO         Bi-directional         Debugging through the data line(Default) Alternative Function: Programmable input/output line           16         PIO2/SWCLK         Bi-directional         MIC- Input           17         MIC-         Analogue Input         MIC- Input           18         MIC+         Analogue Output         Right Output (Line or Headphone )           20         SPK_R         Analogue Output         Right Output (Line or Headphone )           21         GND         VSS         Power Ground           22         GND         VSS         Power Ground           23         PIO0/USB_D         Bi-directional         Alternative Function: USB_DM           24         PIO1/USB_DP         Bi-directional         Alternative Function: USB_DP           25         PIO2/SWCLK         Bi-directional         Alternative Function: USB_DP           26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10         | 1             | I/O                   |                                                         |

| 11     RESET     CMOS input     cause a reset.       12     VDD_3V3     VDD     Power supply voltage 3.3V       13     GND     VSS     Power Ground       14     BOOT0     CMOS input     The default is low. (internal 10K resistance drop)       14     BOOT0     CMOS input     UART DFU Mode, Enabled at startup when set to high<br>level, Disabled by default       15     PIO3/SWDIO     Bi-directional     Debugging through the data line(Default)<br>Alternative Function: Programmable input/output line       16     PIO2/SWCLK     Bi-directional     Debugging through the cik line(Default)<br>Alternative Function: Programmable input/output line       17     MIC-     Analogue Input     MIC- Input       18     MIC+     Analogue Output     Right Output (Line or Headphone )       20     SPK_R     Analogue Output     Left Output (Line or Headphone )       21     GND     VSS     Power Ground       22     GND     VSS     Power Ground       23     PIO0/USB_D<br>M     Bi-directional     Programmable input/output line<br>Alternative Function: USB_DM       24     PIO1/USB_DP     Bi-directional     Programmable input/output line<br>Alternative Function: USB_DP       25     PIO2/SWCLK     Bi-directional     Debugging through the cik line(Default)<br>Alternative Function: Programmable input/output line       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |               |                       |                                                         |

| 12         VDD_3V3         VDD         Power supply voltage 3.3V           13         GND         VSS         Power Ground           14         BOOT0         CMOS input         The default is low. (internal 10K resistance drop)           14         BOOT0         CMOS input         UART DFU Mode, Enabled at startup when set to high level, Disabled by default           15         PIO3/SWDIO         Bi-directional         Debugging through the data line(Default) Alternative Function: Programmable input/output line           16         PIO2/SWCLK         Bi-directional         Debugging through the clk line(Default) Alternative Function: Programmable input/output line           17         MIC-         Analogue Input         MIC- Input           18         MIC+         Analogue Output         Right Output (Line or Headphone )           20         SPK_R         Analogue Output         Left Output (Line or Headphone )           21         GND         VSS         Power Ground           22         GND         VSS         Power Ground           23         PIO0/USB_D         Bi-directional         Programmable input/output line           24         PIO1/USB_DP         Bi-directional         Programmable input/output line           25         PIO2/SWCLK         Bi-directional         Debugging thro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11         | RESET         | CMOS input            |                                                         |

| 13         GND         VSS         Power Ground           14         BOOT0         CMOS input         The default is low. (internal 10K resistance drop)           14         BOOT0         CMOS input         UART DFU Mode, Enabled at startup when set to high<br>level, Disabled by default           15         PIO3/SWDI0         Bi-directional         Debugging through the data line(Default)<br>Alternative Function: Programmable input/output line           16         PIO2/SWCLK         Bi-directional         Debugging through the clk line(Default)<br>Alternative Function: Programmable input/output line           17         MIC-         Analogue Input         MIC- Input           18         MIC+         Analogue Output         Right Output (Line or Headphone )           20         SPK_R         Analogue Output         Left Output (Line or Headphone )           21         GND         VSS         Power Ground           22         GND         VSS         Power Ground           23         PIO0/USB_D<br>M         Bi-directional         Programmable input/output line<br>Alternative Function: USB_DM           24         PIO1/USB_DP         Bi-directional         Programmable input/output line<br>Alternative Function: Programmable input/output line           26         PIO3/SWDIO         Bi-directional         Debugging through the clk line(Default)<br>Alternative Functi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |               |                       | cause a reset.                                          |

| 14         BOOT0         CMOS input         The default is low. (internal 10K resistance drop)           14         BOOT0         CMOS input         UART DFU Mode, Enabled at startup when set to high<br>level, Disabled by default           15         PIO3/SWDI0         Bi-directional         Debugging through the data line(Default)<br>Alternative Function: Programmable input/output line           16         PIO2/SWCLK         Bi-directional         Debugging through the clk line(Default)<br>Alternative Function: Programmable input/output line           17         MIC-         Analogue Input         MIC- Input           18         MIC+         Analogue Output         Right Output (Line or Headphone )           20         SPK_R         Analogue Output         Left Output (Line or Headphone )           21         GND         VSS         Power Ground           22         GND         VSS         Power Ground           23         PIO0/USB_D<br>M         Bi-directional         Programmable input/output line<br>Alternative Function: USB_DM           24         PIO1/USB_DP         Bi-directional         Programmable input/output line<br>Alternative Function: Programmable input/output line           26         PIO3/SWDIO         Bi-directional         Debugging through the data line(Default)<br>Alternative Function: Programmable input/output line           27         PIO4         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12         | VDD_3V3       | VDD                   | Power supply voltage 3.3V                               |

| 14     BOOT0     CMOS input     UART DFU Mode, Enabled at startup when set to high<br>level, Disabled by default       15     PIO3/SWDIO     Bi-directional     Debugging through the data line(Default)<br>Atternative Function: Programmable input/output line       16     PIO2/SWCLK     Bi-directional     Debugging through the clk line(Default)<br>Atternative Function: Programmable input/output line       17     MIC-     Analogue Input     MIC- Input       18     MIC+     Analogue Input     MIC- Input       19     SPK_L     Analogue Output     Right Output (Line or Headphone )       20     SPK_R     Analogue Output     Left Output (Line or Headphone )       21     GND     VSS     Power Ground       22     GND     VSS     Power Ground       23     PIO0/USB_D<br>M     Bi-directional     Alternative Function: USB_DM       24     PIO1/USB_DP     Bi-directional     Programmable input/output line<br>Alternative Function: USB_DP       25     PIO2/SWCLK     Bi-directional     Alternative Function: Programmable input/output line<br>Alternative Function: Programmable input/output line       26     PIO3/SWDIO     Bi-directional     Debugging through the data line(Default)<br>Alternative Function: Programmable input/output line       27     PIO4     Bi-directional     Programmable input/output line       28     PIO5/Tran/AIO     I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13         | GND           | VSS                   | Power Ground                                            |

| Image: Constraint of the state of |            |               |                       | The default is low. (internal 10K resistance drop)      |

| 15     PIO3/SWDIO     Bi-directional     Debugging through the data line(Default)<br>Alternative Function: Programmable input/output line       16     PIO2/SWCLK     Bi-directional     Debugging through the clk line(Default)<br>Alternative Function: Programmable input/output line       17     MIC-     Analogue Input     MIC- Input       18     MIC+     Analogue Input     MIC+ Input       19     SPK_L     Analogue Output     Right Output (Line or Headphone )       20     SPK_R     Analogue Output     Left Output (Line or Headphone )       21     GND     VSS     Power Ground       22     GND     VSS     Power Ground       23     PIO0/USB_D<br>M     Bi-directional     Programmable input/output line<br>Alternative Function: USB_DM       24     PIO1/USB_DP     Bi-directional     Programmable input/output line<br>Alternative Function: USB_DP       25     PIO2/SWCLK     Bi-directional     Debugging through the clk line(Default)<br>Alternative Function: Programmable input/output line       26     PIO3/SWDIO     Bi-directional     Programmable input/output line<br>Alternative Function: Programmable input/output line       27     PIO4     Bi-directional     Programmable input/output line       28     PIO5/Tran/AIO     I/O     Programmable input/output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14         | BOOT0         | CMOS input            | UART DFU Mode, Enabled at startup when set to high      |

| 15     PIO3/SWDIO     Bi-directional     Atternative Function: Programmable input/output line       16     PIO2/SWCLK     Bi-directional     Debugging through the clk line(Default)<br>Atternative Function: Programmable input/output line       17     MIC-     Analogue Input     MIC- Input       18     MIC+     Analogue Input     MIC- Input       19     SPK_L     Analogue Output     Right Output (Line or Headphone )       20     SPK_R     Analogue Output     Left Output (Line or Headphone )       21     GND     VSS     Power Ground       22     GND     VSS     Power Ground       23     PIO0/USB_D<br>M     Bi-directional     Programmable input/output line       24     PIO1/USB_DP     Bi-directional     Programmable input/output line       25     PIO2/SWCLK     Bi-directional     Debugging through the clk line(Default)       26     PIO3/SWDIO     Bi-directional     Debugging through the data line(Default)       27     PIO4     Bi-directional     Programmable input/output line       27     PIO4     Bi-directional     Programmable input/output line       28     PIO5/Tran/AIO     I/O     Programmable input/output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |               |                       | level, Disabled by default                              |

| 10       Alternative Function: Programmable input/output line         16       PIO2/SWCLK       Bi-directional       Debugging through the clk line(Default)         17       MIC-       Analogue Input       MIC- Input         18       MIC+       Analogue Input       MIC+ Input         19       SPK_L       Analogue Output       Right Output (Line or Headphone )         20       SPK_R       Analogue Output       Left Output (Line or Headphone )         21       GND       VSS       Power Ground         22       GND       VSS       Power Ground         23       PIO0/USB_D<br>M       Bi-directional       Programmable input/output line         24       PIO1/USB_DP       Bi-directional       Programmable input/output line         25       PIO2/SWCLK       Bi-directional       Debugging through the clk line(Default)         26       PIO3/SWDIO       Bi-directional       Debugging through the data line(Default)         Alternative Function: Programmable input/output line       Debugging through the data line(Default)         27       PIO4       Bi-directional       Programmable input/output line         26       PIO3/SWDIO       Bi-directional       Programmable input/output line         27       PIO4       Bi-directional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.5        |               | <b>Bi-directional</b> | Debugging through the data line(Default)                |

| 16PIO2/SWCLKBi-directionalAtternative Function: Programmable input/output line17MIC-Analogue InputMIC- Input18MIC+Analogue InputMIC+ Input19SPK_LAnalogue OutputRight Output (Line or Headphone )20SPK_RAnalogue OutputLeft Output (Line or Headphone )21GNDVSSPower Ground22GNDVSSPower Ground23PIO0/USB_D<br>MBi-directionalProgrammable input/output line<br>Alternative Function: USB_DM24PIO1/USB_DP<br>MBi-directionalProgrammable input/output line<br>Alternative Function: USB_DP25PIO2/SWCLKBi-directionalDebugging through the clk line(Default)<br>Alternative Function: Programmable input/output line<br>Alternative Function: Programmable input/output line26PIO3/SWDIOBi-directionalProgrammable input/output line<br>Alternative Function: Programmable input/output line<br>Alternative Function: Programmable input/output line27PIO4Bi-directionalProgrammable input/output line<br>Alternative Function: PA_EN pin, active high28PIO5/Tran/AIOI/OProgrammable input/output line<br>Alternative Function: PA_EN pin, active high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15         | F105/3WD10    | Di-unectional         |                                                         |

| Atternative Function: Programmable input/output line17MIC-18MIC+18MIC+19SPK_L19SPK_R20SPK_R20SPK_R21GND22GND23PIO0/USB_D<br>M24PIO1/USB_DP25PIO2/SWCLK26PIO2/SWCLK27PIO3/SWDIO27PIO428PIO5/Tran/AIO28PIO5/Tran/AIO28PIO5/Tran/AIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16         | PIO2/SWCLK    | <b>Bi-directional</b> |                                                         |

| Indication       Indication       MIC+       Analogue Input       MIC+ Input         18       MIC+       Analogue Input       MIC+ Input         19       SPK_L       Analogue Output       Right Output (Line or Headphone )         20       SPK_R       Analogue Output       Left Output (Line or Headphone )         21       GND       VSS       Power Ground         22       GND       VSS       Power Ground         23       PIO0/USB_D<br>M       Bi-directional       Programmable input/output line<br>Alternative Function: USB_DM         24       PIO1/USB_DP<br>M       Bi-directional       Programmable input/output line<br>Alternative Function: USB_DP         25       PIO2/SWCLK       Bi-directional       Debugging through the clk line(Default)<br>Alternative Function: Programmable input/output line         26       PIO3/SWDIO       Bi-directional       Debugging through the data line(Default)<br>Alternative Function: Programmable input/output line         27       PIO4       Bi-directional       Programmable input/output line<br>Alternative Function: PA_EN pin, active high         28       PIO5/Tran/AIO       I/O       Programmable input/output line<br>Alternative Function: PA_EN pin, active high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |               |                       |                                                         |

| 19       SPK_L       Analogue Output       Right Output (Line or Headphone )         20       SPK_R       Analogue Output       Left Output (Line or Headphone )         21       GND       VSS       Power Ground         22       GND       VSS       Power Ground         23       PIO0/USB_D<br>M       Bi-directional       Programmable input/output line<br>Alternative Function: USB_DM         24       PIO1/USB_DP       Bi-directional       Programmable input/output line<br>Alternative Function: USB_DP         25       PIO2/SWCLK       Bi-directional       Debugging through the clk line(Default)<br>Alternative Function: Programmable input/output line         26       PIO3/SWDIO       Bi-directional       Debugging through the data line(Default)<br>Alternative Function: Programmable input/output line         27       PIO4       Bi-directional       Programmable input/output line         28       PIO5/Tran/AIO       I/O       Programmable input/output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17         | MIC-          | Analogue Input        | MIC- Input                                              |

| 20     SPK_R     Analogue Output     Left Output (Line or Headphone )       21     GND     VSS     Power Ground       22     GND     VSS     Power Ground       23     GND     VSS     Power Ground       23     PIO0/USB_D<br>M     Bi-directional     Programmable input/output line<br>Alternative Function: USB_DM       24     PIO1/USB_DP     Bi-directional     Programmable input/output line<br>Alternative Function: USB_DP       25     PIO2/SWCLK     Bi-directional     Debugging through the clk line(Default)<br>Alternative Function: Programmable input/output line       26     PIO3/SWDIO     Bi-directional     Debugging through the data line(Default)<br>Alternative Function: Programmable input/output line       27     PIO4     Bi-directional     Programmable input/output line       27     PIO5/Tran/AIO     I/O     Programmable input/output line       28     PIO5/Tran/AIO     I/O     Programmable input/output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18         | MIC+          | Analogue Input        | MIC+ Input                                              |

| 21       GND       VSS       Power Ground         22       GND       VSS       Power Ground         23       PIO0/USB_D<br>M       Bi-directional       Programmable input/output line         24       PIO1/USB_DP       Bi-directional       Programmable input/output line         24       PIO1/USB_DP       Bi-directional       Programmable input/output line         25       PIO2/SWCLK       Bi-directional       Debugging through the clk line(Default)         26       PIO3/SWDIO       Bi-directional       Debugging through the data line(Default)         27       PIO4       Bi-directional       Programmable input/output line         27       PIO4       Bi-directional       Programmable input/output line         28       PIO5/Tran/AIO       I/O       Programmable input/output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19         | SPK_L         | Analogue Output       | Right Output (Line or Headphone)                        |

| 22       GND       VSS       Power Ground         23       PIO0/USB_D<br>M       Bi-directional       Programmable input/output line         23       M       Bi-directional       Programmable input/output line         24       PIO1/USB_DP       Bi-directional       Programmable input/output line         24       PIO1/USB_DP       Bi-directional       Programmable input/output line         25       PIO2/SWCLK       Bi-directional       Debugging through the clk line(Default)         26       PIO3/SWDIO       Bi-directional       Debugging through the data line(Default)         26       PIO3/SWDIO       Bi-directional       Debugging through the data line(Default)         27       PIO4       Bi-directional       Programmable input/output line         27       PIO4       Bi-directional       Programmable input/output line         28       PIO5/Tran/AIO       I/O       Programmable input/output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20         | SPK_R         | Analogue Output       | Left Output (Line or Headphone)                         |

| 23       PIO0/USB_D<br>M       Bi-directional       Programmable input/output line<br>Alternative Function: USB_DM         24       PIO1/USB_DP       Bi-directional       Programmable input/output line<br>Alternative Function: USB_DP         25       PIO2/SWCLK       Bi-directional       Debugging through the clk line(Default)<br>Alternative Function: Programmable input/output line         26       PIO3/SWDIO       Bi-directional       Debugging through the data line(Default)<br>Alternative Function: Programmable input/output line         27       PIO4       Bi-directional       Programmable input/output line         28       PIO5/Tran/AIO       I/O       Programmable input/output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21         | GND           | VSS                   | Power Ground                                            |

| 23     Bi-directional     Bi-directional     Alternative Function: USB_DM       24     PIO1/USB_DP     Bi-directional     Programmable input/output line       25     PIO2/SWCLK     Bi-directional     Debugging through the clk line(Default)       26     PIO3/SWDIO     Bi-directional     Debugging through the data line(Default)       27     PIO4     Bi-directional     Programmable input/output line       28     PIO5/Tran/AIO     I/O     Programmable input/output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22         | GND           | VSS                   | Power Ground                                            |

| MAlternative Function: USB_DM24PIO1/USB_DPBi-directionalProgrammable input/output line<br>Alternative Function: USB_DP25PIO2/SWCLKBi-directionalDebugging through the clk line(Default)<br>Alternative Function: Programmable input/output line26PIO3/SWDIOBi-directionalDebugging through the data line(Default)<br>Alternative Function: Programmable input/output line27PIO4Bi-directionalProgrammable input/output line<br>Alternative Function: PA_EN pin, active high28PIO5/Tran/AIOI/OAlternative Function 1: Analogue programmable I/O line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            | PIO0/USB_D    |                       | Programmable input/output line                          |

| 24       PIO1/USB_DP       Bi-directional       Programmable input/output line         25       PIO2/SWCLK       Bi-directional       Debugging through the clk line(Default)         26       PIO3/SWDIO       Bi-directional       Debugging through the data line(Default)         26       PIO3/SWDIO       Bi-directional       Debugging through the data line(Default)         27       PIO4       Bi-directional       Programmable input/output line         27       PIO4       Bi-directional       Programmable input/output line         28       PIO5/Tran/AIO       I/O       Programmable input/output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23         | м             | <b>Bi-directional</b> | Alternative Function: USB_DM                            |

| 24     PIO1/USB_DP     Bi-directional     Alternative Function: USB_DP       25     PIO2/SWCLK     Bi-directional     Debugging through the clk line(Default)       26     PIO3/SWDIO     Bi-directional     Debugging through the data line(Default)       26     PIO3/SWDIO     Bi-directional     Debugging through the data line(Default)       27     PIO4     Bi-directional     Programmable input/output line       27     PIO4     Bi-directional     Programmable input/output line       28     PIO5/Tran/AIO     I/O     Programmable input/output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |               |                       |                                                         |

| 25       PIO2/SWCLK       Bi-directional       Debugging through the clk line(Default)         26       PIO3/SWDIO       Bi-directional       Debugging through the data line(Default)         26       PIO3/SWDIO       Bi-directional       Debugging through the data line(Default)         27       PIO4       Bi-directional       Programmable input/output line         27       PIO4       Bi-directional       Programmable input/output line         28       PIO5/Tran/AIO       I/O       Programmable input/output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24         | PIO1/USB_DP   | <b>Bi-directional</b> |                                                         |

| 25     PIO2/SWCLK     Bi-directional     Alternative Function: Programmable input/output line       26     PIO3/SWDIO     Bi-directional     Debugging through the data line(Default)<br>Alternative Function: Programmable input/output line       27     PIO4     Bi-directional     Programmable input/output line       27     PIO4     Bi-directional     Programmable input/output line       28     PIO5/Tran/AIO     I/O     Programmable input/output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |               |                       |                                                         |

| 26     PIO3/SWDIO     Bi-directional     Alternative Function: Programmable input/output line       27     PIO4     Bi-directional     Programmable input/output line       27     PIO4     Bi-directional     Programmable input/output line       28     PIO5/Tran/AIO     I/O     Programmable input/output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25         | PIO2/SWCLK    | Bi-directional        | Alternative Function: Programmable input/output line    |

| 20     Alternative Function: Programmable input/output line       27     PIO4     Bi-directional     Programmable input/output line       28     PIO5/Tran/AIO     I/O     Programmable input/output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26         | PIO3/SW/DIO   | <b>Bi-directional</b> |                                                         |

| 27     PIO4     Bi-directional       Alternative Function:     PA_EN pin, active high       PIO5/Tran/AIO     Programmable input/output line       28     I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20         |               |                       | Alternative Function: Programmable input/output line    |