GM500\_U1A

# HARDWARE DEVELOPMENT GUIDE

Version: V1.1 Date: 2018-04-28

LTE Module Series

# **REVISION HISTORY**

| Version | Date       | Description                      |

|---------|------------|----------------------------------|

| 1.0     | 2018-04-18 | 1 <sup>st</sup> released version |

# **ABOUT THIS DOCUMENT**

### A. Application Range

This document is the Product Technical Specification for the GM500\_U1A GSM/WCDMA/LTE-FDD module. It defines the high level product features and illustrates the interface for these features. This document is intended to cover the hardware aspects of the product, including electrical and mechanical.

### B. Reading Note

The symbols below are the reading notes you should pay attention on:

#### C. Purpose

This document provides the hardware solutions and development fundamentals for a product with the module. By reading this document, the user can have an overall knowledge of the module and a clear understanding of the technical parameters. With this document, the user can successfully fulfill the application and development of wireless Internet product or equipment.

Besides the product features and technical parameters, this document also provides the product reliability tests and related testing standards, RF performance indexes and a guide on the design of user circuits, to provide the user with a complete design reference.

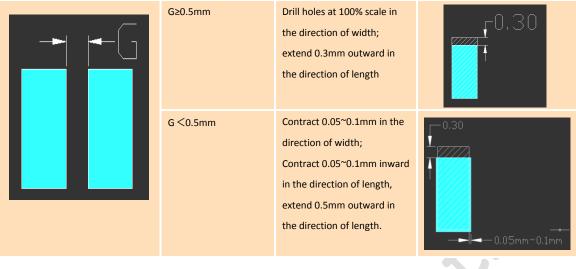

To ensure the module manufacturing and welding quality, do as the chapter 7 of Manufacturing Guide in this document. The force on the squeegee should be adjusted so as to produce a clean stencil surface on a single pass and ensure the module soldering quality.

#### D. Abbreviations

Table below is a list of abbreviations involved in this document, as well as the English full names.

| Abbreviations | Full Name                                   |  |

|---------------|---------------------------------------------|--|

| 3GPP          | Third Generation Partnership Project        |  |

| AP            | Another name of DTE                         |  |

| CHAP          | Challenge Handshake Authentication Protocol |  |

| CE            | European Conformity                         |  |

| CMOS          | Complementary Metal Oxide Semiconductor     |  |

| DCE           | Data Communication Equipment                |  |

| DL            | Downlink                                    |  |

| DTE           | Data Terminal Equipment                     |  |

| EIA           | Electronic Industries Association           |  |

| EMC           | Electromagnetic Compatibility               |  |

| ESD           | Electro-Static discharge                    |  |

| ESR           | Equivalent Series Resistance                |  |

| FDD           | Frequency Division Duplex                   |  |

| GPIO          | General-purpose I/O                         |  |

| LCC           | Leadless Chip Carrier                       |  |

| LDO                                    | Low-Dropout                                 |  |

|----------------------------------------|---------------------------------------------|--|

| LED                                    | Light Emitting Diode                        |  |

| LTE                                    | Long Term Evolution                         |  |

| ME                                     | Mobile Equipment                            |  |

| MO                                     | Mobile Origination Call                     |  |

| MT                                     | Mobile Termination Call                     |  |

| MSB                                    | Most Significant Bit                        |  |

|                                        |                                             |  |

| PC                                     | Personal Computer                           |  |

| PCB                                    | Printed Circuit Board                       |  |

| PDA                                    | Personal Digital Assistant                  |  |

| PDU                                    | Protocol Data Unit                          |  |

| PAP                                    | Password Authentication Protocol            |  |

| PPP                                    | Point to Point Protocol                     |  |

| RTC                                    | Real Time Clock                             |  |

| SMS                                    | Short Messaging Service                     |  |

| SMT                                    | Surface Mount Technology                    |  |

| SPI                                    | Serial Peripheral Interface                 |  |

| TBD                                    | To Be Determined                            |  |

| ТСР                                    | Transmission Control Protocol               |  |

| TIS                                    | Total Isotropic Sensitivity                 |  |

| TRP                                    | Total Radiated Power                        |  |

| TVS                                    | Transient Voltage Suppressor                |  |

| UART                                   | Universal Asynchronous Receiver-Transmitter |  |

| UDP                                    | User Datagram Protocol                      |  |

| UL                                     | Up Link                                     |  |

| USB                                    | Universal Serial Bus                        |  |

| USIM                                   | Universal Subscriber Identity Module        |  |

| URC                                    | Unsolicited result code                     |  |

| VIH                                    | Logic High level of input voltage           |  |

| VIL                                    | Logic Low level of input voltage            |  |

| VOH Logic High level of output voltage |                                             |  |

| VOL                                    | Logic Low level of output voltage           |  |

|                                        |                                             |  |

# **SAFETY INFORMATION**

The following safety precautions must be observed during all phases of the operation, such as usage, service or repair of any cellular terminal or mobile incorporating ME3610 module. Manufacturers of the cellular terminal should send the following safety information to users and operating personnel and to incorporate these guidelines into all manuals supplied with the product. If not so, GOSUNCN does not take on any liability for customer failure to comply with these precautions.

Full attention must be given to driving at all times in order to reduce the risk of an accident. Using a mobile while driving (even with a hands free kit) cause distraction and can lead to an accident. You must comply with laws and regulations restricting the use of wireless devices while driving.

Switch off the cellular terminal or mobile before boarding an aircraft. Make sure it switched off. The operation of wireless appliances in an aircraft is forbidden to prevent interference with communication systems. Consult the airline staff about the use of wireless devices on boarding the aircraft, if your device offers a Airplane Mode which must be enabled prior to boarding an aircraft.

Switch off your wireless device when in hospitals or clinics or other health care facilities. These requests are designed to prevent possible interference with sensitive medical equipment.

GSM cellular terminals or mobiles operate over radio frequency signal and cellular network and cannot be guaranteed to connect in all conditions, for example no mobile fee or an invalid SIM card. While you are in this condition and need emergent help, please remember using emergency call. In order to make or receive call, the cellular terminal or mobile must be switched on and in a service area with adequate cellular signal strength.

Your cellular terminal or mobile contains a transmitter and receiver. When it is on, it receives and transmits radio frequency energy. RF interference can occur if it is used close to TV set, radio, computer or other electric equipment.

In locations with potentially explosive atmospheres, obey all posted signs to turn off wireless devices such as your phone or other cellular terminals. Areas with potentially explosive atmospheres including fuelling areas, below decks on boats, fuel or chemical transfer or storage facilities, areas where the air contains chemicals or particles such as grain, dust or metal powders.

# **CONTENTS**

| 1. Product Overview                                                      |     |

|--------------------------------------------------------------------------|-----|

| 1.1. General Description                                                 | 11  |

| 1.2. Key Features 11                                                     |     |

| 1.3. Function Diagram                                                    | 12  |

| 1.4. Evaluation Board                                                    | 13  |

| 2. Application Interface                                                 | 4.4 |

| 2.1. General Description                                                 |     |

|                                                                          | 14  |

| <ul><li>2.2. Pin Assignment 14</li><li>2.3. Pin Description 16</li></ul> |     |

| 2.4. Power Supply 22                                                     |     |

| 2.4.1. Power Supply Pins                                                 | 25  |

| 2.4.2. Decrease Voltage Drop                                             |     |

| 2.4.3. Reference Circuit of Power Supply                                 |     |

| 2.4.3. Reference Circuit of Power Supply                                 |     |

| 2.6. Turn off Scenarios                                                  |     |

| 2.7. Reset Scenarios 26                                                  | 22  |

| 2.8. USIM Card Interface                                                 | 25  |

| 2.8.1. Description of PINs                                               | 25  |

| 2.8.2. Design Considerations for USIM Card Holder                        |     |

| 2.9 LISB Interface 31                                                    |     |

| 2.10. UART Interface                                                     | 33  |

| 2.10.1. UART CONNECTION                                                  |     |

| 2.10.2. UART LEVEL MATCH                                                 |     |

| 2.10.3. Use ic for level switch                                          |     |

| 2.11. Network Status Indication                                          |     |

| 2.12. POWER_ON/OFF Status Indicator ON_STATE                             |     |

| 2.13. ADC Interface 43                                                   |     |

| 2.14. WAKEUP_IN Signal                                                   | 43  |

| 2.15. WAKEUP OUT Signal                                                  |     |

| 2.16. GPIO Interface 46                                                  |     |

|                                                                          |     |

| 3. Antenna Interface                                                     | 47  |

| 3.1. Pin Definition 47                                                   |     |

| 3.2. Reference Design                                                    | 47  |

| 3.3. Reference PCB Layout of Antenna                                     | 49  |

| 3.4. Suggestions for EMC & ESD Design                                    | 49  |

| 3.4.1. EMC Design Requirements                                           | 49  |

| 3.4.2. ESD Design Requirements                                           | 49  |

| 3.5. Test Methods for Whole-Set Antenna OTA                              | 50  |

| 4. Electrical, Reliability and Radio Characteristics           | 51 |

|----------------------------------------------------------------|----|

| 4.1. Absolute Maximum Ratings                                  | 51 |

| 4.2. Operating Temperature                                     | 51 |

| 4.3. Electrostatic Discharge                                   | 51 |

| 4.4. GM500_U1A Test                                            | 51 |

| 4.4.1. Current Consumption                                     | 51 |

| 4.4.2. RF Output Power                                         | 52 |

| 4.4.3. RF Receiving Sensitivity                                | 52 |

| 4.5. GNSS Technical Parameters                                 | 52 |

| •                                                              |    |

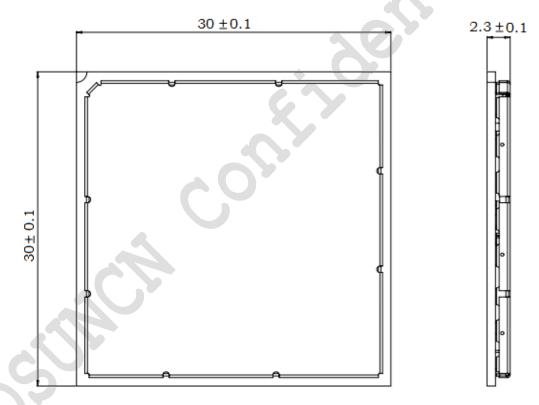

| 5. Mechanical Dimensions                                       |    |

| 5.1. Mechanical Dimensions of the Module                       |    |

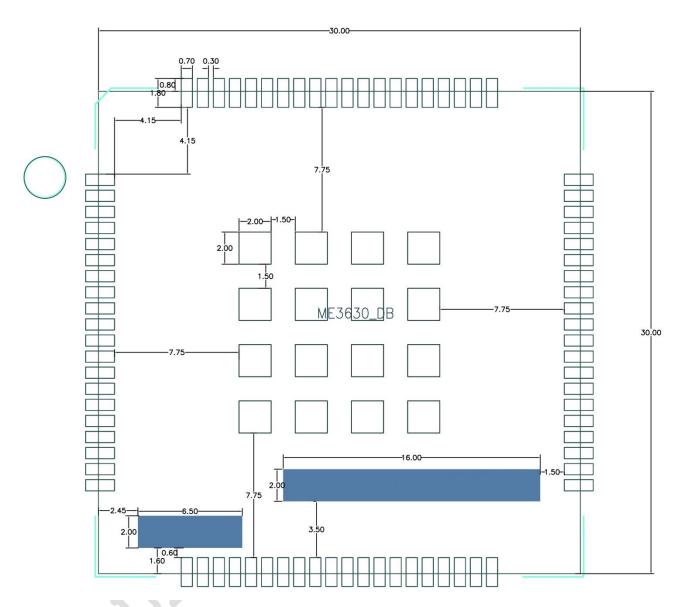

| 5.2. Footprint of Recommendation                               | 55 |

| 6. Related Test & Test Standard                                |    |

|                                                                |    |

| 6.1. Testing Reference                                         |    |

| 6.2. Description of Testing Environment                        |    |

| 6.3. Reliability Testing Environment                           | 57 |

| 7. SMT Process and Baking Guide                                | 58 |

| 7.1. Storage Requirements                                      |    |

| 7.2. Module Plainness Standard                                 |    |

| 7.3. Process Routing Selection                                 |    |

| 7.3.1. Solder Paste Selection                                  |    |

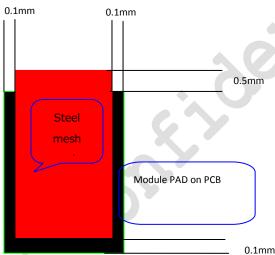

| 7.3.2. Design of module PAD's steel mesh opening on main board |    |

| 7.3.3. Module Board's SMT process                              | 59 |

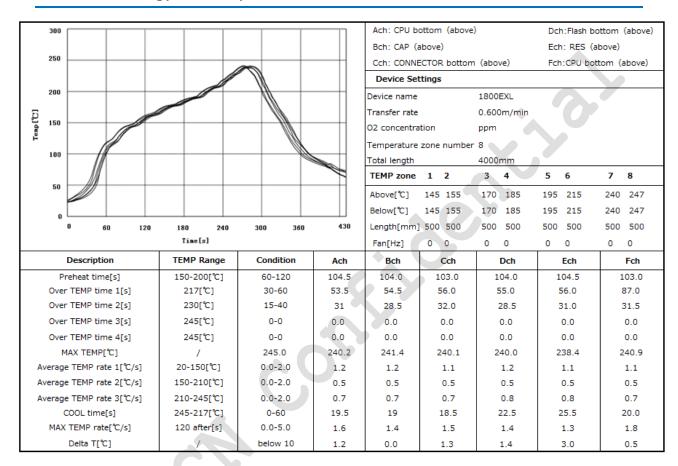

| 7.3.4. Module Soldering Reflow Curve                           | 60 |

| 7.3.5. Reflow method                                           | 61 |

| 7.3.6. Maintenance of defects                                  | 61 |

| 7.4. Module's Baking Requirements                              | 61 |

| 7.4.1. Module's Baking Environment                             |    |

| 7.4.2. Baking device and operation procedure                   | 62 |

| 7.4.3. Module Baking Conditions                                | 62 |

|                                                                |    |

| 8. Federal Communication Commission Interference Statement     | 62 |

# **TABLES**

| Table 1-1  | GM500_U1A Supported Band                     | 11 |

|------------|----------------------------------------------|----|

| Table 1-2  | GM500_U1A Key Features                       | 11 |

| Table 2-1  | IO Parameters Definition                     | 16 |

| Table 2-2  | Logic levels Description                     | 16 |

| Table 2-3  | Pin Description                              | 16 |

| Table 2-4  | Power Supply                                 | 22 |

| Table 2-5  | Definition of POWER_ON                       | 24 |

| Table 2-6  | Power-on Time                                | 25 |

| Table 2-7  | Power-off Time                               |    |

| Table 2-8  | Pin Definition of the USIM Interface         |    |

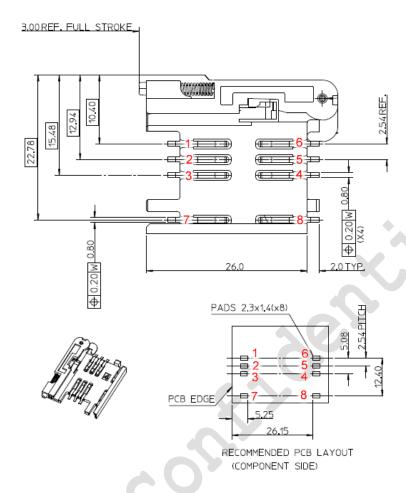

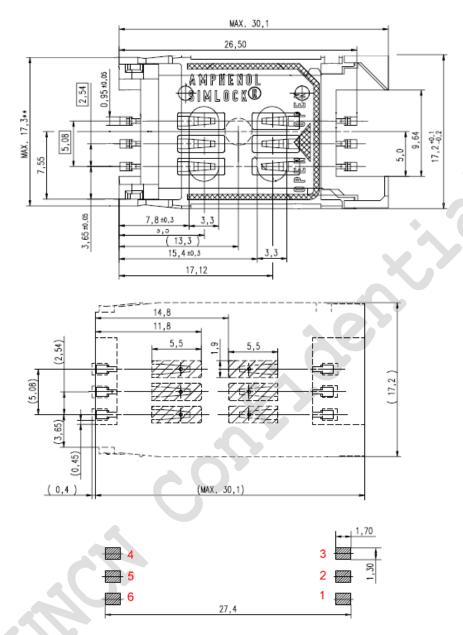

| Table 2-9  | Pin Description of Molex USIM Card Holder    | 30 |

| Table 2-10 | Pin Description of Amphenol USIM Card Holder | 31 |

| Table 2-11 | USB Pin Description                          | 32 |

| Table 2-12 | Pin Definition of the Main UART Interface    | 33 |

| Table 2-13 | Pin Definition of the Debug UART Interface   | 34 |

| Table 2-14 | Pin Definition of Network Indicator          | 42 |

| Table 2-15 | Working State of the Network Indicator       | 42 |

| Table 2-16 | Pin Definition of ON_STATE                   | 42 |

| Table 2-17 | Pin Definition of the ADC                    | 43 |

| Table 2-18 | Characteristic of the ADC                    | 43 |

| Table 2-19 | Pin Definition of WAKEUP_IN                  | 43 |

| Table 2-20 | Pin Definition of WAKEUP_OUT                 | 45 |

| Table 2-21 | Pin Definition of GPIO                       | 46 |

| Table 3-1  | Pin Definition of Antenna                    | 47 |

| Table 4-1  | Absolute Maximum Ratings                     | 51 |

| Table 4-2  | Operating Temperature                        | 51 |

| Table 4-3  | ESD characteristic                           | 51 |

| Table 4-4  | Averaged standby DC power consumption [1]    | 51 |

| Table 4-5  | Averaged working current [1]                 | 51 |

| Table 4-6  | Averaged working current [2]                         | 5 | 52 |

|------------|------------------------------------------------------|---|----|

| Table 4-7  | Conducted RF Output Power                            | 5 | 52 |

| Table 4-8  | Conducted RF Receiving Sensitivity Typical Value [1] | 5 | 52 |

| Table 4-9  | Conducted RF Receiving Sensitivity Typical Value [2] | 5 | 52 |

| Table 4-10 | GNSS Technical Parameters                            | 5 | 52 |

|            | Testing Standard                                     |   |    |

|            | Testing Environment                                  |   |    |

| Table 6-3  | Testing Instrument & Device                          | 5 | 57 |

| Table 6-4  | Reliability Features                                 | 5 | 57 |

| Table 7-1  | Baking parameters                                    | 5 | 58 |

| Table 7-2  | LCC module PAD's steel mesh opening                  | 5 | 58 |

# **FIGURES**

| Figure 1–1  | System Connection Structure                                   | . 13 |

|-------------|---------------------------------------------------------------|------|

| Figure 2–1  | Pin Assignment                                                | . 16 |

| Figure 2–2  | The input reference circuit of VBAT                           |      |

| Figure 2–3  | Reference circuit of DC-DC                                    |      |

| Figure 2–4  | Reference circuit of LDO                                      | . 23 |

| Figure 2–5  | Reference circuit of POWER_ON                                 | . 24 |

| Figure 2–6  | Timing of Turning on Mode                                     | . 25 |

| Figure 2–7  | Timing of Turning off Mode                                    |      |

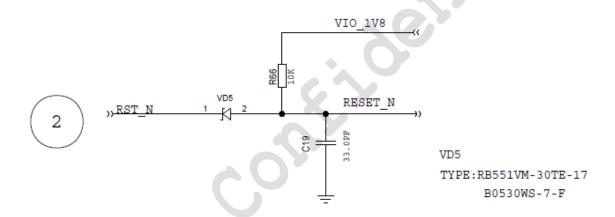

| Figure 2–8  | reference circuit to reset module                             |      |

| Figure 2–9  | Timing of Reset Mode                                          | . 27 |

| Figure 2–10 | Reference Circuit of the 8 Pin USIM Card                      |      |

| Figure 2–11 | Reference Circuit of the 6 Pin USIM Card                      | . 29 |

| Figure 2–12 | Molex 91228 USIM Card Holder                                  | . 30 |

| Figure 2–13 | Amphenol C707 10M006 512 2 USIM Card Holder                   | . 31 |

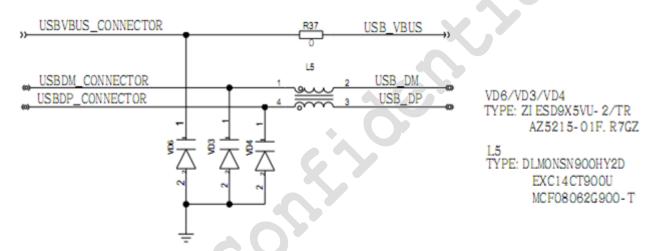

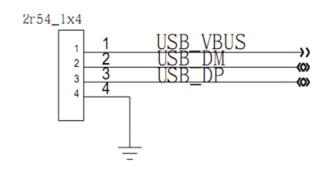

| Figure 2–14 | Reference Circuit of USB Application                          | . 32 |

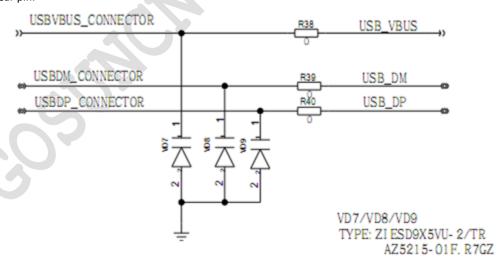

| Figure 2–15 | Reference Circuit of USB Communication between module and AP  | . 32 |

| Figure 2–16 | Reference circuit of USB when USB is not the desired function | . 33 |

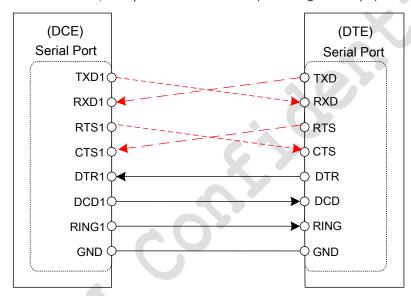

| Figure 2–17 | Schematic of 8-wire UART Connection                           | . 34 |

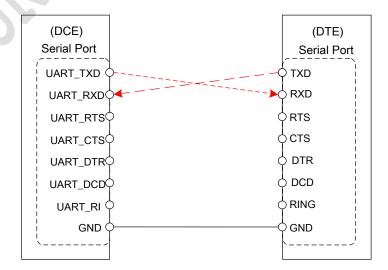

| Figure 2–18 | Schematic of 3-wire UART Connection                           | . 34 |

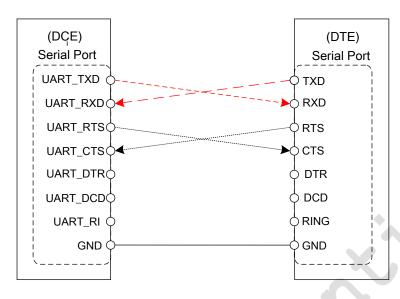

| Figure 2–19 | Schematic of 4-wire UART Connection                           | . 35 |

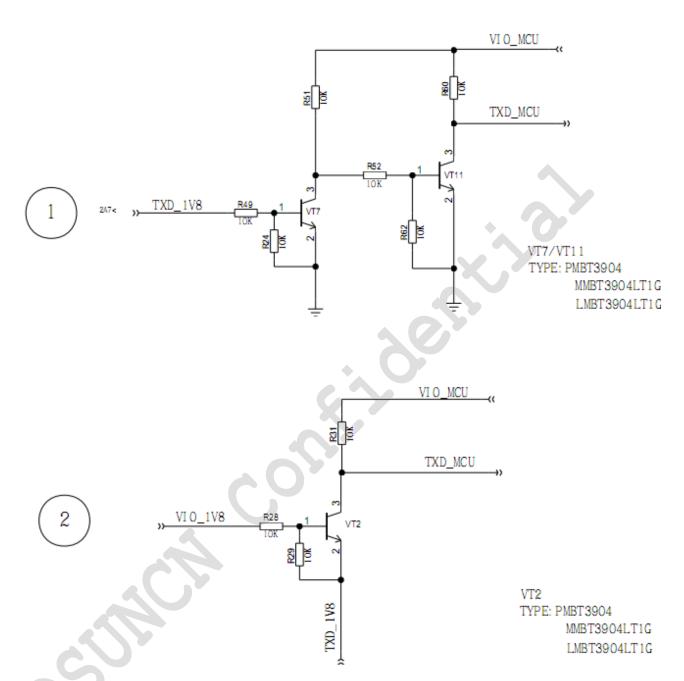

| Figure 2–20 | Recommended TXD circuit                                       | . 36 |

| Figure 2–21 | Recommended RXD circuit                                       | . 37 |

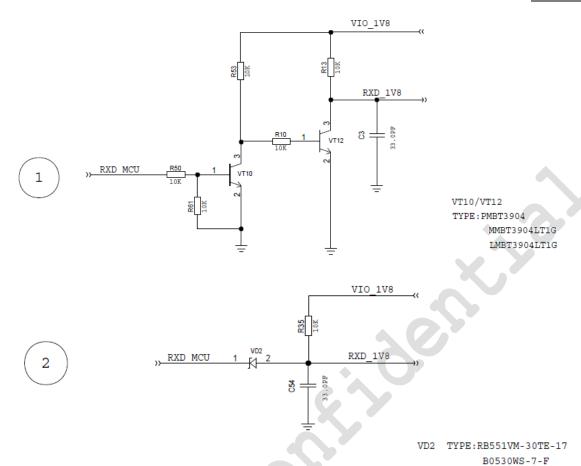

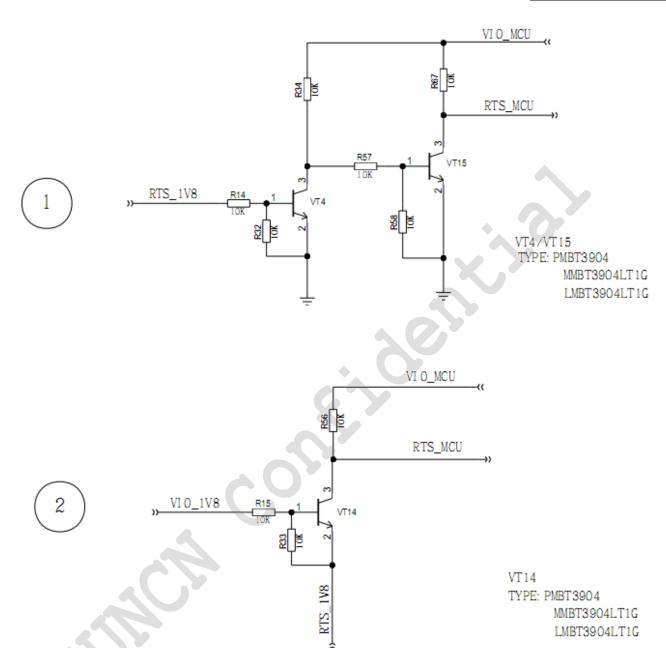

| Figure 2–22 | Recommended RTS circuit                                       | . 38 |

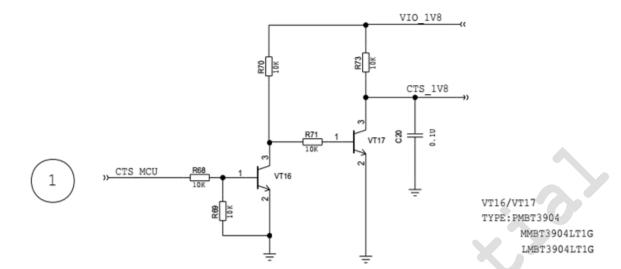

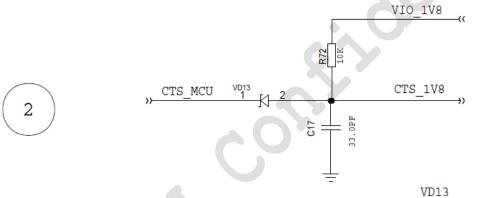

| Figure 2–23 | Recommended CTS circuit                                       | . 39 |

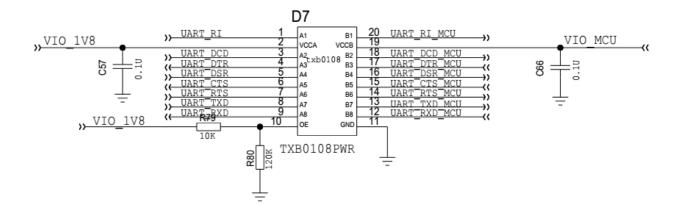

| Figure 2–24 | Recommended 8-wires UART level switch circuit                 | . 40 |

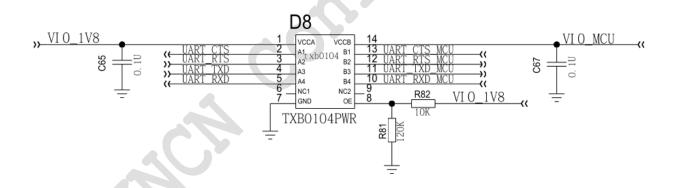

| Figure 2–25 | Recommended 4-wires UART level switch circuit                 | . 41 |

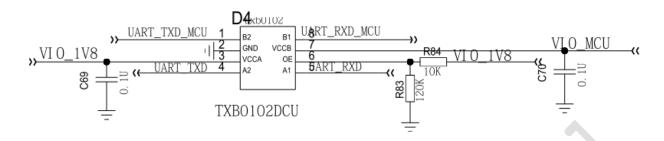

| Figure 2–26 | Recommended 2-wires UART level switch circuit                 | . 41 |

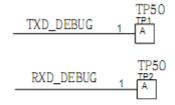

| Figure 2–27 | The test point of debug UART                                  | . 41 |

| Figure 2–28 | Reference Circuit of the Network Indicator                    | . 42 |

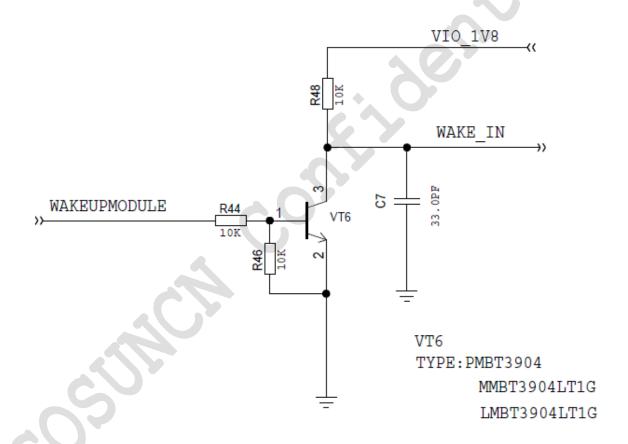

| Figure 2–29 | WAKEUP_IN input sequence                                      | . 44 |

| Figure 2–30 | Connections of the WAKEUP_IN pin                   | 14             |

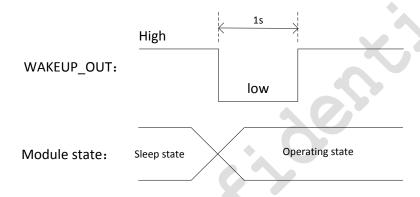

|-------------|----------------------------------------------------|----------------|

| Figure 2–31 | The output signal of WAKEUP_OUT                    | 45             |

| Figure 2–32 | Connections of the WAKEUP_OUT pin                  | 45             |

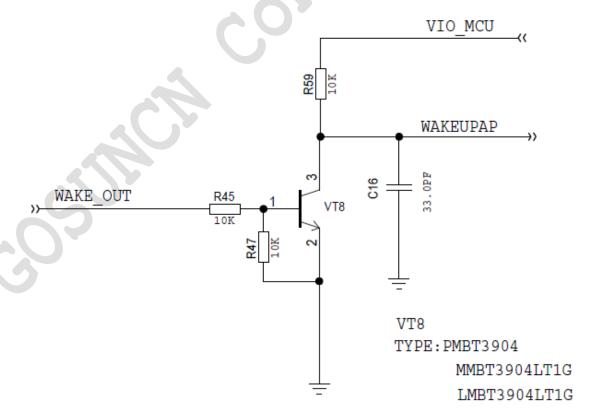

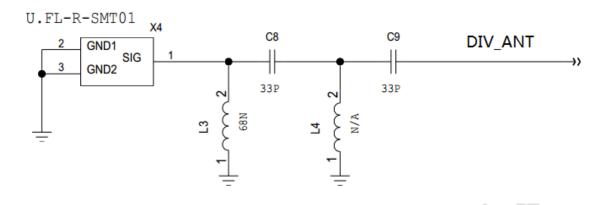

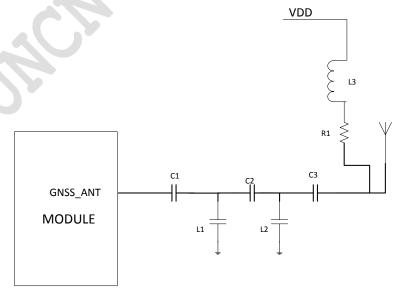

| Figure 3–1  | Reference Circuit of Antenna Interface             | <del>1</del> 8 |

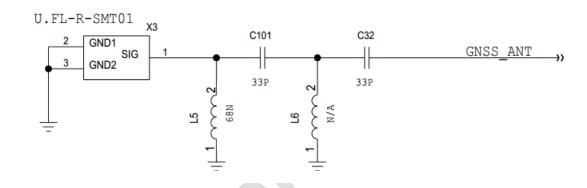

| Figure 3–2  | Reference Circuit of GNSS Antenna                  | <del>1</del> 8 |

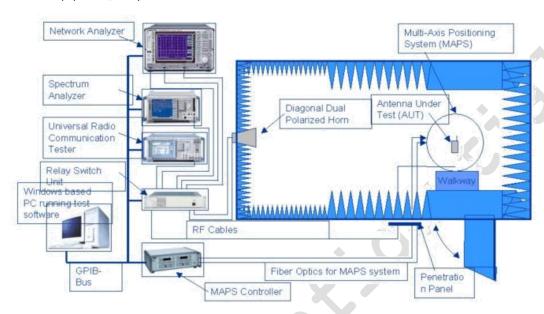

| Figure 3–3  | The OTA test system of CTIA                        | 50             |

| Figure 5–1  | GM500_U1A Top and Side Dimensions                  | 53             |

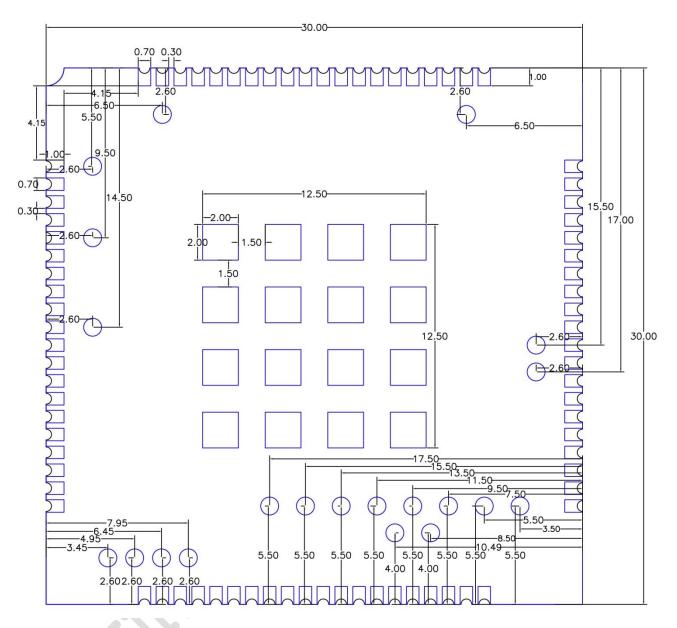

| Figure 5–2  | GM500_U1A Bottom Dimensions                        | 54             |

| Figure 5–3  | Recommended Footprint                              | 55             |

| Figure 7–1  | Module Board's Steel Mesh Diagram                  | 59             |

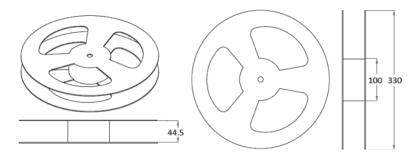

| Figure 7–2  | Material Module Pallet                             | 59             |

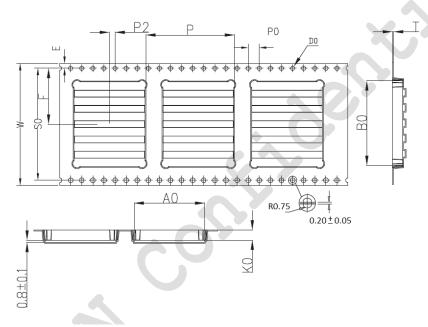

| Figure 7–3  | Tape Reel Dimension                                | 50             |

| Figure 7–4  | Module Furnace Temperature Curve Reference Diagram | 51             |

# 1. PRODUCT OVERVIEW

# 1.1. GENERAL DESCRIPTION

GM500\_U1A is a LTE/WCDMA/GSM wireless communication module with LCC interface. It is widely applied to but not limited to the various products and equipment such as laptops, vehicle-mounted terminals, and electric devices, by providing data services.

Customer can choose the dedicated type based on the wireless network configuration and using area. The following table shows the entire radio band configuration of GM500\_U1A.

Table 1-1 GM500\_U1A Supported Band

| PID             | RF support | RF Band | Transmit Frequency (TX) | Receive Frequency (RX) |

|-----------------|------------|---------|-------------------------|------------------------|

| GM500_U1A(CAT4) | I) LTE FDD | B2      | 1850 to 1910 MHz        | 1930 to 1990 MHz       |

|                 |            | B4      | 1710 to 1755 MHz        | 2110 to 2155 MHz       |

|                 |            | B5      | 824 to 849 MHz          | 869 to 894 MHz         |

|                 |            | B12     | 698 to 716 MHz          | 728 to 746 MHz         |

|                 | WCDMA      | B2      | 1850 to 1910 MHz        | 1930 to 1990 MHz       |

|                 |            | B5      | 824 to 849 MHz          | 869 to 894 MHz         |

|                 |            | 850     | 824.2 to 848.8MHz       | 869.2 to 893.8 MHz     |

|                 |            | 1900    | 1850.2 to 1909.8 MHz    | 1930.2 to 1989.8MHz    |

# 1.2. KEY FEATURES

The table below describes the detailed features of the GM500\_U1A module.

Table 1-2 GM500\_U1A Key Features

| Feature                                              | Description                                                              |                        |  |

|------------------------------------------------------|--------------------------------------------------------------------------|------------------------|--|

| Physical                                             | Small form factor-30 mm × 30 mm × 2.3mm  LCC with 80 pins                |                        |  |

| Power Supply                                         | The range of voltage supply is 3.4V-4.2V, typi                           | cal value is 3.8V      |  |

| Frequency Bands                                      | U1A                                                                      | LTE FDD: B2,B4 ,B5,B12 |  |

|                                                      | (for America)                                                            | WCDMA: B2,B5           |  |

| Rx Diversity                                         | U1A                                                                      | LTE FDD:B2,B4,B5,B12   |  |

|                                                      |                                                                          | WCDMA:B2,B5            |  |

| Transmission Rate                                    | LTE FDD (CAT4): Max 150Mbps(DL)/Max 50Mbps(UL)                           |                        |  |

| Network Protocols Support TCP/PPP/UDP/FTP protocols  |                                                                          |                        |  |

| Support PAP, CHAP protocols used for PPP connection. |                                                                          | nnection.              |  |

| USIM Interface                                       | 1.8V/3V support                                                          |                        |  |

|                                                      | SIM extraction/hot plug detection                                        |                        |  |

|                                                      | Support SIM and USIM                                                     |                        |  |

| UART Interface                                       | Support two UART interface: main UART interface and debug UART interface |                        |  |

|                    | Main UART interface:                                                                       |

|--------------------|--------------------------------------------------------------------------------------------|

|                    | Eight lines on main UART interface                                                         |

|                    | Support RTS and CTS hardware flow control                                                  |

|                    | Baud rate can reach up to 921600 bps,115200 bps by default                                 |

|                    | Used for AT command, data transmission or firmware upgrade                                 |

|                    | Debug UART interface:                                                                      |

|                    | Two lines on debug UART interface, can be used for software debug, firmware upgrade        |

| USB Interface      | Compliant with USB 2.0 specification (slave only)                                          |

|                    | Used for AT command communication, data transmission, software debug and firmware upgrade. |

| USB Driver         | Support Windows XP, Windows Vista, Windows 7, Windows 8, Windows 10,                       |

|                    | Windows CE5.0/6.0 and later,                                                               |

|                    | Linux 2.6.20 and later,                                                                    |

|                    | Android 2.3 / 4.X/ 5.X                                                                     |

| SDIO interface     | 1.8V support (full speed) 4bits,SDIO compatible to WLAN (802.11)                           |

| Antenna Interface  | Include main antenna ,diversity antenna and GNSS antenna                                   |

| Rx-diversity       | Support WCDMA/LTE Rx-diversity                                                             |

| AT commands        | Compliant with 3GPP TS 27.007,27.005 and GOSUNCN enhanced AT commands                      |

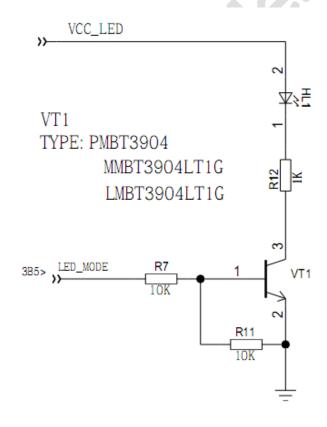

| Network Indication | Use LED_MODE to indicate network connectivity status                                       |

| SMS                | Text and PDU mode                                                                          |

|                    | Point to point MO and MT                                                                   |

|                    | SMS saving/reading to SIM card or module storage                                           |

|                    | SMS cell broadcast                                                                         |

| Temperature Range  | Normal operation: -30°C to +75°C                                                           |

|                    | Restricted operation: -40°C~ -30°C and +75°C~ +85°C <sup>1)</sup>                          |

|                    | Storage temperature: -40°C to +85°C                                                        |

| Firmware Upgrade   | USB interface or UART interface or OTA(WEFOTA)                                             |

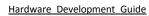

# 1.3. FUNCTION DIAGRAM

The figure below shows a block diagram of the GM500\_U1A and illustrates the major functional parts.

- Power management

- Baseband

- Memory

- RF send-receive

- Peripheral interface

- --UART interface

- --USIM card interface

- --USB interface

- --SDIO interface

- --SPI interface

- --I2C interface

- --ADC interface

- --Status interface (LED)

Figure 1–1 System Connection Structure

# 1.4. EVALUATION BOARD

In order to help you to develop applications with GM500\_U1A, GOSUNCN supplies an evaluation board (G2000/GE2015), RS-232 to USB cable, USB data cable, power adapter, antenna and other peripherals to control or test the module. For details, please refer to the related document [GE2015 Dev Board User Guide].

# 2. APPLICATION INTERFACE

# 2.1. GENERAL DESCRIPTION

GM500\_U1A is equipped with an 80-pin 0.72mm pitch SMT pads plus 16-pin ground pads and reserved pads that connect to customer's cellular application platform. Sub-interface included in these pads is described in detail in the following chapters:

- · Pin assignment

- Pin description

- Power supply

- Turn on/off scenarios

- USIM interface

- USB interface

- UART interface

- Network status indication

- ADC interface

- WAKEUP\_IN signal

- WAKEUP\_OUT signal

- · GPIO interface

# 2.2. PIN ASSIGNMENT

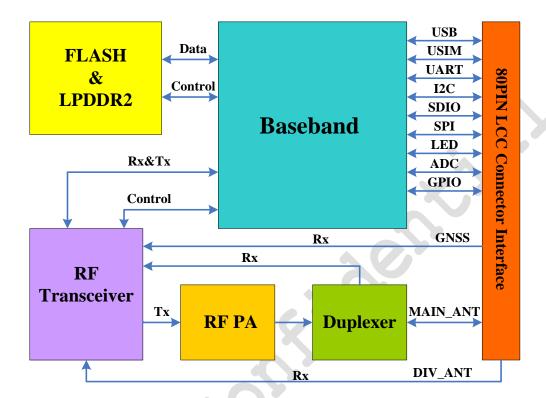

The following figure shows the pin assignment of the GM500\_U1A module.

Figure 2–1 Pin Assignment

Keep all NC pins unconnected.

# 2.3. PIN DESCRIPTION

The following table shows the IO Parameters Definition.

Table 2-1 IO Parameters Definition

| Туре | Description                |

|------|----------------------------|

| 10   | Bidirectional input/output |

| DI   | Digital input              |

| DO   | Digital output             |

| PI   | Power input                |

| PO   | Power output               |

| AI   | Analog input               |

| AO   | Analog output              |

| OD   | Open drain                 |

The logic levels are described in the following table.

Table 2-2 Logic levels Description

| Parameter | Min         | Max          | Unit |

|-----------|-------------|--------------|------|

| VIH       | 0.65*VDD_IO | VDD_IO+0.3   | V    |

| VIL       | -0.3        | 0.35* VDD_IO | V    |

| VOH       | VDD_IO-0.45 | VDD_IO       | V    |

| VOL       | 0           | 0.45         | V    |

VDD\_IO is the voltage level of pins.

The following tables show the GM500\_U1A's pin definition.

Table 2-3 Pin Description

| Power Supply |                                            |     |                                   |                                            |                                                                                                     |  |  |

|--------------|--------------------------------------------|-----|-----------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|

| Pin Name     | Pin NO.                                    | 1/0 | Description                       | DC Characteristics                         | Comment                                                                                             |  |  |

| V_BAT        | 50.51                                      | PI  | Power supply for module           | Vmax = 4.2V<br>Vmin = 3.4V<br>Vnorm = 3.8V | It must be able to provide sufficient current in a transmitting burst which typically rises to 2.0A |  |  |

| VREF_1V8     | 5                                          | РО  | Provide 1.8V for external circuit | Vnorm = 1.8V<br>Imax = 300mA               | Power supply for external GPIO'S pull up circuits                                                   |  |  |

| PLL_1V8      | 4                                          | PO  | Provide 1.8V for external circuit | Vnorm = 1.8V<br>Imax = 20mA                | This pin can only be used for WiFi interface, and can left unconnected when not used.               |  |  |

| GND          | 3,9,11,20,21,31,36,<br>46,49,52, 61,63,78, |     | Ground                            |                                            |                                                                                                     |  |  |

|                   | 80,     |     |                            |                                              |                                        |

|-------------------|---------|-----|----------------------------|----------------------------------------------|----------------------------------------|

| Turn On/Off       |         |     |                            |                                              |                                        |

| Pin Name          | Pin NO. | 1/0 | Description                | DC Characteristics                           | Comment                                |

| POWER_ON          | 1       | DI  | Turn on/off module         | V <sub>IH</sub> max = 2.1V                   | Pull-up to 0.8V internally, active low |

|                   |         |     |                            | V <sub>IH</sub> min = 1.17V                  |                                        |

|                   |         |     |                            | V <sub>IL</sub> max = 0.63V                  |                                        |

| RESET_N           | 2       | DI  | Reset module               | V <sub>IH</sub> max = 2.1V                   | Active low                             |

|                   |         |     |                            | $V_{IH}$ min = 1.17V<br>$V_{IL}$ max = 0.63V |                                        |

| Status Indication |         |     |                            | VIL 1114X = 0.03V                            |                                        |

| Pin Name          | Pin NO. | 1/0 | Description                | DC Characteristics                           | Comment                                |

|                   |         |     |                            |                                              |                                        |

| ON_STATE          | 69      | DO  | Module power on/off status | $V_{OH} min = 1.35V$<br>$V_{OL} max = 0.45V$ | 1.8V power domain                      |

|                   |         |     | indicator                  | VOL IIIAX – 0.43V                            |                                        |

| LED_MODE          | 70      | DO  | Indicate the module        | V <sub>он</sub> min = 1.35V                  | 1.8V power domain                      |

|                   |         |     | network registration       | V <sub>OL</sub> max = 0.45V                  |                                        |

|                   |         |     | mode                       |                                              |                                        |

| USB Interface     |         |     |                            |                                              |                                        |

| Pin Name          | Pin NO. | I/O | Description                | DC Characteristics                           | Comment                                |

| USB_DP            | 24      | 10  | USB differential data      |                                              | Compliant with USB 2.0 standard        |

| USB_DM            | 23      | Ю   | bus                        |                                              | specification Require differential     |

|                   |         |     |                            |                                              | impedance of $90\Omega$                |

| USB_VBUS          | 22      | PI  | USB power                  |                                              |                                        |

| HSIC Interface    |         |     |                            |                                              |                                        |

| Pin Name          | Pin NO. | I/O | Description                | DC Characteristics                           | Comment                                |

| USB_STROBE        | 25      | Ю   | HSIC strobe                | InterChip USB(HSIC)                          | line impedance 50 ohm, isometric       |

| USB_DATA          | 26      | Ю   | HSIC data                  |                                              | constraint is less than 2 mm, line     |

| USIM Interface    |         |     |                            |                                              | length is less than 10 cm              |

|                   |         |     |                            |                                              |                                        |

| Pin Name          | Pin NO. | 1/0 | Description                | DC Characteristics                           | Comment                                |

| USIM_VCC          | 40      | РО  | Power supply for           | For 1.8V USIM:                               | Either 1.8V or 3V is supported by the  |

|                   |         |     | USIM card                  | Vmax = 1.9V                                  | module automatically                   |

|                   |         |     |                            | Vmin = 1.7V<br>For 3.0V USIM:                |                                        |

|                   |         |     |                            | Vmax = 3.05V                                 |                                        |

|                   |         |     |                            | Vmin = 2.7V                                  |                                        |

|                   |         |     |                            | I <sub>0</sub> max = 50mA                    |                                        |

| USIM_DATA         | 38      | 10  | Data signal of USIM        | For 1.8V USIM:                               | Pull-up to USIM_VCC with 10k resistor  |

|                   |         |     | card                       | V <sub>IL</sub> max = 0.63V                  | internally                             |

|                   |         |     |                            | V <sub>IH</sub> min = 1.17V                  |                                        |

|                     |         |     |                                | $V_{OL}$ max = 0.45V                                                               |                                       |

|---------------------|---------|-----|--------------------------------|------------------------------------------------------------------------------------|---------------------------------------|

|                     |         |     |                                | V <sub>OH</sub> min = 1.35V                                                        |                                       |

|                     |         |     |                                | For 3V USIM:                                                                       |                                       |

|                     |         |     |                                | V <sub>IL</sub> max = 1.05V                                                        |                                       |

|                     |         |     |                                | V <sub>IH</sub> min = 1.95V                                                        |                                       |

|                     |         |     |                                | $V_{OL}$ max = 0.45V                                                               |                                       |

|                     |         |     |                                | V <sub>OH</sub> min = 2.6V                                                         |                                       |

| USIM_CLK            | 37      | DO  | Clock signal of USIM           | For 1.8V USIM:                                                                     |                                       |

|                     |         |     | card                           | $V_{OL}$ max = 0.45V                                                               |                                       |

|                     |         |     |                                | V <sub>OH</sub> min = 1.35V                                                        |                                       |

|                     |         |     |                                | For 3V USIM:                                                                       |                                       |

|                     |         |     |                                | $V_{OL}$ max = 0.45V                                                               |                                       |

|                     |         |     |                                | V <sub>OH</sub> min = 2.6V                                                         |                                       |

| USIM_RST            | 39      | DO  | Reset signal of USIM           | For 1.8V USIM:                                                                     |                                       |

|                     |         |     | card                           | $V_{OL}$ max = 0.45V                                                               |                                       |

|                     |         |     |                                | V <sub>OH</sub> min = 1.35V                                                        |                                       |

|                     |         |     |                                | For 3V USIM:                                                                       |                                       |

|                     |         |     |                                | $V_{OL}$ max = 0.45V                                                               |                                       |

|                     |         |     |                                | V <sub>OH</sub> min = 2.6V                                                         |                                       |

| USIM_DETECT         | 41      | DI  | USIM card input                | V <sub>IL</sub> min = -0.3V                                                        | 1.8V power domain. Active low         |

|                     |         |     | detection                      | V <sub>IL</sub> max = 0.63V                                                        | If no need of USIM detect, leave this |

|                     |         |     |                                | V <sub>IH</sub> min = 1.17V                                                        | pin not connected.                    |

|                     |         |     |                                | V <sub>IH</sub> max = 2.1V                                                         |                                       |

| ADC Interface       |         |     |                                |                                                                                    |                                       |

| Pin Name            | Pin NO. | 1/0 | Description                    | DC Characteristics                                                                 | Comment                               |

| ADC1                | 48      | Al  | Analog to digital              | 0.05V to 4.15V                                                                     | External sensor signal detection      |

| ADC2                | 47      | Al  | Analog to digital              | 0.05V to 4.15V                                                                     | External sensor signal detection      |

| Main UART Interface |         |     |                                |                                                                                    |                                       |

| Pin Name            | Pin NO. | 1/0 | Description                    | DC Characteristics                                                                 | Comment                               |

|                     |         |     |                                |                                                                                    |                                       |

| UART_TXD            | 53      | DO  | Transmit data                  | $V_{OL}$ max = 0.45V                                                               | 1.8V power domain                     |

|                     |         |     |                                | V <sub>OH</sub> min = 1.35V                                                        |                                       |

| UART_RXD            | 54      | DI  | Receive data                   | V <sub>IL</sub> min = -0.3V                                                        | 1.8V power domain                     |

|                     |         |     |                                | $V_{IL}$ max = 0.63V                                                               |                                       |

|                     |         |     |                                |                                                                                    |                                       |

|                     |         |     |                                | V <sub>IH</sub> min = 1.17V                                                        |                                       |

|                     |         |     |                                | $V_{IH}$ min = 1.17V<br>$V_{IH}$ max = 2.1V                                        |                                       |

| UART_RTS            | 55      | DO  | Request to send                |                                                                                    | 1.8V power domain                     |

| UART_RTS            | 55      | DO  | Request to send                | V <sub>IH</sub> max = 2.1V                                                         | 1.8V power domain                     |

| UART_RTS            | 55      | DO  | Request to send                | $V_{IH}$ max = 2.1V<br>$V_{IL}$ min = -0.3V                                        | 1.8V power domain                     |

| UART_RTS            | 55      | DO  | Request to send                | $V_{IH} max = 2.1V$ $V_{IL} min = -0.3V$ $V_{IL} max = 0.63V$                      | 1.8V power domain                     |

| UART_RTS  UART_CTS  | 55      | DO  | Request to send  Clear to send | $V_{IH} max = 2.1V$ $V_{IL} min = -0.3V$ $V_{IL} max = 0.63V$ $V_{IH} min = 1.17V$ | 1.8V power domain  1.8V power domain  |

|                      |         |     |                        |                             | nardware Developmen                        |  |  |  |

|----------------------|---------|-----|------------------------|-----------------------------|--------------------------------------------|--|--|--|

| UART_DSR             | 57      | DO  | Data set ready         | V <sub>IL</sub> min = -0.3V | 1.8V power domain.                         |  |  |  |

|                      |         |     |                        | V <sub>IL</sub> max = 0.63V |                                            |  |  |  |

|                      |         |     |                        | V <sub>IH</sub> min = 1.17V |                                            |  |  |  |

|                      |         |     |                        | V <sub>IH</sub> max = 2.1V  |                                            |  |  |  |

| UART_DTR             | 58      | DI  | Data terminal ready    | $V_{IL}$ min = -0.3V        | 1.8V power domain.                         |  |  |  |

|                      |         |     |                        | V <sub>IL</sub> max = 0.63V |                                            |  |  |  |

|                      |         |     |                        | V <sub>IH</sub> min = 1.17V |                                            |  |  |  |

| HART DCD             | 50      | 200 | Data assista           | V <sub>IH</sub> max = 2.1V  | 4.004                                      |  |  |  |

| UART_DCD             | 59      | DO  | Data carrier detection | $V_{OL}$ max = 0.45V        | 1.8V power domain                          |  |  |  |

| LIADT DI             | 60      | D0  |                        | V <sub>OH</sub> min = 1.35V | 1 OV novembers in DO not well we           |  |  |  |

| UART_RI              | 60      | DO  | Ring indicator         | $V_{OL}$ max = 0.45V        | 1.8V power domain, DO not pull-up external |  |  |  |

| Dahar HADT laterface |         |     |                        | V <sub>OH</sub> min = 1.35V | external                                   |  |  |  |

| Debug UART Interface |         |     |                        |                             |                                            |  |  |  |

| Pin Name             | Pin NO. | 1/0 | Description            | DC Characteristics          | Comment                                    |  |  |  |

| UART_DEBUG_TXD       | 68      | DO  | Transmit data          | $V_{OL}$ max = 0.45V        | 1.8V power domain                          |  |  |  |

|                      |         |     |                        | V <sub>OH</sub> min = 1.35V |                                            |  |  |  |

| UART_DEBUG_RXD       | 67      | DI  | Receive data           | $V_{IL}$ min = -0.3V        | 1.8V power domain                          |  |  |  |

|                      |         |     |                        | $V_{IL}$ max = 0.63V        |                                            |  |  |  |

|                      |         |     |                        | V <sub>IH</sub> min = 1.17V |                                            |  |  |  |

|                      |         |     |                        | V <sub>IH</sub> max = 2.1V  |                                            |  |  |  |

| RF Interface         |         |     |                        |                             |                                            |  |  |  |

| Pin Name             | Pin NO. | 1/0 | Description            | DC Characteristics          | Comment                                    |  |  |  |

| MAIN_ANT             | 62      | Ю   | Main antenna           | 50Ω impedance               |                                            |  |  |  |

| DIV_ANT              | 79      | Al  | Diversity antenna      | 50Ω impedance               |                                            |  |  |  |

| GNSS_ANT             | 10      | Ю   | GNSS antenna           | 50Ω impedance               |                                            |  |  |  |

| I2C Interface        |         |     |                        |                             |                                            |  |  |  |

| Pin Name             | Pin NO. | 1/0 | Description            | DC Characteristics          | Comment                                    |  |  |  |

| I2C_SCL              | 73      | DO  | I2C serial clock       | V <sub>OL</sub> max = 0.45V | Pull-up to 1.8V through external 2.2K      |  |  |  |

|                      |         |     |                        | V <sub>OH</sub> min = 1.35V | resistance, active low                     |  |  |  |

| I2C_SDA              | 74      | Ю   | I2C serial data        | V <sub>OL</sub> max = 0.45V | Pull-up to 1.8V through external 2.2K      |  |  |  |

|                      |         |     |                        | V <sub>OH</sub> min = 1.35V | resistance, active low                     |  |  |  |

|                      |         |     |                        | V <sub>IL</sub> min = -0.3V |                                            |  |  |  |

|                      |         |     |                        | V <sub>IL</sub> max = 0.63V |                                            |  |  |  |

|                      |         |     |                        | V <sub>IH</sub> min = 1.17V |                                            |  |  |  |

|                      |         |     |                        | V <sub>IH</sub> max = 2.1V  |                                            |  |  |  |

| SDIO Interface       |         |     |                        |                             |                                            |  |  |  |

| Pin Name             | Pin NO. | I/O | Description            | DC Characteristics          | Comment                                    |  |  |  |

| SDIO_CMD             | 14      | Ю   | Secure digital CMD     | V <sub>OL</sub> max = 0.45V | Pull-up to 1.8V through external 10K       |  |  |  |

|                      |         |     |                        | V <sub>OH</sub> min = 1.35V | resistance, active low                     |  |  |  |

|                      |         |     |                        | V <sub>IL</sub> min = -0.3V |                                            |  |  |  |

|                      |         |     |                        |                             |                                            |  |  |  |

|                |         |     |                        | V <sub>IL</sub> max = 0.63V |                   |

|----------------|---------|-----|------------------------|-----------------------------|-------------------|

|                |         |     |                        | V <sub>IH</sub> min = 1.17V |                   |

|                |         |     |                        | VIH max = 2.1V              |                   |

| SDIO_D0        | 15      | 10  | Secure digital IO data | $V_{OL}$ max = 0.45V        | 1.8V power domain |

|                |         |     | bit 0                  | V <sub>OH</sub> min = 1.35V |                   |

|                |         |     |                        | V <sub>IL</sub> min = -0.3V |                   |

|                |         |     |                        | V <sub>IL</sub> max = 0.63V |                   |

|                |         |     |                        | V <sub>IH</sub> min = 1.17V |                   |

|                |         |     |                        | VIH max = 2.1V              |                   |

| SDIO_D1        | 16      | 10  | Secure digital IO data | V <sub>OL</sub> max = 0.45V | 1.8V power domain |

|                |         |     | bit 1                  | V <sub>OH</sub> min = 1.35V |                   |

|                |         |     |                        | V <sub>IL</sub> min = -0.3V |                   |

|                |         |     |                        | V <sub>IL</sub> max = 0.63V |                   |

|                |         |     |                        | V <sub>IH</sub> min = 1.17V |                   |

|                |         |     |                        | VIH max = 2.1V              |                   |

| SDIO_D2        | 17      | 10  | Secure digital IO data | V <sub>OL</sub> max = 0.45V | 1.8V power domain |

|                |         |     | bit 2                  | V <sub>OH</sub> min = 1.35V | ·                 |

|                |         |     |                        | V <sub>IL</sub> min = -0.3V |                   |

|                |         |     |                        | V <sub>IL</sub> max = 0.63V |                   |

|                |         |     |                        | V <sub>IH</sub> min = 1.17V |                   |

|                |         |     |                        | VIH max = 2.1V              |                   |

| SDIO_D3        | 18      | 10  | Secure digital IO data | V <sub>OL</sub> max = 0.45V | 1.8V power domain |

|                |         |     | bit 3                  | V <sub>OH</sub> min = 1.35V |                   |

|                |         |     |                        | V <sub>IL</sub> min = -0.3V |                   |

|                |         |     |                        | V <sub>IL</sub> max = 0.63V |                   |

|                |         |     |                        | V <sub>IH</sub> min = 1.17V |                   |

|                |         |     |                        | VIH max = 2.1V              |                   |

| SDIO_CLK       | 19      | DO  | Secure digital CLK     | V <sub>OL</sub> max = 0.45V | 1.8V power domain |

|                |         |     |                        | V <sub>OH</sub> min = 1.35V |                   |

| SDIO Interface |         |     |                        |                             |                   |

| Pin Name       | Pin NO. | 1/0 | Description            | DC Characteristics          | Comment           |

| SPI_MISO       | 32      | 10  | SPI main input slave   | V <sub>OL</sub> max = 0.45V | 1.8V power domain |

|                |         |     | output                 | V <sub>OH</sub> min = 1.35V |                   |

|                |         |     |                        | V <sub>IL</sub> min = -0.3V |                   |

|                |         |     |                        | V <sub>IL</sub> max = 0.63V |                   |

|                |         |     |                        | V <sub>IH</sub> min = 1.17V |                   |

|                |         |     |                        | VIH max = 2.1V              |                   |

| SPI_MOSI       | 33      | 10  | SPI main output slave  | V <sub>OL</sub> max = 0.45V | 1.8V power domain |

|                |         |     | input                  | V <sub>OH</sub> min = 1.35V |                   |

|                |         |     |                        | V <sub>IL</sub> min = -0.3V |                   |

|                |         |     |                        | V <sub>IL</sub> max = 0.63V |                   |

|                |         |     |                        |                             |                   |

|                |                    |     |                       | V <sub>IH</sub> min = 1.17V |                                         |  |  |

|----------------|--------------------|-----|-----------------------|-----------------------------|-----------------------------------------|--|--|

|                |                    |     |                       | VIH max = 2.1V              |                                         |  |  |

| SPI_CLK        | 34                 | DO  | SPI clock             | $V_{OL}$ max = 0.45V        | 1.8V power domain                       |  |  |

|                |                    |     |                       | V <sub>OH</sub> min = 1.35V |                                         |  |  |

| SPI_CS_N       | 35                 | DO  | SPI segment           | $V_{OL}$ max = 0.45V        | 1.8V power domain                       |  |  |

|                |                    |     |                       | V <sub>OH</sub> min = 1.35V |                                         |  |  |

| WiF PINs       |                    |     |                       |                             |                                         |  |  |

| WLAN_SLEEP_CLK | 6                  | DO  | WLAN sleep clock      | V <sub>OL</sub> max = 0.45V | Only supported by firmware with WiFi.   |  |  |

|                |                    |     |                       | V <sub>OH</sub> min = 1.35V | Other firmware, this pin is NC          |  |  |

| COEX_UART_TX   | 7                  | DO  | LTE transmitter sync  | V <sub>OL</sub> max = 0.45V | Only supported by firmware with WiFi.   |  |  |

|                |                    |     | for coexistence with  | V <sub>OH</sub> min = 1.35V | Other firmware, this pin is NC          |  |  |

|                |                    |     | UART                  |                             |                                         |  |  |

| COEX_UART_RX   | 8                  | DI  | LTE receiver sync for | V <sub>IL</sub> max = 0.63V | Only supported by firmware with WiFi.   |  |  |

|                |                    |     | coexistence with      | V <sub>IH</sub> min = 1.17V | Other firmware, this pin is NC          |  |  |

|                |                    |     | UART                  |                             | When pull-up this pin to 1.8V, the      |  |  |

|                |                    |     |                       |                             | module will enter emergency             |  |  |

|                |                    |     |                       |                             | download mode.                          |  |  |

| WLAN_EN        | 12                 | DO  | WLAN enable           | $V_{OL}$ max = 0.45V        | Only supported by firmware with WiFi.   |  |  |

|                |                    |     |                       | V <sub>OH</sub> min = 1.35V | Other firmware, this pin is NC          |  |  |

| WLAN_3V3_EN    | 13                 | DO  | WLAN power enable     | $V_{OL}$ max = 0.45V        | Only supported by firmware with WiFi.   |  |  |

|                |                    |     |                       | V <sub>OH</sub> min = 1.35V | Other firmware, this pin is NC          |  |  |

| WLAN_SLEEP_CLK | 6                  | DO  | WLAN sleep clock      | $V_{OL}$ max = 0.45V        | Only supported by firmware with WiFi.   |  |  |

|                |                    |     |                       | V <sub>OH</sub> min = 1.35V | Other firmware, this pin is NC          |  |  |

| Other Pins     |                    |     |                       |                             |                                         |  |  |

| Pin Name       | Pin NO.            | 1/0 | Description           | DC Characteristics          | Comment                                 |  |  |

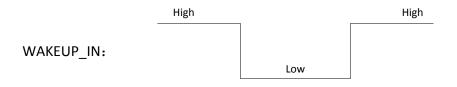

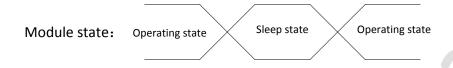

| WAKEUP_IN      | 72                 | DI  | Sleep mode control,   | V <sub>IL</sub> min = -0.3V | 1.8V power domain. Pull-down            |  |  |

|                |                    |     | External device       | V <sub>IL</sub> max = 0.45V | internally. Edge-triggered, Rising edge |  |  |

|                |                    |     | wakeup module         | V <sub>IH</sub> min = 1.53V | wake up module; Falling edge modules    |  |  |

|                |                    |     |                       | V <sub>IH</sub> max = 2.1V  | can enter sleep                         |  |  |

| WAKEUP_OUT     | 71                 | DO  | Output wakeup         | $V_{OL}$ max = 0.8V         | Wakeup external circuits                |  |  |

|                |                    |     | signal, wake up the   | V <sub>OH</sub> min = 1.35V |                                         |  |  |

|                |                    |     | external devices      |                             |                                         |  |  |

| GPIO           | 27, 28, 29, 30, 65 | 10  | General input/output  | V <sub>OL</sub> max = 0.45V | If unused, keep them floating.          |  |  |

|                |                    |     |                       | V <sub>OH</sub> min = 1.35V | DO not pull-up PIN77 external           |  |  |

|                |                    |     |                       | V <sub>IL</sub> min = -0.3V |                                         |  |  |

|                |                    |     |                       | V <sub>IL</sub> max = 0.63V |                                         |  |  |

|                |                    |     |                       | V <sub>IH</sub> min = 1.17V |                                         |  |  |

|                |                    |     |                       | VIH max = 2.1V              |                                         |  |  |

| NC             | 66,64,75,76,77,4   |     | No connection         |                             | NC, there is no connection internal,    |  |  |

|                | 5,44,43,42         |     |                       |                             | please keep them floating .             |  |  |

#### 2.4. POWER SUPPLY

#### 2.4.1. POWER SUPPLY PINS

The GM500\_U1A is supplied through the V\_BAT signal with the following characteristics.

Table 2-4 Power Supply

| Pin Name | Pin NO.                       | Description             | Minimum | Typical | Maximum | Unit |

|----------|-------------------------------|-------------------------|---------|---------|---------|------|

| V_BAT    | 50,51                         | Power supply for module | 3.4     | 3.8     | 4.2     | V    |

| GND      | 3, 9, 11, 20, 21, 31, 36, 46, | Ground                  | -       |         | -       |      |

|          | 49, 52, 61, 63, 78, 80,       |                         |         |         |         |      |

GND signal (Pin No: 3/9/11/20/21/31/36/46/49/52/61/63/78/80) is the power and signal ground of the module, which needs to be connected to the ground on the system board. If the GND signal is not connected completely, the performance of module will be affected.

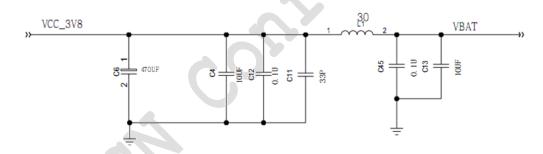

### 2.4.2. DECREASE VOLTAGE DROP

The power supply range of the module is  $3.4V^{\sim}$  4.2V. In poor situation of the network is, the antenna will transmit at the maximum power, and the transient maximum peak current can reach as high as 2A. So we recommended to add Energy storage capacitor (C6: 470 $\mu$ F). Filter capacitor(10 $\mu$ F, 0.1 $\mu$ F, 33 $\mu$ F) need to be added to reduce interference. The capacitors should be placed close to the GM500\_U1A's V\_BAT pins. The following figure shows structure of the power supply.

PLACE CLOSE TO MODULE

Figure 2–2 The input reference circuit of VBAT

The PCB traces from the V\_BAT pins to the power source must be wide enough to ensure that there isn't too much voltage drop occurs in the transmitting procedure. The width of V\_BAT trace should be no less than 2mm, and the principle of the V\_BAT trace is the longer, the wider.

In addition, make the ground plane as complete as possible, and play more holes.

#### 2.4.3. REFERENCE CIRCUIT OF POWER SUPPLY

# Option 1:DC-DC switching

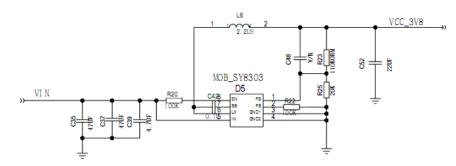

The over-current capability requirement of DC/DC switching power supply needs to be above 2.5A. When the input and output voltage difference is large, you need to select Buck circuit to improve translate efficiency.

Two reference power supply circuit design with DC-DC is shown as figure below:

FB: 0. 6V VI N: 4. 5V- 40V 3. 0A

D5 TYPE: SY8303AIC

FB: 0. 6V VI N: 2. 7V- 6V 3. 5A

D1 TYPE: NZ87203-11-631LF PAM2326AGPADJ

Figure 2–3 Reference circuit of DC-DC

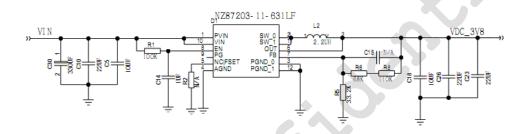

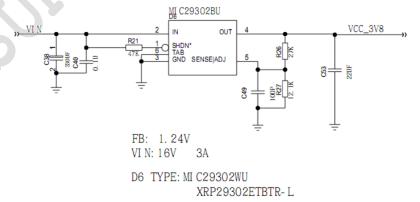

# Option 2:LDO

The over-current capability of LDO is above 2.5A. This LDO is apply to this situation: input and output voltage difference is small.

The reference power supply circuit design with LDO is shown as figure below:

Figure 2–4 Reference circuit of LDO

# 2.5. TURN ON SCENARIOS

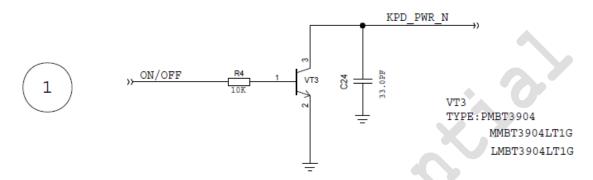

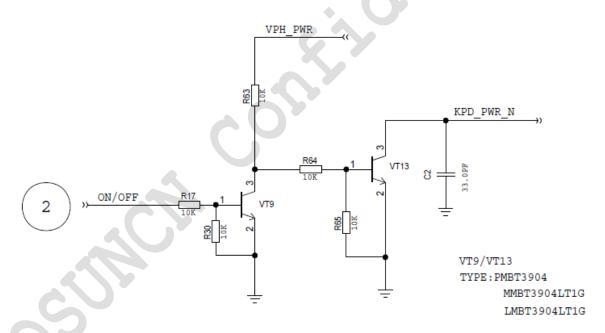

When MCU can provide high/low level pulse with adjustable length, the reference circuit to turn-on/off module is as shown in the following figure below.

The resistors in Figures below are only the recommended value and they need to adjust according to the actual situation.

Power-on by dynatron, the circuit ① connect ON/OFF to high level to power-on the module, the circuit ② can connect ON/OFF to low level to power-on the module

PULL ON/OFF HIGH TO POWER ON

PULL ON/OFF LOW TO POWER ON

Figure 2–5 Reference circuit of POWER\_ON

The table below is the information of power-on/off pin

Table 2-5 Definition of POWER\_ON

| Pin Name | Pin NO. | 1/0 | Description            | Comment                                |

|----------|---------|-----|------------------------|----------------------------------------|

| POWER_ON | 1       | DI  | Turn on/off the module | low active. Pull-up to 0.8V internally |

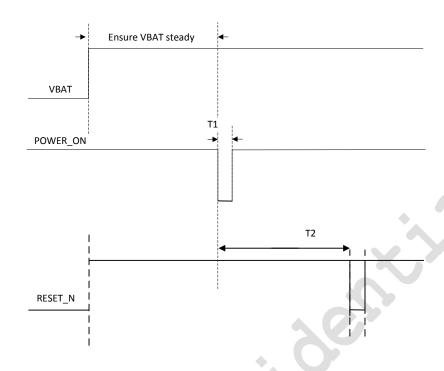

The power on scenarios is illustrated as the following figure, the module will power on and working when the POWER\_ON pin keep in low level for T1, in this process, please ensure VBAT steady.

Figure 2–6 Timing of Turning on Mode

Table 2-6 Power-on Time

| Parameter | Description                                                                       | Min | Typical | Max | Unit   |

|-----------|-----------------------------------------------------------------------------------|-----|---------|-----|--------|

| T1        | The period that the Power-on signal for power on operation is kept on the low PWL | 0.1 | 0.2     |     | Second |

| T2        | The minimum interval between the POWER_ON and RESET signals if you want to        | 10  | 15      |     | Second |

|           | reset the module after power-on.                                                  |     |         |     |        |

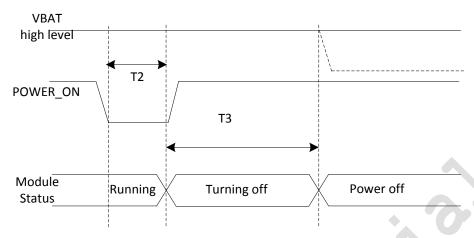

# 2.6. TURN OFF SCENARIOS

The module supports two modes to turn off:

# Mode 1:

Pull down pin1 (POWER\_ON) for 2.5-3s will turn off the module. The power off process will take 22s at least. The reference circuit can refer to the figure 2-5.

Table 2-7 Power-off Time

| Parameter | Description                                                                        | Min | Typical | Max | Unit   |

|-----------|------------------------------------------------------------------------------------|-----|---------|-----|--------|

| Т2        | The period that the POWER_ON signal for power off operation is kept on the low PWL | 2.5 | 3       |     | second |

| Т3        | The period that the VBAT signal should be kept after power off operation is down   | 22  |         |     | second |

Figure 2–7 Timing of Turning off Mode

Mode 2: Send command of AT+ZTURNOFF, and the power off process will take 15s at least.

Note:when using modules, you need to avoid power off abnormally and frequently, as it will cause several risks shwon as below:

- 1. it will damage the flash permanently.

- 2. it can't send deregiter message to e-NodeB, and the MMS takes for the module is still registering to network, and it won't remind "the user can't reach" or "the user has turn down" when it's called (MT).

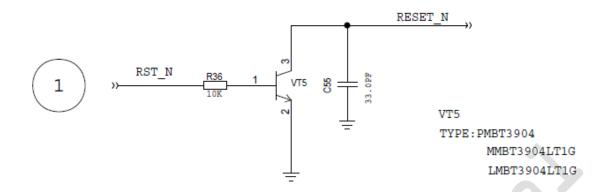

### 2.7. RESET SCENARIOS

When the software stops response, you can pulled down RESET\_N pin(pin2) for 1 second to reset the module's system.

When MCU can provide high/low level pulse with 1 second, the reference circuit to reset module is as shown in the following figure below. The resistors in Figures below are only the recommended value and they need to adjust according to the actual situation.

PULL RST N HIGH TO RESET

# PULL RST N LOW TO RESET

Figure 2–8 reference circuit to reset module

The reset scenario is illustrated as the following figure,

Figure 2–9 Timing of Reset Mode

# Mode 2:

Send command of AT+ZRST, and the RESET process until the AT port can communicate will take 27s at least.

# 2.8. USIM CARD INTERFACE

### 2.8.1. DESCRIPTION OF PINS

The USIM card interface circuitry meets ETSI and IMT-2000 SIM interface requirements. Both 1.8V and 3.0V USIM cards are supported.

Table 2-8 Pin Definition of the USIM Interface

| Pin Name    | Pin NO. | I/O | Description                                                              | Comment                                                                                                                                                                                                                                       |

|-------------|---------|-----|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USIM_VCC    | 40      | РО  | Power supply for USIM card                                               | Either 1.8V or 3V is supported by the module automatically                                                                                                                                                                                    |

| USIM_DATA   | 38      | 10  | IO Data signal of USIM card Pull-up to USIM_VDD with 10k resistor intern |                                                                                                                                                                                                                                               |

| USIM_CLK    | 37      | DO  | Clock signal of USIM card                                                |                                                                                                                                                                                                                                               |

| USIM_RST    | 39      | DO  | Reset signal of USIM card                                                |                                                                                                                                                                                                                                               |

| USIM_DETECT | 41      | DI  | USIM card hot swap detection pin.                                        | 1.8V power domain. The signal is internally pulled up.  Keep USIM_DETECT not connected, if it is not used. When USIM detect function is enable (send AT command AT+ZSDT=1), and if it is Low, USIM is present; if it is High, USIM is absent. |

| GND         | 36      |     | Ground                                                                   |                                                                                                                                                                                                                                               |

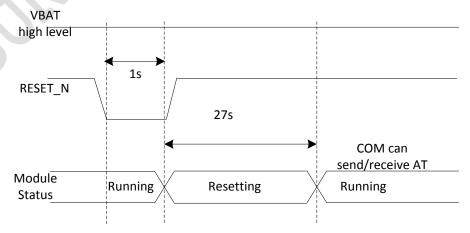

The following figure shows the reference design of the 8-pin USIM card.

### NOTES:

- 1. FOR ME3630, R74 CAN BE NA, UIM DATA PULL-UP HAS BEEN ADDED IN MODULE.

- 2.RECOMMENDED ADD AN ESD PROTECTION DEVICE FOR SIM PROTECTION.

PLEASE PLACE ESD NEAR THE SIM CARD AND LAYOUT FIRST THROUGH ESD DEVICE.

- 3.RECOMMENDED ADD 33PF BETWEEN UIM\_CLK, UIM\_DATA, UIM\_RST AND GND TO FILTER RF SIGNAL INTERFERENCE.

- 4.RECOMMENDED ADD SERIES RESISTANCE IN UIM\_DATA AND UIM\_CLK SIGNAL.

- 5.UIM DETECT IS THE INPUT SIGNAL OF THE MODULE, 1.8V.

RECOMMENDED PUIL UP UIM\_DETECT TO THE REFERENCE LEVEL (1.8V ) BY 10K.

IT IS USED TO DETECT SIM CARD.

WHEN IT IS LOW, THERE IS A CARD, FOR HIGH, NO CARD.

PLEASE CONFIRM IF THE SIM CONNECTOR PLUG MEET THE HARDWARE REQUIREMENTS.

Figure 2–10 Reference Circuit of the 8 Pin USIM Card

GM500\_U1A supports USIM card hot-plugging via the USIM\_ DETECT pin. For details, refer to document [AT Command Reference Guide of Module Product GM500\_U1A]. If you do not need the USIM card detect function, keep USIM\_ DETECT unconnected.

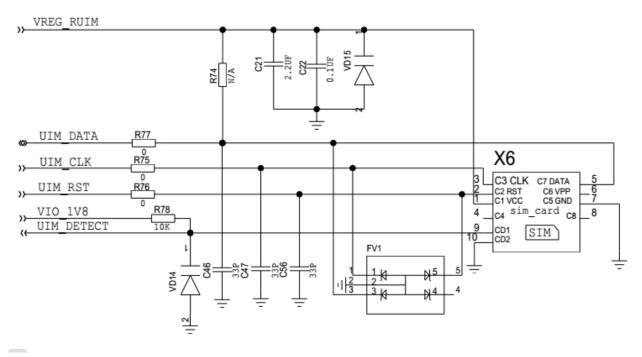

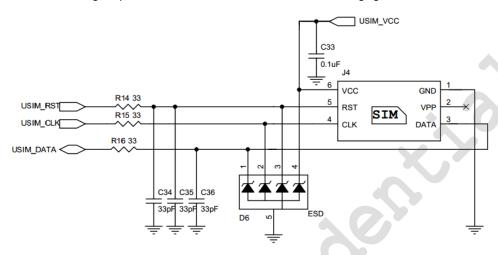

The reference circuit for using a 6-pin USIM card socket is illustrated as the following figure.

Figure 2–11 Reference Circuit of the 6 Pin USIM Card

- ☑ R14~R16 and D6 are applied to suppress the EMI spurious transmission and enhance the ESD protection.D6 should be closed to J4

- **☑** The value of C33 should be less than 1uF.

In order to enhance the reliability and availability of the USIM card in customer's application, please follow the following criterion in the USIM circuit design:

- Keep layout of USIM card as close as possible to the module. Assure the possibility of the length of the trace is less than

- Keep USIM card signal away from RF and V BAT alignment.

- Assure the ground between module and USIM cassette short and wide. Keep the width of ground and USIM\_VCC no less

than 0.5mm to maintain the same electric potential. The decouple capacitor of USIM\_VCC should be less than 1uF and