# SNM909 Hardware Design Manual

Release date:2022.11

Controlled file name: SNM909 Hardware Design Manual

Controlled version number: V1.00

Publishing organization: MeiG Smart Technology Co., Ltd

# **Important Notice**

#### **Copyright Notice**

All rights reserved. MeiG Smart Technology Co., Ltd

This manual and all its contents are owned by MeiG Smart Technology Co., Ltd and protected by Chinese laws and relevant copyright laws in applicable international conventions. Without the written authorization of MeiG Smart Technology Co., Ltd, no one may copy, disseminate, distribute, modify or use part or all of this manual in any form, and the offenders will be held responsible according to law.

#### Statement of No Guarantee

MeiG Smart Technology Co., Ltd makes no representations or guarantees, either express or implied, for any contents in this document, and assumes no responsibility for the merchantability and fitness for a particular purpose or any indirect, extraordinary or consequential losses.

#### **Confidentiality Claim**

The information contained in this document (including any annexes) is confidential. The recipient understands that the document obtained by him is confidential and shall not be used for any purpose other than the stated purpose, and he shall not disclose this document to any third party.

#### **Disclaimer**

The company assumes no responsibility for property damage or personal injury caused by customers' improper operation. Customers are requested to develop corresponding products according to the technical specifications and reference designs in the manual. Before the disclaimer, the company has the right to change the contents of this manual according to the needs of technological development, and the version is subject to change without further notice.

### Safety warning

Pay attention to the following safety precautions when using or repairing any terminal or mobile phone that contains modules. The user should be informed of the following safety information on the terminal device. Otherwise, Meig will not be responsible for any consequences caused by the user not following these warning actions.

#### Identification

#### Claim

When you are at a hospital or medical facility, observe the restrictions on using your phone. If necessary, please turn off the terminal or mobile phone, otherwise the medical device may malfunction due to radio frequency interference.

Turn off the wireless terminal or mobile phone before boarding. To prevent interference with the communication system, wireless communication equipment is prohibited on the aircraft. Ignoring the above will violate local laws and may result in a flight accident.

Do not use mobile terminals or mobile phones in front of flammable gases. Turn off the mobile terminal when you are near an explosion, chemical factory, fuel depot, or gas station. It is dangerous to operate a mobile terminal next to any potentially explosive electrical equipment.

The mobile terminal receives or transmits radio frequency energy when it is turned on. It can interfere with TV, radio, computer or other electrical equipment.

Road safety first! Do not use a handheld terminal or mobile phone while driving, please use a hands-free device. Stop before using your handheld terminal or mobile phone.

GSM mobile terminals operate under RF signals and cellular networks, but are not guaranteed to be connected in all situations. For example, there is no credit or invalid SIM card. When in this situation and need emergency services, remember to use an emergency call. In order to be able to call and receive calls, the mobile terminal must be powered on and in a service area where the mobile signal is strong enough. Emergency calls are not allowed when certain network services or telephony features are in use, such as feature locks, keyboard locks. These functions should be removed before using an emergency call. Some networks require effective SIM card support.

# SNM909 Hardware Design Manual\_V1.00

# Foreword

Thank you for using the SNM909 module from Meg Smart. This product can provide data communication services. Please read the user manual carefully before use, you will appreciate its perfect function and simple operation method.

The company does not assume responsibility for property damage or personal injury caused by improper operation of the user. Users are requested to develop the corresponding products according to the technical specifications and reference designs in the manual. Also pay attention to the general safety issues that mobile products should focus on.

Before the announcement, the company has the right to modify the contents of this manual according to the needs of technological development.

# 目录

|   | nportant Notice                                   |          |

|---|---------------------------------------------------|----------|

|   | Introduction                                      |          |

| 2 | Module overview                                   |          |

|   | 2.1 Summary of features                           |          |

|   | 2.2 Block diagram                                 |          |

| 3 | Module Package                                    |          |

|   | 3.1 Pin definitions                               |          |

|   | 3.2 Mechanical Dimensions                         |          |

| 4 | Interface application                             |          |

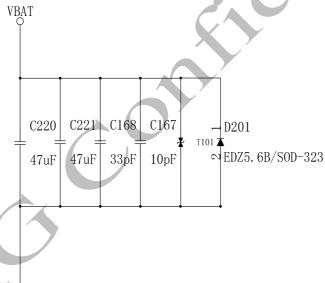

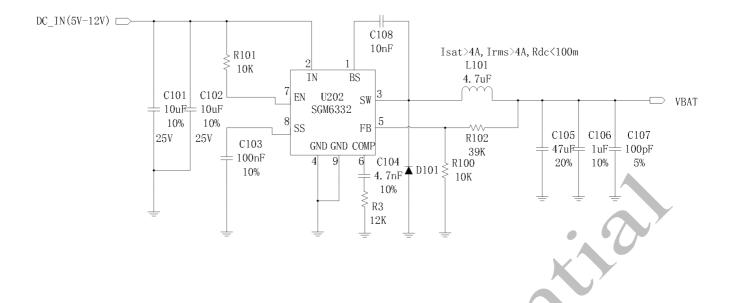

|   | 4.1 Power Supply                                  |          |

|   | 4.1.1 Power Pin                                   |          |

|   | 4.1.2 Power PCB layout                            |          |

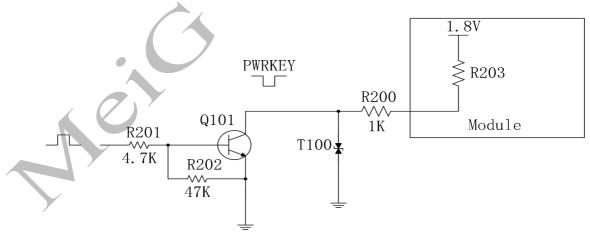

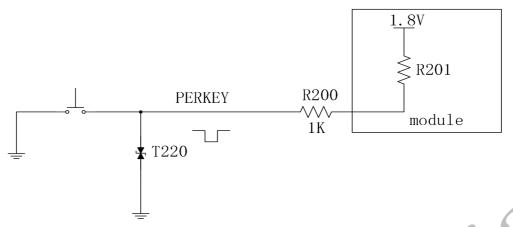

|   | 4.2 Power on and off                              |          |

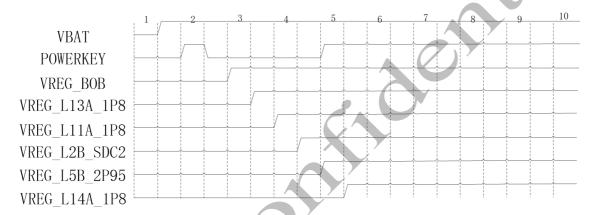

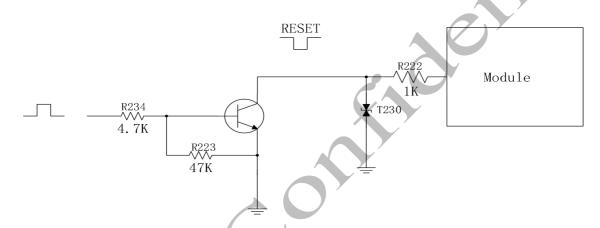

|   | 4.2.1.模块开机                                        | 32       |

|   | 4.2.2 Module Shutdown                             | 33       |

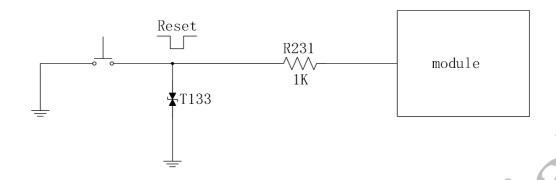

|   | 4.2.3 Module Reset                                | 33       |

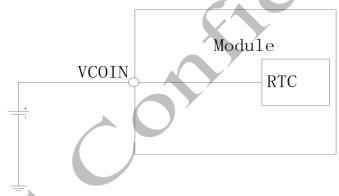

|   | 4.3.VCOIN 电源                                      |          |

|   | 4.4 Power Output                                  |          |

|   | 4.5 Serial Port                                   | 36       |

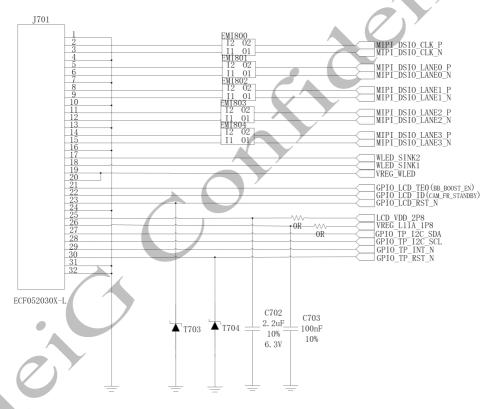

|   | 4.6 MIPI Interface                                | 38       |

|   | 4.6.1 LCD Interface                               | 38       |

|   | 4.6.2 MIPI Camera Interface                       | 42       |

|   | 4.6.3 MIPI PCB layout                             | 45       |

|   | 4.7 Capacitive Touch Interface                    | 45       |

|   | 4.8 Audio Interface                               | 46       |

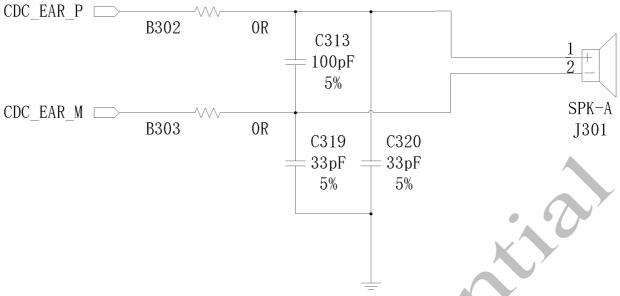

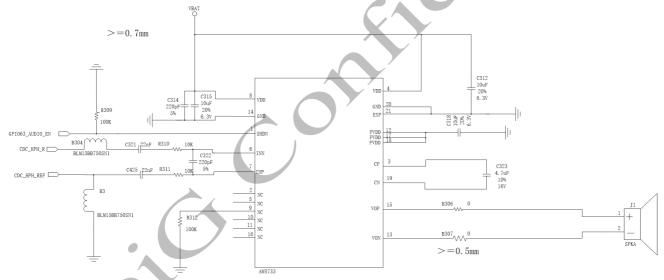

|   | 4.8.1 Receiver Interface Circuit                  | 46       |

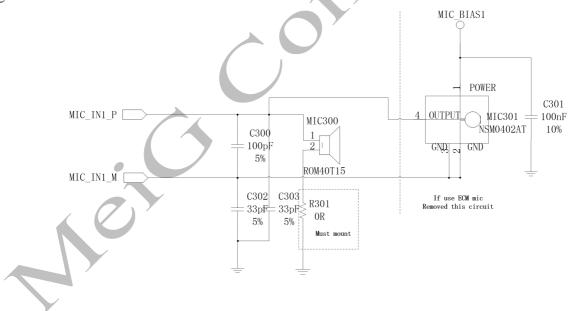

|   | 4.8.2 Microphone receiving Circuit                | 4/       |

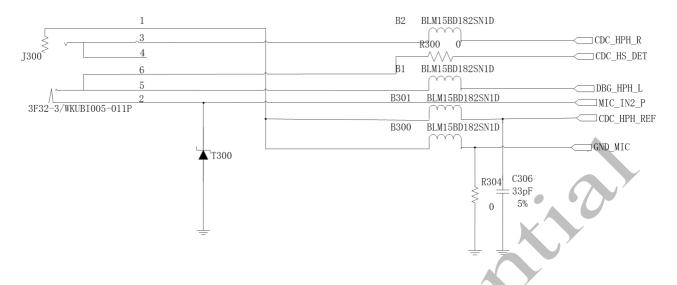

|   | 4.8.5 Headphone interface Circuit                 | 4/       |

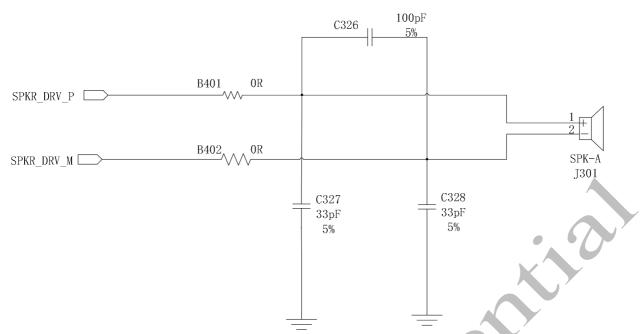

|   | 4.8.4 Speaker interface circuit                   | 48       |

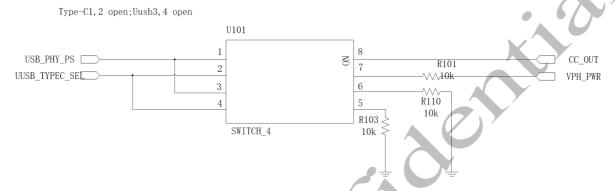

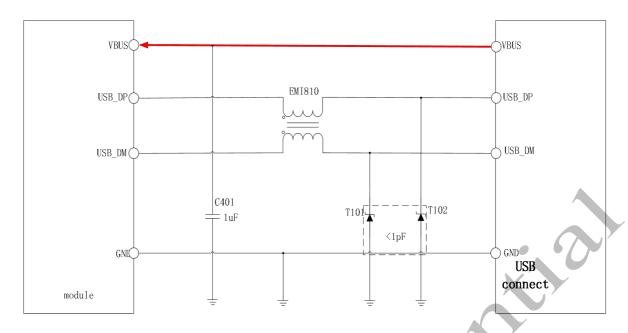

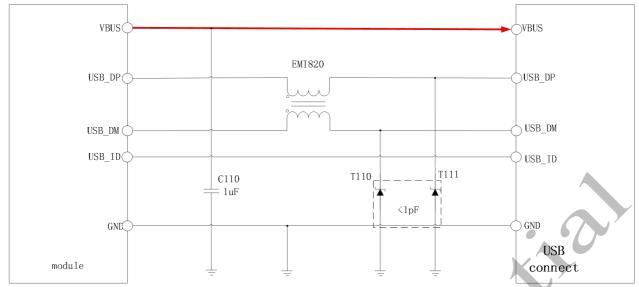

|   | 4.9 USB Interface                                 | 49<br>51 |

|   | 4.10.1 USB PCB layout                             |          |

|   | 4.10 Charging Interface                           |          |

|   | 4.10.1 Charging Detection                         |          |

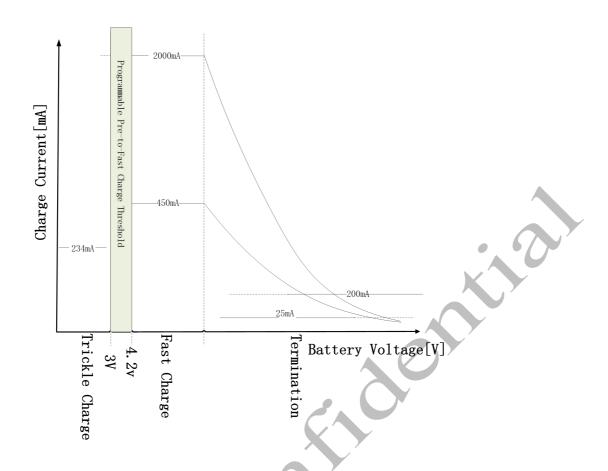

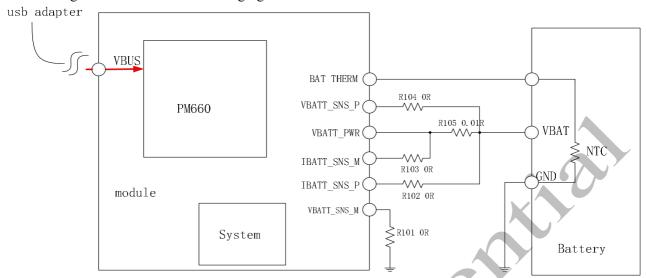

|   | 4.10.2 Charge Control                             | 53       |

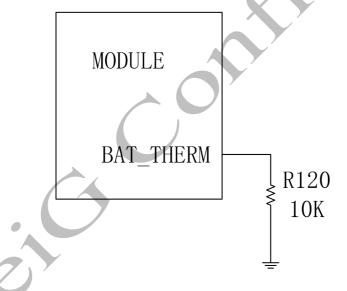

|   | 4.10.3 BAT CON TEM                                |          |

|   | 4.11 UIM Card Interface                           |          |

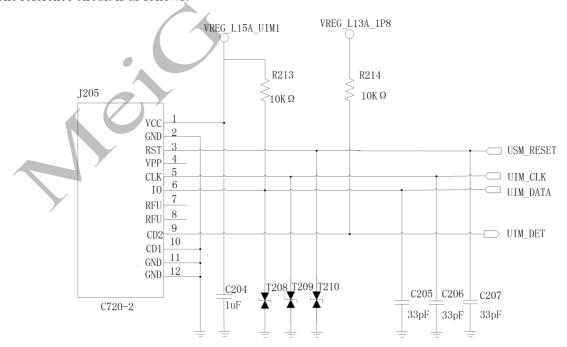

|   | 4.11.1 UIM card interface circuit                 |          |

|   | 4.11.2 UIM card PCB layout                        |          |

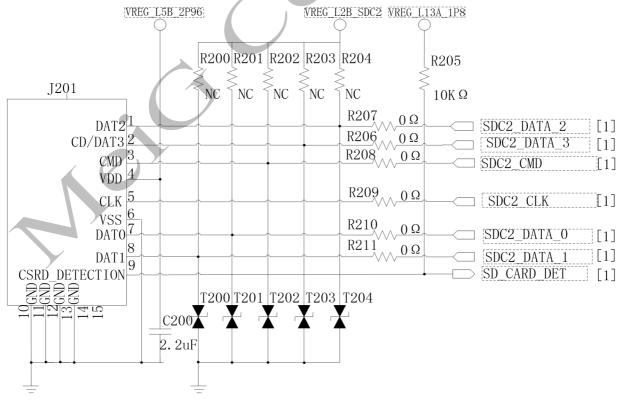

|   | 4.12 SD Card Interface                            |          |

|   | 4.13 I2C Bus Interface                            |          |

|   | 4.14 Analog to Digital Converter (ADC)            |          |

|   | 4.15 PWM                                          |          |

|   | 4.16 Motor                                        | 57       |

|   | 4.17 Antenna Interface                            | 57       |

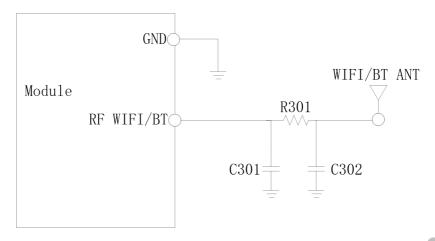

|   | 4.17.1 Wi-Fi/BT antenna                           | 57       |

|   | 4.17.2 Antenna PCB layout                         | 58       |

| 5 | Electrical, Reliability                           |          |

|   | 5.1 Absolute Maximum                              |          |

|   | 5.2 Working Temperature                           |          |

|   | 5.3 Working Voltage                               |          |

|   | 5.4 Digital Interface Features                    |          |

|   | 5.5 SIM_VDD Feature                               |          |

|   | 5.6 PWRKEY Feature                                |          |

|   | 5.7 VCOIN Feature Current consumption (VBAT=3.8V) |          |

|   | 5.8 Current consumption (VBAT=3.8V)               |          |

|   | 5.9 Electrostatic Protection                      |          |

|   | 5.10 WIFI Main RF Performance                     |          |

|   | 5.11 BT Main RF Performance                       |          |

|   | 5.12 Important Notice to OEM integrator           | 65       |

| 6 | Produ | ction                              | 60 |

|---|-------|------------------------------------|----|

|   | 6.1   | Top and Bottom Views of The Module | 6′ |

|   |       | Humidity Sensitivity (MSL)         |    |

|   |       | Baking Requirements                |    |

| 7 | Apper | ndix                               | 68 |

|   |       | Related Documents                  |    |

|   | 7.2   | Terms and Explanations             | 70 |

# **Revision History**

| Date       | Revision | Description   | Author   |

|------------|----------|---------------|----------|

| 2022/11/05 | 1.00     | First version | Hardware |

# 1 Introduction

This document describes the hardware application interface of the module, including the connection of the circuit and the RF interface. It can help users quickly understand the interface definition, electrical performance, and structural dimensions of the module. Combining this document with other application documents, users can quickly use modules to design mobile communication applications.

# 2 Module overview

SNM909 core board, the main chip is Qualcomm Snapdragon 600 series SDM660, the CPU is made of 14nm FinFET, built-in 64bit ARM, 8-core Kryo 260 CPU (Kryo Gold: quad high-performance cores targeting 2.2 GHz, Kryo Silver: quad low-power cores targeting 1.843 GHz). 2.2G processor, support LPDDR4/4X SDRAM memory. The support card memory is 128GB+4GB.

SNM909 provides high-speed broadband data access while providing WiFi, BT functions; Products support double 1600W 3D Camera or depth of field photography, can be widely used in police law enforcement instrument, intelligent POS cash register, logistics terminal, VR Camera, intelligent robot, video surveillance, security monitoring, vehicle equipment, intelligent information acquisition equipment, intelligent handheld terminals, drones and other products.

The physical interface of the module is a 653 pin pad, which provides the following hardware interfaces:

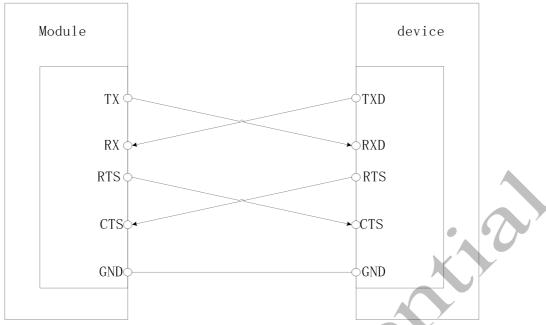

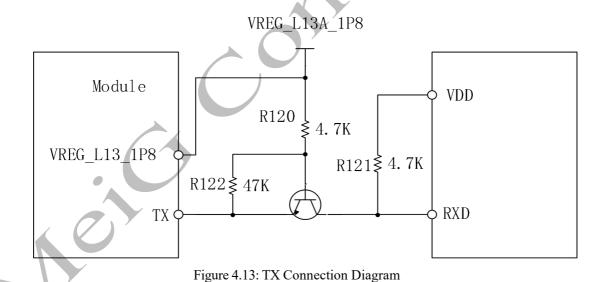

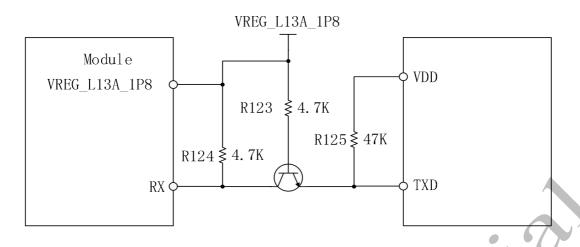

- 2 sets of 1.8V UART serial ports, supporting four or two wires

- LCD interface (MIPI interface)

- LCD backlight interface

- Camera interface (MIPI interface)

- flash interface

- High speed USB interface

- analog audio input interface

- Digital MIC interface

- Audio output interface

- GPIO interface

- I2C interface

- Indicates the SPI interface

- TF card interface

- Supports WiFi and Bluetooth 5.x functions.

# 2.1 Summary of features

Table 2.1: SNM909 features

| Product characteristics | Description                                                                                       |                                                                                       |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

|                         | Orgalia array CDMC                                                                                | (0                                                                                    |  |  |

| Platform                | Qualcomm SDM6                                                                                     |                                                                                       |  |  |

| CPU                     | Octa-core Kryo 26                                                                                 | 0 CPU                                                                                 |  |  |

| GPU                     | Adreno512;650MF                                                                                   | łz                                                                                    |  |  |

| System memory           | 32GB eMMC + 3C                                                                                    | GB LPDDR4X 1866Mhz可兼容64GB+4GB,128GB+8GB                                               |  |  |

| OS                      | Android 10.0                                                                                      |                                                                                       |  |  |

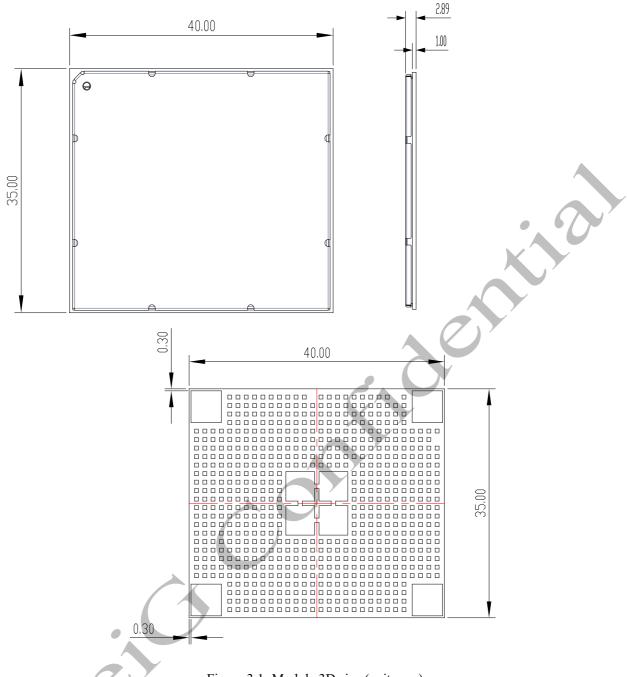

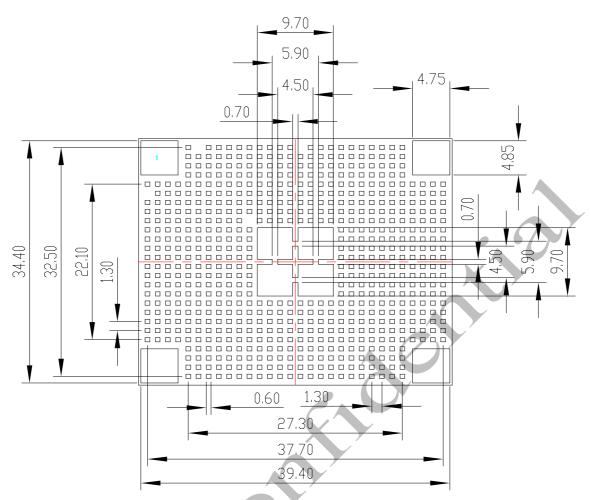

| Size                    | 40*35*2.89mm                                                                                      |                                                                                       |  |  |

| Wi-Fi                   | WCN3990:IEEE 8                                                                                    | 02.11b/g/n/a/ac 2.4G&5G                                                               |  |  |

| Bluetooth               | BT 5.x                                                                                            |                                                                                       |  |  |

| Display                 | Matrix:<br>FULL HD: 2560*1                                                                        |                                                                                       |  |  |

| (Main/Sub)              | LCD Size: User defined                                                                            |                                                                                       |  |  |

|                         | Interface: 1st LCM: MIPI DSI 4-lane; 2nd LCM: MIPI DSI 4-lane                                     |                                                                                       |  |  |

|                         | Interface: supports 3 sets of 4-Lane CSI interface                                                |                                                                                       |  |  |

| Camera                  | Camera Pixel:Rear CAM16-16Mp, Dual ISP supports up to 24MP Camera, Front CAM supports up to 16MP. |                                                                                       |  |  |

| (Rear/Front)            | From CAW suppor                                                                                   | 4K30 8-bit: H.264/VP8/VP9                                                             |  |  |

| (Real/1 font)           | Video decode                                                                                      | 4K30 10-bit: HEVC                                                                     |  |  |

|                         | Video encode                                                                                      | 4K30 HEVC/H264/VP8/MPEG4                                                              |  |  |

| T 1                     | Keys (Power_on/off, Home, Reset, Volume +, Volume -)                                              |                                                                                       |  |  |

| Input device            | Capacitive TP                                                                                     |                                                                                       |  |  |

| Reset                   | Support hardware reset                                                                            |                                                                                       |  |  |

|                         | Interface name                                                                                    | Main function description                                                             |  |  |

| (7)                     | VBAT                                                                                              | Module power input $3.5\mathrm{V}{\sim}4.2\mathrm{V}$ , Nominal value $3.8\mathrm{V}$ |  |  |

|                         | SDIO *1                                                                                           | TF Card, support up to 128GB                                                          |  |  |

|                         | USB2.0(3.0)                                                                                       | Support OTG USB_BOOT (Forced USB for emergency download)                              |  |  |

| Application interface   | BLSP ports                                                                                        | 8 ports (BLSP1-8), 4-bits each, multiplexed serial interface functions                |  |  |

|                         | UART*3                                                                                            | BLSP1-2,BLSP7-8&BLSP5 support UART, up to 4 Mbps                                      |  |  |

|                         | I2C*9                                                                                             | BLSP1-8&LPI_GPIO2-3 support I2C                                                       |  |  |

|                         | SPI(master only)                                                                                  | SPI is only support via BLSP                                                          |  |  |

|                         | ADC*2                                                                                             | Support                                                                               |  |  |

|                         | Charge                                                                                            | Support Quick Charge 4.0                                                              |  |  |

| Motor     | Support                                                 |

|-----------|---------------------------------------------------------|

| GPIO      | 100 GPIOs                                               |

| VCOIN     | Real time clock backup battery                          |

| 射频接口      | 2.4G WiFi/BT antenna                                    |

| 71.7火1女 口 | 5G WIFI- antenna                                        |

|           | 1 main MIC                                              |

|           | 1 sub MIC                                               |

|           | 1 hands-free speaker (built-in 0.8W Class D power       |

| Audio     | amplifier)                                              |

|           | 1 channel stereo headset (with headset MIC)             |

|           | 2 digital MIC signals (can support 4 digital MIC at the |

|           | same time)                                              |

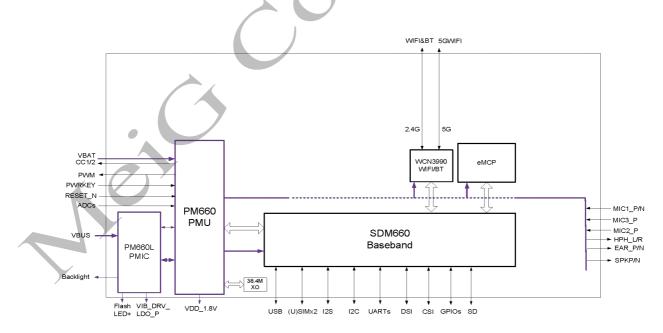

# 2.2 Block diagram

The following figure lists the main functional parts of the module:

- SDM660 -- Baseband chip

- PM660, PM660L -- Power management chip

- WCN3990-WIFI/BT Two-in-one chip

- Antenna interface

- LCD/CAM-MIPI interface

- EMCP --Memory chip

- AUDIO interface

- Serial ports, SD card interface, SIM interface, I2C interface, etc.

Figure 2.1: Functional block diagram of the module

# 3 Module Package

# 3.1 Pin definitions

Table 3.1: Pin description (GPIOs with '\*' support INT)

| PIN#    | SNM_909 Pin name          | GPIO<br>Interrupt | Pad characteristics | Functional description                                                                                                                                         |

|---------|---------------------------|-------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1      | GND                       |                   | GND                 | GND                                                                                                                                                            |

| A5      | GND                       |                   | GND                 | GND                                                                                                                                                            |

| A7      | GND                       |                   | GND                 | GND                                                                                                                                                            |

| A8-A22  | NC                        |                   | NC                  | NC                                                                                                                                                             |

| A26     | GND                       |                   | GND                 | GND                                                                                                                                                            |

| В5      | GND                       |                   | GND                 | GND                                                                                                                                                            |

| В6      | CH0_FEM_QM48858_<br>ANT 3 |                   | AI, AO              | WLAN/BT Antenna port 0                                                                                                                                         |

| В7      | GND                       |                   | GND                 | GND                                                                                                                                                            |

| В8      | NC                        |                   | NC                  | NC                                                                                                                                                             |

| В9      | WCD_SB_DATA0              | LPI_GPIO_20       | DO                  | Module internal used. Do not connect (leave floating).                                                                                                         |

| B10     | CC_OUT                    |                   | AO                  | 1.8V push-pull tri-state output indicating CC1 or CC2 connection (orientation).                                                                                |

| B11     | USB_ID                    |                   | AI                  | OTG mode enable or CC1 pin for the USB Type-C connector (userprogrammable).Requires IEC protection.                                                            |

| B12     | BEEP_VOL1                 | GPIO_2            | В                   | 32 kHz clock for WiPower. When WiPower is not used,then this GPIO can be reused for other purpose.                                                             |

| B13     | VREG_WLED                 |                   | AO                  | WLED boost output                                                                                                                                              |

| B14     | WLED_SINK2                |                   | AI                  | WLED low-side current sink input, string 2                                                                                                                     |

| B15-B16 | GND                       |                   | GND                 | GND                                                                                                                                                            |

| B17     | IBATT_SNS_M               |                   | AI                  | Battery minus terminal sense input. Connect this directly to the battery negative node.                                                                        |

| B18     | VBATT_SNS_P               |                   | AI                  | Battery plus terminal sense input. Connect this directly to the battery positive node.                                                                         |

| B19     | PM_USB_SNS                |                   | AI                  | USB input voltage sense pin from the external 28 V OVP.                                                                                                        |

| B20     | DC_EN                     |                   | DO                  | Enable the DC_IN path from the external power multiplexer or external FET control.                                                                             |

| B21,B22 | USB_VBUS_IN               |                   | PI, PO              | Input power from the selected source (USB or WiPower), or output during USB-OTG. This is a power entry node for the charger and connects to the OVP circuitry. |

| C5-C7   | GND                       |                   | GND                 | GND                                                                                                                                                            |

|         | l .                       | I .               | <u> </u>            |                                                                                                                                                                |

| C8      | WCD_SB_CLK     | LPI_GPIO_19 |        | Module internal used. Do not connect (leave floating).                                                                                                                       |

|---------|----------------|-------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С9      | WCD_RESET_N    | LPI_GPIO_24 |        | Module internal used. Do not connect (leave floating).                                                                                                                       |

| C10     | GND            |             | GND    | GND                                                                                                                                                                          |

| C11     | SPKR_DRV_P     |             | AO     | Class-D speaker driver output, plus (+)                                                                                                                                      |

| C12     | UUSB_TYPEC_SEL |             | MV     | Used for Type-C and Micro USB select                                                                                                                                         |

| C13     | WLED_SINK3     |             | AI     | WLED low-side current sink input, string 3                                                                                                                                   |

| C14     | LCD_BKL_PWM    |             | DI     | External dimming control pin PWM input, controls LED brightness.                                                                                                             |

| C15     | VREG_L6B_3P3_1 |             | PO     | L6B LDO regulated output                                                                                                                                                     |

| C16     | VREG_BOB       |             | PO     | Regulated BOB output                                                                                                                                                         |

| C17     | IBATT_SNS_P    |             | AI     | Battery plus terminal sense input. Connect this directly to the battery positive node.                                                                                       |

| C18     | VBATT_SNS_M    |             | AI     | Battery voltage sense input minus. Connect to the battery negative remote sense node or connect this directly to the battery negative node.                                  |

| C19     | STAT_CHG       |             | DO     | Status/fault/interrupt indicator. Indicates charging, fault status, or enable for parallel charging. Multiplexed static (fault) or pulsed output (IRQ).Programmable polarity |

| C20     | USB_EN         |             | DO     | Enable the USB path from the external 28 V OVP.                                                                                                                              |

| C21-C22 | USB_VBUS_IN    |             | PI, PO | Input power from the selected source (USB or WiPower), or output during USB-OTG. This is a power entry node for the charger and connects to the OVP circuitry.               |

| D5-D7   | GND            |             | GND    | GND                                                                                                                                                                          |

| D8      | WCD_SB_DATA1   |             |        | Do not connect (leave floating). Reserved pin.                                                                                                                               |

| D9      | WCD_INT1       |             |        | Do not connect (leave floating). Reserved pin.                                                                                                                               |

| D10     | GND            |             | GND    | GND                                                                                                                                                                          |

| D11     | SPKR_DRV_M     |             | AO     | Class-D speaker driver output, minus (-)                                                                                                                                     |

| D12     | CDC_IN1_P      |             | AI     | Microphone input 1, plus                                                                                                                                                     |

| D13     | WLED_SINK1     |             | AI     | WLED low-side current sink input, string 1                                                                                                                                   |

| D14     | RGB_GRN        |             | AO     | RGB LED high-side current source for the green LED                                                                                                                           |

| D15     | VREG_L6B_3P3_1 |             | РО     | L6B LDO regulated output                                                                                                                                                     |

| D16     | VREG BOB       |             | PO     | Regulated BOB output                                                                                                                                                         |

| D17       | USB_CC2           |         | AI               | CC2 pin for the USB Type-C connector.                                                                                                                         |

|-----------|-------------------|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D18       | PMI_HAP_OUT_P     |         | AO               | Haptics H-bridge driver output plus                                                                                                                           |

| D19       | DC_SNS            |         | AI               | Voltage sense for DC_IN path                                                                                                                                  |

| D20       | VREG_L18A_2P85    |         | РО               | L18A LDO regulated output                                                                                                                                     |

| D21-D22   | USB_VBUS_IN       |         | PI, PO           | Input power from the selected source (USB or WiPower),or output during USB-OTG. This is a power entry node for the charger and connects to the OVP circuitry. |

| DD1       | GND               |         | GND              | GND                                                                                                                                                           |

| AA5       | DP_AUX_EN_N       | GPIO_55 | B-PD:nppukp      | Configurable I/O                                                                                                                                              |

| AA6       | BEEP_EN           | GPIO_13 | B-PD:nppukp      | Configurable I/O                                                                                                                                              |

| AA7-AA12  | GND               |         | GND              | GND                                                                                                                                                           |

| AA13      | NFC_EN            | GPIO_8  | B-PD:nppukp      | Configurable I/O                                                                                                                                              |

| AA14      | LCD_RST_N         | GPIO_53 | B-PD:nppukp      | Configurable I/O                                                                                                                                              |

| AA15      | MIPI_DSI0_LANE1_N |         | AI, AO           | MIPI display serial interface 0 lane 1– positive                                                                                                              |

| AA16      | MIPI_DSI0_LANE1_P |         | AI, AO           | MIPI display serial interface 0 lane 1– negative                                                                                                              |

| AA17-AA22 | GND               |         | GND              | GND                                                                                                                                                           |

| DD26      | GND               |         | GND              | GND                                                                                                                                                           |

| BB5       | SMB_STAT          | GPIO_21 | B-PD:nppukp      | Configurable I/O                                                                                                                                              |

| BB6       | SPI_CLK_WSA_EN2   | GPIO_27 | B-PD:nppukp      | Configurable I/O                                                                                                                                              |

| BB7       | JTAG_TDO          |         | DO-Z             | JTAG data output                                                                                                                                              |

| BB8       | SDC2_CMD          |         | BH-PD:<br>nppukp | Secure digital controller 2 command                                                                                                                           |

| BB9       | SDC2_DATA_0       |         | BH-PD:<br>nppukp | Secure digital controller 2 data bit 0                                                                                                                        |

| BB10      | SDC2_DATA_1       |         | BH-PD:           | Secure digital controller 2 data bit 1                                                                                                                        |

| BB11      | SDC2_CLK          |         | BH-NP: dpukp     | Secure digital controller 2 clock                                                                                                                             |

| BB12      | MIPI_DSI1_LANE3_N |         | AI, AO           | MIPI display serial interface 1 lane 3– negative                                                                                                              |

| BB13      | MIPI_DSI1_LANE0_N |         | AI, AO           | MIPI display serial interface 1 lane 0– negative                                                                                                              |

| BB14      | MIPI_DSI1_LANE1_N |         | AI, AO           | MIPI display serial interface 1 lane 1– negative                                                                                                              |

| BB15      | MIPI_DSI1_LANE2_N |         | AI, AO           | MIPI display serial interface 1 lane 2– negative                                                                                                              |

| BB16      | MIPI_DSI1_CLK_N   |         | AO               | MIPI display serial interface 1 clock  – negative                                                                                                             |

| BB17      | USB0_SS_TX_P      |         | AO               | USB super-speed 0 transmit – plus                                                                                                                             |

| BB18      | USB1_SS_RX_M      |         | AI               | USB super-speed 1 receive – minus                                                                                                                             |

| BB19      | USB1_SS_TX_M      |         | AO               | USB super-speed 1 transmit – minus                                                                                                                            |

| BB20     | USB0_SS_RX_M      |          | AI               | USB super-speed 0 receive – minus                                                                                    |

|----------|-------------------|----------|------------------|----------------------------------------------------------------------------------------------------------------------|

| BB21     | USB1_HS_DM        |          | AI, AO           | USB high-speed 1 data – minus                                                                                        |

| BB22     | USB1_HS_DP        |          | AI, AO           | USB high-speed 1 data – plus                                                                                         |

| CC5      | OTG_OUT_EN        | GPIO_113 | B-PD:nppukp      | Configurable I/O                                                                                                     |

| CC6      | LNBBCLK1_EN       |          |                  | Module internal used. Do not connect (leave floating).                                                               |

| CC7      | SDM_SWR_CLK       | GPIO_24  | DO               | SoundWire clock                                                                                                      |

| CC8      | SDM_SWR_DATA      | GPIO_25  | В                | SoundWire data                                                                                                       |

| CC9      | SPI_CS_N_WSA_EN1  | GPIO_26  | B-PD:nppukp      | Configurable I/O                                                                                                     |

| CC10     | SDC2_DATA_3       |          | BH-PD:<br>nppukp | Secure digital controller 2 data bit 3                                                                               |

| CC11     | SDC2_DATA_2       |          | BH-PD:<br>nppukp | Secure digital controller 2 data bit 2                                                                               |

| CC12     | MIPI_DSI1_LANE3_P |          | AI, AO           | MIPI display serial interface 1 lane 3 – positive                                                                    |

| CC13     | MIPI_DSI1_LANE0_P |          | AI, AO           | MIPI display serial interface 1 lane 0– positive                                                                     |

| CC14     | MIPI_DSI1_LANE1_P |          | AI, AO           | MIPI display serial interface 1 lane 1– positive                                                                     |

| CC15     | MIPI_DSI1_LANE2_P |          | AI, AO           | MIPI display serial interface 1 lane 2– positive                                                                     |

| CC16     | MIPI_DSI1_CLK_P   |          | AØ               | MIPI display serial interface 1 clock  – positive                                                                    |

| CC17     | USB0_SS_TX_M      |          | AO               | USB super-speed 0 transmit – minus                                                                                   |

| CC18     | USB1_SS_RX_P      |          | AI               | USB super-speed 1 receive – plus                                                                                     |

| CC19     | USB1_SS_TX_P      |          | AO               | USB super-speed 1 transmit – plus                                                                                    |

| CC20     | USB0_SS_RX_P      |          | AI               | USB super-speed 0 receive – plus                                                                                     |

| CC21     | USB2_HS_DM        |          | AI, AO           | USB high-speed 2 data – minus                                                                                        |

| CC22     | USB2_HS_DP        |          | AI, AO           | USB high-speed 2 data – plus                                                                                         |

| DD5-DD22 | NC                |          | NC               | NC                                                                                                                   |

| L1       | NC                |          | NC               | NC                                                                                                                   |

| L2-L5    | GND               |          | GND              | GND                                                                                                                  |

| L6       | LPI_UART_1_TX     |          | DO               | Module internal used. Do not connect (leave floating).                                                               |

| L7       | WP_IF             |          | В                | Open Drain, single wire (half-duplex) UART between WiPower IC and BT subsystem to exchange WiPower related messages. |

| L8-L9    | GND               |          | GND              | GND                                                                                                                  |

| M10      | GND               |          | GND              | GND                                                                                                                  |

| L18      | GND               |          | GND              | GND                                                                                                                  |

| L19      | PON_OUT           |          |                  | Module internal used. Do not connect (leave floating).                                                               |

| L20      | BEEP_VOL2         | GPIO_11  | LV               | Configurable I/O                                                                                                     |

| L21      | QNOVO_FET_CTL     | GPIO_13  | LV               | Qnovo FET discharge control                                                                                          |

| L22    | GND               |             | GND         | GND                                                           |

|--------|-------------------|-------------|-------------|---------------------------------------------------------------|

| L23    | PTT               | GPIO_43     | B-PD:nppukp | Configurable I/O                                              |

| L24    | MIPI_CSI1_LANE2_P |             | AI          | MIPI CSI 1, differential lane 2 – plus                        |

| L25    | MIPI_CSI1_LANE2_M |             | AI          | MIPI CSI 1, differential lane 2 – minus                       |

| L26    | NC                |             | NC          | NC                                                            |

| M1     | NC                |             | NC          | NC                                                            |

| M2-M6  | GND               |             | GND         | GND                                                           |

| M7     | SDM660_GPIO_73    | GPIO_73     | B-PD:nppukp | Configurable I/O                                              |

| M8     | SCAN_LED_G        | GPIO_61     | B-PD:nppukp | Configurable I/O                                              |

| M9,M10 | GND               |             | GND         | GND                                                           |

| M18    | GND               |             | GND         | GND                                                           |

| M19    | CCI_I2C_SDA0      | GPIO_36     | В           | Dedicated camera control interface I2C 0 serial data          |

| M20    | CCI_I2C_SCL0      | GPIO_37     | В           | Dedicated camera control interface I2C 0 clock                |

| M21    | CAM_AVDD_EN       | GPIO_51     | B-PD:nppukp | Configurable I/O                                              |

| M22    | CAM0_MCLK         | GPIO_32     | DO          | Camera master clock 0                                         |

| M23    | RESIN_N           |             | DI          | Input pad used for generating reset when held at a logic low. |

| M24    | MIPI_CSI1_LANE3_M |             | AI          | MIPI CSI 1, differential lane 3 – minus                       |

| M25    | MIPI_CSI1_LANE3_P |             | AI          | MIPI CSI 1, differential lane 3 – plus                        |

| M26    | NC                |             | NC          | NC                                                            |

| N1     | NC                |             | NC          | NC                                                            |

| N2-N9  | GND               |             | GND         | GND                                                           |

| N18    | GND               |             | GND         | GND                                                           |

| N19    | LPI_SPI_1_CLK     | LPI_GPIO_9  | DO          | LPI SPI 1 clock                                               |

| N20    | LPI_SPI_1_MISO    | LPI_GPIO_11 | DI          | LPI SPI 1 data master in/slave out                            |

| N21    | CAM_FR_STANDBY    | GPIO_49     | B-PD:nppukp | Configurable I/O                                              |

| N22    | CAM1_MCLK         | GPIO_33     | DO          | Camera master clock 1                                         |

| N23    | GND_141           |             | GND         | GND                                                           |

| N24    | MIPI_CSI1_CLK_P   |             | AI          | MIPI CSI 1, differential clock – plus                         |

| N25    | MIPI_CSI1_CLK_M   |             | AI          | MIPI CSI 1, differential clock – minus                        |

| N26    | NC                |             | NC          | NC                                                            |

| O1     | NC                |             | NC          | NC                                                            |

| O2     | GND               |             | GND         | GND                                                           |

| О3     | BLSP_GPIO_31      | GPIO_31     | В           | BLSP 8 bit 0; SPI, UART, or I2C                               |

| O4     | BLSP_GPIO_30      | GPIO_30     | В           | BLSP 8 bit 1; SPI, UART, or I2C                               |

| O5      | BLSP_GPIO_28      | GPIO_28     | В           | BLSP 8 bit 3; SPI, UART, or I2C                           |

|---------|-------------------|-------------|-------------|-----------------------------------------------------------|

| O6      | GND               |             | GND         | GND                                                       |

| О7      | SCAN_I2C_SDA      | GPIO_22     | В           | BLSP 6 bit 1; I2C serial data                             |

| O8      | SCAN_I2C_SCL      | GPIO_23     | В           | BLSP 6 bit 0; I2C serial clock                            |

| О9      | GND               |             | GND         | GND                                                       |

| O18     | GND               |             | GND         | GND                                                       |

| O19     | LPI_I2C_3_SDA     | LPI_GPIO_2  | В           | LPI I2C 3 serial data                                     |

| O20     | LPI_SPI_1_CS1_N   | LPI_GPIO_0  | DO          | LPI SPI 1 chip select 1                                   |

| O21     | GND               |             | GND         | GND                                                       |

| O22     | CAM0_RST_N        | GPIO_46     | B-PD:nppukp | Configurable I/O                                          |

| O23     | GND               |             | GND         | GND                                                       |

| O24     | MIPI_CSI1_LANE0_P |             | AI          | MIPI CSI 1, differential lane 0 – plus                    |

| O25     | MIPI_CSI1_LANE0_M |             | AI          | MIPI CSI 1, differential lane 0 – minus                   |

| O26     | NC                |             | NC          | NC                                                        |

| P2      | RF_TP             |             | AI, AO      | For RF test purpose only.Do not connect (leave floating). |

| Р3      | GND               |             | GND         | GND                                                       |

| P4      | BLSP_GPIO_29      | GPIO_29     | В           | BLSP 8 bit 2; SPI or UART                                 |

| P5-P7   | GND               |             | GND         | GND                                                       |

| P8      | LP4X_MODE         |             |             | Module internal used. Do not connect (leave floating).    |

| Р9      | GND               |             | GND         | GND                                                       |

| P18     | GND               |             | GND         | GND                                                       |

| P19     | LPI_I2C_3_SCL     | LPI_GPIO_3  | В           | LPI I2C 3 serial clock                                    |

| P20     | LPI_SPI_1_MOSI    | LPI_GPIO_10 | DO          | LPI SPI 1 data master out/slave in                        |

| P21     | GND               |             | GND         | GND                                                       |

| P22     | CAM1_RST_N        | GPIO_47     | B-PD:nppukp | Configurable I/O                                          |

| P23-P24 | GND               |             | GND         | GND                                                       |

| P25     | SDM660_GPIO_35    | GPIO_35     | B-PD:nppukp | Configurable I/O                                          |

| P26     | NC                |             | NC          | NC                                                        |

| Q1      | NC                |             | NC          | NC                                                        |

| Q2-Q4   | VREG_L13A_1P8     |             | РО          | L13A LDO regulated output                                 |

| Q5-Q9   | GND               |             | GND         | GND                                                       |

| Q18-Q19 | GND               |             | GND         | GND                                                       |

| Q20     | LPI_SPI_1_CS0_N   | LPI_GPIO_8  | DO          | LPI SPI 1 chip select                                     |

| Q21-Q24 | GND               |             | GND         | GND                                                       |

| Q25     | BOOT_CONFIG_0     | GPIO_96     | B-PD:nppukp | Boot configuration control bit 0;<br>Configurable I/O     |

| Q26     | NC             |                    | NC          | NC                                                                              |

|---------|----------------|--------------------|-------------|---------------------------------------------------------------------------------|

| R1      | NC             |                    | NC          | NC                                                                              |

| R2-R9   | GND            |                    | GND         | GND                                                                             |

| R18-R24 | GND            |                    | GND         | GND                                                                             |

| R25     | PON_RESET_N    |                    | DIS         | Reset input                                                                     |

| R26     | NC             |                    | NC          | NC                                                                              |

| S1      | NC             |                    | NC          | NC                                                                              |

| S2      | GND            |                    | GND         | GND                                                                             |

| S3      | TS_KP_I2C_SCL  | GPIO_15            | DO          | Touch Panel I2C Clock                                                           |

| S4      | TS_KP_I2C_SDA  | GPIO_14            | В           | Touch Panel I2C Data                                                            |

| S5-S9   | GND            |                    | GND         | GND                                                                             |

| S18     | GND            |                    | GND         | GND                                                                             |

| S19     | LPI_SPI_2_CLK  | LPI_GPIO_5         | DO          | LPI SPI 2 clock                                                                 |

| S20-S22 | GND            |                    | GND         | GND                                                                             |

| S23     | NFC_INT_N      | GPIO_40            | B-PD:nppukp | Configurable I/O                                                                |

| S24     | SCAN_BUTTON_2  | GPIO_45            | B-PD:nppukp | Configurable I/O                                                                |

| S25     | BB_VOLTAGE_DET | GPIO_48            | B-PD:nppukp | Configurable I/O                                                                |

| S26     | NC             |                    | NC          | NC                                                                              |

| E1-E7   | GND            |                    | GND         | GND                                                                             |

| E8      | WCD_INT2       | A U                |             | Do not connect (leave floating).<br>Reserved pin.                               |

| E9      | NC             |                    | NC          | NC                                                                              |

| E10     | CDC_EAR_M      |                    | AO          | Earpiece output, minus (-)                                                      |

| E11     | CDC_MIC2_P     |                    | AI          | Microphone input 2                                                              |

| E12     | CDC_IN1_M      |                    | AI          | Microphone input 1,minus                                                        |

| E13     | KEY_VOL_UP     | PM660L_GPIO<br>_07 | MV          | Volume up key                                                                   |

| E14     | RGB_RED        |                    | AO          | RGB LED high-side current source for the red LED                                |

| E15     | FLASH_LED1     |                    | AO          | Flash high-side current source for LED1.                                        |

| E16     | LNBBCLK3       |                    | DO          | 19.2 MHz baseband (low-power) XO clock buffer output                            |

| E17     | VCONN_EN       |                    | DO          | Digital output to toggle the external FET gate drive.                           |

| E18     | VCONN_IN       |                    | AI          | An external 5 V supply is applied to this pin to support Type-C powered cables. |

| E19     | PMI_HAP_OUT_M  |                    | AO          | Haptics H-bridge driver output minus                                            |

| E20     | VREG_L15A_UIM1 |                    | PO          | L15A LDO regulated output                                                       |

| E21-E22 | USB_VBUS_IN    |                    | PI, PO      | Input power from the selected source (USB or WiPower),or output during          |

|         |                           |                    |        | USB-OTG. This is a power entry node for the charger and connects to the OVP circuitry.                                                                                                                    |

|---------|---------------------------|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E23     | VREG_L17A_UIM2            |                    | PO     | L17A LDO regulated output                                                                                                                                                                                 |

| E24     | BATT_THERM_BIAS           |                    | AO     | Dedicated voltage source for BATT_THERM resistor network biasing.                                                                                                                                         |

| E25     | UIM1_PRESENT              | GPIO_90            | DI     | UIM1 presence detection                                                                                                                                                                                   |

| E26     | NC                        |                    | NC     | NC                                                                                                                                                                                                        |

| F2      | CH1_FEM_QM48858_<br>ANT_3 |                    | AI, AO | WLAN/BT Antenna port 1                                                                                                                                                                                    |

| F3-F8   | GND                       |                    | GND    | GND                                                                                                                                                                                                       |

| F9      | CDC_MIC_BIAS2             |                    | AO     | Microphone bias 2                                                                                                                                                                                         |

| F10     | CDC_EAR_P                 |                    | AO     | Earpiece output, plus (+)                                                                                                                                                                                 |

| F11     | CDC_HPH_R                 |                    | AO     | Headphone output, right channel                                                                                                                                                                           |

| F12     | HEADSET_DETECT            |                    | AI     | Headset detection                                                                                                                                                                                         |

| F13     | CDC_IN3_P                 |                    | AI     | Microphone input 3                                                                                                                                                                                        |

| F14     | BEEP_PWM                  | PM660L_GPIO<br>06  | MV     | Configurable I/O                                                                                                                                                                                          |

| F15     | FLASH_LED1                |                    | AO     | Flash high-side current source for LED1.                                                                                                                                                                  |

| F16     | WIPWR_CHG_OK              |                    | DO     | Charger request hardware output signal to the WiPower interface. Hi-Z indicates a WiPower charge request. It asserts low to indicate that charging is complete or that WiPower charging is not requested. |

| F17-F18 | GND                       |                    | GND    | GND                                                                                                                                                                                                       |

| F19     | PWR_BUTTON                |                    | DI     | Input pad generally connected to a keypad power-on button and when grounded, initiates the power-on sequence. Pulled up internally to 1.8 V via the dVdd regulator.                                       |

| F20     | USB_IN_MID                |                    | AO     | Opitional power support for VCONN.                                                                                                                                                                        |

| F21-F22 | USB_VBUS_IN               |                    | PI, PO | Input power from the selected source (USB or WiPower),or output during USB-OTG. This is a power entry node for the charger and connects to the OVP circuitry.                                             |

| F23     | VREG_L11A_1P8             |                    | РО     | L11A LDO regulated output                                                                                                                                                                                 |

| F24     | UIM1_RESET                | GPIO_89            | DO     | UIM1 reset                                                                                                                                                                                                |

| F25     | VREG_L14A_1P8             |                    | РО     | L14A LDO regulated output                                                                                                                                                                                 |

| F26     | NC                        |                    | NC     | NC                                                                                                                                                                                                        |

| G1-G8   | GND                       |                    | GND    | GND                                                                                                                                                                                                       |

| G9      | CDC_MIC_BIAS1             |                    | AO     | Microphone bias 1                                                                                                                                                                                         |

| G10     | REAR_DVDD_EN              | PM660L_GPIO<br>_04 | LV     | Enable for camera LDO2                                                                                                                                                                                    |

| G11 HPH_GND_SENSE AI Headphone ground reference  G12 FRONT_DVDD_EN L V Enable for camera LDO1  G13 GGND_CFILT GND Microphone bias filter ground  G14 RGB_BLU AO RGB LED high-side current source for the blue LED  G15 FLASH_LED1 AO Flash high-side current source for LED1.  G16-G17 FLASH_LED3 AO Flash high-side current source for LED3.  G18 VBATT_PWR PI, PO Charging, and input is for all other operations.  G19 BOOT_PWR AO (LDO) output 50 mA (minimum) output supply.  G20 GND GND GND  G21 BATT_ID AI MIPI BIP interface. It can be used for missing battery detection.  G22 GND GND GND GND  G23 VREG L16A 2P7 PO L16A LDO regulated output |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G13 GGND_CFILT  GND Microphone bias filter ground  G14 RGB_BLU  AO RGB LED high-side current source for the blue LED  G15 FLASH_LED1  AO Flash high-side current source for LED1.  G16-G17 FLASH_LED3  AO Flash high-side current source for LED3.  G18 VBATT_PWR  PI, PO Charging, and input is for all other operations.  G19 BOOT_PWR  AO (LDO) output 50 mA (minimum) output supply.  G20 GND  GND  GND  GND  GND  GND  GND  GND                                                                                                                                                                                                                      |

| G14  RGB_BLU  AO  RGB LED high-side current source for the blue LED  Flash high-side current source for LED1.  G15  FLASH_LED1  AO  Flash high-side current source for LED1.  G16-G17  FLASH_LED3  AO  Flash high-side current source for LED3.  Battery voltage node. Output is for charging, and input is for all other operations.  G19  BOOT_PWR  AO  GND  GND  GND  GND  GND  GND  GND  GN                                                                                                                                                                                                                                                           |

| G15 FLASH_LED1 AO Flash high-side current source for LED1.  G16-G17 FLASH_LED3 AO Flash high-side current source for LED3.  G18 VBATT_PWR PI, PO Charging, and input is for all other operations.  G19 BOOT_PWR AO (LDO) output 50 mA (minimum) output supply.  G20 GND GND GND  G21 BATT_ID AI MIPI BIF interface. It can be used for missing battery detection.  GND GND  GND GND  GND  GND  GND  GND                                                                                                                                                                                                                                                   |

| G16-G17  FLASH_LED3  AO  ED1.  G16-G17  FLASH_LED3  AO  Flash high-side current source for LED3.  Battery voltage node. Output is for charging, and input is for all other operations.  G19  BOOT_PWR  AO  GND  GND  GND  GND  GND  GND  GND  GN                                                                                                                                                                                                                                                                                                                                                                                                          |

| G18 VBATT_PWR PI, PO Battery voltage node. Output is for charging, and input is for all other operations.  G19 BOOT_PWR AO (LDO) output 50 mA (minimum) output supply.  G20 GND GND GND  G21 BATT_ID AI MIPI BIF interface. It can be used for missing battery detection.  G22 GND GND GND GND  GND GND GND                                                                                                                                                                                                                                                                                                                                               |

| G18 VBATT_PWR  PI, PO charging, and input is for all other operations.  Auxiliary 4.4 V to 5 V low dropout (LDO) output 50 mA (minimum) output supply.  G20 GND  GND  GND  BATT_ID  AI  MIPI BIF interface. It can be used for missing battery detection.  G22 GND  GND  GND  GND  GND  GND  GND  GND                                                                                                                                                                                                                                                                                                                                                     |

| G19 BOOT_PWR AO (LDO) output 50 mA (minimum) output supply.  G20 GND GND GND  Battery ID input to the ADC and MIPI BIF interface. It can be used for missing battery detection.  G22 GND GND GND GND                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| G21 BATT_ID AI Battery ID input to the ADC and MIPI BIF interface. It can be used for missing battery detection.  G22 GND GND GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| G21 BATT_ID AI MIPI BIF interface. It can be used for missing battery detection.  G22 GND GND GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| G23 VREG L16A 2P7 PO L16A LDO regulated output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| G24 UIM2_PRESENT GPIO_86 DI UIM2 presence detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| G25 AUX_THERM AI Battery temperature input to the ADC for the remote thermistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| G26 NC NC NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| H1 NC NC NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |