In this mode, the RESULTDONE event signals has the same meaning as DONE when no oversampling takes place. Note that both events may occur before the actual values have been transferred into RAM by EasyDMA.

Example of RAM placement (even RESULT.MAXCNT), channels 1, 2 and 5 enabled on page 199 provides an example of results placement in Data RAM, with an even RESULT.MAXCNT. In this example, channels 1, 2 and 5 are enabled, all others are disabled.

|                                     | 31 16                        | 15 0                         |

|-------------------------------------|------------------------------|------------------------------|

| RESULT.PTR                          | CH[2] 1 <sup>st</sup> result | CH[1] 1 <sup>st</sup> result |

| RESULT.PTR + 4                      | CH[1] 2 <sup>nd</sup> result | CH[5] 1 <sup>st</sup> result |

| RESULT.PTR + 8                      | CH[5] 2 <sup>nd</sup> result | CH[2] 2 <sup>nd</sup> result |

|                                     | (.                           | )                            |

| RESULT.PTR +<br>(RESULT.MAXCNT – 2) | CH[5] last result            | CH[2] last result            |

Figure 63: Example of RAM placement (even RESULT.MAXCNT), channels 1, 2 and 5 enabled

2\*

Example of RAM placement (odd RESULT.MAXCNT), channels 1, 2 and 5 enabled on page 199 provides an example of results placement in Data RAM, with an odd RESULT.MAXCNT. In this example, channels 1, 2 and 5 are enabled, all others are disabled. The last 32-bit word is populated only with one 16-bit result.

|                                       | 31 16                        | 15 0                         |

|---------------------------------------|------------------------------|------------------------------|

| RESULT.PTR                            | CH[2] 1 <sup>st</sup> result | CH[1] 1 <sup>st</sup> result |

| RESULT.PTR + 4                        | CH[1] 2 <sup>nd</sup> result | CH[5] 1 <sup>st</sup> result |

| RESULT.PTR + 8                        | CH[5] 2 <sup>nd</sup> result | CH[2] 2 <sup>nd</sup> result |

|                                       | (                            | )                            |

| RESULT.PTR +<br>2*(RESULT.MAXCNT – 1) |                              | CH[5] last result            |

Figure 64: Example of RAM placement (odd RESULT.MAXCNT), channels 1, 2 and 5 enabled

# 6.14.6 EasyDMA

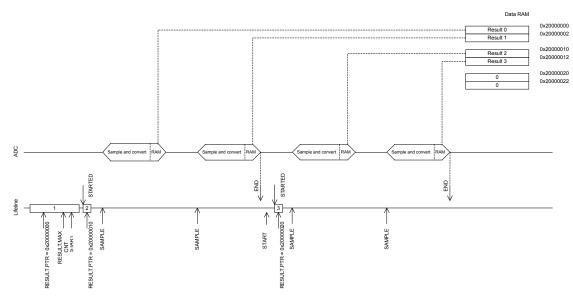

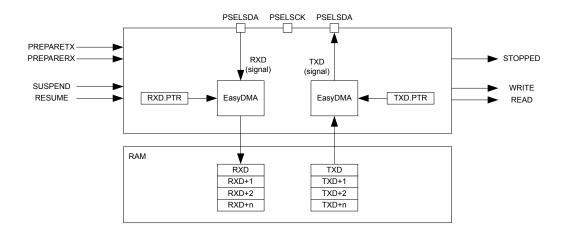

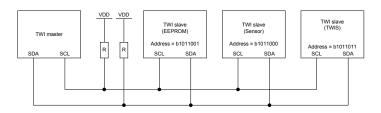

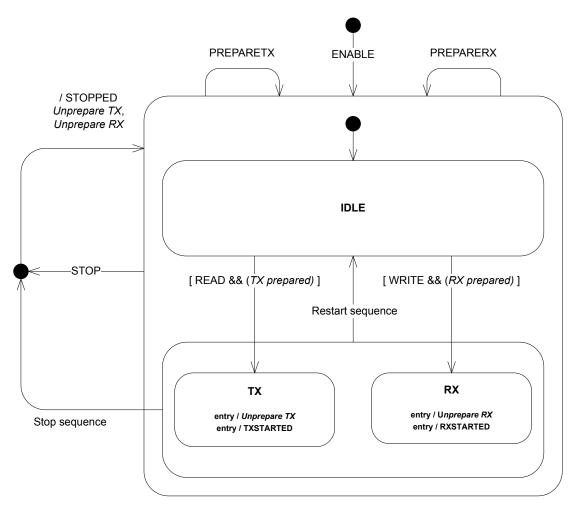

After configuring RESULT.PTR and RESULT.MAXCNT, the ADC resources are started by triggering the START task. The ADC is using EasyDMA to store results in a Result buffer in RAM.

The Result buffer is located at the address specified in the RESULT.PTR register. The RESULT.PTR register is double-buffered and it can be updated and prepared for the next START task immediately after the STARTED event is generated. The size of the Result buffer is specified in the RESULT.MAXCNT register and the ADC will generate an END event when it has filled up the Result buffer, see ADC on page 200. Results are stored in little-endian byte order in Data RAM. Every sample will be sign extended to 16 bit before stored in the Result buffer.

The ADC is stopped by triggering the STOP task. The STOP task will terminate an ongoing sampling. The ADC will generate a STOPPED event when it has stopped. If the ADC is already stopped when the STOP task is triggered, the STOPPED event will still be generated.

Figure 65: ADC

If the RESULT.PTR is not pointing to the Data RAM region, an EasyDMA transfer may result in a HardFault or RAM corruption. See Memory on page 20 for more information about the different memory regions.

The EasyDMA will have finished accessing the RAM when the END or STOPPED event has been generated.

The RESULT.AMOUNT register can be read following an END event or a STOPPED event to see how many results have been transferred to the Result buffer in RAM since the START task was triggered.

In scan mode, SAMPLE tasks can be triggered once the START task is triggered. The END event is generated when the number of samples transferred to memory reaches the value specified by RESULT.MAXCNT. After an END event, the START task needs to be triggered again before new samples can be taken. Also make sure that the size of the Result buffer is large enough to have space for minimum one result from each of the enabled channels, by specifying RESULT.MAXCNT >= number of channels enabled. For more information about the scan mode, see Scan mode on page 198.

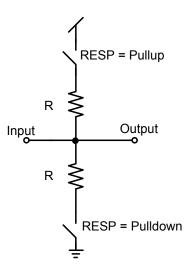

# 6.14.7 Resistor ladder

The ADC has an internal resistor string for positive and negative input.

See Resistor ladder for positive input (negative input is equivalent, using RESN instead of RESP) on page 201. The resistors are controlled in the CH[n].CONFIG.RESP and CH[n].CONFIG.RESN registers.

*Figure 66: Resistor ladder for positive input (negative input is equivalent, using RESN instead of RESP)*

# 6.14.8 Reference

The ADC can use two different references, controlled in the REFSEL field of the CH[n].CONFIG register.

These are:

- Internal reference

- VDD as reference

The internal reference results in an input range of  $\pm 0.6$  V on the ADC core. VDD as reference results in an input range of  $\pm$ VDD/4 on the ADC core. The gain block can be used to change the effective input range of the ADC.

Input range = (+- 0.6 V or +-VDD/4)/Gain

For example, choosing VDD as reference, single ended input (grounded negative input), and a gain of 1/4 the input range will be:

Input range = (VDD/4)/(1/4) = VDD

With internal reference, single ended input (grounded negative input), and a gain of 1/6 the input range will be:

Input range = (0.6 V) / (1/6) = 3.6 V

The AINO-AIN7 inputs cannot exceed VDD, or be lower than VSS.

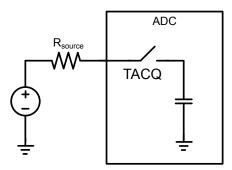

# 6.14.9 Acquisition time

To sample the input voltage, the ADC connects a capacitor to the input.

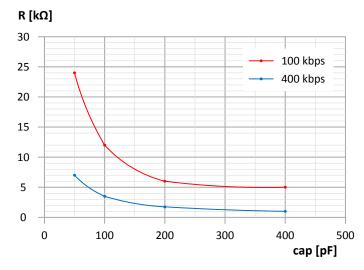

For illustration, see Simplified ADC sample network on page 202. The acquisition time indicates how long the capacitor is connected, see TACQ field in CH[n].CONFIG register. The required acquisition time depends on the source (R<sub>source</sub>) resistance. For high source resistance the acquisition time should be increased, see Acquisition time on page 202.

Figure 67: Simplified ADC sample network

| TACQ [µs] | Maximum source resistance [kOhm] |

|-----------|----------------------------------|

| 3         | 10                               |

| 5         | 40                               |

| 10        | 100                              |

| 15        | 200                              |

| 20        | 400                              |

| 40        | 800                              |

Table 64: Acquisition time

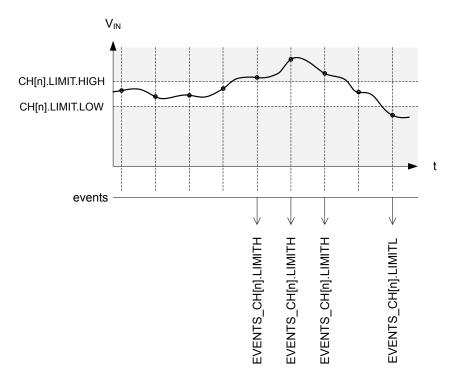

# 6.14.10 Limits event monitoring

A channel can be event monitored by configuring limit register CH[n].LIMIT.

If the conversion result is higher than the defined high limit, or lower than the defined low limit, the appropriate event will get fired.

Figure 68: Example of limits monitoring on channel 'n'

Note that when setting the limits, CH[n].LIMIT.HIGH shall always be higher than or equal to CH[n].LIMIT.LOW . In other words, an event can be fired only when the input signal has been sampled outside of the defined limits. It is not possible to fire an event when the input signal is inside a defined range by swapping high and low limits.

The comparison to limits always takes place, there is no need to enable it. If comparison is not required on a channel, the software shall simply ignore the related events. In that situation, the value of the limits registers is irrelevant, so it does not matter if CH[n].LIMIT.LOW is lower than CH[n].LIMIT.HIGH or not.

# 6.14.11 Registers

| Base address Periphera   | l Instance              | Secure mapping | DMA security           | Description              | Configuration                |

|--------------------------|-------------------------|----------------|------------------------|--------------------------|------------------------------|

| 0x5000E000<br>0x4000E000 | SAADC : S<br>SAADC : NS | US             | SA                     | Analog to digital co     | onverter                     |

|                          |                         |                | Table 65: Ins          | tances                   |                              |

|                          |                         |                |                        |                          |                              |

| Register                 | Offset Se               | curity D       | escription             |                          |                              |

| TASKS_START              | 0x000                   |                |                        | pare the result buffer   | in RAM                       |

| TASKS_SAMPLE             | 0x004                   | Та             | ake one ADC sample     | , if scan is enabled all | channels are sampled         |

| TASKS_STOP               | 0x008                   |                |                        | minate any on-going c    |                              |

| TASKS_CALIBRATEOFFSET    | 0x00C                   | St             | tarts offset auto-cali | bration                  |                              |

| SUBSCRIBE_START          | 0x080                   | S              | ubscribe configuration | on for task START        |                              |

| SUBSCRIBE_SAMPLE         | 0x084                   | S              | ubscribe configuration | on for task SAMPLE       |                              |

| SUBSCRIBE_STOP           | 0x088                   | S              | ubscribe configuration | on for task STOP         |                              |

| SUBSCRIBE_CALIBRATEOF    | F: 0x08C                | S              | ubscribe configuration | on for task CALIBRATE    | DFFSET                       |

| EVENTS_STARTED           | 0x100                   | T              | he ADC has started     |                          |                              |

| EVENTS_END               | 0x104                   | Т              | he ADC has filled up   | the Result buffer        |                              |

| EVENTS_DONE              | 0x108                   | A              | conversion task has    | been completed. Dep      | ending on the mode, multiple |

|                          |                         | co             | onversions might be    | needed for a result to   | be transferred to RAM.       |

| EVENTS_RESULTDONE        | 0x10C                   | A              | result is ready to ge  | t transferred to RAM.    |                              |

| EVENTS_CALIBRATEDONE     | 0x110                   | с              | alibration is complet  | te                       |                              |

| EVENTS_STOPPED           | 0x114                   | T              | he ADC has stopped     |                          |                              |

| EVENTS_CH[0].LIMITH      | 0x118                   | Li             | ast results is equal o | r above CH[0].LIMIT.H    | IGH                          |

| EVENTS_CH[0].LIMITL      | 0x11C                   | La             | ast results is equal o | r below CH[0].LIMIT.LC   | w                            |

| EVENTS_CH[1].LIMITH      | 0x120                   | Li             | ast results is equal o | r above CH[1].LIMIT.H    | IGH                          |

| EVENTS_CH[1].LIMITL      | 0x124                   | La             | ast results is equal o | r below CH[1].LIMIT.LC   | w                            |

| EVENTS_CH[2].LIMITH      | 0x128                   | La             | ast results is equal o | r above CH[2].LIMIT.H    | IGH                          |

| EVENTS_CH[2].LIMITL      | 0x12C                   | La             | ast results is equal o | r below CH[2].LIMIT.LC   | w                            |

| EVENTS_CH[3].LIMITH      | 0x130                   | La             | ast results is equal o | r above CH[3].LIMIT.H    | IGH                          |

| EVENTS_CH[3].LIMITL      | 0x134                   | La             | ast results is equal o | r below CH[3].LIMIT.LC   | w                            |

| EVENTS_CH[4].LIMITH      | 0x138                   | La             | ast results is equal o | r above CH[4].LIMIT.H    | IGH                          |

| EVENTS_CH[4].LIMITL      | 0x13C                   | Li             | ast results is equal o | r below CH[4].LIMIT.LC   | ow.                          |

| EVENTS_CH[5].LIMITH      | 0x140                   | Li             | ast results is equal o | r above CH[5].LIMIT.H    | IGH                          |

| EVENTS_CH[5].LIMITL      | 0x144                   | Li             | ast results is equal o | r below CH[5].LIMIT.LC   | ow.                          |

| EVENTS_CH[6].LIMITH      | 0x148                   | Li             | ast results is equal o | r above CH[6].LIMIT.H    | IGH                          |

| EVENTS_CH[6].LIMITL      | 0x14C                   | Li             | ast results is equal o | r below CH[6].LIMIT.LC   | 9W                           |

| EVENTS_CH[7].LIMITH      | 0x150                   | La             | ast results is equal o | r above CH[7].LIMIT.H    | IGH                          |

| EVENTS_CH[7].LIMITL      | 0x154                   | La             | ast results is equal o | r below CH[7].LIMIT.LC   | W                            |

| PUBLISH_STARTED          | 0x180                   | Р              | ublish configuration   | for event STARTED        |                              |

| PUBLISH_END              | 0x184                   | Р              | ublish configuration   | for event END            |                              |

| PUBLISH_DONE             | 0x188                   | Р              | ublish configuration   | for event DONE           |                              |

| PUBLISH_RESULTDONE       | 0x18C                   | Р              | ublish configuration   | for event RESULTDON      | E                            |

| PUBLISH_CALIBRATEDON     | E 0x190                 | P              | ublish configuration   | for event CALIBRATED     | ONE                          |

| Register             | Offset         | Security | Description                                    |

|----------------------|----------------|----------|------------------------------------------------|

| PUBLISH_STOPPED      | 0x194          |          | Publish configuration for event STOPPED        |

| PUBLISH_CH[0].LIMITH | 0x198          |          | Publish configuration for event CH[0].LIMITH   |

| PUBLISH_CH[0].LIMITL | 0x19C          |          | Publish configuration for event CH[0].LIMITL   |

| PUBLISH_CH[1].LIMITH | 0x1A0          |          | Publish configuration for event CH[1].LIMITH   |

| PUBLISH_CH[1].LIMITL | 0x1A4          |          | Publish configuration for event CH[1].LIMITL   |

| PUBLISH_CH[2].LIMITH | 0x1A8          |          | Publish configuration for event CH[2].LIMITH   |

| PUBLISH_CH[2].LIMITL | 0x1AC          |          | Publish configuration for event CH[2].LIMITL   |

| PUBLISH_CH[3].LIMITH | 0x1B0          |          | Publish configuration for event CH[3].LIMITH   |

| PUBLISH_CH[3].LIMITL | 0x1B4          |          | Publish configuration for event CH[3].LIMITL   |

| PUBLISH_CH[4].LIMITH | 0x1B8          |          | Publish configuration for event CH[4].LIMITH   |

| PUBLISH_CH[4].LIMITL | 0x1BC          |          | Publish configuration for event CH[4].LIMITL   |

| PUBLISH CH[5].LIMITH | 0x1C0          |          | Publish configuration for event CH[5].LIMITH   |

| PUBLISH_CH[5].LIMITL | 0x1C4          |          | Publish configuration for event CH[5].LIMITL   |

| PUBLISH_CH[6].LIMITH | 0x1C8          |          | Publish configuration for event CH[6].LIMITH   |

| PUBLISH_CH[6].LIMITL | 0x1CC          |          | Publish configuration for event CH[6].LIMITL   |

| PUBLISH_CH[7].LIMITH | 0x1D0          |          | Publish configuration for event CH[7].LIMITH   |

| PUBLISH_CH[7].LIMITL | 0x1D4          |          | Publish configuration for event CH[7].LIMITL   |

| INTEN                | 0x1D4          |          | Enable or disable interrupt                    |

| INTENSET             | 0x300          |          | Enable interrupt                               |

|                      | 0x304<br>0x308 |          |                                                |

| INTENCLR             |                |          | Disable interrupt                              |

| STATUS               | 0x400          |          | Status                                         |

| ENABLE               | 0x500          |          | Enable or disable ADC                          |

| CH[0].PSELP          | 0x510          |          | Input positive pin selection for CH[0]         |

| CH[0].PSELN          | 0x514          |          | Input negative pin selection for CH[0]         |

| CH[0].CONFIG         | 0x518          |          | Input configuration for CH[0]                  |

| CH[0].LIMIT          | 0x51C          |          | High/low limits for event monitoring a channel |

| CH[1].PSELP          | 0x520          |          | Input positive pin selection for CH[1]         |

| CH[1].PSELN          | 0x524          |          | Input negative pin selection for CH[1]         |

| CH[1].CONFIG         | 0x528          |          | Input configuration for CH[1]                  |

| CH[1].LIMIT          | 0x52C          |          | High/low limits for event monitoring a channel |

| CH[2].PSELP          | 0x530          |          | Input positive pin selection for CH[2]         |

| CH[2].PSELN          | 0x534          |          | Input negative pin selection for CH[2]         |

| CH[2].CONFIG         | 0x538          |          | Input configuration for CH[2]                  |

| CH[2].LIMIT          | 0x53C          |          | High/low limits for event monitoring a channel |

| CH[3].PSELP          | 0x540          |          | Input positive pin selection for CH[3]         |

| CH[3].PSELN          | 0x544          |          | Input negative pin selection for CH[3]         |

| CH[3].CONFIG         | 0x548          |          | Input configuration for CH[3]                  |

| CH[3].LIMIT          | 0x54C          |          | High/low limits for event monitoring a channel |

| CH[4].PSELP          | 0x550          |          | Input positive pin selection for CH[4]         |

| CH[4].PSELN          | 0x554          |          | Input negative pin selection for CH[4]         |

| CH[4].CONFIG         | 0x558          |          | Input configuration for CH[4]                  |

| CH[4].LIMIT          | 0x55C          |          | High/low limits for event monitoring a channel |

| CH[5].PSELP          | 0x560          |          | Input positive pin selection for CH[5]         |

| CH[5].PSELN          | 0x564          |          | Input negative pin selection for CH[5]         |

| CH[5].CONFIG         | 0x568          |          | Input configuration for CH[5]                  |

| CH[5].LIMIT          | 0x56C          |          | High/low limits for event monitoring a channel |

| CH[6].PSELP          | 0x570          |          | Input positive pin selection for CH[6]         |

| CH[6].PSELN          | 0x574          |          | Input negative pin selection for CH[6]         |

| CH[6].CONFIG         | 0x578          |          | Input configuration for CH[6]                  |

| CH[6].LIMIT          | 0x57C          |          | High/low limits for event monitoring a channel |

| CH[7].PSELP          | 0x580          |          | Input positive pin selection for CH[7]         |

| CH[7].PSELN          | 0x584          |          | Input negative pin selection for CH[7]         |

|                      |                |          |                                                |

| Register      | Offset | Security | Description                                                                   |

|---------------|--------|----------|-------------------------------------------------------------------------------|

| CH[7].LIMIT   | 0x58C  |          | High/low limits for event monitoring a channel                                |

| RESOLUTION    | 0x5F0  |          | Resolution configuration                                                      |

| OVERSAMPLE    | 0x5F4  |          | Oversampling configuration. OVERSAMPLE should not be combined with SCAN.      |

|               |        |          | The RESOLUTION is applied before averaging, thus for high OVERSAMPLE a higher |

|               |        |          | RESOLUTION should be used.                                                    |

| SAMPLERATE    | 0x5F8  |          | Controls normal or continuous sample rate                                     |

| RESULT.PTR    | 0x62C  |          | Data pointer                                                                  |

| RESULT.MAXCNT | 0x630  |          | Maximum number of buffer words to transfer                                    |

| RESULT.AMOUNT | 0x634  |          | Number of buffer words transferred since last START                           |

Table 66: Register overview

## 6.14.11.1 TASKS\_START

Address offset: 0x000

Start the ADC and prepare the result buffer in RAM

| Bit n | umber         |         | 31 30 29 28 27 26 | 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|---------------|---------|-------------------|---------------------------------------------------------------------|

| ID    |               |         |                   | А                                                                   |

| Rese  | et 0x0000000  |         | 0 0 0 0 0         | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                             |

| ID    |               |         |                   | Description                                                         |

| А     | W TASKS_START |         |                   | Start the ADC and prepare the result buffer in RAM                  |

|       |               | Trigger | 1                 | Trigger task                                                        |

## 6.14.11.2 TASKS\_SAMPLE

Address offset: 0x004

Take one ADC sample, if scan is enabled all channels are sampled

| Bit number       |         | 31 30 29 28 27 2 | 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------------------|---------|------------------|------------------------------------------------------------------------|

| ID               |         |                  | А                                                                      |

| Reset 0x0000000  |         | 0 0 0 0 0        | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                |

| ID Acce Field    |         |                  | Description                                                            |

| A W TASKS_SAMPLE |         |                  | Take one ADC sample, if scan is enabled all channels are               |

|                  |         |                  | sampled                                                                |

|                  | Trigger | 1                | Trigger task                                                           |

# 6.14.11.3 TASKS\_STOP

Address offset: 0x008

Stop the ADC and terminate any on-going conversion

| Bit n | umber        |         | 31 30 29 28 27 26 | 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|--------------|---------|-------------------|---------------------------------------------------------------------|

| ID    |              |         |                   | А                                                                   |

| Rese  | et 0x0000000 |         | 0 0 0 0 0 0       | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                             |

| ID    |              |         |                   | Description                                                         |

| А     | W TASKS_STOP |         |                   | Stop the ADC and terminate any on-going conversion                  |

|       |              | Trigger | 1                 | Trigger task                                                        |

# 6.14.11.4 TASKS\_CALIBRATEOFFSET

Address offset: 0x00C

### Starts offset auto-calibration

| Bit n | um                        | ıber     |         | 31 30 29 28 27 26 25 | 24 | 23   | 22  | 21   | 20  | 19   | 1   | 8 1  | 71   | .6 1 | .5 : | 14 3 | 13 | 12 : | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------------------------|----------|---------|----------------------|----|------|-----|------|-----|------|-----|------|------|------|------|------|----|------|----|----|---|---|---|---|---|---|---|---|---|---|

| ID    |                           |          |         |                      |    |      |     |      |     |      |     |      |      |      |      |      |    |      |    |    |   |   |   |   |   |   |   |   |   | А |

| Rese  | et O                      | x0000000 |         | 0 0 0 0 0 0          | 0  | 0    | 0   | 0    | 0   | 0    | 0   | 0    | ) (  | 0 (  | D    | 0    | 0  | 0    | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ID    |                           |          |         |                      |    |      |     |      |     |      |     |      |      |      |      |      |    |      |    |    |   |   |   |   |   |   |   |   |   |   |

| А     | A W TASKS_CALIBRATEOFFSET |          |         |                      |    | Sta  | rts | off  | set | t ai | uto | )-Ca | alib | orat | ioi  | ı    |    |      |    |    |   |   |   |   |   |   |   |   |   |   |

|       |                           |          | Trigger | 1                    |    | Trig | ge  | r ta | ask |      |     |      |      |      |      |      |    |      |    |    |   |   |   |   |   |   |   |   |   |   |

# 6.14.11.5 SUBSCRIBE\_START

Address offset: 0x080

Subscribe configuration for task START

| Bit n  | umber             |          | 31 30 29 28 27 26 25 2 | 4 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0   |

|--------|-------------------|----------|------------------------|-------------------------------------------------------------------|

| ID     |                   |          | В                      | A A A A                                                           |

| Rese   | t 0x0000000       |          | 0 0 0 0 0 0 0          | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                           |

| ID     |                   |          |                        | Description                                                       |

|        |                   |          |                        |                                                                   |

| А      | RW CHIDX          |          | [150]                  | Channel that task START will subscribe to                         |

| A<br>B | RW CHIDX<br>RW EN |          | [150]                  | Channel that task START will subscribe to                         |

|        |                   | Disabled | [150]<br>0             | Channel that task START will subscribe to<br>Disable subscription |

# 6.14.11.6 SUBSCRIBE\_SAMPLE

Address offset: 0x084

Subscribe configuration for task SAMPLE

| Bit n | umber       |          | 31 30 29 28 27 26 25 24 | 4 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|-------------|----------|-------------------------|-----------------------------------------------------------------|

| ID    |             |          | В                       | АААА                                                            |

| Rese  | t 0x0000000 |          | 0 0 0 0 0 0 0           | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                         |

| ID    |             |          |                         |                                                                 |

| А     | RW CHIDX    |          | [150]                   | Channel that task SAMPLE will subscribe to                      |

| В     | RW EN       |          |                         |                                                                 |

|       |             | Disabled | 0                       | Disable subscription                                            |

|       |             | Enabled  | 1                       | Enable subscription                                             |

# 6.14.11.7 SUBSCRIBE\_STOP

Address offset: 0x088

Subscribe configuration for task STOP

| Bit n | umber        |          | 31 30 29 28 27 26 25 24 | 4 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|--------------|----------|-------------------------|-----------------------------------------------------------------|

| ID    |              |          | В                       | АААА                                                            |

| Rese  | et 0x0000000 |          | 0 0 0 0 0 0 0           | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                         |

| ID    |              |          |                         | Description                                                     |

| A     | RW CHIDX     |          | [150]                   | Channel that task STOP will subscribe to                        |

| В     | RW EN        |          |                         |                                                                 |

|       |              | Disabled | 0                       | Disable subscription                                            |

|       |              | Enabled  | 1                       | Enable subscription                                             |

# 6.14.11.8 SUBSCRIBE\_CALIBRATEOFFSET

### Address offset: 0x08C

### Subscribe configuration for task CALIBRATEOFFSET

| Bit number             | 31 30 29 28 27 26 | 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------------------------|-------------------|---------------------------------------------------------------------|

| ID                     | В                 | АААА                                                                |

| Reset 0x00000000       | 0 0 0 0 0 0       | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                             |

| ID Acce Field Value ID |                   |                                                                     |

| A RW CHIDX             | [150]             | Channel that task CALIBRATEOFFSET will subscribe to                 |

| B RW EN                |                   |                                                                     |

| Disabled               | 0                 | Disable subscription                                                |

| Enabled                | 1                 | Enable subscription                                                 |

# 6.14.11.9 EVENTS\_STARTED

Address offset: 0x100

The ADC has started

| Bit number          |              | 31 30 29 28 27 26 25 | 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|---------------------|--------------|----------------------|------------------------------------------------------------------|

| ID                  |              |                      | A                                                                |

| Reset 0x0000000     |              | 0 0 0 0 0 0 0        | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                          |

| ID Acce Field       |              |                      |                                                                  |

| A RW EVENTS_STARTED |              |                      | The ADC has started                                              |

|                     | NotGenerated | 0                    | Event not generated                                              |

|                     | Generated    | 1                    | Event generated                                                  |

# 6.14.11.10 EVENTS\_END

Address offset: 0x104

The ADC has filled up the Result buffer

| Bit number      |              | 31 30 29 28 27 26 | 2 5 2 4 2 3 2 2 2 1 2 0 1 9 1 8 1 7 1 6 1 5 1 4 1 3 1 2 1 1 1 0 9 8 7 6 5 4 3 2 1 0 |

|-----------------|--------------|-------------------|-------------------------------------------------------------------------------------|

| ID              |              |                   | А                                                                                   |

| Reset 0x0000000 |              | 0 0 0 0 0 0       | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                             |

| ID Acce Field   |              |                   | Description                                                                         |

| A RW EVENTS_END |              |                   | The ADC has filled up the Result buffer                                             |

|                 | NotGenerated | 0                 | Event not generated                                                                 |

|                 | Generated    | 1                 | Event generated                                                                     |

# 6.14.11.11 EVENTS\_DONE

Address offset: 0x108

A conversion task has been completed. Depending on the mode, multiple conversions might be needed for a result to be transferred to RAM.

| Bit n | umber          |              | 31 30 29 28 27 26 | 2 5 2 4 2 3 2 2 2 1 2 0 1 9 1 8 1 7 1 6 1 5 1 4 1 3 1 2 1 1 1 0 9 8 7 6 5 4 3 2 1 0 |

|-------|----------------|--------------|-------------------|-------------------------------------------------------------------------------------|

| ID    |                |              |                   | А                                                                                   |

| Rese  | et 0x0000000   |              | 0 0 0 0 0 0       | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                             |

| ID    |                |              |                   | Description                                                                         |

| А     | RW EVENTS_DONE |              |                   | A conversion task has been completed. Depending on the                              |

|       |                |              |                   | mode, multiple conversions might be needed for a result to                          |

|       |                |              |                   | be transferred to RAM.                                                              |

|       |                | NotGenerated | 0                 | Event not generated                                                                 |

|       |                | Generated    | 1                 | Event generated                                                                     |

## 6.14.11.12 EVENTS\_RESULTDONE

Address offset: 0x10C

A result is ready to get transferred to RAM.

| Bit n | umber                |              | 31 30 29 28 27 26 25 24 | 4 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|----------------------|--------------|-------------------------|-----------------------------------------------------------------|

| ID    |                      |              |                         | А                                                               |

| Rese  | t 0x0000000          |              | 0 0 0 0 0 0 0 0         | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                         |

| ID    |                      |              |                         | Description                                                     |

| А     | RW EVENTS_RESULTDONE |              |                         | A result is ready to get transferred to RAM.                    |

|       |                      | NotGenerated | 0                       | Event not generated                                             |

|       |                      | Generated    | 1                       | Event generated                                                 |

## 6.14.11.13 EVENTS\_CALIBRATEDONE

Address offset: 0x110

Calibration is complete

| Bit n | umber                 |              | 313 | 0 2 | 9 28 | 27 | 26 | 25 | 24 | 23  | 22    | 212  | 01   | 9 18 | 3 17 | 16  | 5 15 | 14 | 13 | 12 | 11 1 | 0.9 | 8 ( | 7 | 6 | 5 | 4 | 3   | 2 1        | 0 |

|-------|-----------------------|--------------|-----|-----|------|----|----|----|----|-----|-------|------|------|------|------|-----|------|----|----|----|------|-----|-----|---|---|---|---|-----|------------|---|

| ID    |                       |              |     |     |      |    |    |    |    |     |       |      |      |      |      |     |      |    |    |    |      |     |     |   |   |   |   |     |            | А |

| Rese  | t 0x0000000           |              | 0 ( | 0 0 | 0 0  | 0  | 0  | 0  | 0  | 0   | 0     | 0    | ) (  | ) 0  | 0    | 0   | 0    | 0  | 0  | 0  | 0    | 0 ( | ) 0 | 0 | 0 | 0 | 0 | 0 ( | <b>)</b> ( | 0 |

| ID    |                       |              |     |     |      |    |    |    |    | De  |       |      |      |      |      |     |      |    |    |    |      |     |     |   |   |   |   |     |            |   |

| А     | RW EVENTS_CALIBRATEDO | νE           |     |     |      |    |    |    |    | Cal | libra | atio | n is | con  | nple | ete |      |    |    |    |      |     |     |   |   |   |   |     |            |   |

|       |                       | NotGenerated | 0   |     |      |    |    |    |    | Eve | ent   | not  | gen  | era  | ted  |     |      |    |    |    |      |     |     |   |   |   |   |     |            |   |

|       |                       | Generated    | 1   |     |      |    |    |    |    | Eve | ent   | gen  | erat | ed   |      |     |      |    |    |    |      |     |     |   |   |   |   |     |            |   |

# 6.14.11.14 EVENTS\_STOPPED

Address offset: 0x114

The ADC has stopped

| Bit n | umber             |              | 31 30 29 28 27 26 2 | 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|-------------------|--------------|---------------------|---------------------------------------------------------------------|

| ID    |                   |              |                     | A                                                                   |

| Rese  | t 0x0000000       |              | 0 0 0 0 0 0         | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                             |

| ID    |                   |              |                     |                                                                     |

| A     | RW EVENTS_STOPPED |              |                     | The ADC has stopped                                                 |

|       |                   | NotGenerated | 0                   | Event not generated                                                 |

|       |                   | Generated    | 1                   | Event generated                                                     |

# 6.14.11.15 EVENTS\_CH[n].LIMITH (n=0..7)

Address offset: 0x118 + (n × 0x8)

### Last results is equal or above CH[n].LIMIT.HIGH

| Bit number      |              | 31 30 29 28 27 2 | 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-----------------|--------------|------------------|------------------------------------------------------------------------|

| ID              |              |                  | А                                                                      |

| Reset 0x0000000 |              | 0 0 0 0 0        | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                |

| ID Acce Field   |              |                  | Description                                                            |

| A RW LIMITH     |              |                  | Last results is equal or above CH[n].LIMIT.HIGH                        |

|                 | NotGenerated | 0                | Event not generated                                                    |

|                 | Generated    | 1                | Event generated                                                        |

# 6.14.11.16 EVENTS\_CH[n].LIMITL (n=0..7)

Address offset: 0x11C + (n × 0x8)

Last results is equal or below CH[n].LIMIT.LOW

| Bit num | ber      |              | 31 30 | 29 28 : | 27 26 | 25 2 | 4 23 | 22    | 21 2  | 0 19   | 18   | 17 1  | 16 15 | 5 14 | 13   | 12 1   | 1 10  | 9   | 8 | 7 | 6 | 54  | 3 | 2 | 1 0 |

|---------|----------|--------------|-------|---------|-------|------|------|-------|-------|--------|------|-------|-------|------|------|--------|-------|-----|---|---|---|-----|---|---|-----|

| ID      |          |              |       |         |       |      |      |       |       |        |      |       |       |      |      |        |       |     |   |   |   |     |   |   | А   |

| Reset 0 | x0000000 |              | 0 0   | 0 0     | 0 0   | 0 0  | 0 0  | 0     | 0 0   | 0      | 0    | 0     | 0 0   | 0    | 0    | 0 0    | 0     | 0   | 0 | 0 | 0 | D C | 0 | 0 | 0 0 |

| ID A    |          |              |       |         |       |      |      |       |       |        |      |       |       |      |      |        |       |     |   |   |   |     |   |   |     |

| A R     | W LIMITL |              |       |         |       |      | La   | st re | esult | s is e | qua  | al or | bel   | ow   | CH[I | n].LII | VIT.I | .00 | / |   |   |     |   |   |     |

|         |          | NotGenerated | 0     |         |       |      | Ev   | ent   | not ( | gene   | rate | ed    |       |      |      |        |       |     |   |   |   |     |   |   |     |

|         |          | Generated    | 1     |         |       |      | Ev   | ent   | gene  | erate  | d    |       |       |      |      |        |       |     |   |   |   |     |   |   |     |

## 6.14.11.17 PUBLISH\_STARTED

Address offset: 0x180

Publish configuration for event STARTED

| Bit n | umber       |          | 31 30 29 28 27 26 2 | 5 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|-------------|----------|---------------------|--------------------------------------------------------------------|

| ID    |             |          | В                   | A A A A                                                            |

| Rese  | t 0x0000000 |          | 0 0 0 0 0 0         | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                            |

| ID    |             |          |                     |                                                                    |

| А     | RW CHIDX    |          | [150]               | Channel that event STARTED will publish to.                        |

| В     | RW EN       |          |                     |                                                                    |

|       |             | Disabled | 0                   | Disable publishing                                                 |

|       |             | Enabled  | 1                   | Enable publishing                                                  |

## 6.14.11.18 PUBLISH\_END

Address offset: 0x184

Publish configuration for event END

| Bit n | umber       |          | 31 30 29 28 27 26 25 | 2 4 2 3 2 2 1 2 0 1 9 1 8 1 7 1 6 1 5 1 4 1 3 1 2 1 1 1 0 9 8 7 6 5 4 3 2 1 0 |

|-------|-------------|----------|----------------------|-------------------------------------------------------------------------------|

| ID    |             |          | В                    | АААА                                                                          |

| Rese  | t 0x0000000 |          | 0 0 0 0 0 0 0        | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                       |

| ID    |             |          |                      |                                                                               |

| А     | RW CHIDX    |          | [150]                | Channel that event END will publish to.                                       |

| В     | RW EN       |          |                      |                                                                               |

|       |             | Disabled | 0                    | Disable publishing                                                            |

|       |             | Enabled  | 1                    | Enable publishing                                                             |

# 6.14.11.19 PUBLISH\_DONE

Address offset: 0x188

Publish configuration for event DONE

| Bit n | umber       |          | 31 30 29 28 27 26 2 | 5 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|-------------|----------|---------------------|--------------------------------------------------------------------|

| ID    |             |          | В                   | A A A A                                                            |

| Rese  | t 0x0000000 |          | 0 0 0 0 0 0         | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                            |

| ID    |             |          |                     |                                                                    |

| А     | RW CHIDX    |          | [150]               | Channel that event DONE will publish to.                           |

| В     | RW EN       |          |                     |                                                                    |

|       |             | Disabled | 0                   | Disable publishing                                                 |

|       |             | Enabled  | 1                   | Enable publishing                                                  |

## 6.14.11.20 PUBLISH\_RESULTDONE

### Address offset: 0x18C

Publish configuration for event **RESULTDONE**

| Bit n | umber       |          | 31 30 29 28 27 26 | 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|-------------|----------|-------------------|---------------------------------------------------------------------|

| ID    |             |          | В                 | АААА                                                                |

| Rese  | t 0x0000000 |          | 0 0 0 0 0 0       | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                             |

| ID    |             |          |                   |                                                                     |

| А     | RW CHIDX    |          | [150]             | Channel that event RESULTDONE will publish to.                      |

| В     | RW EN       |          |                   |                                                                     |

|       |             | Disabled | 0                 | Disable publishing                                                  |

|       |             | Enabled  | 1                 | Enable publishing                                                   |

# 6.14.11.21 PUBLISH\_CALIBRATEDONE

Address offset: 0x190

Publish configuration for event CALIBRATEDONE

| Bit n | umber       |          | 31 30 29 28 27 26 25 24 | 4 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|-------------|----------|-------------------------|-----------------------------------------------------------------|

| ID    |             |          | В                       | A A A A                                                         |

| Rese  | t 0x0000000 |          | 0 0 0 0 0 0 0 0         | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                         |

| ID    |             |          |                         | Description                                                     |

| А     | RW CHIDX    |          | [150]                   | Channel that event CALIBRATEDONE will publish to.               |

| В     | RW EN       |          |                         |                                                                 |

|       |             | Disabled | 0                       | Disable publishing                                              |

|       |             | Enabled  | 1                       | Enable publishing                                               |

### 6.14.11.22 PUBLISH\_STOPPED

Address offset: 0x194

Publish configuration for event STOPPED

| Bit n | umber       |          | 31 30 29 28 27 26 | 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |

|-------|-------------|----------|-------------------|-------------------------------------------------------------------|

| ID    |             |          | В                 | A A A                                                             |

| Rese  | t 0x0000000 |          | 0 0 0 0 0 0       | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                           |

|       |             |          |                   |                                                                   |

| А     | RW CHIDX    |          | [150]             | Channel that event STOPPED will publish to.                       |

| В     | RW EN       |          |                   |                                                                   |

|       |             | Disabled | 0                 | Disable publishing                                                |

|       |             | Enabled  | 1                 | Enable publishing                                                 |

# 6.14.11.23 PUBLISH\_CH[n].LIMITH (n=0..7)

Address offset: 0x198 + (n × 0x8)

Publish configuration for event CH[n].LIMITH

| Bit number      |          | 31 30 29 28 27 26 | 5 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-----------------|----------|-------------------|-----------------------------------------------------------------------|

| ID              |          | В                 | АААА                                                                  |

| Reset 0x0000000 |          | 0 0 0 0 0 0       | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                               |

| ID Acce Field   |          |                   |                                                                       |

| A RW CHIDX      |          | [150]             | Channel that event CH[n].LIMITH will publish to.                      |

| B RW EN         |          |                   |                                                                       |

|                 | Disabled | 0                 | Disable publishing                                                    |

|                 | Enabled  | 1                 | Enable publishing                                                     |

## 6.14.11.24 PUBLISH\_CH[n].LIMITL (n=0..7)

Address offset: 0x19C + (n × 0x8)

Publish configuration for event CH[n].LIMITL

| Bit n | umber       |          | 31 30 29 28 27 26 25 24 | 4 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|-------------|----------|-------------------------|-----------------------------------------------------------------|

| ID    |             |          | В                       | АААА                                                            |

| Rese  | t 0x0000000 |          | 0 0 0 0 0 0 0 0         | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                         |

| ID    |             |          |                         |                                                                 |

| А     | RW CHIDX    |          | [150]                   | Channel that event CH[n].LIMITL will publish to.                |

| В     | RW EN       |          |                         |                                                                 |

|       |             | Disabled | 0                       | Disable publishing                                              |

|       |             | Enabled  | 1                       | Enable publishing                                               |

### 6.14.11.25 INTEN

Address offset: 0x300

Enable or disable interrupt

| Bit number      |          | 31 30 29 28 27 26 25 2 | 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-----------------|----------|------------------------|------------------------------------------------------------------|

| ID              |          |                        | VUTSRQPONMLKJIHGFEDCBA                                           |

| Reset 0x0000000 |          | 0 0 0 0 0 0 0          | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                          |

| ID Acce Field   |          |                        | Description                                                      |

| A RW STARTED    |          |                        | Enable or disable interrupt for event STARTED                    |

|                 | Disabled | 0                      | Disable                                                          |

|                 | Enabled  | 1                      | Enable                                                           |

| B RW END        |          |                        | Enable or disable interrupt for event END                        |

|                 | Disabled | 0                      | Disable                                                          |

|                 | Enabled  | 1                      | Enable                                                           |

| Bit n | number           |          | 31 30 29 28 2 | 7 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |

|-------|------------------|----------|---------------|------------------------------------------------------------------------|

| ID    |                  |          |               | V U T S R Q P O N M L K J I H G F E D C B .                            |

| Rese  | et 0x0000000     |          | 0 0 0 0 0     |                                                                        |

|       |                  | Value ID |               |                                                                        |

| C     | RW DONE          | Value 15 | Value         | Enable or disable interrupt for event DONE                             |

| C     | NW DONE          | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| D     | RW RESULTDONE    | Lindbled | 1             |                                                                        |

| U     | RW RESULIDONE    |          | 0             | Enable or disable interrupt for event RESULTDONE                       |

|       |                  | Disabled | 0             | Disable                                                                |

| _     |                  | Enabled  | 1             | Enable                                                                 |

| E     | RW CALIBRATEDONE |          |               | Enable or disable interrupt for event CALIBRATEDONE                    |

|       |                  | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| F     | RW STOPPED       |          |               | Enable or disable interrupt for event STOPPED                          |

|       |                  | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| G     | RW CHOLIMITH     |          |               | Enable or disable interrupt for event CHOLIMITH                        |

|       |                  | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| н     | RW CHOLIMITL     |          |               | Enable or disable interrupt for event CHOLIMITL                        |

|       |                  | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| I     | RW CH1LIMITH     |          |               | Enable or disable interrupt for event CH1LIMITH                        |

|       |                  | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| J     | RW CH1LIMITL     | Lindbied | -             | Enable or disable interrupt for event CH1LIMITL                        |

| 5     |                  | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| K.    |                  | Enabled  | T             |                                                                        |

| К     | RW CH2LIMITH     |          | _             | Enable or disable interrupt for event CH2LIMITH                        |

|       |                  | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| L     | RW CH2LIMITL     |          |               | Enable or disable interrupt for event CH2LIMITL                        |

|       |                  | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| М     | RW CH3LIMITH     |          |               | Enable or disable interrupt for event CH3LIMITH                        |

|       |                  | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| N     | RW CH3LIMITL     |          |               | Enable or disable interrupt for event CH3LIMITL                        |

|       |                  | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| 0     | RW CH4LIMITH     |          |               | Enable or disable interrupt for event CH4LIMITH                        |

|       |                  | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| Р     | RW CH4LIMITL     |          |               | Enable or disable interrupt for event CH4LIMITL                        |

|       |                  | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| 0     | RW CH5LIMITH     | LINDUCU  | 1             | Enable or disable interrupt for event CH5LIMITH                        |

| Q     |                  | Disablad | 0             |                                                                        |

|       |                  | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| R     | RW CH5LIMITL     |          |               | Enable or disable interrupt for event CH5LIMITL                        |

|       |                  | Disabled | 0             | Disable                                                                |

|       |                  | Enabled  | 1             | Enable                                                                 |

| S     | RW CH6LIMITH     |          |               | Enable or disable interrupt for event CH6LIMITH                        |

|       |                  |          |               |                                                                        |

|       |              |          |                   |                   |            |           |       |      |   |   |     |   |   | _ |   |

|-------|--------------|----------|-------------------|-------------------|------------|-----------|-------|------|---|---|-----|---|---|---|---|

| Bit r | umber        |          | 31 30 29 28 27 26 | 23 22 21 20 19 18 | 3 17 16 15 | 14 13 12  | 11 10 | 98   | 7 | 6 | 54  | 3 | 2 | 1 | 0 |

| ID    |              |          |                   | VUTS              | RQP        | ΟΝΜ       | LΚ    | JI   | н | G | FΕ  | D | С | В | A |

| Res   | et 0x0000000 |          | 0 0 0 0 0 0       | 0 0 0 0 0 0       | 000        | 0 0 0     | 0 0   | 0 0  | 0 | 0 | 0 0 | 0 | 0 | 0 | 0 |

| ID    |              |          |                   | Description       |            |           |       |      |   |   |     |   |   |   |   |

|       |              | Enabled  | 1                 | Enable            |            |           |       |      |   |   |     |   |   |   |   |

| т     | RW CH6LIMITL |          |                   | Enable or disable | interrupt  | for event | CH6LI | MITL |   |   |     |   |   |   |   |

|       |              | Disabled | 0                 | Disable           |            |           |       |      |   |   |     |   |   |   |   |

|       |              | Enabled  | 1                 | Enable            |            |           |       |      |   |   |     |   |   |   |   |

| U     | RW CH7LIMITH |          |                   | Enable or disable | interrupt  | for event | CH7LI | мітн |   |   |     |   |   |   |   |

|       |              | Disabled | 0                 | Disable           |            |           |       |      |   |   |     |   |   |   |   |

|       |              | Enabled  | 1                 | Enable            |            |           |       |      |   |   |     |   |   |   |   |

| v     | RW CH7LIMITL |          |                   | Enable or disable | interrupt  | for event | CH7LI | MITL |   |   |     |   |   |   |   |

|       |              | Disabled | 0                 | Disable           |            |           |       |      |   |   |     |   |   |   |   |

|       |              | Enabled  | 1                 | Enable            |            |           |       |      |   |   |     |   |   |   |   |

|       |              |          |                   |                   |            |           |       |      |   |   |     |   |   |   |   |

## 6.14.11.26 INTENSET

### Address offset: 0x304

### Enable interrupt

| Bit r | number           |          | 31 30 29 28 27 26 25 24 | 4 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|------------------|----------|-------------------------|-----------------------------------------------------------------|

| ID    |                  |          |                         | V U T S R Q P O N M L K J I H G F E D C B A                     |

| Res   | et 0x00000000    |          | 0 0 0 0 0 0 0 0         |                                                                 |

| ID    |                  |          |                         | Description                                                     |

| А     | RW STARTED       |          |                         | Write '1' to enable interrupt for event STARTED                 |

|       |                  | Set      | 1                       | Enable                                                          |

|       |                  | Disabled | 0                       | Read: Disabled                                                  |

|       |                  | Enabled  | 1                       | Read: Enabled                                                   |

| В     | RW END           |          |                         | Write '1' to enable interrupt for event END                     |

|       |                  | Set      | 1                       | Enable                                                          |

|       |                  | Disabled | 0                       | Read: Disabled                                                  |

|       |                  | Enabled  | 1                       | Read: Enabled                                                   |

| с     | RW DONE          |          |                         | Write '1' to enable interrupt for event DONE                    |

|       |                  | Set      | 1                       | Enable                                                          |

|       |                  | Disabled | 0                       | Read: Disabled                                                  |

|       |                  | Enabled  | 1                       | Read: Enabled                                                   |

| D     | RW RESULTDONE    |          |                         | Write '1' to enable interrupt for event RESULTDONE              |

|       |                  | Set      | 1                       | Enable                                                          |

|       |                  | Disabled | 0                       | Read: Disabled                                                  |

|       |                  | Enabled  | 1                       | Read: Enabled                                                   |

| Е     | RW CALIBRATEDONE |          |                         | Write '1' to enable interrupt for event CALIBRATEDONE           |

|       |                  | Set      | 1                       | Enable                                                          |

|       |                  | Disabled | 0                       | Read: Disabled                                                  |

|       |                  | Enabled  | 1                       | Read: Enabled                                                   |

| F     | RW STOPPED       |          |                         | Write '1' to enable interrupt for event STOPPED                 |

|       |                  | Set      | 1                       | Enable                                                          |

|       |                  | Disabled | 0                       | Read: Disabled                                                  |

|       |                  | Enabled  | 1                       | Read: Enabled                                                   |

| G     | RW CHOLIMITH     |          |                         | Write '1' to enable interrupt for event CHOLIMITH               |

|       |                  | Set      | 1                       | Enable                                                          |

|       |                  | Disabled | 0                       | Read: Disabled                                                  |

|       |                  | Enabled  | 1                       | Read: Enabled                                                   |

| н     | RW CHOLIMITL     |          |                         | Write '1' to enable interrupt for event CHOLIMITL               |

|       |                  |          |                         |                                                                 |

| Bit r    | umber        |          | 31 30 29 28 | 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|----------|--------------|----------|-------------|---------------------------------------------------------------------------|

| ID       |              |          |             | V U T S R Q P O N M L K J I H G F E D C B A                               |

| Res      | et 0x0000000 |          | 0 0 0 0     | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                   |

|          |              |          |             |                                                                           |

|          |              | Set      | 1           | Enable                                                                    |

|          |              | Disabled | 0           | Read: Disabled                                                            |

|          |              | Enabled  | 1           | Read: Enabled                                                             |

| 1        | RW CH1LIMITH |          |             | Write '1' to enable interrupt for event CH1LIMITH                         |

|          |              | Set      | 1           | Enable                                                                    |

|          |              | Disabled | 0           | Read: Disabled                                                            |

|          |              | Enabled  |             | Read: Enabled                                                             |

|          |              | Enabled  | 1           |                                                                           |

| J        | RW CH1LIMITL | C-+      | 1           | Write '1' to enable interrupt for event CH1LIMITL                         |

|          |              | Set      | 1           | Enable                                                                    |

|          |              | Disabled | 0           | Read: Disabled                                                            |

|          |              | Enabled  | 1           | Read: Enabled                                                             |

| К        | RW CH2LIMITH |          |             | Write '1' to enable interrupt for event CH2LIMITH                         |

|          |              | Set      | 1           | Enable                                                                    |

|          |              | Disabled | 0           | Read: Disabled                                                            |

|          |              | Enabled  | 1           | Read: Enabled                                                             |

| L        | RW CH2LIMITL |          |             | Write '1' to enable interrupt for event CH2LIMITL                         |

|          |              | Set      | 1           | Enable                                                                    |

|          |              | Disabled | 0           | Read: Disabled                                                            |

|          |              | Enabled  | 1           | Read: Enabled                                                             |

| М        | RW CH3LIMITH |          |             | Write '1' to enable interrupt for event CH3LIMITH                         |

|          |              | Set      | 1           | Enable                                                                    |

|          |              | Disabled | 0           | Read: Disabled                                                            |

|          |              | Enabled  | 1           | Read: Enabled                                                             |

| N        | RW CH3LIMITL |          |             | Write '1' to enable interrupt for event CH3LIMITL                         |

|          |              | Set      | 1           | Enable                                                                    |

|          |              | Disabled | 0           | Read: Disabled                                                            |

|          |              | Enabled  | 1           | Read: Enabled                                                             |

| 0        | RW CH4LIMITH |          | -           | Write '1' to enable interrupt for event CH4LIMITH                         |

| -        |              | Set      | 1           | Enable                                                                    |

|          |              | Disabled |             | Read: Disabled                                                            |

|          |              |          | 0           |                                                                           |

| <b>D</b> |              | Enabled  | 1           | Read: Enabled                                                             |

| Р        | RW CH4LIMITL |          |             | Write '1' to enable interrupt for event CH4LIMITL                         |

|          |              | Set      | 1           | Enable                                                                    |

|          |              | Disabled | 0           | Read: Disabled                                                            |

|          |              | Enabled  | 1           | Read: Enabled                                                             |

| Q        | RW CH5LIMITH |          |             | Write '1' to enable interrupt for event CH5LIMITH                         |

|          |              | Set      | 1           | Enable                                                                    |

|          |              | Disabled | 0           | Read: Disabled                                                            |

|          |              | Enabled  | 1           | Read: Enabled                                                             |

| R        | RW CH5LIMITL |          |             | Write '1' to enable interrupt for event CH5LIMITL                         |

|          |              | Set      | 1           | Enable                                                                    |

|          |              | Disabled | 0           | Read: Disabled                                                            |

|          |              | Enabled  | 1           | Read: Enabled                                                             |

| S        | RW CH6LIMITH |          |             | Write '1' to enable interrupt for event CH6LIMITH                         |

|          |              | Set      | 1           | Enable                                                                    |

|          |              | Disabled | 0           | Read: Disabled                                                            |

|          |              | Enabled  | 1           | Read: Enabled                                                             |

| т        | RW CH6LIMITL |          |             | Write '1' to enable interrupt for event CH6LIMITL                         |

|          |              | Set      | 1           | Enable                                                                    |

|          |              | Disabled | 0           | Read: Disabled                                                            |

|          |              |          | v           |                                                                           |

| Bit number      |          | 31 30 29 28 27 26 | 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-----------------|----------|-------------------|---------------------------------------------------------------------|

| ID              |          |                   | V U T S R Q P O N M L K J I H G F E D C B A                         |

| Reset 0x0000000 |          | 0 0 0 0 0 0       | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                             |

| ID Acce Field   |          |                   |                                                                     |

|                 | Enabled  | 1                 | Read: Enabled                                                       |

| U RW CH7LIMITH  |          |                   | Write '1' to enable interrupt for event CH7LIMITH                   |