# FSC-BT806A

# **5.0 Dual Mode Bluetooth Module Datasheet**

Version 1.2

## Copyright © 2013-2019 Feasycom Technology. All Rights Reserved.

Feasycom Technology reserves the right to make corrections, modifications, and other changes to its products, documentation and services at anytime. Customers should obtain the newest relevant information before placing orders. To minimize customer product risks, customers should provide adequate design and operating safeguards. Without written permission from Feasycom Technology, reproduction, transfer, distribution or storage of part or all of the contents in this document in any form is prohibited.

## **Revision History**

| Version | Data       | Notes                                                              |           |

|---------|------------|--------------------------------------------------------------------|-----------|

| 1.0     | 2018/05/25 | Initial Version                                                    | Devin Wan |

| 1.1     | 2019/10/22 | 1. Add Ordering Information and modify some incorrect descriptions | Devin Wan |

|         |            | 2. Update General Specifications                                   |           |

| 1.2     | 2020/03/25 | Update module picture, block diagram                               | Devin Wan |

|         |            |                                                                    |           |

## **Contact Us**

Shenzhen Feasycom Technology Co.,LTD

Email: sales@feasycom.com

Address: Room 2004-2005,20th Floor,Huichao Technology Building,Jinhai Road, Xixiang ,Baoan District,Shenzhen,518100,China. Tel: 86-755-27924639, 86-755-23062695

# Contents

| 1. INTRODUCTION                                  | 5  |

|--------------------------------------------------|----|

| 2. GENERAL SPECIFICATION                         | 7  |

| 3. HARDWARE SPECIFICATION                        | Q  |

|                                                  |    |

| 3.1 PIN DEFINITION DESCRIPTIONS                  | 9  |

| 4. PHYSICAL INTERFACE                            |    |

| 4.1 Power Management                             | 12 |

| 4.1.1 Power Supply                               | 12 |

| 4.1.2 Battery Charger                            |    |

| 4.1.2.1 Battery Charger Hardware Operating Modes |    |

| 4.1.2.2 Battery Charger Trimming and Calibration | 14 |

| 4.1.2.3 VM Battery Charger Control               | 14 |

| 4.1.2.4 Battery Charger Firmware and PS Keys     | 14 |

| 4.2 Reset                                        |    |

| 4.2.1 Digital Pin States on Reset                |    |

| 4.2.2 Status After Reset                         |    |

| 4.2.3 Automatic Reset Protection                 |    |

| 4.3 GENERAL PURPOSE ANALOG IO                    | 16 |

| 4.4 GENERAL PURPOSE DIGITAL IO                   |    |

| 4.5 RF INTERFACE                                 |    |

| 4.6 Serial Interfaces                            |    |

| 4.6.1 UART Interface                             |    |

| 4.6.2 I <sup>2</sup> C Interface                 |    |

| 4.6.3 USB Interface                              |    |

| 4.7 LED Drivers                                  |    |

| 4.8 AUDIO INTERFACES                             |    |

| 4.8.1 Audio Input and Output                     |    |

| 4.8.2 Audio Codec Interface                      |    |

| 4.8.3 Output Stage                               |    |

| 4.8.4 PCM Controller                             |    |

| 4.8.5 I <sup>2</sup> S Controller                |    |

| 4.9 PROGRAMMING AND DEBUG INTERFACE              | 36 |

| 5. ELECTRICAL CHARACTERISTICS                    |    |

| 5.1 Absolute Maximum Ratings                     | 37 |

| 5.2 Recommended Operating Conditions             |    |

| 5.3 INPUT/OUTPUT TERMINAL CHARACTERISTICS        |    |

| 5.3.1 Digital                                    |    |

| 5.3.2 Battery Charger                            |    |

| 5.3.3 USB                                        |    |

| 5.3.4 LED Driver Pads                            | 39 |

| 5.4 Stereo Codec                                 | 40 |

| 5.4.1 Analogue to Digital Converter                                                                                                                 |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.4.1 Digital to Analogue Converter                                                                                                                 | 40 |

| 5.5 AUXILIARY ADC                                                                                                                                   | 41 |

| 5.6 AUXILIARY DAC                                                                                                                                   | 41 |

| 5.7 I <sup>2</sup> C Dynamic Characteristics                                                                                                        | 42 |

| 5.8 PCM Dynamic Characteristics                                                                                                                     | 43 |

| 5.9 I <sup>2</sup> S Dynamic Characteristics                                                                                                        | 44 |

| 5.10 Power consumptions                                                                                                                             | 44 |

| 6. MSL & ESD PROTECTION                                                                                                                             | 45 |

| 6.1 USB Electrostatic Discharge Immunity                                                                                                            | 45 |

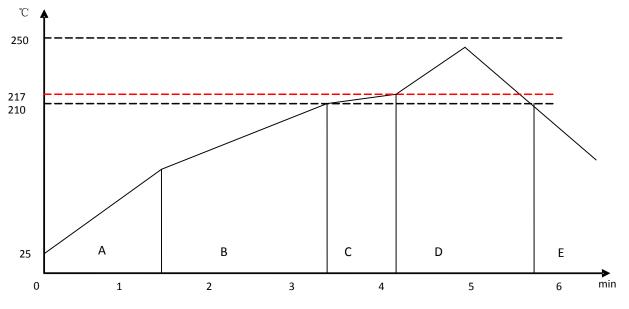

| 7. RECOMMENDED TEMPERATURE REFLOW PROFILE                                                                                                           | 46 |

| 8. MECHANICAL DETAILS                                                                                                                               | 47 |

| 8.1 MECHANICAL DETAILS                                                                                                                              | 47 |

|                                                                                                                                                     |    |

| 9. HARDWARE INTEGRATION SUGGESTIONS                                                                                                                 | 48 |

| 9. HARDWARE INTEGRATION SUGGESTIONS                                                                                                                 |    |

|                                                                                                                                                     | 48 |

| 9.1 Soldering Recommendations                                                                                                                       |    |

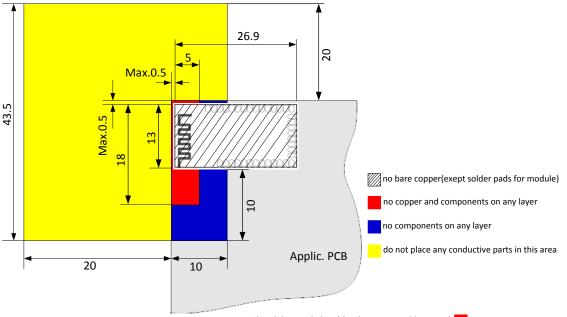

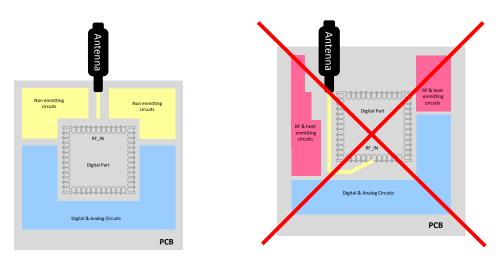

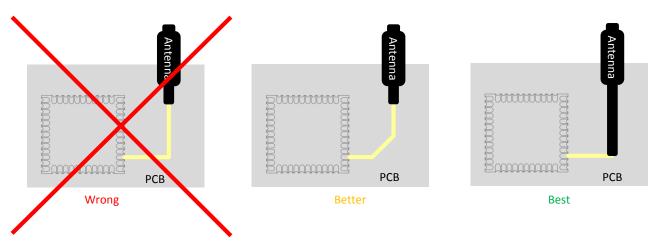

| 9.1 Soldering Recommendations         9.2 Layout Guidelines(Internal Antenna)                                                                       |    |

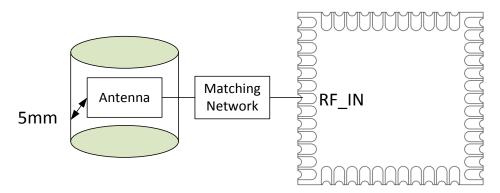

| <ul> <li>9.1 Soldering Recommendations</li> <li>9.2 Layout Guidelines(Internal Antenna)</li> <li>9.3 Layout Guidelines(External Antenna)</li> </ul> |    |

| <ul> <li>9.1 SOLDERING RECOMMENDATIONS</li> <li>9.2 LAYOUT GUIDELINES(INTERNAL ANTENNA)</li></ul>                                                   |    |

| <ul> <li>9.1 SOLDERING RECOMMENDATIONS</li> <li>9.2 LAYOUT GUIDELINES(INTERNAL ANTENNA)</li></ul>                                                   |    |

| <ul> <li>9.1 SOLDERING RECOMMENDATIONS</li></ul>                                                                                                    |    |

| <ul> <li>9.1 SOLDERING RECOMMENDATIONS</li></ul>                                                                                                    |    |

| <ul> <li>9.1 SOLDERING RECOMMENDATIONS</li></ul>                                                                                                    |    |

## 1. INTRODUCTION

#### **Overview**

FSC-BT806A is a Bluetooth 5.0 dual-mode module. It provides a Bluetooth Low Energy fully compliant system for audio and data communication with Feasycom stack.

FSC-BT806A integrates an ultra-low-power DSP and application processor with embedded flash memory, a high-performance stereo codec, a power management subsystem, I<sup>2</sup>S, LED drivers and ADC I/O in a SOC IC. The dual-core architecture with flash memory enables manufacturers to easily differentiate their products with new features without extending development cycles.

By default, FSC-BT806A module is equipped with powerful and easy-to-use Feasycom firmware. It's easy-to-use and completely encapsulated. Feasycom firmware enables users to access Bluetooth functionality with simple ASCII commands delivered to the module over serial interface - it's just like a Bluetooth modem.

Therefore, FSC-BT806A provides an ideal solution for developers who want to integrate Bluetooth wireless technology into their design.

#### Features

- Bluetooth v5.0/4.0/3.0/2.1/2.0/1.2/1.1, Class 1.5

- 80MHz RISC MCU and 80MIPS Kalimba DSP

- Stereo codec with 2 channels of ADC and up to 4 microphone inputs (includes bias generators and digital microphone support)

- Support for CSR's latest CVC technology for narrow-band and wideband voice connections including wind noise reduction

- Audio interfaces: I<sup>2</sup>S/PCM and SPDIF

- Music Enhancements: SBC,MP3,AAC and AAC+,Faststream codec,atpX,5-band EQ,3D stereo separation and so on.

- Support HSP, HFP, A2DP, AVRCP, PBAP, MAP, SPP, BLE profile

- Multipoint support for HFP connection to 2 handsets for voice

- Multipoint support for A2DP connection to 2 A2DP source for music playback

- 3 Hardware LED controllers(for RGB)

- UART,I<sup>2</sup>C,SPI,PIO,AIO,USB control interfaces

- Postage stamp sized form factor

- MFI Support

- Built-in RF combo filter, Built-in PCB antenna to support external antenna

- Fast charging support up to 200mA with no external components

- RoHS compliant

- Industrial temperature range from -40°C to +85°C

#### Application

- Smart watches & Bluetooth bracelets

- Bluetooth headphones

- Smart remote controllers

- Wired or wireless sound bars

- Wired or wireless speakers

- Wearable audio with sensors(health and well-being applications)

- Stereo (AV) Transmitter

- Automotive Hands-Free Kits

# Module picture as below showing

Figure 1: FSC-BT806A Picture

# 2. General Specification

#### Table 1: General Specifications

| Categories    | Features                   | Implementation                                                       |  |  |  |

|---------------|----------------------------|----------------------------------------------------------------------|--|--|--|

|               | On-board chip              | CSR8670                                                              |  |  |  |

| -             |                            | V5.0 Dual-mode Bluetooth low energy radio                            |  |  |  |

|               |                            | Software complies with the Bluetooth Core v5.0 Specification         |  |  |  |

|               | Bluetooth Low energy       | Support for Bluetooth basic rate / EDR and low energy Connections    |  |  |  |

| Wireless      |                            | 3 Bluetooth low energy connections at the same time as basic rate    |  |  |  |

| Specification |                            | A2DP                                                                 |  |  |  |

| opeomoution   | Frequency                  | 2.402 - 2.480 GHz                                                    |  |  |  |

| -             | Transmit Power             | +10 dBm (Maximum)                                                    |  |  |  |

| -             | Receive Sensitivity        | -88 dBm(Typical)                                                     |  |  |  |

|               |                            | Real-time digitised RSSI available to application                    |  |  |  |

| -             | Raw Data Rates (Air)       | 3 Mbps(Classic BT - BR/EDR)                                          |  |  |  |

|               |                            | TX, RX, CTS, RTS                                                     |  |  |  |

|               |                            | General Purpose I/O                                                  |  |  |  |

|               | UART Interface             | Default 115200,N,8,1                                                 |  |  |  |

|               |                            | Baudrate support from 1200 to 921600                                 |  |  |  |

|               |                            | 8 data bit character                                                 |  |  |  |

| -             |                            | 23(maximum – configurable) lines                                     |  |  |  |

|               |                            | O/P drive strength (4 mA)                                            |  |  |  |

|               | GPIO                       | Pull-up resistor (33 KΩ) control                                     |  |  |  |

|               |                            | Read pin-level                                                       |  |  |  |

| -             | I <sup>2</sup> C Interface | 1 (hardware I <sup>2</sup> C interface). Up to 400 kbps              |  |  |  |

|               |                            | Master and slave I <sup>2</sup> C interface                          |  |  |  |

|               |                            | SPI debug and programming interface with read access disable         |  |  |  |

|               | SPI Interface              | locking                                                              |  |  |  |

| Peripherals   |                            | Analog input voltage range: 0~ 1.3V                                  |  |  |  |

|               | ADC Interface              | Supports single a 10-bit ADC and a 10-bit DAC                        |  |  |  |

|               |                            | 1 channels (configured from GPIO total)                              |  |  |  |

| -             | USB Interface              | 1 full-speed (12Mbps)                                                |  |  |  |

| -             |                            |                                                                      |  |  |  |

|               |                            |                                                                      |  |  |  |

|               |                            |                                                                      |  |  |  |

| -             |                            | 80 MHz RISC MCU and 120 MHz Kalimba DSP                              |  |  |  |

|               | <b>.</b>                   | Up to 120MIPS DSP for intensive digital signal processing algorithms |  |  |  |

|               | Digital audio parameters   | 24-bit audio                                                         |  |  |  |

|               | CSR8670                    | Supported sample rates of 8, 11.025, 16, 22.05, 32, 44.1,48,96kHz    |  |  |  |

|               |                            | and 192kHz (DAC only)                                                |  |  |  |

|               |                            | SPP (Serial Port Profile) - Up to 600 Kbps                           |  |  |  |

| Profiles      | BR/EDR                     | A2DP/AVRCP/HFP/HSP/HID/PBAP/SPP Profiles support                     |  |  |  |

| FIUMES        |                            |                                                                      |  |  |  |

|                   |                      | Simultaneous BR/EDR and BLE support                        |

|-------------------|----------------------|------------------------------------------------------------|

| Maximum BR/EDR    |                      | up to 7 active slaves                                      |

| Connections       | Bluetooth Low Energy | 1 connection as peripheral, up to 5 connections as central |

|                   |                      | Via UART                                                   |

| FW upgrade        |                      | USB                                                        |

|                   |                      | SPI                                                        |

| Supply Voltage    | Supply               | VDD_IO: 1.7 ~ 3.6V ; VBAT_IN: 2.8V ~ 4.3V                  |

|                   |                      | Max Peak Current(TX Power @ +10dBm TX): 85mA               |

| Power Consumption |                      | Standby Doze (Wait event) - <1mA (TBD)                     |

|                   |                      | Deep Sleep - ~300uA(TBD)                                   |

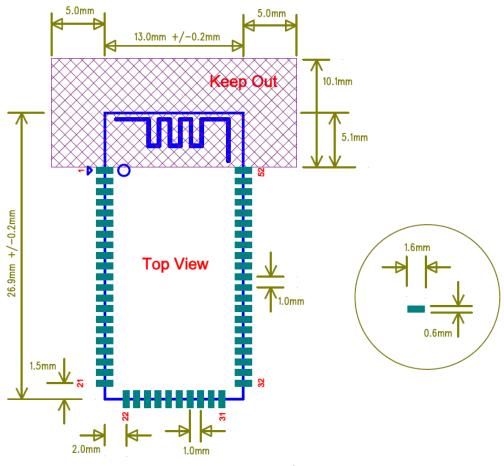

| Physical          | Dimensions           | 13mm(W) X 26.9mm(L) X 2.2mm(H); Pad Pitch 1mm              |

| Environmental     | Operating            | -40°C to +85°C                                             |

| Environmental     | Storage              | -40°C to +105°C                                            |

| Miscellaneous     | Lead Free            | Lead-free and RoHS compliant                               |

| wiscellaneous     | Warranty             | One Year                                                   |

| Humidity          |                      | 10% ~ 90% non-condensing                                   |

| MSL grade:        |                      | MSL 3 (With JEDEC J-STD-020)                               |

|                   |                      | Human Body Model: Class-2                                  |

| ESD grade:        |                      | Machine Model: Class-200V                                  |

|                   |                      | Charged Device Model: Class II                             |

# 3. HARDWARE SPECIFICATION

Г

٦

|              |                                                                                                                                                                              |            | ٦ | ſ | l          | ſ | ٦ |   |      |                  |                                                                                |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---|---|------------|---|---|---|------|------------------|--------------------------------------------------------------------------------|--|

|              | AIO0<br>AIO1<br>I2S_CLK<br>I2S_IN<br>I2S_OUT<br>I2S_WS<br>RESET<br>SPI_CSB<br>SPI_CSB<br>SPI_MISO<br>SPI_CLK<br>BT_TX<br>BT_CTS<br>BT_RX<br>BT_CTS<br>BT_RTS<br>LED0<br>LED1 |            |   |   |            |   |   |   |      | OUT              | EXT_ANT<br>GND<br>SPK_LP<br>SPK_LN<br>SPK_RP<br>SPK_RN<br>MIC_L_BIAS<br>MIC_LN |  |

| -20-<br>-21- | PIO0                                                                                                                                                                         |            |   |   |            |   |   | 4 | 5    | /DD_USB/3.3V_OU1 | VBAT_IN                                                                        |  |

|              |                                                                                                                                                                              | CN5<br>222 |   |   | 201d<br>26 |   |   |   | PI01 |                  |                                                                                |  |

Figure 3: FSC-BT806A PIN Diagram(Top View)

# **3.1 PIN Definition Descriptions**

| Table | Table 2: Pin definition |      |                                                      |        |  |  |  |

|-------|-------------------------|------|------------------------------------------------------|--------|--|--|--|

| Pin   | Pin Name                | Туре | Pin Descriptions                                     | Notes  |  |  |  |

| 1     | GND                     | Vss  | Power Ground                                         |        |  |  |  |

| 2     | AIOO                    | I/O  | Analogue 1 programmable input/output line.           | Note 8 |  |  |  |

| 3     | AIO1                    | I/O  | Analogue 2 programmable input/output line.           | Note 8 |  |  |  |

| 4     | I2S_CLK                 | I/O  | I2S/PCM synchronous data clock.                      | Note 6 |  |  |  |

|       |                         |      | Alternative Function: Programmable input/output line |        |  |  |  |

| 5     | I2S_IN                  | I/O  | I2S/PCM synchronous data input.                      | Note 6 |  |  |  |

|       |                         |      | Alternative Function: Programmable input/output line |        |  |  |  |

| 6     | I2S_OUT                 | I/O  | I2S/PCM synchronous data output.                     | Note 6 |  |  |  |

|       |                         |      | Alternative Function: Programmable input/output line |        |  |  |  |

| 7  | 12S_WS           | I/O | I2S/PCM synchronous data sync.                                       | Note 6 |

|----|------------------|-----|----------------------------------------------------------------------|--------|

|    |                  |     | Alternative Function: Programmable input/output line                 |        |

| 8  | RESET            | I   | External reset input: Active LOW, with an inter an internal pull-up. |        |

|    |                  |     | Set this pin low reset to initial state. (>5mS)                      |        |

| 9  | SPI_CSB          | I/O | Chip select for SPI, active low.(Debug)                              |        |

| 10 | SPI_MOSI         | I/O | SPI data input. (Debug)                                              |        |

| 11 | SPI_MISO         | I/O | SPI data output. (Debug)                                             |        |

| 12 | SPI_CLK          | I/O | SPI clock. (Debug)                                                   |        |

| 13 | BT_TX            | I/O | UART Data output                                                     | Note6  |

|    |                  |     | Alternative Function: Programmable input/output line                 |        |

| 14 | BT_RX            | I/O | UART Data input                                                      | Note 6 |

|    |                  |     | Alternative Function: Programmable input/output line                 |        |

| 15 | BT_CTS           | I/O | UART clear to send, active low.                                      | Note6  |

|    |                  |     | Alternative Function: Programmable input/output line                 |        |

| 16 | BT_RTS           | I/O | UART request to send, active low.                                    | Note 6 |

|    |                  |     | Alternative Function: Programmable input/output line                 |        |

| 17 | LED0             | I/O | LED driver. (RED LED)                                                | Note 6 |

| 18 | LED1             | I/O | LED driver. (BLUE LED)                                               | Note 6 |

| 19 | LED2             | I/O | LED driver. (GREEN LED)                                              | Note 6 |

| 20 | PIOO             | I/O | Programmable input/output line                                       |        |

| 21 | PIO1             | I/O | Programmable input/output line                                       |        |

| 22 | GND              | Vss | Power Ground                                                         |        |

| 23 | PIO2             | I/O | Programmable input/output line                                       |        |

| 24 | PIO3             | I/O | Programmable input/output line                                       |        |

| 25 | PIO4             | I/O | Programmable input/output line                                       |        |

| 26 | PIO5             | I/O | Programmable input/output line                                       |        |

| 27 | PIO6             | I/O | Programmable input/output line                                       | Note 5 |

|    |                  |     | Alternative Function: I <sup>2</sup> C_SCL                           |        |

| 28 | PIO7             | I/O | Programmable input/output line                                       | Note 5 |

|    |                  |     | Alternative Function: I <sup>2</sup> C_SDA                           |        |

| 29 | PIO14            | I/O | Programmable input/output line                                       |        |

| 30 | PIO15            | I/O | Programmable input/output line                                       |        |

| 31 | VDD_USB/3.3V_OUT | Vdd | Positive supply for USB ports/ 3.3V bypass linear regulator output   | Note 7 |

| 32 | GND              | Vss | Power Ground                                                         |        |

| 33 | VBAT_IN          | Vdd | Power supply voltage 2.8V~ 4.3V (Battery positive terminal)          |        |

| 34 | VREGENABLE       | I   | Power enable                                                         | Note 3 |

|    |                  |     | * The PIN on electricity than VBAT_IN and VDD_IO foot 100 ms         |        |

|    |                  |     | delay.                                                               |        |

| 35 | 1.8V_OUT         | Vdd | 1.8V switch-mode power regulator output                              | Note 1 |

| 36 | VDD_IO           | Vdd | Power supply voltage 1.7V ~ 3.6V (for input/output ports)            | Note 2 |

| 37 | USB_DP           | I/O | USB data positive                                                    | Note 4 |

| 38 | USB_DN           | I/O | USB data negative                                                    | Note 4 |

| 39 | VCC_CHG          | Vdd | Battery charger input (5V)                                           | Note 4 |

| 40 | MIC_RP           | I   | Microphone input positive, right                                     |        |

| -  |                  |     |                                                                      |        |

| 41 | MIC_RN     | Ι   | Microphone input negative, right                             |      |

|----|------------|-----|--------------------------------------------------------------|------|

| 42 | MIC_R_BIAS | 0   | Microphone R bias                                            |      |

| 43 | MIC_LP     | Ι   | Microphone input positive, left                              |      |

| 44 | MIC_LN     | I   | Microphone input negative, left                              |      |

| 45 | MIC_L_BIAS | 0   | Microphone L bias                                            |      |

| 46 | SPK_RN     | 0   | Speaker output negative, right                               |      |

| 47 | SPK_RP     | 0   | Speaker output positive, right                               |      |

| 48 | SPK_LN     | 0   | Speaker output negative, left                                |      |

| 49 | SPK_LP     | 0   | Speaker output positive, left                                |      |

| 50 | GND        | Vss | Power Ground                                                 |      |

| 51 | EXT_ANT    | RF  | Bluetooth 50 $\Omega$ transmitter output /receiver input Not | te 9 |

| 52 | GND        | Vss | Power Ground                                                 |      |

|    |            |     |                                                              |      |

#### Module Pin Notes:

| module |                                                                                                                                                                                                                                                                                                                                              |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note 1 | The internal output of 1.8 V power supply provides maximum 30MA current, and the specific use method can see the application circuit diagram                                                                                                                                                                                                 |

| Note 2 | Provid voltage reference to I/O, such as: PIO, UART, SPI, I2S, PCM, etc                                                                                                                                                                                                                                                                      |

| Note 3 | Regulator enable input. Can also be sensed as an input.<br>Regulator enable and multifunction button. A high input (tolerant to VBAT) enables the on-chip regulators,<br>which can then be latched on internally and the button used as a multifunction input.<br><b>* The PIN on electricity than VBAT_IN and VDD_IO foot 100 ms delay.</b> |

| Note 4 | Using USB function and Lithium battery charging function, the pin should connect 5V voltage                                                                                                                                                                                                                                                  |

| Note 5 | I <sup>2</sup> C Serial Clock and Data.<br>It is essential to remember that pull-up resistors on both SCL and SDA lines are not provided in the module<br>and MUST be provided external to the module.                                                                                                                                       |

| Note 6 | For customized module, this pin can be work as I/O Interface.                                                                                                                                                                                                                                                                                |

| Note 7 | <ol> <li>When you need to use the USB function,<br/>this pin needs to be connected to 3.3V (voltage range: 3.1V~3.6V)</li> <li>when the No. 39 PIN (VCC_CHG) with a 5V input pin,<br/>this pin outputs 3.2V ~ 3.4V (maximum current: 250mA)</li> </ol>                                                                                       |

| Note 8 | Analog input voltage range: 0~ 1.3V                                                                                                                                                                                                                                                                                                          |

| Note 9 | By default, this PIN is an empty feet. This PIN can connect to an external antenna to improve the Bluetooth signal coverage.<br>If you need to use an external antenna, by modifying the module on the OR resistance to block out the on-board antenna; Or contact Feasycom for modification.                                                |

# 4. PHYSICAL INTERFACE

#### 4.1 Power Management

#### 4.1.1 Power Supply

The transient response of the regulator is important. If the power rails of the module are supplied from an external voltage source, the transient response of any regulator used should be 20µs or less. It is essential that the power rail recovers quickly.

#### 4.1.2 Battery Charger

#### 4.1.2.1 Battery Charger Hardware Operating Modes

The default mode for the FSC-BT806A battery charger is OFF.

The internal charger circuit can provide up to 200mA of charge current.

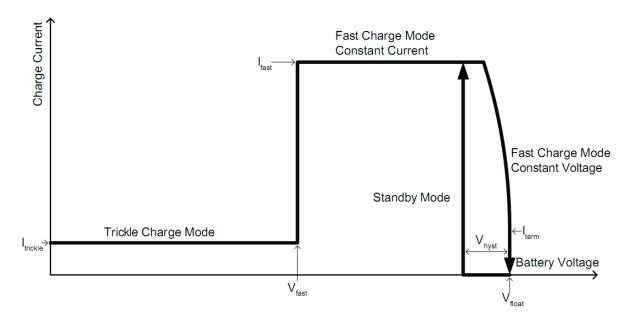

The battery charger hardware is controlled by the VM, see picture below. The battery charger has 5 modes:

- Disabled

- Trickle charge

- Fast charge

- Standby: fully charged or float charge

- Error: charging input voltage, VCHG, is too low

The battery charger operating mode is determined by the battery voltage and current, see the table below and the picture below.

| Parameter      | Battery Charger Enabled | VBAT_SENSE(internal)                               |

|----------------|-------------------------|----------------------------------------------------|

| Off            | No                      | х                                                  |

| Trickle charge | Yes                     | >0 and <v<sub>fast</v<sub>                         |

| Fast charge    | Yes                     | >V <sub>fast</sub> and <v<sub>float</v<sub>        |

| Standby        | Yes                     | $I_{term}^{(a)}$ and >( $V_{float}$ - $V_{hyst}$ ) |

| Error          | Yes                     | >(VCC_CHG - 50mV)                                  |

Table 3: Battery Charger Operating Modes Determined by Battery Voltage and Current

The picture below shows the mode-to-mode transition voltages. These voltages are fixed and calibrated. The transition between modes can occur at any time.

Figure 4: Battery Charger Mode-to-Mode Transition Diagram

#### **Disabled Mode**

In the disabled mode the battery charger is fully disabled and draws no active current on any of its terminals.

## Trickle Charge Mode

In the trickle charge mode, when the voltage on VBAT\_SENSE is lower than the V<sub>fast</sub> threshold, a current of

approximately 10% of the fast charge current, I<sub>fast</sub>, is sourced from the VBAT\_IN pin.

The V<sub>fast</sub> threshold detection has hysteresis to prevent the charger from oscillating between modes.

## Fast Charge Mode

When the voltage on VBAT\_SENSE is greater than  $V_{fast}$ , the current sourced from the VBAT pin increases to  $I_{fast}$ .  $I_{fast}$  is between 10mA and 200mA set by PS Key or a VM trap. In addition,  $I_{fast}$  is calibrated in production test to correct for process variation in the charger circuit.

The current is held constant at  $I_{fast}$  until the voltage at VBAT\_SENSE reaches  $V_{float}$ , then the charger reduces the current sourced to maintain a constant voltage on the VBAT\_SENSE pin.

When the current sourced is below the termination current,  $I_{term}$ , the charging stops and the charger enters standby mode.  $I_{term}$  is typically 10% of the fast charge current.

## Standby Mode

When the battery is fully charged, the charger enters standby mode, and battery charging stops. The battery voltage on the VBAT\_SENSE pin is monitored, and when it drops below a threshold set at  $V_{hyst}$  below the final charging voltage,  $V_{float}$ , the charger re-enters fast charge mode.

#### Error Mode

The charger enters the error mode if the voltage on the VCC\_CHG pin is too low to operate the charger correctly (VBAT\_SENSE is greater than VCC\_CHG - 50mV (typical)).

In this mode, charging is stopped. The battery charger does not require a reset to resume normal operation.

## 4.1.2.2 Battery Charger Trimming and Calibration

The battery charger default trim values are written into internal flash when each IC is characterised. Please contact Feasycom regarding to PS keys.

#### 4.1.2.3 VM Battery Charger Control

The VM charger code has overall supervisory control of the battery charger and is responsible for:

- Responding to charger power connection/disconnection events

- Monitoring the temperature of the battery

- Monitoring the temperature of the die to protect against silicon damage

- Monitoring the time spent in the various charge states

- Enabling/disabling the charger circuitry based on the monitored information

- Driving the user visible charger status LED(s)

#### 4.1.2.4 Battery Charger Firmware and PS Keys

The battery charger firmware sets up the charger hardware based on the PS Key settings and call traps from the VM charger code. It also performs the initial analogue trimming. Settings for the charger current depend on the battery capacity and type, which are set by the user in the PS Keys.

## 4.2 Reset

FSC-BT806A is reset from several sources:

- 🕿 RST# pin

- Power-on reset

- USB charger attach reset

- UART break character

- Software configured watchdog timer

The RST# pin is an active low reset and is internally filtered using the internal low frequency clock oscillator. Feasycom recommends applying RST# for a period >5ms.

At reset the digital I/O pins are set to inputs for bidirectional pins and outputs are set to tristate. Following a reset, FSC-BT806A assumes the maximum XTAL\_IN frequency, which ensures that the internal clocks run at a safe (low) frequency until FSC-BT806A is configured for the actual XTAL\_IN frequency. If no clock is present at XTAL\_IN, the oscillator in FSC-BT806A free runs, again at a safe frequency.

The RESET pin is an active low reset and is internally filtered using the internal low frequency clock oscillator. A reset will be performed between 1.5 and 4.0ms following RESET being active. It is recommended that RESET be applied for a period greater than 5ms.

At reset the digital I/O pins are set to inputs for bi-directional pins and outputs are tri-state. The PIOs have weak pull-ups.

#### 4.2.1 Digital Pin States on Reset

This table shows the pin states of FSC-BT806A on reset. PU and PD default to weak values unless specified otherwise.

| Pin Name/Group           | І/О Туре                        | Full Chip Reset |

|--------------------------|---------------------------------|-----------------|

| USB_DP                   | Digital bidirectional           | N/A             |

| USB_DN                   | Digital bidirectional           | N/A             |

| BT_TX                    | Digital bidirectional with PU   | Weak PU         |

| BT_RX                    | Digital bidirectional with PU   | Strong PU       |

| BT_CTS                   | Digital bidirectional with PD   | Weak PD         |

| BT_RTS                   | Digital bidirectional with PU   | Strong PU       |

| SPI_CSB                  | Digital input with PU           | Strong PU       |

| SPI_CLK                  | Digital input with PD           | Weak PD         |

| SPI_MISO                 | Digital tristate output with PD | Weak PD         |

| SPI_MOSI                 | Digital input with PD           | Weak PD         |

| RESET                    | Digital input with PU           | Strong PU       |

| 125_IN                   | Digital bidirectional with PD   | Weak PD         |

| I2S_OUT                  | Digital bidirectional with PD   | Weak PD         |

| I2S_WS                   | Digital bidirectional with PD   | Weak PD         |

| I2S_CLK                  | Digital bidirectional with PD   | Weak PD         |

| RESET                    | Digital input with PU           | Strong PU       |

| PIO0,1,2,3,4,5,6,7,14,15 | Digital bidirectional with PD   | Weak PD         |

Table 4: Pin States on Reset

#### 4.2.2 Status After Reset

The status of FSC-BT806A after a reset is:

- Warm reset: baud rate and RAM data remain available

- Cold reset: baud rate and RAM data not available

#### 4.2.3 Automatic Reset Protection

FSC-BT806A includes an automatic reset protection circuit which restarts/resets CSR8670 WLCSP when an unexpected reset occurs, e.g. ESD strike or lowering of RST#. The automatic reset protection circuit enables resets from the VM without the requirement for external circuitry.

#### Note:

The reset protection is cleared after typically 2s (1.6s min to 2.4s max).

If RST# is held low for >2.4s FSC-BT806A turns off.

A rising edge on VREGENABLE or VCC\_CHG is required to power on FSC-BT806A.

## 4.3 General Purpose Analog IO

FSC-BT806A has 1 general-purpose analogue interface pins, AIO1, for accessing internal circuitry and control signals. Auxiliary functions available on the analogue interface include a 10-bit ADC and a 10-bit DAC. Signals selectable on this interface include the band gap reference voltage. When configured for analogue signals the voltage range is constrained by the analogue supply voltage. When configured to drive out digital level signals generated from within the analogue part of the device, the output voltage level is determined by VDD\_AUX(internal).

## 4.4 General Purpose Digital IO

10 lines of programmable bidirectional I/O are available on the FSC-BT806A. Some of the PIOs on the FSC-BT806A have alternative functions:

- **3** digital microphone interfaces for control of up to 3 digital microphones:

- Clock on any even PIOs as determined by the software

- Data on any odd PIOs as determined by the software

- I<sup>2</sup>C interface on any PIOs as determined by the software

- LED[2:0] directly map to PO[31:29]

- I2S/PCM interface on PIO[20:17]

## 4.5 **RF Interface**

For this module, the antenna must be connected to work properly.

The user can connect a 50 ohm antenna directly to the RF port.

- **2402–2480** MHz Bluetooth 5.0 Dual Mode (BT and BLE); 1 Mbps to 3 Mbps over the air data rate.

- TX output power of +10dBm(MAX).

- Receiver to achieve maximum sensitivity -88dBm @ 1 Mbps BLE or Classic BT, 2 Mbps, 3 Mbps).

# 4.6 Serial Interfaces

## 4.6.1 UART Interface

FSC-BT806A provides one channels of Universal Asynchronous Receiver/Transmitters(UART)(Full-duplex asynchronous communications). The UART Controller performs a serial-to-parallel conversion on data received from the peripheral and a parallel-to-serial conversion on data transmitted from the CPU. Each UART Controller channel supports ten types of interrupts.

This is a standard UART interface for communicating with other serial devices. The UART interface provides a simple mechanism for communicating with other serial devices using the RS232 protocol.

When the module is connected to another digital device, UART\_RX and UART\_TX transfer data between the two devices. The remaining two signals, UART\_CTS and UART\_RTS, can be used to implement RS232 hardware flow control where both are active low indicators.

This module output is at 3.3V CMOS logic levels (tracks VCC). Level conversion must be added to interface with an RS-232 level compliant interface.

Some serial implementations link CTS and RTS to remove the need for handshaking. We do not recommend linking CTS and RTS except for testing and prototyping. If these pins are linked and the host sends data when the FSC-BT806A deasserts its RTS signal, there is significant risk that internal receive buffers will overflow, which could lead to an internal processor crash. This drops the connection and may require a power cycle to reset the module. We recommend that you adhere to the correct CTS/RTS handshaking protocol for proper operation.

#### Table 5: Possible UART Settings

| Parameter           |          | Possible Values      |

|---------------------|----------|----------------------|

|                     | Minimum  | 1200 baud (≤2%Error) |

| Baudrate            | Standard | 115200bps(≤1%Error)  |

|                     | Maximum  | 4Mbaud(≤1%Error)     |

| Flow control        |          | RTS/CTS, or None     |

| Parity              |          | None, Odd or Even    |

| Number of stop bits |          | 1 /2                 |

| Bits per channel    |          | 8                    |

When connecting the module to a host, please make sure to follow .

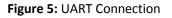

The UART interface resets FSC-BT806A on reception of a break signal. A break is identified by a continuous logic low (0V) on the UART\_RX terminal, as below picture shows. If t BRK is longer than the value defined by the PSKEY\_HOSTIO\_ UART\_RESET\_TIMEOUT, a reset occurs. This feature enables a host to initialise the system to a known state. Also, FSC-BT806A can issue a break character for waking the host.

Figure 6: Break Signal

The UART interface is tristate while FSC-BT806A is being held in reset. This enables the user to connect other devices onto the physical UART bus. The restriction with this method is that any devices connected to this bus must tristate when FSC-BT806A reset is de-asserted and the firmware begins to run.

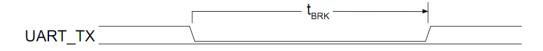

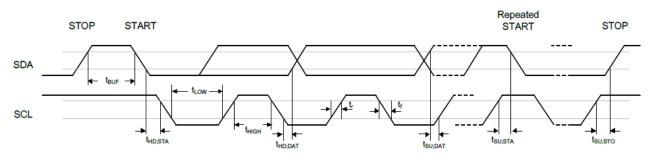

## 4.6.2 I<sup>2</sup>C Interface

FSC-BT806A includes a configurable I<sup>2</sup>C interface.

$I^2C$  is a two-wire, bi-directional serial bus that provides a simple and efficient method of data exchange between devices. The  $I^2C$  standard is a true multi-master bus including collision detection and arbitration that prevents data corruption if two or more masters attempt to control the bus simultaneously.

Data is transferred between a Master and a Slave synchronously to SCL on the SDA line on a byte-by-byte basis. Each data byte is 8-bit long. There is one SCL clock pulse for each data bit with the MSB being transmitted first. An acknowledge bit follows each transferred byte. Each bit is sampled during the high period of SCL; therefore, the SDA line may be changed only during the low period of SCL and must be held stable during the high period of SCL. A transition on the SDA line while SCL is high is interpreted as a command (START or STOP). Please refer to the following figure for more details about I<sup>2</sup>C Bus Timing.

Figure 7: I2C Bus Timing

The device on-chip  $I^2C$  logic provides the serial interface that meets the  $I^2C$  bus standard mode specification. The  $I^2C$  port handles byte transfers autonomously. The  $I^2C$  H/W interfaces to the  $I^2C$  bus via two pins: SDA and SCL. Pull up resistor is needed for  $I^2C$  operation as these are open drain pins. When the I/O pins are used as  $I^2C$  port, user must set the pins function to  $I^2C$  in advance.

#### 4.6.3 USB Interface

FSC-BT806A has a full-speed (12Mbps) USB interface for communicating with other compatible digital devices. The USB interface on FSC-BT806A acts as a USB peripheral, responding to requests from a master host controller.

FSC-BT806A supports the Universal Serial Bus Specification, Revision v2.0 (USB v2.0 Specification) and USB Battery Charging Specification , available from <u>http://www.usb.org</u>. For more information on how to integrate the USB interface on FSC-BT806A see the Bluetooth and USB Design Considerations Application Note .

As well as describing USB basics and architecture, the application note describes:

- Power distribution for high and low bus-powered configurations

- Power distribution for self-powered configuration, which includes USB VBUS monitoring (when VBUS is>3.1)

- USB enumeration

- Electrical design guidelines for the power supply and data lines, as well as PCB tracks and the effects of ferrite beads

- USB suspend modes and Bluetooth low-power modes:

- ♦ Global suspend

- Selective suspend, includes remote wake

- Wake on Bluetooth, includes permitted devices and set-up prior to selective suspend

- Suspend mode current draw

- PIO status in suspend mode

- Resume, detach and wake PIOs

- Battery charging from USB, which describes dead battery provision, charge currents, charging in suspend modes and USB VBUS voltage consideration

- USB termination when interface is not in use

- Internal modules, certification and non-specification compliant operation

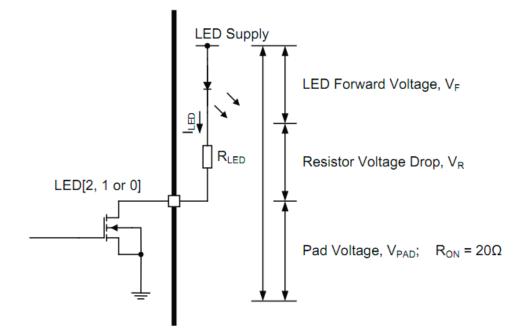

#### 4.7 LED Drivers

FSC-BT806A includes a 3-pad synchronised PWM LED driver for driving RGB LEDs for producing a wide range of colours. All LEDs are controlled by firmware.

The terminals are open-drain outputs, so the LED must be connected from a positive supply rail to the pad in series with a current-limiting resistor.

Figure 8: LED Equivalent Circuit

If a known value of current is required through the LED to give a specific luminous intensity, then the value of R<sub>LED</sub> is calculated.

$$I_{LED} = \frac{VDD - V_F}{R_{LED} + R_{ON}}$$

For the LED pads to act as resistance, the external series resistor,  $R_{LED}$ , needs to be such that the voltage dropacross it, V<sub>R</sub>, keeps V<sub>PAD</sub> below 0.5V.

#### $VDD=V_F+V_R+V_{PAD}$

#### Note:

The LED current adds to the overall current. Conservative LED selection extends battery life.

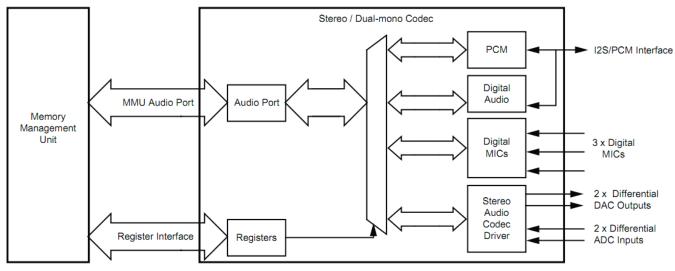

## 4.8 Audio Interfaces

The audio interface circuit consists of:

- Stereo/dual-mono audio codec

- Dual analogue audio inputs

- Dual analogue audio outputs

- 2 digital MEMS microphone inputs

- A configurable PCM, I<sup>2</sup>S or SPDIF interface

Figure 9: Audio Interface

The interface for the digital audio bus shares the same pins as the PCM codec interface described. which means each of the audio buses are mutually exclusive in their usage.

Table 6: Alternative functions of the digital audio bus interface on the PCM interface

| PCM Interface | SPDIF Interface | I2S Interface |

|---------------|-----------------|---------------|

| PCM_OUT       | SPDIF_OUT       | I2S_OUT       |

| PCM_IN        | SPDIF_IN        | 125_IN        |

| PCM_SYNC      |                 | 12S_WS        |

| PCM_CLK       |                 | I2S_CLK       |

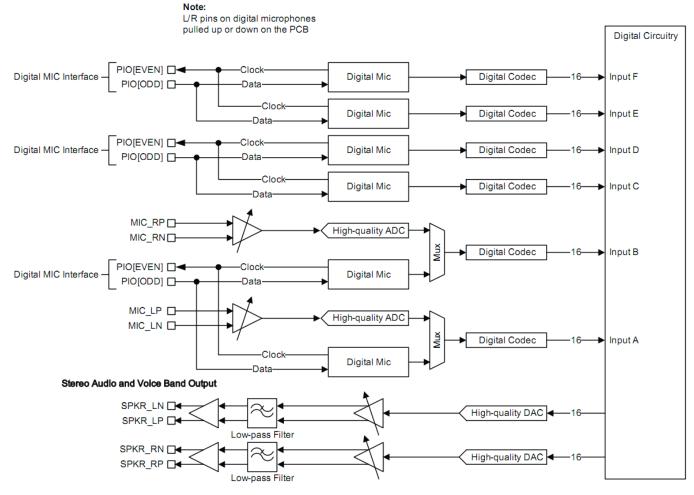

#### 4.8.1 Audio Input and Output

The audio input circuitry consists of:

- 2 independent 16-bit high-quality ADC channels:

- Programmable as either microphone or line input

- Programmable as either stereo or dual-mono inputs

- Multiplexed with 2 of the digital microphone inputs

- Each channel is independently configurable to be either single-ended or fully differential

- Each channel has an analogue and digital programmable gain stage for optimisation of different microphones

- 2 digital MEMS microphone channels, of which 4 have independent codec channels and 2 share their codecs with the 2 high-quality audio inputs

The audio output circuitry consists of a dual differential class A-B output stage.

#### Note:

FSC-BT806A is designed for a differential audio output. If a single-ended audio output is required, use an external differential to single-ended converter.

#### 4.8.2 Audio Codec Interface

The main features of the interface are:

- Stereo and mono analogue input for voice band and audio band

- Stereo and mono analogue output for voice band and audio band

- Support for stereo digital audio bus standards such as I<sup>2</sup>S

- Support for IEC-60958 standard stereo digital audio bus standards, e.g. SPDIF and AES3 (also known as AES/EBU)

- Support for PCM interfaces including PCM master codecs that require an external system clock

#### Note:

To avoid any confusion regarding stereo operation this data sheet explicitly states which is the left and right channel for audio output. With respect to audio input, software and any registers, channel 0 or channel A represents the left channel and channel 1 or channel B represents the right channel.

## Audio Codec Block Diagram

#### Stereo Audio, Voice Band and Digital Microphone Input

Figure 10: Audio Codec Input and Output Stages

FSC-BT806A audio codec uses a fully differential architecture in the analogue signal path, which results in low noise sensitivity and good power supply rejection while effectively doubling the signal amplitude. It operates from a dual power supply, VDD\_AUDIO(internal) for the audio circuits and VDD\_AUDIO\_DRV (internal) for the audio driver circuits.

#### ADC

The picture above shows the FSC-BT806A consists of 2 high-quality ADCs

- Each ADC has a second-order Sigma-Delta converter.

- Each ADC is a separate channel with identical functionality.

- There are 2 gain stages for each channel, 1 of which is an analogue gain stage and the other is a digital gain stage

## ADC Sample Rate Selection

Each ADC supports the following pre-defined sample rates, although other rates are programmable, e.g. 40kHz:

- 🛚 8kHz

- **=** 11.025kHz

- 16kHz

- **22.050kHz**

- 🛚 24kHz

- 🛎 32kHz

- 🕿 44.1kHz

- 🛚 48kHz

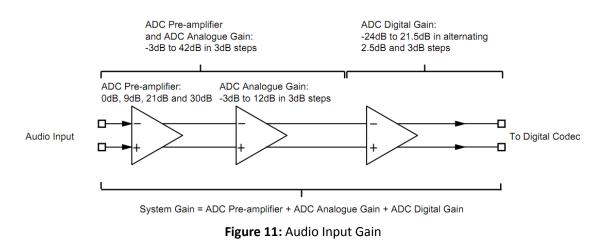

## ADC Audio Input Gain

The picture below shows that the FSC-BT806A audio input gain consists of:

- An analogue gain stage based on a pre-amplifier and an analogue gain amplifier

- A digital gain stage

#### ADC Pre-amplifier and ADC Analogue Gain

FSC-BT806A has an analogue gain stage based on an ADC pre-amplifier and ADC analogue amplifier:

- The ADC pre-amplifier has 4 gain settings: 0dB, 9dB, 21dB and 30dB

- The ADC analogue amplifier gain is -3dB to 12dB in 3dB steps

- The overall analogue gain for the pre-amplifier and analogue amplifier is -3dB to 42dB in 3dB steps

- At mid to high gain levels it acts as a microphone pre-amplifier

- At low gain levels it acts as an audio line level amplifier

#### ADC Digital Gain

A digital gain stage inside the ADC varies from -24dB to 21.5dB, see following table. There is also a fine gain interface with a 9-bit gain setting allowing gain changes in 1/32 steps, for more infomation contact Feasycom.

The firmware controls the audio input gain.

| Digital Gain Selection<br>Value | ADC Digital Gain Setting(dB) | Digital Gain Selection<br>Value | ADC Digital Gain Setting(dB) |

|---------------------------------|------------------------------|---------------------------------|------------------------------|

| 0                               | 0                            | 8                               | -24                          |

| 1                               | 3.5                          | 9                               | -20.5                        |

| 2                               | 6                            | 10                              | -18                          |

| 3                               | 9.5                          | 11                              | -14.5                        |

| 4                               | 12                           | 12                              | -12                          |

| 5                               | 15.5                         | 13                              | -8.5                         |

| 6                               | 18                           | 14                              | -6                           |

| 7                               | 21.5                         | 15                              | -2.5                         |

#### Table 7: ADC Audio Input Gain Rate

#### ADC Digital IIR Filter

The ADC contains 2 integrated anti-aliasing filters:

- A long IIR filter suitable for music (>44.1kHz)

- G.722 filter is a digital IIR filter that improves the stop-band attenuation required for G.722 compliance (which is the best selection for 8kHz / 16kHz / voice)

For more information contact Feasycom.

#### DAC

The DAC consists of:

- 2 fourth-order Sigma-Delta converters enabling 2 separate channels that are identical in functionality

- 2 gain stages for each channel, 1 of which is an analogue gain stage and the other is a digital gain stage.

#### DAC Sample Rate Selection

Each DAC supports the following sample rates:

- 🛚 8kHz

- 11.025kHz

- 🛎 16kHz

- **22.050kHz**

- 32kHz

- 🛎 40kHz

- 🕿 44.1kHz

- 🛎 48kHz

- 96kHz

## DAC Digital Gain

A digital gain stage inside the DAC varies from -24dB to 21.5dB, see following table. There is also a fine gain interface with a 9-bit gain setting enabling gain changes in 1/32 steps, for more information contact CSR.

The overall gain control of the DAC is controlled by the firmware. Its setting is a combined function of the digital and analogue amplifier settings.

| Digital Gain Selection<br>Value | DAC Digital Gain Setting(dB) | Digital Gain Selection<br>Value | DAC Digital Gain Setting(dB) |

|---------------------------------|------------------------------|---------------------------------|------------------------------|

| 0                               | 0                            | 8                               | -24                          |

| 1                               | 3.5                          | 9                               | -20.5                        |

| 2                               | 6                            | 10                              | -18                          |

| 3                               | 9.5                          | 11                              | -14.5                        |

| 4                               | 12                           | 12                              | -12                          |

| 5                               | 15.5                         | 13                              | -8.5                         |

| 6                               | 18                           | 14                              | -6                           |

| 7                               | 21.5                         | 15                              | -2.5                         |

#### Table 8: DAC Digital Gain Rate Selection

## DAC Analogue Gain

The following table shows that the DAC analogue gain stage consists of 8 gain selection values that represent seven 3dBsteps.

The firmware controls the overall gain control of the DAC. Its setting is a combined function of the digital and analogue amplifier settings.

#### Table 9: DAC Analogue Gain Rate Selection

| Analogue Gain Selection<br>Value | DAC Analogue Gain<br>Setting(dB) | Analogue Gain Selection<br>Value | DAC Analogue Gain<br>Setting(dB) |

|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| 7                                | 0                                | 3                                | -12                              |

| 6                                | -3                               | 2                                | -15                              |

| 5                                | -6                               | 1                                | -18                              |

| 4                                | -9                               | 0                                | -21                              |

#### **DAC Digital FIR Filter**

The DAC contains an integrated digital FIR filter with the following modes:

- A default long FIR filter for best performance at >= 44.1kHz.

- A short FIR to reduce latency.

- A narrow FIR (a very sharp roll-off at Nyquist) for G.722 compliance. Best for 8kHz / 16kHz.

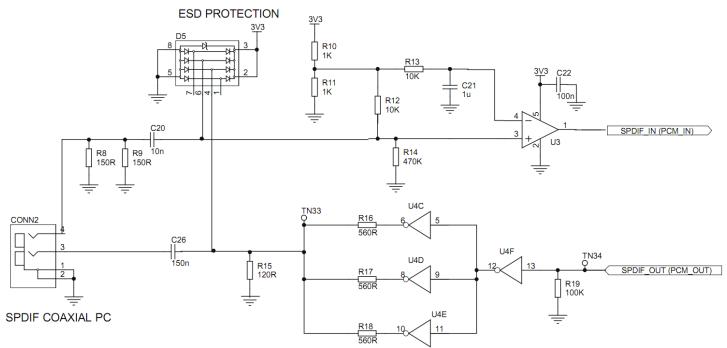

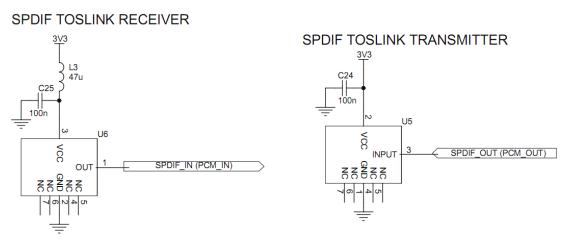

#### IEC 60958 Interface

The IEC 60958 interface is a digital audio interface that uses bi-phase coding to minimise the DC content of the transmitted signal and enables the receiver to decode the clock information from the transmitted signal. The IEC 60958 specification is based on the 2 industry standards:

- AES3 (also known as AES/EBU)

- Sony and Philips interface specification SPDIF

The interface is compatible with IEC 60958-1, IEC 60958-3 and IEC 60958-4.

The SPDIF interface signals are SPDIF\_IN and SPDIF\_OUT and are shared on the PCM interface pins. The input and output stages of the SPDIF pins interface to:

- A 75Ω coaxial cable with an RCA connector

- An optical link that uses Toslink optical components

Figure 12: Example Circuit for SPDIF Interface(Co-axial)

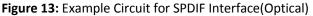

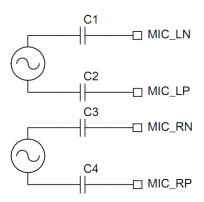

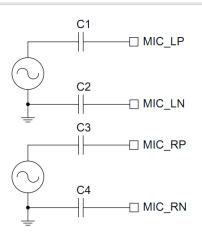

#### **Microphone Input**

FSC-BT806A contains an independent low-noise microphone bias generator. The microphone bias generator is recommended for biasing electret condensor microphones. Figure 9.6 shows a biasing circuit for microphones with a sensitivity between about -40 to -60dB (OdB = 1V/Pa).

#### Where:

- The microphone bias generator derives its power from VBAT or 3V3\_USB and requires no capacitor on its output.

- The microphone bias generator maintains regulation within the limits 70uA to 2.8mA, supporting a 2mA source typically required by 2 electret condensor microphones. If the microphone sits below these limits, then the microphone output must be pre-loaded with a large value resistor to ground.

- Biasing resistors R1 and R2 equal 2.2kΩ.

- When the input pre-amplifier is enabled, the input impedance at MIC\_LN, MIC\_LP, MIC\_RN and MIC\_RP varies between  $6k\Omega$ (pre-amplifier gain >0dB) and  $12k\Omega$ (pre-amplifier gain = 0dB).

- **C1**, C2, C3 and C4 are 100/150nF if bass roll-off is required to limit wind noise on the microphone.

- R1 and R2 set the microphone load impedance and are normally around 2.2kΩ.

Figure 14: Microphone Biasing

The microphone bias characteristics include:

- Power supply:

- FSC-BT806A microphone supply is VBAT or 3V3\_USB(inernal) Minimum input voltage = Output voltage + drop-out voltage Maximum input voltage is 4.3V

- Drop-out voltage:

- 300mV maximum

- Output voltage:

- 1.8V or 2.6V

- Tolerance 90% to 110%

- Output current: 70uA to 2.8mA

- No load capacitor required

## **Digital Microphone Inputs**

FSC-BT806A interfaces to 2 digital MEMS microphones. shows that 4 of the inputs have dedicated codec channels and 2 are multiplexed with the high-quality ADC channels.

Clock lines shared between 2 microphone outputs, linked to any even-numbered PIO pin as determinedby the firmware.

#### Note:

Multiple digital microphones can share the same clock if they are configured for the same frequency, e.g. 1 clock for 6 digital microphones.

Data lines shared between 2 microphone inputs, linked to any odd-numbered PIO as determined by the firmware.

#### Note:

For the digital microphone interface to work in this configuration ensure the microphone uses a tristate between edges.

The left and right selection for the digital microphones are appropriately pulled up or down for selection on the PCB.

## Line Input

The picture below show 2 circuits for line input operation and show connections for either differential or singleended inputs.

In line input mode, the input impedance of the pins to ground varies from  $6k\Omega$  to  $34k\Omega$  depending on input gain setting.

Figure 15: Differential Input

Figure 16: Single-ended Input

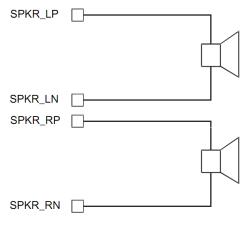

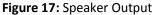

#### 4.8.3 Output Stage

The output stage digital circuitry converts the signal from 16-bit per sample, linear PCM of variable sampling frequency to bit stream, which is fed into the analogue output circuitry.

The analogue output circuit comprises a DAC, a buffer with gain-setting, a low-pass filter and a class AB output stage amplifier. The picture below shows that the output is available as a differential signal between SPKR\_LN and SPKR\_LP for the left channel, and between SPKR\_RN and SPKR\_RP for the right channel.

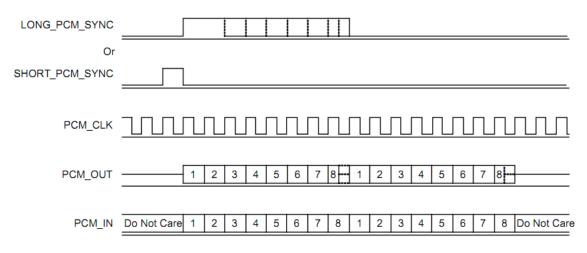

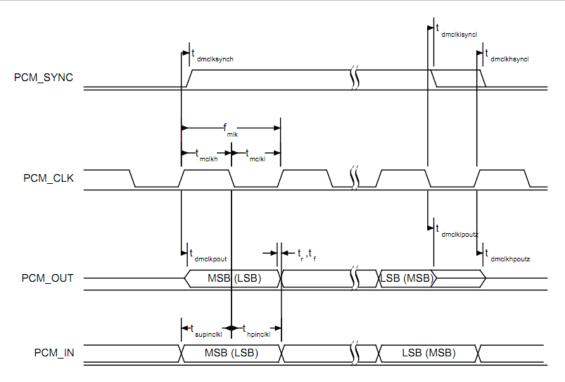

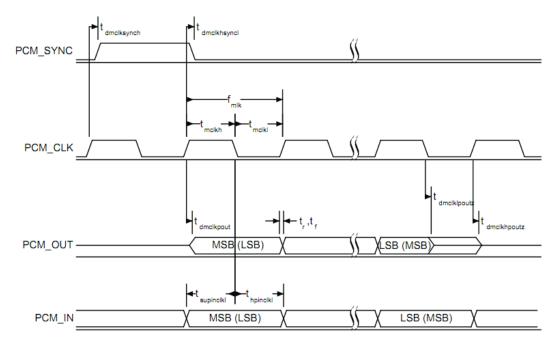

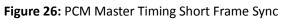

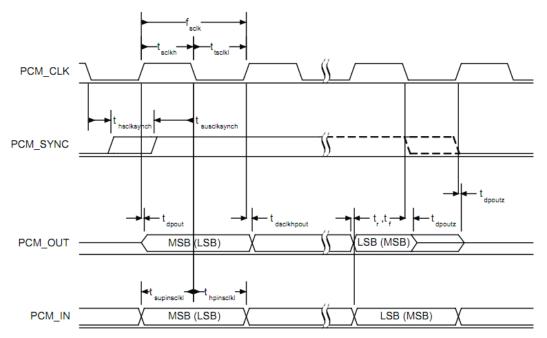

#### 4.8.4 PCM Controller

The audio PCM interface on the FSC-BT806A supports:

- On-chip routing to Kalimba DSP

- Continuous transmission and reception of PCM encoded audio data over Bluetooth.

- Processor overhead reduction through hardware support for continual transmission and reception of PCM data

- A bidirectional digital audio interface that routes directly into the baseband layer of the firmware. It does not pass through the HCI protocol layer.

- Hardware on the CSR8670 WLCSP for sending data to and from a SCO connection.

- Up to 3 SCO connections on the PCM interface at any one time.

- PCM interface master, generating PCM\_SYNC and PCM\_CLK.

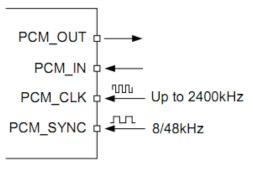

- PCM interface slave, accepting externally generated PCM\_SYNC and PCM\_CLK.

- Various clock formats including:

- Long Frame Sync

- Short Frame Sync

- GCI timing environments

- 13-bit or 16-bit linear, 8-bit μ-law or A-law companded sample formats.

- Receives and transmits on any selection of 3 of the first 4 slots following PCM\_SYNC.

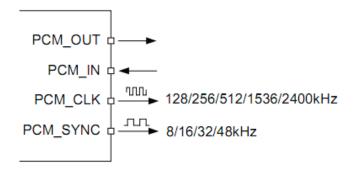

## PCM Interface Master/Slave

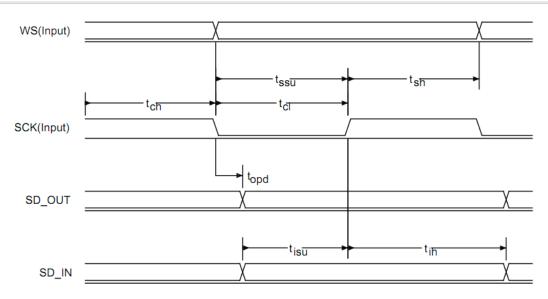

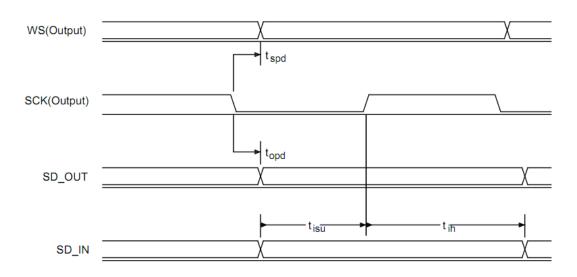

#### Figure 18: PCM Interface Master

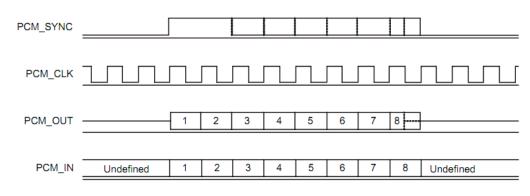

## Long Frame Sync

Figure 20: Long Frame Sync (shown with 8-bit Companded Sample)

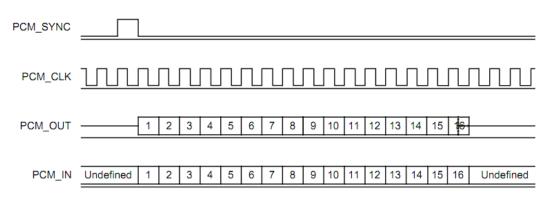

#### Short Frame Sync

Figure 21: Short Frame Sync (shown with 16-bit Sample)

#### Multi-slot Operation

Figure 22: Multi Slot Operation with 2 Slots and 8-bit Companded Samples

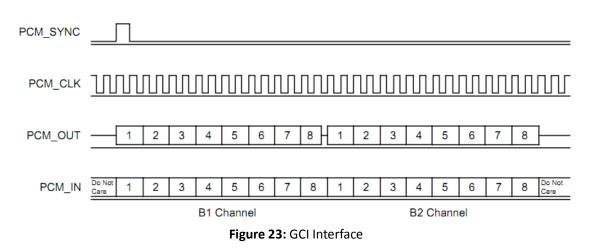

## **GCI** Interface

## Slots and Sample Formats

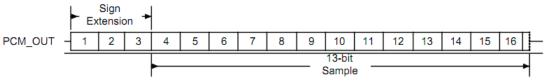

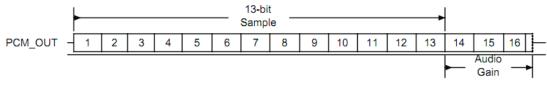

FSC-BT806A receives and transmits on any selection of the first 4 slots following each sync pulse. Slot durations are either 8 or 16 clock cycles:

- 8 clock cycles for 8-bit sample formats.

- **1**6 clocks cycles for 8-bit, 13-bit or 16-bit sample formats.

FSC-BT806A supports:

- **Ξ** 13-bit linear, 16-bit linear and 8-bit μ-law or A-law sample formats.

- A sample rate of 8ksamples/s, 16ksamples/s or 32ksamples/s.

- Little or big endian bit order.

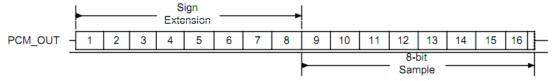

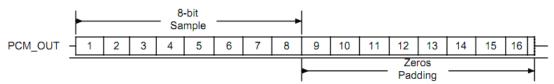

- For 16-bit slots, the 3 or 8 unused bits in each slot are filled with sign extension, padded with zeros or a programmable 3-bit audio attenuation compatible with some codecs.

A 16-bit slot with 8-bit companded sample and sign extension selected.

A 16-bit slot with 8-bit companded sample and zeros padding selected.

A 16-bit slot with 13-bit linear sample and sign extension selected.

A 16-bit slot with 13-bit linear sample and audio gain selected.

Figure 24: 16-bit Slot Length and Sample Formats

#### **Additional Features**

FSC-BT806A has a mute facility that forces PCM\_OUT to be 0. In master mode, FSC-BT806A is compatible with some codecs which control power down by forcing PCM\_SYNC to 0 while keeping PCM\_CLK running.

#### Figure 25: PCM Master Timing Long Frame Sync

Figure 27: PCM Slave Timing Long Frame Sync

Figure 28: PCM Slave Timing Short Frame Sync

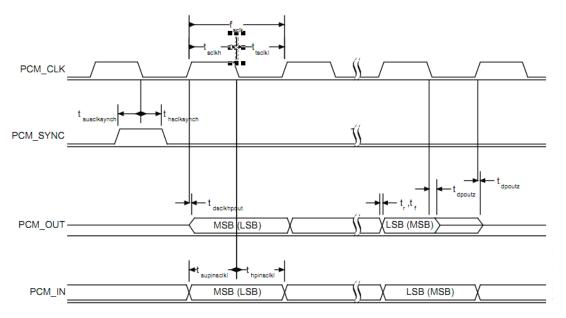

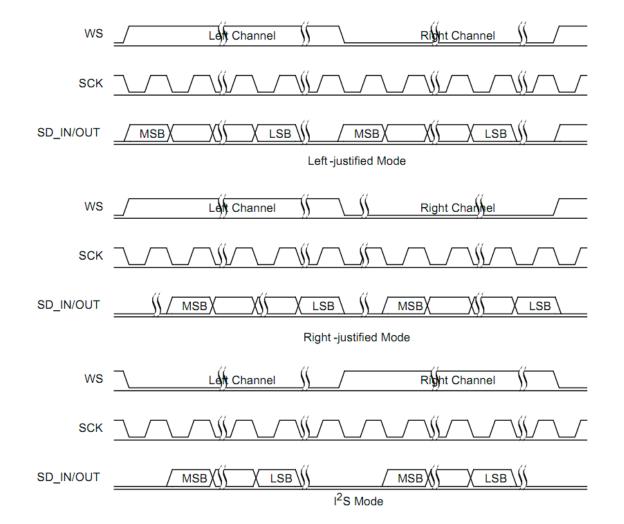

## 4.8.5 I<sup>2</sup>S Controller

The digital audio interface supports the industry standard formats for  $I^2 S$ , left-justified or right-justified. The interface shares the same pins as the PCM interface, which means each audio bus is mutually exclusive in its usage. This Table lists these alternative functions.

#### FSC-BT806 Datasheet

#### Table 10: Alternative functions of the digital audio bus interface on the PCM interface

| PCM Interface | I2S Interface |

|---------------|---------------|

| PCM_OUT       | I2S_OUT       |

| PCM_IN        | 125_IN        |

| PCM_SYNC      | I2S_WS        |

| PCM_CLK       | I2S_CLK       |

|               |               |

Figure 29: Digital Audio Interface Modes

Figure 30: Digital Audio Interface Slave Timing

Figure 31: Digital Audio Interface Master Timing

## 4.9 **Programming and Debug Interface**

#### **Important Note:**

The SPI is for programming, configuring (PS Keys) and debugging the FSC-BT806A. It is required in production. Ensure the 4 SPI signals are brought out to either test points or a header.

Feasycom provides development and production tools to communicate over the SPI from a PC, although a level translator circuit is often required.

FSC-BT806A uses a 16-bit data and 16-bit address programming and debug interface. Transactions occur when the internal processor is running or is stopped.

Data is written or read one word at a time, or the auto-increment feature is available for block access.

# 5. ELECTRICAL CHARACTERISTICS

### 5.1 Absolute Maximum Ratings

Absolute maximum ratings for supply voltage and voltages on digital and analogue pins of the module are listed below. Exceeding these values causes permanent damage.

The average PIO pin output current is defined as the average current value flowing through any one of the corresponding pins for a 100mS period. The total average PIO pin output current is defined as the average current value flowing through all of the corresponding pins for a 100mS period. The maximum output current is defined as the value of the peak current flowing through any one of the corresponding pins.

#### Table 11: Absolute Maximum Rating

| Parameter                              | Min     | Max                          | Unit |

|----------------------------------------|---------|------------------------------|------|

| 5V (VCC_CHG)                           | -0.4    | + 5.75 / 6.50 <sup>(a)</sup> | V    |

| BATTERY(LED 0,1,2)                     | -0.4    | +4.4                         | V    |

| BATTERY(VBAT_IN)                       | 2.7     | + 5.75                       | V    |

| BATTERY(VREGENABLE)                    | -0.4    | +4.4                         | V    |

| VDD_IO                                 | -0.4    | +3.6                         | V    |

| Other terminal voltages                | VSS-0.4 | VDD+0.4                      | V    |

| T <sub>A</sub> - Operating Temperature | -40     | +85                          | °C   |

| T <sub>ST</sub> - Storage Temperature  | -40     | +105                         | °C   |

(a) Standard maximum input voltage is 5.75V, a 6.50V maximum depends on firmware version and implementation of over-temperature protection software, for more information contact Feasycom.

### 5.2 Recommended Operating Conditions

#### Table 12: Recommended Operating Conditions

| Parameter                              | Min             | Туре | Max             | Unit |

|----------------------------------------|-----------------|------|-----------------|------|

| 5V (VCC_CHG)                           | 4.75 / 3.10 (a) | 5    | 5.75 / 6.50 (b) | V    |

| BATTERY(LED 0,1,2)                     | 1.10            | 3.70 | 4.30            | V    |

| BATTERY(VBAT_IN)                       | 2.8             | 3.3  | 4.30            | V    |

| BATTERY(VREGENABLE)                    | 0               | 3.3  | 4.30            | V    |

| VDD_IO                                 | 1.7             | 3.3  | 3.6             | V    |

| T <sub>A</sub> - Operating Temperature | -40             | 25   | +85             | °C   |

| T <sub>ST</sub> - Storage Temperature  | -40             | 25   | +85             | °C   |

(a) Minimum input voltage of 4.75V is required for full specification, regulator operates at reduced load current from 3.1V

(b) Standard maximum input voltage is 5.75V, a 6.50V maximum depends on firmware version and implementation of over-temperature protection software, for more information contact Feasycom.

## 5.3 Input/output Terminal Characteristics

### 5.3.1 Digital

#### Table 13: DC Characteristics ( $V_{DD} - V_{SS} = 3 \approx 3.6 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ )

| Parameter                                                          | Min        | Туре | Max        | Unit |

|--------------------------------------------------------------------|------------|------|------------|------|

| Input Voltage                                                      |            |      |            |      |

| V <sub>IL</sub> - Standard IO Low level input voltage              | -0.4       | -    | 0.4        | V    |

| $V_{\text{IH}}$ - Standard IO Low level input voltage              | 0.7XVDD_IO | -    | VDD_IO+0.4 | V    |

| Tr/Tf                                                              | -          | -    | 25         | nS   |

|                                                                    |            |      |            |      |

| Output Voltage                                                     |            |      |            |      |

| $V_{OL}$ - Low Level Output Voltage, $I_{OL}$ =4mA                 | -          | -    | 0.4        | V    |

| V <sub>OH</sub> - High Level Output Voltage, I <sub>OH</sub> =-4mA | 0.7XVDD_IO | -    | -          | V    |

| Tr/Tf                                                              | -          | -    | 5          | nS   |

|                                                                    |            |      |            |      |

| Input and Tristate Currents                                        |            |      |            |      |

| Strong pull-up                                                     | -150       | -40  | -10        | uA   |

| Strong pull-down                                                   | 10         | 40   | 150        | uA   |

| Weak pull-up                                                       | -5         | -1.0 | -0.33      | uA   |

| Weak pull-down                                                     | 0.33       | 1.0  | 5.0        | uA   |

| C I Input Capacitance                                              | 1.0        | -    | 5.0        | рF   |

|                                                                    |            |      |            |      |

### 5.3.2 Battery Charger

#### Table 14: Battery Charger

| Parameter                                                      | Min                 | Туре | Max           | Unit |

|----------------------------------------------------------------|---------------------|------|---------------|------|

| Battery Charger                                                |                     |      |               |      |

| Input voltage, VCHG                                            | 4.75 / 3.10(a) 5.00 |      | 5.75 /6.50(b) | V    |

| (a)Reduced specification from 3.1V to 4.75V. Full specificatio | n >4.75V.           |      |               |      |

(b) Standard maximum input voltage is 5.75V, a 6.50V maximum depends on firmware version and implementation of over-temperature protection software, for more information contact Feasycom.

| Trickle Charge Mode                                                        |   |     |    |   |

|----------------------------------------------------------------------------|---|-----|----|---|

| Charge current I <sub>trickle</sub> , as percentage of fast charge current | 8 | 10  | 12 | % |

| V <sub>fast</sub> rising threshold                                         | - | 2.9 | -  | V |

| V <sub>fast</sub> rising threshold trim step size                          | - | 0.1 | -  | V |

| V <sub>fast</sub> falling threshold                                        | - | 2.8 | -  | V |

| Fast Charge Mode                                                           |   |     |    |   |

| Tust enarge mode                |                      |     |     |     |    |

|---------------------------------|----------------------|-----|-----|-----|----|

| Charge current during constant  | Max, headroom >0.55V | 194 | 200 | 206 | mA |

| current mode, I <sub>fast</sub> | Min, headroom >0.55V | -   | 10  | -   | mA |

#### FSC-BT806 Datasheet

| Reduced headroom charge                       | Mid, headroom =0.15V                                                | 50   | -    | 100  | %  |

|-----------------------------------------------|---------------------------------------------------------------------|------|------|------|----|

| current, as a percentage of I <sub>fast</sub> |                                                                     |      |      |      |    |

| Charge current step size                      |                                                                     | -    | 10   | -    | mA |

| V <sub>float</sub> threshold, calibrated      |                                                                     | 4.16 | 4.20 | 4.24 | V  |

| Charge termination current I <sub>term</sub>  | Charge termination current $I_{term}$ , as percentage of $I_{fast}$ |      | 10   | 20   | %  |

|                                               |                                                                     |      |      |      |    |

| Standby Mode                                  |                                                                     |      |      |      |    |

| Voltage hysteresis on VBAT_IN, V              | / <sub>hyst</sub>                                                   | 100  | -    | 150  | mV |

|                                               |                                                                     |      |      |      |    |

| Error Charge Mode                             |                                                                     |      |      |      |    |

| Headroom(a) error falling thresh              | old                                                                 | -    | 50   | -    | mV |

| (a) Headroom = VCC_CHG – VBA                  | T_IN                                                                |      |      |      |    |